### LM5021

## **AC-DC Current Mode PWM Controller**

## **General Description**

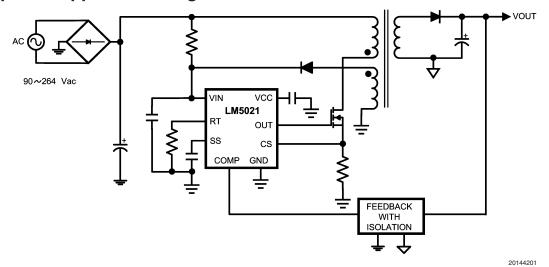

The LM5021 off-line pulse width modulation (PWM) controller contains all of the features needed to implement highly efficient off-line single-ended flyback and forward power converters using current-mode control. The LM5021 features include an ultra-low (25  $\mu A)$  start-up current, which minimizes power losses in the high voltage start-up network. A skip cycle mode reduces power consumption with light loads for energy conserving applications (ENERGY STAR®, CECP, etc.). Additional features include under-voltage lock-out, cycle-by-cycle current limit, hiccup mode overload protection, slope compensation, soft-start and oscillator synchronization capability. This high performance 8-pin IC has total propagation delays less than 100nS and a 1MHz capable oscillator that is programmed with a single resistor.

#### **Features**

- Ultra Low Start-up Current (25 µA maximum)

- Current Mode Control

- Skip Cycle Mode for Low Standby Power

- Single Resistor Programmable Oscillator

- Synchronizable Oscillator

- Adjustable Soft-start

- Integrated 0.7A Peak Gate Driver

- Direct Opto-Coupler Interface

- Maximum Duty Cycle Limiting (80% for LM5021-1 or 50% for LM5021-2)

- Slope Compensation for (LM5021-1 Only)

- Under Voltage Lockout (UVLO) with Hysteresis

- Cycle-by-Cycle Over-Current Protection

- Hiccup Mode for Continuous Overload Protection

- Leading Edge Blanking of Current Sense Signal

- Packages: MSOP-8 or MDIP-8

## **Simplified Application Diagram**

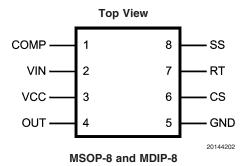

# **Connection Diagram**

# **Ordering Information**

| Order Number | Order Number Description |        | Supplied As                 |

|--------------|--------------------------|--------|-----------------------------|

| LM5021MM-1   | 80% Duty Cycle Limit     | MSOP-8 | 1000 Units on Tape and Reel |

| LM5021MMX-1  | 80% Duty Cycle Limit     | MSOP-8 | 3500 Units on Tape and Reel |

| LM5021NA-1   | 80% Duty Cycle Limit     | MDIP-8 | 40 Units per Rail           |

| LM5021MM-2   | 50% Duty Cycle Limit     | MSOP-8 | 1000 Units on Tape and Reel |

| LM5021MMX-2  | 50% Duty Cycle Limit     | MSOP-8 | 3500 Units on Tape and Reel |

| LM5021NA-2   | 50% Duty Cycle Limit     | MDIP-8 | 40 Units per Rail           |

# **Pin Description**

| PIN | NAME      | DESCRIPTION                                 | APPLICATION INFORMATION                                   |  |  |

|-----|-----------|---------------------------------------------|-----------------------------------------------------------|--|--|

| 1   | COMP      | Control input for the Pulse Width Modulator | COMP pull-up is provided by an internal 5K resistor       |  |  |

|     |           | and Hiccup comparators.                     | which may be used to bias an opto-coupler transistor.     |  |  |

| 2   | VIN       | Input voltage.                              | Input to start-up regulator. The VIN pin is clamped at    |  |  |

|     |           |                                             | 36V by an internal zener diode.                           |  |  |

| 3   | vcc       | Output of a linear bias supply regulator.   | VCC provides bias to controller and gate drive sections   |  |  |

|     |           | Nominally 8.5V.                             | of the LM5021. An external capacitor must be connected    |  |  |

|     |           |                                             | from this pin to ground.                                  |  |  |

| 4   | OUT       | MOSFET gate driver output.                  | High current output to the external MOSFET gate input     |  |  |

|     |           |                                             | with source/sink current capability of 0.3A and 0.7A      |  |  |

|     |           |                                             | respectively.                                             |  |  |

| 5   | GND       | Ground return.                              |                                                           |  |  |

| 6   | CS        | Current Sense input.                        | Current sense input for current mode control and          |  |  |

|     |           |                                             | over-current protection. Current limiting is accomplished |  |  |

|     |           |                                             | using a dedicated current sense comparator. If the CS     |  |  |

|     |           |                                             | comparator input exceeds 0.5 Volts the OUT pin            |  |  |

|     |           |                                             | switches low for cycle-by-cycle current limit. CS is held |  |  |

|     |           |                                             | low for 90ns after OUT switches high to blank the         |  |  |

|     |           |                                             | leading edge current spike.                               |  |  |

| 7   | RT / SYNC | Oscillator timing resistor pin and          | An external resistor connected from RT to GND sets the    |  |  |

|     |           | synchronization input.                      | oscillator frequency. This pin will also accept           |  |  |

|     |           |                                             | synchronization pulses from an external clock.            |  |  |

| 8   | SS        | Soft-start / Hiccup time                    | An external capacitor and an internal 22 µA current       |  |  |

|     |           |                                             | source set the soft-start ramp. The soft -start capacitor |  |  |

|     |           |                                             | controls both the soft-start rate and the hiccup mode     |  |  |

|     |           |                                             | period.                                                   |  |  |

www.national.com 2

2kV

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

VIN to GND -0.3V to 30V

VIN Clamp Continuous Current 5mA

CS to GND -0.3V to 1.25V

RT to GND -0.3V to 5.5V

All other pins to GND -0.3V to 7.0V

ESD Rating (Note 2)

Human Body Model

Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ Operating Junction Temperature  $+150^{\circ}\text{C}$

## **Operating Ratings** (Note 1)

VIN Voltage (Note 5) 8V to 30V Junction Temperature -40°C to +125°C

**Electrical Characteristics** Specifications in standard type face are for  $T_J = +25^{\circ}C$  and those in **boldface type** apply over the full **Operating Junction Temperature Range**. Unless otherwise specified:  $V_{IN} = 15V$ ,  $R_T = 44.2K\Omega$ . (Note 3)

| Symbol              | Parameter                        | Conditions                                                                    | Min  | Тур  | Max  | Unit |

|---------------------|----------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| STARTUP             | CIRCUIT                          |                                                                               |      | -    |      |      |

|                     | Start Up Current                 | Before VCC Enable                                                             |      | 18   | 25   | μA   |

|                     | VCC Regulator enable threshold   |                                                                               | 17   | 20   | 23   | V    |

|                     | VCC Regulator disable threshold  |                                                                               |      | 7.25 |      | V    |

|                     | VIN ESD Clamp voltage            | I = 5mA                                                                       | 30   | 36   | 40   | V    |

| I <sub>VIN</sub>    | Operating supply current         | COMP = 0VDC                                                                   |      | 2.5  | 3.75 | mA   |

| VCC SUPP            | LY                               |                                                                               |      |      |      |      |

|                     | Controller enable threshold      |                                                                               | 6.5  | 7    | 7.5  | V    |

|                     | Controller disable threshold     |                                                                               | 5.3  | 5.8  | 6.3  | V    |

|                     | VCC regulated output             | No External Load                                                              | 8    | 8.5  | 9    | V    |

|                     | VCC dropout voltage (VIN - VCC)  | I = 5 mA                                                                      |      | 1.7  |      | V    |

|                     | VCC regulator current limit      | VCC = 7.5V (Note<br>4)                                                        | 15   | 22   |      | mA   |

| SKIP CYCL           | E MODE COMPARATOR                |                                                                               |      |      |      | '    |

|                     | Skip Cycle mode enable threshold | ⅓ [COMP - 1.25V]                                                              | 75   | 125  | 175  | mV   |

|                     | Skip Cycle mode hysteresis       |                                                                               |      | 5    |      | mV   |

| CURRENT             | LIMIT                            |                                                                               |      |      | l    | _    |

|                     | CS limit to OUT delay            | CS stepped from 0 to 0.6V, time to OUT transition low, C <sub>load</sub> = 0. |      | 35   |      | ns   |

|                     | CS limit threshold               |                                                                               | 0.45 | 0.5  | 0.55 | V    |

|                     | Leading Edge Blanking time       |                                                                               |      | 90   |      | ns   |

|                     | CS blanking sinking impedance    |                                                                               |      | 35   | 55   | Ω    |

| SOFT-STA            | RT                               |                                                                               |      |      |      |      |

| V <sub>SS-OCV</sub> | SS pin open-circuit voltage      |                                                                               | 4.3  | 5.2  | 6.1  | V    |

|                     | Soft-start Current Source        |                                                                               | 15   | 22   | 30   | μΑ   |

|                     | Soft-start to COMP Offset        |                                                                               | 0.35 | 0.55 | 0.75 | V    |

|                     | COMP sinking impedance           | During SS ramp                                                                |      | 60   |      | Ω    |

| OSCILLAT            | OR                               | I                                                                             |      |      |      |      |

|                     | Frequency1 (RT = 44.2K)          |                                                                               | 135  | 150  | 165  | kHz  |

|                     | Frequency2 (RT = 13.3K)          |                                                                               | 440  | 500  | 560  | kHz  |

|                     | Sync threshold                   |                                                                               | 2.4  | 3.2  | 3.8  | V    |

**Electrical Characteristics** Specifications in standard type face are for  $T_J = +25^{\circ}C$  and those in **boldface type** apply over the full **Operating Junction Temperature Range**. Unless otherwise specified:  $V_{IN} = 15V$ ,  $R_T = 44.2K\Omega$ . (Note 3) (Continued)

| Symbol            | Parameter                        | Conditions                        | Min                       | Тур                       | Max                       | Unit |

|-------------------|----------------------------------|-----------------------------------|---------------------------|---------------------------|---------------------------|------|

| PWM COM           | PARATOR                          |                                   |                           |                           |                           |      |

|                   | COMP to OUT delay                | COMP set to 2V                    |                           | 20                        |                           | ns   |

|                   |                                  | CS stepped 0 to                   |                           |                           |                           |      |

|                   |                                  | 0.4V, time to OUT                 |                           |                           |                           |      |

|                   |                                  | transition low, C <sub>load</sub> |                           |                           |                           |      |

|                   |                                  | = 0.                              |                           |                           |                           |      |

|                   | Min Duty Cycle                   | COMP = 0V                         |                           |                           | 0                         | %    |

|                   | Max Duty Cycle (-1 Device)       |                                   | 75                        | 80                        | 85                        | %    |

|                   | Max Duty Cycle (-2 Device)       |                                   |                           | 50                        |                           | %    |

|                   | COMP to PWM comparator gain      |                                   |                           | 0.33                      |                           |      |

|                   | COMP Open Circuit Voltage        |                                   | 4.2                       | 5.1                       | 6                         | V    |

|                   | COMP at Max Duty Cycle           |                                   |                           | 2.75                      |                           | V    |

|                   | COMP Short Circuit Current       | COMP = 0V                         | 0.6                       | 1.1                       | 1.5                       | mA   |

| SLOPE CO          | MPENSATION                       |                                   |                           |                           |                           |      |

|                   | Slope Comp Amplitude             | CS pin to PWM                     | 70                        | 90                        | 110                       | mV   |

|                   | (LM5021-1 only)                  | Comparator offset at              |                           |                           |                           |      |

|                   |                                  | maximum duty cycle                |                           |                           |                           |      |

| OUTPUT S          | ECTION                           |                                   |                           |                           |                           |      |

|                   | OUT High Saturation              | IOUT = 50mA, VCC                  |                           | 0.6                       | 1.1                       | V    |

|                   |                                  | - OUT                             |                           |                           |                           |      |

|                   | OUT Low Saturation               | IOUT = 100mA                      |                           | 0.3                       | 1                         | V    |

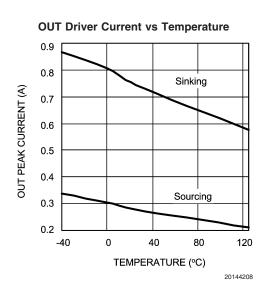

|                   | Peak Source Current              | OUT = VCC/2.                      |                           | 0.3                       |                           | Α    |

|                   | Peak Sink Current                | OUT = VCC/2.                      |                           | 0.7                       |                           | Α    |

|                   | Rise time                        | C <sub>load</sub> = 1nF           |                           | 25                        |                           | ns   |

|                   | Fall time                        | C <sub>load</sub> = 1nF           |                           | 10                        |                           | ns   |

| HICCUP M          | ODE                              |                                   |                           |                           | '                         |      |

| V <sub>OVLD</sub> | Over load detection threshold    | COMP pin                          | V <sub>SS-OCV</sub> - 0.8 | V <sub>SS-OCV</sub> - 0.6 | V <sub>SS-OCV</sub> - 0.4 | V    |

| V <sub>HIC</sub>  | Hiccup mode threshold            | SS pin                            | V <sub>SS-OCV</sub> - 0.8 | V <sub>SS-OCV</sub> - 0.6 |                           | V    |

| V <sub>RST</sub>  | Hiccup mode Restart threshold    | SS pin                            | 0.1                       | 0.3                       | 0.5                       | V    |

| I <sub>DTCS</sub> | Dead-time current source         |                                   | 0.1                       | 0.25                      | 0.4                       | μA   |

| l <sub>ovcs</sub> | Overload detection timer current |                                   | 6                         | 10                        | 14                        | μA   |

|                   | source                           |                                   |                           |                           |                           |      |

| THERMAL           | RESISTANCE                       |                                   |                           |                           |                           |      |

| $\theta_{JA}$     | MSOP-8 Junction to Ambient       | 0 LFM                             |                           | 200                       |                           | °C/W |

| $\theta_{JA}$     | MDIP-8 Junction to Ambient       | 0 LFM                             |                           | 107                       |                           | °C/W |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: The human body model is a 100 pF capacitor discharged through a  $1.5 k\Omega$  resistor into each pin.

Note 3: Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 4: Device thermal limitations may limit usable range.

Note 5: After initial turn-on at VIN = 20V.

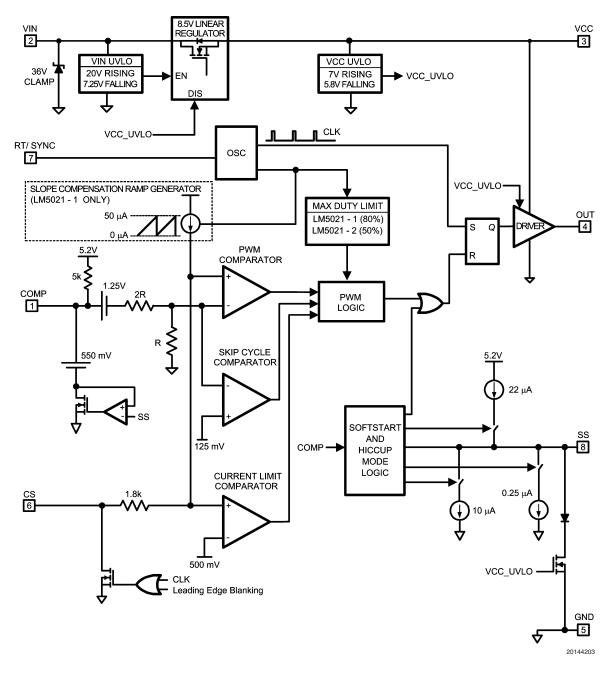

## **Simplified Block Diagram**

FIGURE 1.

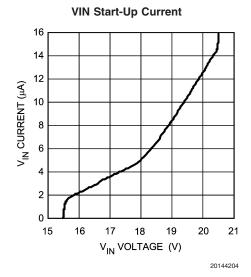

## **Typical Performance Characteristics** Unless otherwise specified: T<sub>J</sub> = 25°C.

## Typical Performance Characteristics Unless otherwise specified: T<sub>J</sub> = 25°C. (Continued)

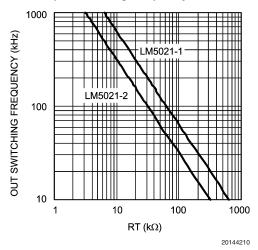

#### **Output Switching Frequency vs RT**

### **Detailed Operating Description**

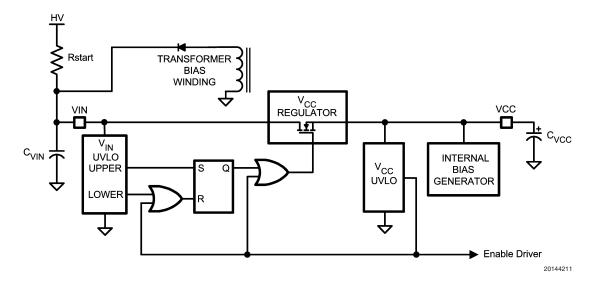

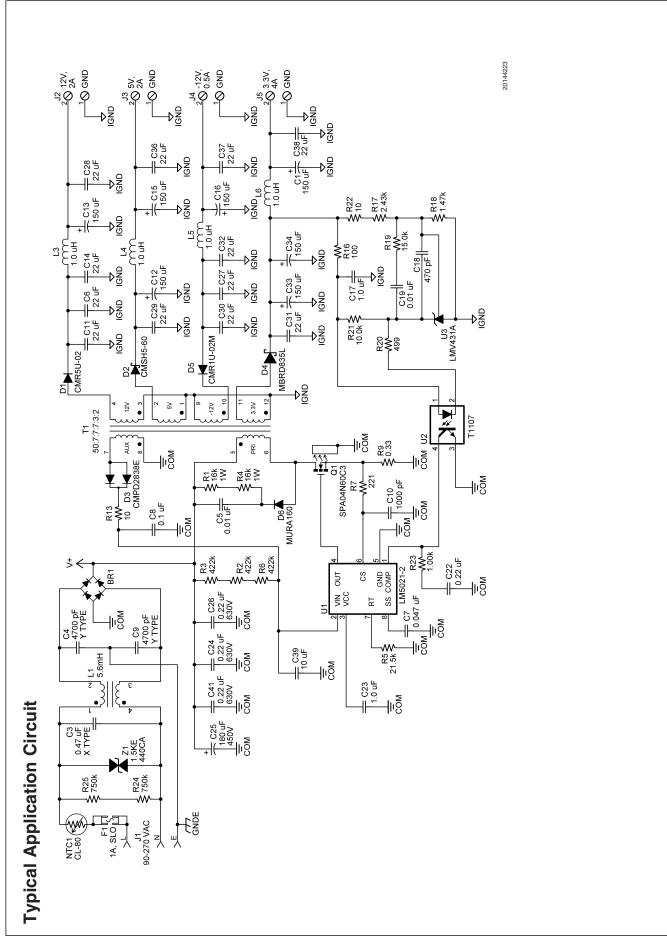

#### START UP CIRCUIT

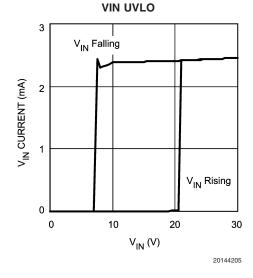

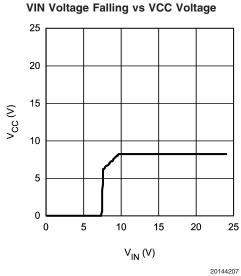

Referring to Figure 2, the input capacitor  $C_{VIN}$  is trickle charged through the start-up resistor Rstart, when the rectified ac input voltage HV is applied. The VIN current consumed by the LM5021 is only 18  $\mu$ A (nominal) while the capacitor  $C_{VIN}$  is initially charged to the start-up threshold. When the input voltage, VIN reaches the upper VIN UVLO threshold of 20V, the internal VCC linear regulator is enabled. The VCC regulator will remain on until VIN falls to the lower UVLO threshold of 7.25V (12.5V hysteresis). When the VCC regulator is turned on, the external capacitor at the VCC pin begins to charge. The PWM controller, soft-start circuit and gate driver are enabled when the VCC voltage reaches the VCC UVLO upper threshold of 7V. The VCC UVLO has 1.2V hysteresis between the upper and lower

thresholds to avoid chattering during transients on the VCC pin. When the VCC UVLO enables the switching power supply, energy is transferred from the primary to the secondary transformer winding(s). A bias winding, shown in *Figure 2*, delivers power to the VIN pin to sustain the VCC regulator. The voltage supplied should be from 11V (VCC regulated voltage maximum plus VCC regulator dropout voltage) to 30V (maximum operating VIN voltage). The start-up sequence is completed and normal operation begins when the voltage from the bias winding is sufficient to maintain VCC level greater than the VCC UVLO threshold (5.8V typical).

The size of the start-up resistor Rstart not only affects power supply start-up time, but also power supply efficiency since the resistor dissipates power in normal operation. The ultra low start-up current of the LM5021 allows a large value Rstart resistor (up to 3  $M\Omega)$  for improved efficiency with reasonable start-up time.

FIGURE 2. Start-Up Circuit Block Diagram

## **Detailed Operating Description**

(Continued)

# RELATIONSHIP BETWEEN INPUT CAPACITOR $C_{\text{IN}}$ & $V_{\text{CC}}$ CAPACITOR $C_{\text{VCC}}$

The internal VCC linear regulator is enabled when VIN reaches 20V. The drop in VIN due to charge transfer from  $C_{\rm VIN}$  to  $C_{\rm VCC}$  after the regulator is enabled can be calculated from the following equations where VIN' is the voltage on  $C_{\rm VIN}$  immediately after the VCC regulator charges  $C_{\rm VCC}$ .

$$\Delta$$

VIN x C<sub>VIN</sub> =  $\Delta$ VCC x C<sub>VCC</sub>

$$(20V - V_{IN'}) C_{VIN} = 8.5V C_{VCC}$$

$$VIN = 20V - \left(8.5V \times \frac{C_{VCC}}{C_{VIN}}\right)$$

Assuming  $C_{VIN}$  value as 10  $\mu$ F, and  $C_{VCC}$  of 1 $\mu$ F, then the drop in VIN will be 0.85V, or the VIN value drops to 19.15V. The value of the VCC capacitor can be small (less than 1 $\mu$ F) as it supplies only transient gate drive current of a short duration. The  $C_{VIN}$  capacitor must be sized to supply the gate drive current and the quiescent current of LM5021until the transformer bias winding delivers sufficient voltage to VIN to sustain the VCC voltage.

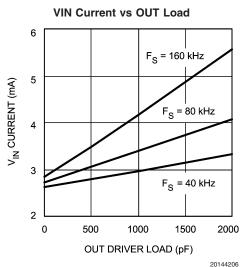

The C<sub>VIN</sub> capacitor value can be calculated from the operating VCC load current after it's output voltage reaches the VCC UVLO threshold. For example, if the LM5021 is driving an external MOSFET with total gate charge (Qg) of 25nC, the average gate drive current is Qg x Fsw, where Fsw is the switching frequency. Assuming a switching frequency of 150KHz, the average gate drive current is 3.75mA. Since the IC consumes approximately 2.5mA operating current in addition to the gate current, the total current drawn from  $C_{VIN}$ capacitor is the operating current plus the gate charge current, or 6.25mA. The  $C_{\text{VIN}}$  capacitor must supply this current for a brief time until the transformer bias winding takes over. The C<sub>VIN</sub> voltage must not fall below 8.5V during the start-up sequence or the cycle will be restarted. The maximum allowable start-up time can be calculated using the value of C<sub>VIN</sub>, the change in voltage allow at VIN (19.15V - 8.5V) and the VCC regulator current (6.25mA). Tmax, the maximum time allowed to energize the bias winding is:

Tmax =

$$\frac{C_{VIN} \times (19.15V - 8.5V)}{6.25 \text{ mA}}$$

= 17 ms

If the calculated value of Tmax is too small, the value of Cin should be increased further to allow more time before the transformer bias winding takes over and delivers the operating current to the VCC regulator. Increasing  $C_{\text{VIN}}$  will increase the time from the application of the rectified ac (HV in the *Figure 2*) to the time when VIN reaches the 20V start threshold. The initial charging time of  $C_{\text{VIN}}$  is:

$$T_{VIN\_THRESHOLD} = R_{START} \times C_{VIN} \times In \left[ \left( 1 - \frac{20V}{HV} \right)^{-1} \right]$$

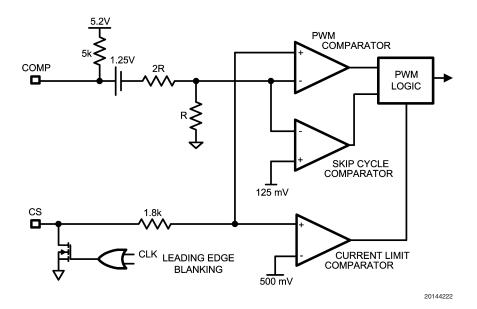

#### PWM COMPARATOR/SLOPE COMPENSATION

The PWM comparator compares the current sense signal with the loop error voltage from the COMP pin. The COMP pin voltage is reduced by 1.25V then attenuated by a 3:1 resistor divider. The PWM comparator input offset voltage is designed such that less than 1.25V at the COMP pin will result in a zero duty cycle at the controller output.

For duty cycles greater than 50 percent, current mode control circuits are subject to sub-harmonic oscillation. By adding an additional fixed slope voltage ramp signal (slope compensation) to the current sense signal, this oscillation can be avoided. The LM5021-1 integrates this slope compensation by summing a ramp signal generated by the oscillator with the current sense signal. The slope compensation is generated by a current ramp driven through an internal 1.8 k $\Omega$  resistor connected to the CS pin. Additional slope compensation may be added by increasing the resistance between the current sense filter capacitor and the CS pin, thereby increasing the voltage ramp created by the oscillator current ramp. Since the LM5021-2 is not capable of duty cycles greater than 50%, there is no slope compensation feature in this device.

#### **CURRENT LIMIT/CURRENT SENSE**

The LM5021 provides a cycle-by-cycle over current protection feature. Current limit is triggered by an internal current sense comparator threshold which is set at 500mV. If the CS pin voltage plus the slope compensation voltage exceeds 500mV, the OUT pin output pulse will be immediately terminated

An RC filter, located near the LM5021, is recommended for the CS pin to attenuate the noise coupled from the power FET's gate to source. The CS pin capacitance is discharged at the end of each PWM clock cycle by an internal switch. The discharge switch remains on for an additional 90ns leading edge blanking interval to attenuate the current sense transient that occurs when the external power FET is turned on. In addition to providing leading edge blanking, this circuit also improves dynamic performance by discharging the current sense filter capacitor at the conclusion of every cycle.

The LM5021 CS comparator is very fast, and may respond to short duration noise pulses. Layout considerations are critical for the current sense filter and sense resistor. The capacitor associated with the CS filter must be placed very close to the device and connected directly to the pins of the IC (CS and GND). If a current sense transformer is used, both leads of the transformer secondary should be routed to the sense resistor, which should also be located close to the IC. If a current sense resistor located in the power FET's source is used for current sense, a low inductance resistor is required. In this case, all of the noise sensitive low current grounds should be connected in common near the IC and then a single connection should be made to the power ground (sense resistor ground point).

#### OSCILLATOR, SHUTDOWN and SYNC CAPABILITY

A single external resistor connected between RT and GND pins sets the LM5021 oscillator frequency. The LM5021-2 device, with 50% maximum duty cycle, includes an internal flip-flop that divides the oscillator frequency by two. This method produces a precise 50% maximum duty cycle limit. Because of this frequency divider, the oscillator frequency of the LM5021-2 is actually twice the frequency of the gate drive output (OUT). For the LM5021-1 device, the oscillator

8

## **Detailed Operating Description**

(Continued)

frequency and the operational output frequency are the same. To set a desired output switching frequency (Fsw), the RT resistor can be calculated from:

LM5021-1:

RT =

$$\frac{6.63 \times 10^9}{F_{SW}}$$

LM5021-2:

$$RT = \frac{6.63 \times 10^9}{2 \times F_{SW}}$$

The LM5021 can also be synchronized to an external clock. The external clock must have a higher frequency than the free running oscillator frequency set by the RT resistor. The clock signal should be capacitively coupled into the RT pin with a 100pF capacitor. A peak voltage level greater than 3.8 Volts at the RT pin is required for detection of the sync pulse. The dc voltage across the RT resistor is internally regulated at 2 volts. Therefore, the ac pulse superimposed on the RT resistor must have 1.8V or greater amplitude to successfully synchronize the oscillator. The sync pulse width should be set between 15ns to 150ns by the external components. The RT resistor is always required, whether the oscillator is free running or externally synchronized. The RT resistor should be located very close to the device and connected directly to the pins of the LM5021 (RT and GND).

#### **GATE DRIVER and MAX DUTY CYCLE LIMIT**

The LM5021 provides a gate driver (OUT), which can source peak current of 0.3A and sink 0.7A. The LM5021 is available in two duty-cycle limit options. The maximum output duty-cycle is typically 80% for the LM5021-1 option, and precisely equal to 50% for the LM5021-2 option. The maximum duty cycle function for the LM5021-2 is accomplished with an internal toggle flip-flop to ensure an accurate duty cycle limit. The internal oscillator frequency of the LM5021-2 is therefore twice the switching frequency of the PWM controller (OUT pin).

The 80% maximum duty-cycle function for the LM5021-1 is determined by the internal oscillator. For the LM5021-1 the internal oscillator frequency and the switching frequency of the PWM controller are the same.

#### **SOFT-START**

The soft-start feature allows the power converter to gradually reach the initial steady state operating point, thus reducing start-up stresses and current surges. An internal 22  $\mu A$  current source charges an external capacitor connected to the SS pin. The capacitor voltage will ramp up slowly, limiting the COMP pin voltage and the duty cycle of the output pulses. The soft-start capacitor is also used to generate the hiccup mode delay time when the output of the switching power supply is continuously overloaded.

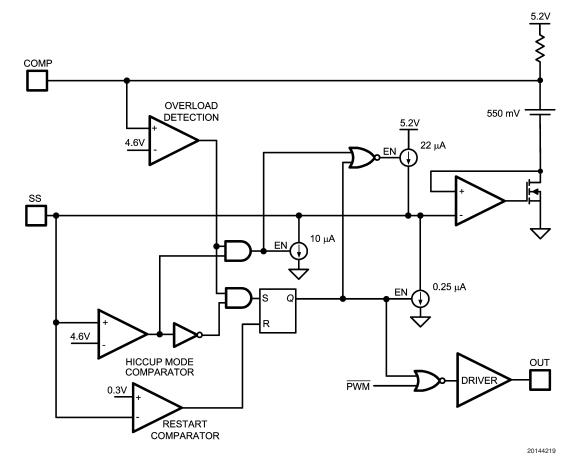

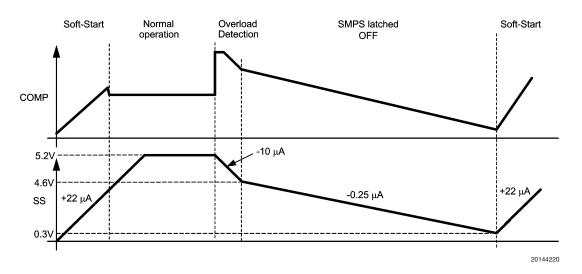

#### HICCUP MODE OVERLOAD CURRENT LIMITING

Hiccup mode is a method of protecting the power supply from over-heating and damage during an extended overload condition. When the output fault is removed the power supply will automatically restart.

Figure 3, Figure 4 and Figure 5 illustrate the equivalent circuit of the hiccup mode for LM5021 and the relevant waveforms. During start-up and in normal operation, the external soft-start capacitor Css is pulled up by a current source that delivers 22 µA to the SS pin capacitor. In normal operation, the soft-start capacitor continues to charge and eventually reaches the saturation voltage of the current source (V<sub>SS OCV</sub>, nominally 5.2V). During start-up the COMP pin voltage follows the SS capacitor voltage and gradually increases the peak current delivered by the power supply. When the output of the switching power supply reaches the desired voltage, the voltage feedback amplifier takes control of the COMP signal (via the opto-coupler). In normal operation the COMP level is held at an intermediate voltage between 1.25V and 2.75V controlled by the voltage regulation loop. When the COMP pin voltage is below 1.25V, the duty-cycle is zero. When the COMP level is above 2.75V, the duty cycle will be limited by the 0.5V threshold of cycleby-cycle current limit comparator.

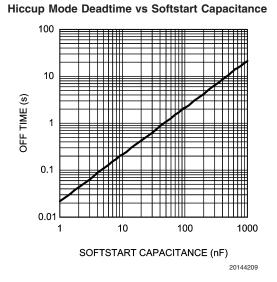

If the output of the power supply is overloaded, the voltage regulation loop demands more current by increasing the COMP pin control voltage. When the COMP pin exceeds the over voltage detection threshold (VOVLD, nominally 4.6V), the SS capacitor Css will be discharged by a 10 µA overload detection timer current source,  $I_{\rm OVCS}$ . If COMP remains above V<sub>OVLD</sub> long enough for the SS capacitor to discharge to the Hiccup mode threshold ( $V_{HIC}$ , nominally 4.6V), the controller enters the hiccup mode. The OUT pin is then latched low and the SS capacitor discharge current source is reduced from 10  $\mu A$  to 0.25  $\mu A$ , the dead-time current source, I<sub>DTCS</sub>. The SS pin voltage is slowly reduced until it reaches the Restart threshold (V<sub>RST</sub>, nominally 0.3V). Then a new start-up sequence commences with 22 µA current source charging the capacitor Css. The slow discharge of the SS capacitor from the Hiccup threshold to the Restart threshold provides an extended off time that reduces the overheating of components including diodes and MOSFETs due to the continuous overload. The off time during the hiccup mode can be calculated from the following equation:

Toff =

$$\frac{C_{SS} \times (V_{HC} - V_{RST})}{I_{DTCS}} = \frac{C_{SS} \times (4.6V - 0.3V)}{0.25 \,\mu\text{A}}$$

Example:

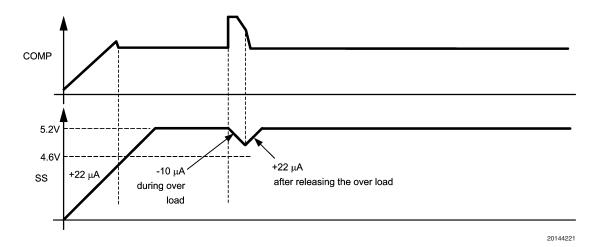

Toff = 808 ms, assuming the  $C_{SS}$  capacitor value is 0.047  $\mu F$  Short duration intermittent overloads will not trigger the hiccup mode. The overload duration required to trigger the hiccup response is set by the capacitor  $C_{SS}$ , the 10  $\mu A$  discharge current source and voltage difference between the saturation level of the SS pin and the Hiccup mode threshold. Figure 5 shows the waveform of SS pin with a short duration overload condition. The overload time required to enter the hiccup mode can be calculated from the following equation:

Toverload =

$$\frac{C_{SS} \times (V_{SS\_OCV} - V_{HC})}{I_{OVCS}} = \frac{C_{SS} \times 0.6V}{10 \mu A}$$

Example:

Toverload = 2.82 ms, assuming the  $C_{\text{SS}}$  capacitor value is 0.047  $\mu\text{F}$

## **Detailed Operating Description** (Continued)

FIGURE 3. Hiccup Mode Control

FIGURE 4. Waveform at SS and COMP Pin due to Continuous Overload

### **Detailed Operating Description** (Continued)

FIGURE 5. Waveform at SS and COMP Pin due to Brief Overload

#### SKIP CYCLE OPERATION

During light load conditions, the efficiency of the switching power supply typically drops as the losses associated with switching and operating bias currents of the converter become a significant percentage of the power delivered to the load. The largest component of the power loss is the switching loss associated with the gate driver and external MOSFET gate charge. Each PWM cycle consumes a finite amout of energy as the MOSFET is turned on and then turned off. These switching losses are proportional to the frequency of operation. The Skip Cycle function integrated within the LM5021 controller reduces the average switching frequency to reduce switching losses and improve efficiency during light load conditions.

When a light load condition occurs, the COMP pin voltage is reduced by the voltage feedback loop to reduce the peak current delivered by the controller. Referring to *Figure 6*, the PWM comparator input tracks the COMP pin voltage through

a 1.25V level shift circuit and a 3:1 resistor divider. As the COMP pin voltage falls, the input to the PWM comparator falls proportionately. When the PWM comparator input falls to 125mV, the Skip Cycle comparator detects the light load condition and disables output pulses from the controller. The controller continues to skip switching cycles until the power supply output falls and the COMP pin voltage increases to demand more output current. The number of cycles skipped will depend on the load and the response time of the frequency compensation network. Eventually the COMP voltage will increase when the voltage loop requires more current to sustain the regulated output voltage. When the PWM comparator input exceeds 130mV (5mV hysteresis), normal fixed frequency switching resumes. Typical power supply designs will produce a short burst of output pulses followed by a long skip cycle interval. The average switching frequency in the Skip Cycle mode can be a small fraction of the normal operating frequency of the power supply.

# **Detailed Operating Description** (Continued)

FIGURE 6. Skip Cycle Control

www.national.com 12

13 www.national.com

#### Physical Dimensions inches (millimeters) unless otherwise noted В .118±.004 [3±0.1] (.189) .193±.006 [4.9±0.15] .118±.004 PIN 1 IDENT-LAND PATTERN RECOMMENDATION -GAGE PLANE R.005 TYP [0.13] .010 [0.25] A .004 [0.1] A .012<sup>+</sup>.004 [0.3<sup>+0.10</sup><sub>-0.05</sub> .007±.002 TYP [0.18±0.05] -SEATING PLANE ф .002 [0.05] M BS CS (.0375 [0.953] CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS MUA08A (Rev E) 8 Lead MSOP Package **NS Package Number MUA08A** 0.373 - 0.400(9.474 - 10.16)-<u>0.090</u> (2.286) 7 6 5 8 8 7 0.092 DIA $\boldsymbol{0.032 \pm 0.005}$ (2.337) $(0.813 \pm 0.127)$ $0.250 \pm 0.005$ RAD PIN NO. 1 IDENT $\overline{(6.35 \pm 0.127)}$ PIN NO. 1 IDENT OPTION 1 1 2 3 $\frac{0.280}{(7.112)}$ MIN 0.040 $\frac{0.030}{(0.762)}$ MAX OPTION 2 (1.016)0.039 0.145 - 0.2000.300 - 0.320(0.991) (3.683 - 5.080)(7.62 - 8.128) $0.130 \pm 0.005$ $(3.302 \pm 0.127)$ 0.125 - 0.140 0.065 (3.175 - 3.556)0.020 0.125 (1.651)0.009 - 0.01590°±4° (0.508)(3.175) DIA (0.229 - 0.381)MIN NOM $0.018 \pm 0.003$ $0.325 \,{}^{+\, 0.040}_{-\, 0.015}$ $(0.457 \pm 0.076)$ $\frac{8.255 + 1.016 - 0.381}{$ $0.100 \pm 0.010$ $(2.540 \pm 0.254)$ $0.045 \pm 0.015$ $\overline{(1.143 \pm 0.381)}$ 0.060 (1.524) 0.050 (1.270)N08E (REV F) 8 Lead MDIP Package **NS Package Number N08E**

### **Notes**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.cor

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560