## LM5009A

# 100V, 150 mA Constant On-Time Buck Switching Regulator

### **General Description**

The LM5009A is a functional variant of the LM5009 COT Buck Switching Regulator. The functional differences of the LM5009A are: The minimum input operating voltage is 6 volts, the on-time equation is slightly different, and the requirement for a minimum load current is removed.

The LM5009A Step Down Switching Regulator features all of the functions needed to implement a low cost, efficient, Buck bias regulator. This high voltage regulator contains an 100 V N-Channel Buck Switch. The device is easy to implement and is provided in the MSOP-8 and the thermally enhanced LLP-8 packages. The regulator is based on a control scheme using an ON time inversely proportional to  $V_{\rm IN}$ . This feature allows the operating frequency to remain relatively constant. The control scheme requires no loop compensation. An intelligent current limit is implemented with forced OFF time, which is inversely proportional to Vout. This scheme ensures short circuit control while providing minimum foldback. Other features include: Thermal Shutdown,  $V_{\rm CC}$  under-voltage lockout, Gate drive under-voltage lockout, Max Duty Cycle limiter, and a pre-charge switch.

### **Features**

- Operating input voltage range: 6V to 95V

- Integrated 100V, N-Channel buck switch

- Internal start-up regulator

- No loop compensation required

- Ultra-Fast transient response

- On time varies inversely with input voltage

- Operating frequency remains constant with varying line voltage and load current

- Adjustable output voltage from 2.5V

- Highly efficient operation

- Precision internal reference

- Low bias current

- Intelligent current limit

- Thermal shutdown

## Typical Applications

- Non-Isolated Telecommunication Buck Regulator

- Secondary High Voltage Post Regulator

- +42V Automotive Systems

## **Package**

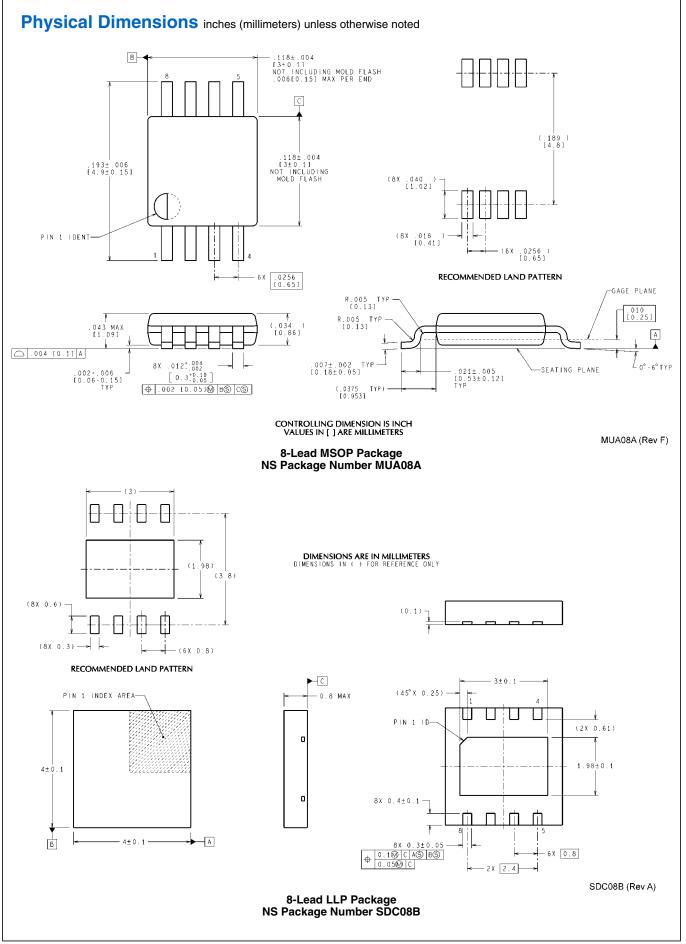

- MSOP 8

- LLP 8 (4mm x 4mm)

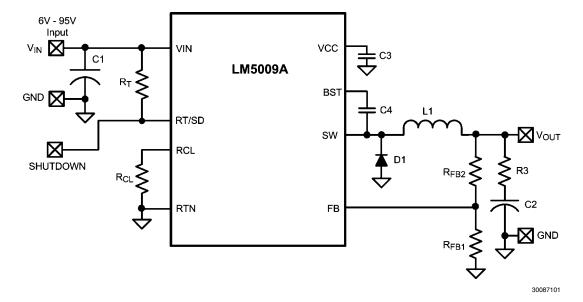

## Typical Application, Basic Step-Down Regulator

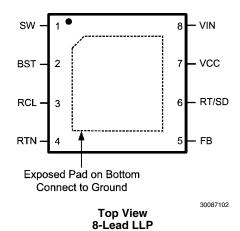

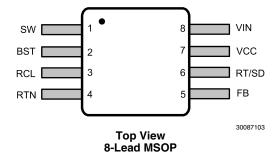

# **Connection Diagrams**

**Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Supplied As                 |

|--------------|--------------|---------------------|-----------------------------|

| LM5009AMM    | MSOP-8       | MUA08A              | 1000 Units on Tape and Reel |

| LM5009AMMX   | WISOF-0      | MUAUSA              | 3500 Units on Tape and Reel |

| LM5009ASDC   | LLDO         | SDC08B              | 1000 Units on Tape and Reel |

| LM5009ASDCX  | LLP-8        | 2DC00B              | 4500 Units on Tape and Reel |

# **Pin Descriptions**

| Pin | Name  | Description                                                  | Application Information                                                                                                                                                                                          |  |  |

|-----|-------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | SW    | Switching Node                                               | Power switching node. Connect to the output inductor, re-circulating dio and bootstrap capacitor.                                                                                                                |  |  |

| 2   | BST   | Boost Pin (Boot–strap capacitor input)                       | An external capacitor is required between the BST and the SW pins. A 0.01 $\mu\text{F}$ ceramic capacitor is recommended. An internal diode charges the capacitor from $V_{\text{CC}}$ during each off-time.     |  |  |

| 3   | RCL   | Current Limit OFF time set pin                               | A resistor between this pin and RTN sets the off-time when current limit is detected. The off-time is preset to 35 $\mu$ s if FB = 0V.                                                                           |  |  |

| 4   | RTN   | Ground pin                                                   | Ground for the entire circuit.                                                                                                                                                                                   |  |  |

| 5   | FB    | Feedback input from Regulated Output                         | This pin is connected to the inverting input of the internal regulation comparator. The regulation threshold is 2.5V.                                                                                            |  |  |

| 6   | RT/SD | On time set pin                                              | A resistor between this pin and VIN sets the switch on time as a function of $V_{\text{IN}}$ . The minimum recommended on time is 400 ns at the maximum input voltage. This pin can be used for remote shutdown. |  |  |

| 7   | VCC   | Output from the internal high voltage series pass regulator. |                                                                                                                                                                                                                  |  |  |

| 8   | VIN   | Input voltage                                                | Input operating range: 6V to 95V.                                                                                                                                                                                |  |  |

|     | EP    | Exposed Pad                                                  | The exposed pad has no electrical contact. Connect to system ground plane for reduced thermal resistance.                                                                                                        |  |  |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$\begin{array}{ccc} V_{\text{IN}} \text{ to GND} & -0.3 \text{V to } 100 \text{V} \\ \text{BST to GND} & -0.3 \text{V to } 114 \text{V} \\ \text{SW to GND (Steady State)} & -1 \text{V} \\ \text{ESD Rating (Note 5)} & & & \\ \text{Human Body Model} & 2 \text{kV} \\ \text{BST to V}_{\text{CC}} & & 100 \text{V} \\ \end{array}$

BST to SW 14V  $V_{CC}$  to GND 14V All Other Inputs to GND -0.3 to 7V Lead Temperature (Soldering 4 sec) 260°C Storage Temperature Range -55°C to +150°C

## **Operating Ratings** (Note 1)

$V_{IN}$  6V to 95V Operating Junction Temperature  $-40^{\circ}\text{C}$  to + 125 $^{\circ}\text{C}$

**Electrical Characteristics** Specifications with standard typeface are for  $T_J = 25^{\circ}$ C, and those with **boldface** type apply over full **Operating Junction Temperature range**.  $V_{IN} = 48V$ , unless otherwise stated (Note 3).

| Symbol      | Parameter                   | Conditions                                              | Min  | Тур  | Max  | Units |

|-------------|-----------------------------|---------------------------------------------------------|------|------|------|-------|

| VCC Supply  |                             |                                                         |      | -    | -    | *     |

| √cc Reg     | Vcc Regulator Output        | Vin = 48V                                               | 6.6  | 7    | 7.4  | V     |

|             | Vin – Vcc                   | 6V < Vin < 8.5V                                         |      | 100  |      | mV    |

|             | Vcc Bypass Threshold        | Vin Increasing                                          |      | 8.5  |      | V     |

|             | Vcc Bypass Hysteresis       |                                                         |      | 300  |      | mV    |

|             | Vcc Output Impedance        | Vin =6V                                                 |      | 100  |      | Ω     |

|             |                             | Vin = 10V                                               |      | 8.8  |      | Ω     |

|             |                             | Vin = 48V                                               |      | 0.8  |      | Ω     |

|             | Vcc Current Limit           | Vin = 48V                                               |      | 9.2  |      | mA    |

|             | Vcc UVLO                    | Vcc Increasing                                          |      | 5.3  |      | V     |

|             | Vcc UVLO hysteresis         |                                                         |      | 190  |      | mV    |

|             | Vcc UVLO filter delay       |                                                         |      | 3    |      | μs    |

|             | lin Operating current       | FB = 3V, Vin = 48V                                      |      | 550  | 750  | μΑ    |

|             | lin Shutdown Current        | RT/SD = 0V                                              |      | 110  | 176  | μΑ    |

| witch Char  | acteristics                 | · · · · · · · · · · · · · · · · · · ·                   |      |      |      | •     |

|             | Buckswitch Rds(on)          | Itest = 200 mA                                          |      | 2.2  | 4.6  | Ω     |

|             | Gate Drive UVLO             | Vbst – Vsw Rising                                       | 2.8  | 3.8  | 4.8  | V     |

|             | Gate Drive UVLO hysteresis  |                                                         |      | 490  |      | mV    |

|             | Pre-charge switch voltage   | At 1 mA                                                 |      | 0.8  |      | V     |

|             | Pre-charge switch on-time   |                                                         |      | 150  |      | ns    |

| urrent Limi | it                          |                                                         |      | ,    |      | ,     |

|             | Current Limit Threshold     |                                                         | 0.24 | 0.3  | 0.36 | А     |

|             | Current Limit Response Time | I <sub>switch</sub> Overdrive = 0.1A Time to Switch Off |      | 350  |      | ns    |

| OFF-1       | OFF time generator          | FB=0V, R <sub>CL</sub> = 100K                           |      | 35   |      | μs    |

| OFF-2       | OFF time generator          | FB=2.3V, R <sub>CL</sub> = 100K                         |      | 2.56 |      | μs    |

| On Time Ge  | nerator                     | <del>'</del>                                            |      | ļ.   | •    |       |

|             | T <sub>ON</sub> - 1         | Vin = 10V<br>Ron = 200K                                 | 2.15 | 2.77 | 3.5  | μs    |

|             | T <sub>ON</sub> - 2         | Vin = 95V<br>Ron = 200K                                 | 200  | 300  | 420  | ns    |

|             | Remote Shutdown Threshold   | Rising                                                  | 0.40 | 0.70 | 1.05 | V     |

|             | Remote Shutdown Hysteresis  |                                                         |      | 35   |      | mV    |

| Symbol        | Parameter                   | Conditions                                  | Min   | Тур   | Max   | Units |

|---------------|-----------------------------|---------------------------------------------|-------|-------|-------|-------|

| Minimum O     | ff Time                     | •                                           | •     | ,     |       |       |

|               | Minimum Off Timer           | FB = 0V                                     |       | 300   |       | ns    |

| Regulation    | and OV Comparators          |                                             | •     |       |       |       |

|               | FB Reference Threshold      | Internal reference Trip point for switch ON | 2.445 | 2.5   | 2.550 | V     |

|               | FB Over-Voltage Threshold   | Trip point for switch OFF                   |       | 2.875 |       | V     |

|               | FB Bias Current             |                                             |       | 100   |       | nA    |

| Thermal Sh    | utdown                      | •                                           |       | ,     |       |       |

| Tsd           | Thermal Shutdown Temp.      |                                             |       | 165   |       | °C    |

|               | Thermal Shutdown Hysteresis |                                             |       | 25    |       | °C    |

| Thermal Re    | sistance                    | •                                           |       | ,     |       | •     |

| $\theta_{JA}$ | Junction to Ambient         | MUA Package                                 |       | 200   |       | °C/W  |

|               |                             | SDC Package                                 |       | 40    |       | °C/W  |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: For detailed information on soldering plastic MSOP and LLP packages, refer to the Packaging Data Book available from National Semiconductor Corporation.

**Note 3:** All limits are guaranteed. All electrical characteristics having room temperature limits are tested during production with  $T_A = T_J = 25^{\circ}$ C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Note 4: The V<sub>CC</sub> output is intended as a self bias for the internal gate drive power and control circuits. Device thermal limitations limit external loading.

Note 5: The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. The ESD rating for pin 2, pin 7, and pin 8 is 1 kV for HBM and 150V for MM.

Note 6: For devices procured in the LLP-8 package the Rds(on) limits are guaranteed by design characterization data only.

# **Typical Performance Characteristics**

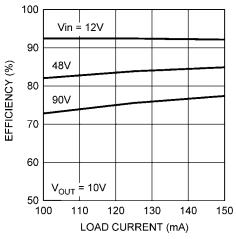

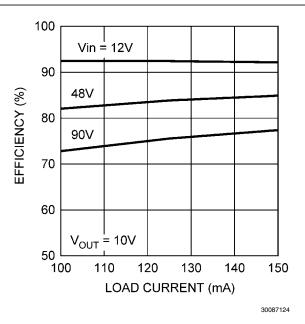

#### Efficiency vs. Load Current and V<sub>IN</sub> (Circuit of Figure 4)

#### 30087124

30087126

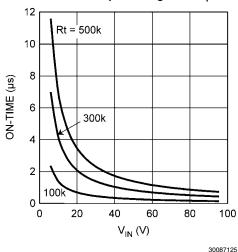

### ON-Time vs Input Voltage and R<sub>T</sub>

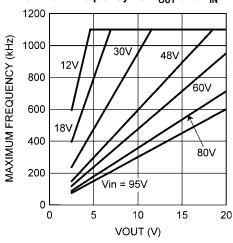

### Maximum Frequency vs. $\mathbf{V}_{\mathrm{OUT}}$ and $\mathbf{V}_{\mathrm{IN}}$

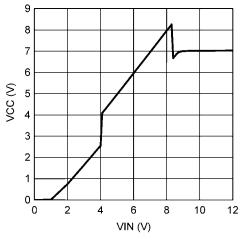

### VCC vs. VIN 9

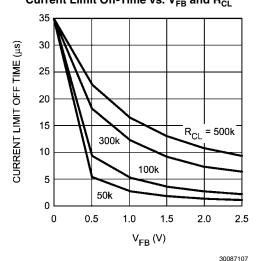

## Current Limit Off-Time vs. $\rm V_{FB}$ and $\rm R_{CL}$

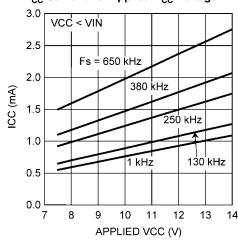

### $\rm I_{CC}$ Current vs. Applied $\rm V_{CC}$ Voltage

30087127

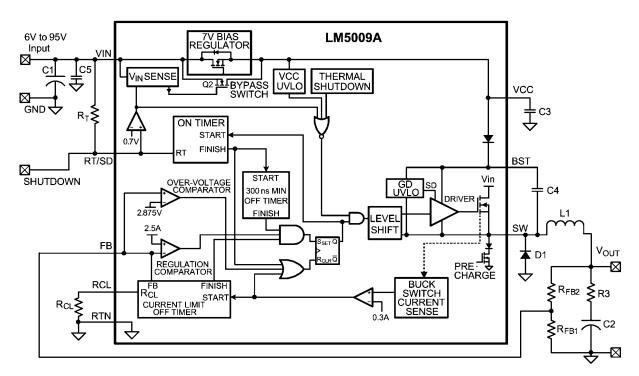

### **Block Diagram**

30087110

## **Functional Description**

The LM5009A Step Down Switching Regulator features all the functions needed to implement a low cost, efficient, Buck bias power converter. This high voltage regulator contains a 100 V N-Channel Buck Switch, is easy to implement and is provided in the MSOP-8 and the thermally enhanced LLP-8 packages. The regulator is based on a control scheme using an on-time inversely proportional to  $\rm V_{IN}$ . The control scheme requires no loop compensation. Current limit is implemented with forced off-time, which is inversely proportional to  $\rm V_{OUT}$ . This scheme ensures short circuit control while providing minimum foldback.

The LM5009A can be applied in numerous applications to efficiently regulate down higher voltages. This regulator is well suited for 48 Volt Telecom and the new 42V Automotive power bus ranges. Features include: Thermal Shutdown,  $V_{\rm CC}$  under-voltage lockout, Gate drive under-voltage lockout, Max Duty Cycle limit timer, intelligent current limit off timer, and a pre-charge switch.

#### **Control Circuit Overview**

The LM5009A is a Buck DC-DC regulator that uses a control scheme in which the on-time varies inversely with line voltage ( $V_{\text{IN}}$ ). Control is based on a comparator and the on-time one-shot, with the output voltage feedback (FB) compared to an internal reference (2.5V). If the FB level is below the reference the buck switch is turned on for a fixed time determined by the line voltage and a programming resistor ( $R_{\text{T}}$ ). Following the ON period the switch will remain off for at least the minimum off-timer period of 300ns. If FB is still below the reference at that time the switch will turn on again for another on-time period. This will continue until regulation is achieved.

The LM5009A operates in discontinuous conduction mode at light load currents, and continuous conduction mode at heavy load current. In discontinuous conduction mode, current through the output inductor starts at zero and ramps up to a peak during the on-time, then ramps back to zero before the end of the off-time. The next on-time period starts when the voltage at FB falls below the internal reference - until then the inductor current remains zero. In this mode the operating frequency is lower than in continuous conduction mode, and varies with load current. Therefore at light loads the conversion efficiency is maintained, since the switching losses reduce with the reduction in load and frequency. The discontinuous operating frequency can be calculated as follows:

$$F = \frac{V_{OUT}^2 x L x 1.04 x 10^{20}}{R_L x (R_T)^2}$$

where  $R_L$  = the load resistance

In continuous conduction mode, current flows continuously through the inductor and never ramps down to zero. In this mode the operating frequency is greater than the discontinuous mode frequency and remains relatively constant with load and line variations. The approximate continuous mode operating frequency can be calculated as follows:

$$F = \frac{V_{OUT}}{1.385 \times 10^{-10} \times R_{T}}$$

(1)

The output voltage ( $V_{OUT}$ ) is programmed by two external resistors as shown in the Block Diagram. The regulation point can be calculated as follows:

$$V_{OUT} = 2.5 x (R_{FB1} + R_{FB2}) / R_{FB1}$$

The LM5009A regulates the output voltage based on ripple voltage at the feedback input, requiring a minimum amount of ESR for the output capacitor C2. A minimum of 25mV to 50mV of ripple voltage at the feedback pin (FB) is required for the LM5009A. In cases where the capacitor ESR is too small, additional series resistance may be required (R3 in the Block Diagram).

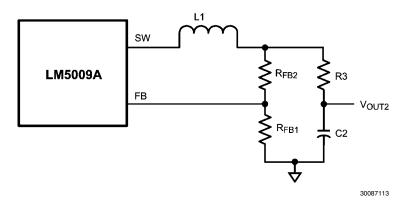

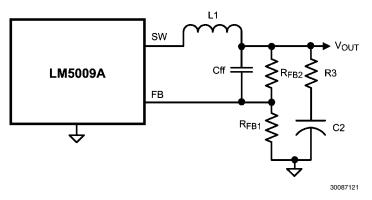

For applications where lower output voltage ripple is required the output can be taken directly from a low ESR output capacitor, as shown in *Figure 1*. However, R3 slightly degrades the load regulation.

FIGURE 1. Low Ripple Output Configuration

## **Start-Up Regulator (V<sub>CC</sub>)**

The high voltage bias regulator is integrated within the LM5009A. The input pin (VIN) can be connected directly to line voltages between 6V and 95V, with transient capability to 100V. Referring to the block diagram and the graph of  $V_{\rm CC}$  vs  $V_{\rm IN}$ , when  $V_{\rm IN}$  is between 6V and the bypass threshold (nominally 8.5V), the bypass switch (Q2) is on, and  $V_{\rm CC}$  tracks  $V_{\rm IN}$  within 100 mV to 150 mV. The bypass switch on-resistance is approximately 100 mA. When  $V_{\rm IN}$  is above the bypass threshold Q2 is turned off, and  $V_{\rm CC}$  is regulated at 7V. The  $V_{\rm CC}$  regulator output current is limited at approximately 9.2 mA. When the LM5009A is shutdown using the RT/SD pin, the  $V_{\rm CC}$  bypass switch is shut off regardless of the voltage at  $V_{\rm IN}$ .

When VIN exceeds the bypass threshold, the time required for Q2 to shut off is approximately 2 - 3  $\mu$ s. The capacitor at VCC (C3) must be a minimum of 0.47  $\mu$ F to prevent the voltage at VCC from rising above its absolute maximum rating in

response to a step input applied at V $_{\rm IN}$ . C3 must be located as close as possible to the VCC and RTN pins. In applications with a relatively high input voltage, power dissipation in the bias regulator is a concern. An auxiliary voltage of between 7.5V and 14V can be diode connected to the VCC pin to shut off the V $_{\rm CC}$  regulator, thereby reducing internal power dissipation. The current required into the VCC pin is shown in the graph "I $_{\rm CC}$  Current vs. Applied V $_{\rm CC}$  Voltage". Internally a diode connects VCC to VIN requiring that the auxiliary voltage be less than V $_{\rm IN}$ .

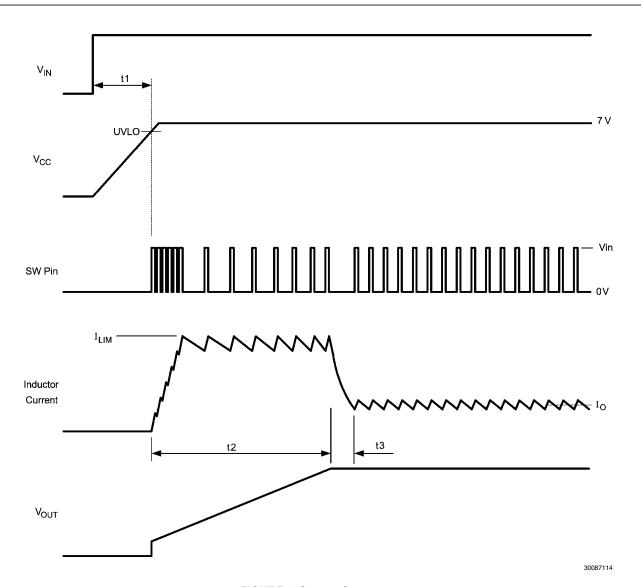

The turn-on sequence is shown in Figure 2. During the initial delay (t1) VCC ramps up at a rate determined by its current limit and C3 while internal circuitry stabilizes. When  $V_{\rm CC}$  reaches the upper threshold of its under-voltage lock-out (UV-LO, typically 5.3V) the buckswitch is enabled. The inductor current increases to the current limit threshold (I $_{\rm LIM}$ ) and during t2  $V_{\rm OUT}$  increases as the output capacitor charges up. When  $V_{\rm OUT}$  reaches the intended voltage the average inductor current decreases (t3) to the nominal load current (I $_{\rm O}$ ).

FIGURE 2. Startup Sequence

## **Regulation Comparator**

The feedback voltage at FB is compared to an internal 2.5V reference. In normal operation (the output voltage is regulated), an on-time period is initiated when the voltage at FB falls below 2.5V. The buck switch will stay on for the on-time, causing the FB voltage to rise above 2.5V. After the on-time period, the buck switch will stay off until the FB voltage again falls below 2.5V. During start-up, the FB voltage will be below 2.5V at the end of each on-time, resulting in the minimum off-time of 300 ns. Bias current at the FB pin is nominally 100 nA.

## **Over-Voltage Comparator**

The feedback voltage at FB is compared to an internal 2.875V reference. If the voltage at FB rises above 2.875V the on-time pulse is immediately terminated. This condition can occur if the input voltage, or the output load, change suddenly. The buck switch will not turn on again until the voltage at FB falls below 2.5V.

## **On-Time Generator and Shutdown**

The on-time for the LM5009A is determined by the  $\rm R_T$  resistor, and is inversely proportional to the input voltage (Vin), resulting in a nearly constant frequency as Vin is varied over its range. The on-time equation for the LM5009A is:

$$T_{ON} = 1.385 \times 10^{-10} \times R_T / V_{IN}$$

(2)

$\rm R_T$  should be selected for a minimum on-time (at maximum  $\rm V_{IN})$  greater than 400 ns, for proper current limit operation. This requirement limits the maximum frequency for each application, depending on  $\rm V_{IN}$  and  $\rm V_{OLIT}$ .

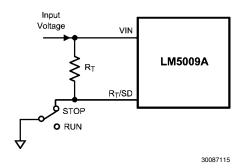

The LM5009A can be remotely disabled by taking the  $\rm R_T/SD$  pin to ground. See *Figure 3*. The voltage at the  $\rm R_T/SD$  pin is between 1.5 and 3.0 volts, depending on Vin and the value of the  $\rm R_T$  resistor.

FIGURE 3. Shutdown Implementation

### **Current Limit**

The LM5009A contains an intelligent current limit OFF timer. If the current in the Buck switch exceeds 0.3A the present cycle is immediately terminated, and a non-resetable OFF timer is initiated. The length of off-time is controlled by an external resistor ( $R_{\rm CL}$ ) and the FB voltage (see the graph Current Limit Off-Time vs.  $V_{\rm FB}$  and  $R_{\rm CL}$ ). When FB = 0V, a maximum off-time is required, and the time is preset to 35µs. This condition occurs when the output is shorted, and during the initial part of start-up. This amount of time ensures safe short circuit operation up to the maximum input voltage of 95V. In cases of overload where the FB voltage is above zero volts (not a short circuit) the current limit off-time will be less than 35µs. Reducing the off-time during less severe overloads reduces the amount of foldback, recovery time, and the start-up time. The off-time is calculated from the following equation:

$$T_{OFF} = 10^{-5} / (0.285 + (V_{FB} / 6.35 \times 10^{-6} \times R_{CL}))$$

(3)

The current limit sensing circuit is blanked for the first 50-70ns of each on-time so it is not falsely tripped by the current surge which occurs at turn-on. The current surge is required by the re-circulating diode (D1) for its turn-off recovery.

#### N - Channel Buck Switch and Driver

The LM5009A integrates an N-Channel Buck switch and associated floating high voltage gate driver. The gate driver circuit works in conjunction with an external bootstrap capacitor and an internal high voltage diode. A 0.01 µF ceramic capacitor (C4) connected between the BST pin and SW pin provides the voltage to the driver during the on-time.

During each off-time, the SW pin is at approximately 0V, and the bootstrap capacitor charges from Vcc through the internal diode. The minimum OFF timer, set to 300ns, ensures a minimum time each cycle to recharge the bootstrap capacitor.

The internal pre-charge switch at the SW pin is turned on for ≊150 ns during the minimum off-time period, ensuring sufficient voltage exists across the bootstrap capacitor for the ontime. This feature helps prevent operating problems which can occur during very light load conditions, involving a long off-time, during which the voltage across the bootstrap capacitor could otherwise reduce below the Gate Drive UVLO threshold. The pre-charge switch also helps prevent startup problems which can occur if the output voltage is pre-charged prior to turn-on. After current limit detection, the pre-charge switch is turned on for the entire duration of the forced off-time.

#### **Thermal Protection**

The LM5009A should be operated so the junction temperature does not exceed 125°C during normal operation. An internal Thermal Shutdown circuit is provided to shutdown the LM5009A in the event of a higher than normal junction temperature. When activated, typically at 165°C, the controller is forced into a low power reset state by disabling the buck switch. This feature prevents catastrophic failures from accidental device overheating. When the junction temperature reduces below 140°C (typical hysteresis = 25°C) normal operation is resumed.

### **Applications Information**

#### **SELECTION OF EXTERNAL COMPONENTS**

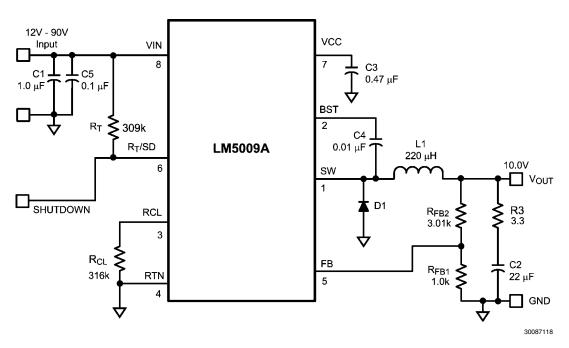

A guide for determining the component values will be illustrated with a design example. Refer to the Block Diagram. The following steps will configure the LM5009A for:

- · Input voltage range (Vin): 12V to 90V

- Output voltage (V<sub>OUT1</sub>): 10V

- Load current (for continuous conduction mode): 100 mA to 150 mA

$\textbf{R}_{\text{FB1}},~\textbf{R}_{\text{FB2}};~\textbf{V}_{\text{OUT}}=\textbf{V}_{\text{FB}}$  x  $(\textbf{R}_{\text{FB1}}+\textbf{R}_{\text{FB2}})$  /  $\textbf{R}_{\text{FB1}},~\text{and since}$   $\textbf{V}_{\text{FB}}=2.5\text{V},~\text{the ratio of }\textbf{R}_{\text{FB2}}$  to  $\textbf{R}_{\text{FB1}}$  calculates as 3:1. Standard values of 3.01  $\text{k}\Omega$  and 1.00  $\text{k}\Omega$  are chosen. Other values could be used as long as the 3:1 ratio is maintained.

${f F_s}$  and  ${f R_T}$ : The recommended operating frequency range for the LM5009A is 50 kHz to 1.1 MHz. Unless the application requires a specific frequency, the choice of frequency is generally a compromise since it affects the size of L1 and C2, and the switching losses. The maximum allowed frequency, based on a minimum on-time of 400 ns, is calculated from:

$$F_{MAX} = V_{OUT} / (V_{INMAX} x 400 ns)$$

For this exercise, Fmax = 277 kHz. From equation 1,  $R_T$  calculates to 260  $k\Omega.$  A standard value 309  $k\Omega$  resistor will be used to allow for tolerances in equation 1, resulting in a frequency of 234 kHz.

L1: The main parameter affected by the inductor is the output current ripple amplitude. The choice of inductor value therefore depends on both the minimum and maximum load currents, keeping in mind that the maximum ripple current occurs at maximum Vin.

a) **Minimum load current:** To maintain continuous conduction at minimum lo (100 mA), the ripple amplitude ( $I_{OR}$ ) must be less than 200 mA p-p so the lower peak of the waveform does not reach zero. L1 is calculated using the following equation:

$$L1 = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{I_{OR} \times F_s \times V_{IN}}$$

At Vin = 90V, L1(min) calculates to 190  $\mu$ H. The next larger standard value (220  $\mu$ H) is chosen and with this value I $_{OR}$  calculates to 173 mA p-p at Vin = 90V, and 32 mA p-p at Vin = 12V

b) **Maximum load current:** At a load current of 150 mA, the peak of the ripple waveform must not reach the minimum guaranteed value of the LM5009A's current limit threshold (240 mA). Therefore the ripple amplitude must be less than 180 mA p-p, which is already satisfied in the above calculation. With L1 = 220  $\mu$ H, at maximum Vin and Io, the peak of the ripple will be 236 mA. While L1 must carry this peak cur-

rent without saturating or exceeding its temperature rating, it also must be capable of carrying the maximum guaranteed value of the LM5009A's current limit threshold (360 mA) without saturating, since the current limit is reached during startup.

The DC resistance of the inductor should be as low as possible to minimize its power loss.

**C3:** The capacitor on the  $V_{CC}$  output provides not only noise filtering and stability, but its primary purpose is to prevent false triggering of the  $V_{CC}$  UVLO at the buck switch on/off transitions. C3 should be no smaller than 0.47  $\mu F$ .

**C2**, and **R3**: When selecting the output filter capacitor C2, the items to consider are ripple voltage due to its ESR, ripple voltage due to its capacitance, and the nature of the load.

**ESR and R3:** A low ESR for C2 is generally desirable so as to minimize power losses and heating within the capacitor. However, the regulator requires a minimum amount of ripple voltage at the feedback input for proper loop operation. For the LM5009A the minimum ripple required at pin 5 is 25 mV p-p, requiring a minimum ripple at  $V_{OUT}$  of 100 mV. Since the minimum ripple current (at minimum Vin) is 32 mA p-p, the minimum ESR required at  $V_{OUT}$  is 100 mV/32 mA = 3.12 $\Omega$ . Since quality capacitors for SMPS applications have an ESR considerably less than this, R3 is inserted as shown in the Block Diagram. R3's value, along with C2's ESR, must result in at least 25 mV p-p ripple at pin 5. Generally, R3 will be 0.5 to 4.0 $\Omega$ .

**R**<sub>CL</sub>: When current limit is detected, the minimum off-time set by this resistor must be greater than the maximum normal off-time, which occurs at maximum input voltage. Using Equation 2, the minimum on-time is 476 ns, yielding an off-time of 3.8 μs (at 234 kHz). Due to the 25% tolerance on the on-time, the off-time tolerance is also 25%, yielding a maximum off-time of 4.75 μs. Allowing for the response time of the current limit detection circuit (350 ns) increases the maximum off-time to 5.1 μs. This is increased an additional 25% to 6.4 μs to allow for the tolerances of Equation 3. Using Equation 3, R<sub>CL</sub> calculates to 310 kΩ at V<sub>FB</sub> = 2.5V. A standard value 316 kΩ resistor will be used.

D1: The important parameters are reverse recovery time and forward voltage. The reverse recovery time determines how long the reverse current surge lasts each time the buck switch is turned on. The forward voltage drop is significant in the event the output is short-circuited as it is only this diode's voltage which forces the inductor current to reduce during the forced off-time. For this reason, a higher voltage is better, although that affects efficiency. A good choice is a Schottky power diode, such as the DFLS1100. D1's reverse voltage rating must be at least as great as the maximum Vin, and its current rating be greater than the maximum current limit threshold (360 mA).

C1: This capacitor's purpose is to supply most of the switch current during the on-time, and limit the voltage ripple at Vin, on the assumption that the voltage source feeding Vin has an output impedance greater than zero. At maximum load current, when the buck switch turns on, the current into pin 8 will suddenly increase to the lower peak of the output current waveform, ramp up to the peak value, then drop to zero at

turn-off. The average input current during this on-time is the load current (150 mA). For a worst case calculation, C1 must supply this average load current during the maximum on-time. To keep the input voltage ripple to less than 2V (for this exercise), C1 calculates to:

C1 =

$$\frac{1 \times t_{ON}}{\Delta V} = \frac{0.15A \times 3.57 \ \mu s}{2.0V} = 0.268 \ \mu F$$

Quality ceramic capacitors in this value have a low ESR which adds only a few millivolts to the ripple. It is the capacitance which is dominant in this case. To allow for the capacitor's tolerance, temperature effects, and voltage effects, a 1.0  $\mu F,$  100V, X7R capacitor will be used.

C4: The recommended value is  $0.01\mu F$  for C4, as this is appropriate in the majority of applications. A high quality ceramic capacitor, with low ESR is recommended as C4 supplies the surge current to charge the buck switch gate at turn-on. A low ESR also ensures a quick recharge during each off-time. At minimum Vin, when the on-time is at maximum, it is possible during start-up that C4 will not fully recharge during each 300 ns off-time. The circuit will not be able to complete the start-up, and achieve output regulation. This can occur when the frequency is intended to be low (e.g.,  $R_T = 500K$ ). In this case C4 should be increased so it can maintain sufficient voltage across the buck switch driver during each on-time.

C5: This capacitor helps avoid supply voltage transients and ringing due to long lead inductance at  $V_{\rm IN}$ . A low ESR,  $0.1\mu F$  ceramic chip capacitor is recommended, located close to the LM5009A.

#### **FINAL CIRCUIT**

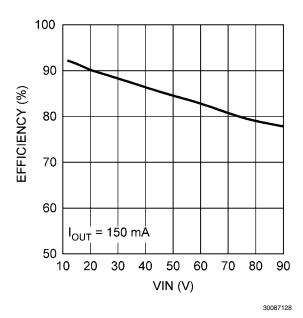

The final circuit is shown in *Figure 4*. The circuit was tested, and the resulting performance is shown in *Figure 5* and *Figure 6*.

#### **PC BOARD LAYOUT**

The LM5009A regulation and over-voltage comparators are very fast, and as such will respond to short duration noise pulses. Layout considerations are therefore critical for optimum performance. The components at pins 1, 2, 3, 5, and 6 should be as physically close as possible to the IC, thereby minimizing noise pickup in the PC tracks. The current loop formed by D1, L1, and C2 should be as small as possible. The ground connection from D1 to C1 should be as short and direct as possible.

If the internal dissipation of the LM5009A produces excessive junction temperatures during normal operation, good use of the pc board's ground plane can help considerably to dissipate heat. The exposed pad on the bottom of the LLP-8 package can be soldered to a ground plane on the PC board, and that plane should extend out from beneath the IC to help dissipate the heat. Additionally, the use of wide PC board traces, where possible, can also help conduct heat away from the IC. Judicious positioning of the PC board within the end product, along with use of any available air flow (forced or natural convection) can help reduce the junction temperatures.

FIGURE 4. LM5009A Example Circuit

## **Bill of Materials**

| Item             | Description          | Part Number                    | Value        |  |

|------------------|----------------------|--------------------------------|--------------|--|

| C1               | Ceramic Capacitor    | TDK C4532X7R2A105M             | 1 μF, 100V   |  |

| C2               | Ceramic Capacitor    | TDK C4532X7R1E226M             | 22 μF, 25V   |  |

| C3               | Ceramic Capacitor    | Kemet C1206C474K5RAC           | 0.47 μF, 50V |  |

| C4               | Ceramic Capacitor    | Kemet C1206C103K5RAC           | 0.01 μF, 50V |  |

| C5               | Ceramic Capacitor    | TDK C3216X7R2A104M             | 0.1 μF, 100V |  |

| D1               | Schottky Power Diode | Diodes Inc. DFLS1100           | 100V, 1A     |  |

| L1               | Power Inductor       | COILTRONICS DR125-221-R, or    | 220 μH       |  |

|                  |                      | TDK SLF10145T-221MR65          |              |  |

| R <sub>FB2</sub> | Resistor             | Vishay CRCW12063011F           | 3.01 kΩ      |  |

| R <sub>FB1</sub> | Resistor             | Vishay CRCW12061001F           | 1.0 kΩ       |  |

| R3               | Resistor             | Vishay CRCW12063R30F           | 3.3 Ω        |  |

| R <sub>T</sub>   | Resistor             | Vishay CRCW12063093F           | 309 kΩ       |  |

| R <sub>CL</sub>  | Resistor             | Vishay CRCW12063163F           | 316 kΩ       |  |

| U1               | Switching Regulator  | National Semiconductor LM5009A |              |  |

FIGURE 5. Efficiency vs. Load Current and V<sub>IN</sub>

FIGURE 6. Efficiency vs. V<sub>IN</sub>

#### LOW OUTPUT RIPPLE CONFIGURATIONS

For applications where low output ripple is required, the following options can be used to reduce or nearly eliminate the ripple.

a) Reduced ripple configuration: In Figure 7, Cff is added across  $\rm R_{FB2}$  to AC-couple the ripple at  $\rm V_{OUT}$  directly to the FB pin. This allows the ripple at  $\rm V_{OUT}$  to be reduced to a minimum of 25 mVp-p by reducing R3, since the ripple at  $\rm V_{OUT}$  is not attenuated by the feedback resistors. The minimum value for Cff is determined from:

$$Cff = \frac{3 \times t_{ON \text{ (max)}}}{(R_{EB1}//R_{EB2})}$$

where  $t_{ON(max)}$  is the maximum on-time, which occurs at  $V_{IN}$   $_{(min)}$ . The next larger standard value capacitor should be used for Cff

FIGURE 7. Reduced Ripple Configuration

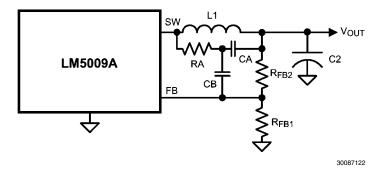

b) Minimum ripple configuration: If the application requires a lower value of ripple (<10 mVp-p), the circuit of *Figure 8* can be used. R3 is removed, and the resulting output ripple voltage is determined by the inductor's ripple current and C2's characteristics. RA and CA are chosen to generate a sawtooth waveform at their junction, and that voltage is AC-coupled to the FB pin via CB. To determine the values for RA, CA and CB, use the following procedure:

Calculate

$$V_A = V_{OUT} - (V_{SW} \times (1 - (V_{OUT}/V_{IN(min)})))$$

where  $V_{SW}$  is the absolute value of the voltage at the SW pin during the off-time (typically 1V). VA is the DC voltage at the RA/CA junction, and is used in the next equation.

- Calculate RA x CA =

$$(V_{IN(min)} - V_A) \times t_{ON}/\Delta V$$

where  $t_{ON}$  is the maximum on-time (at minimum input voltage), and  $\Delta V$  is the desired ripple amplitude at the RA/CA junction (typically 40-50 mV). RA and CA are then chosen from standard value components to satisfy the above product. Typically CA is 1000 pF to 5000 pF, and RA is 10 k $\Omega$  to 300 k $\Omega$ . CB is then chosen large compared to CA, typically 0.1  $\mu$ F.

FIGURE 8. Minimum Output Ripple Using Ripple Injection

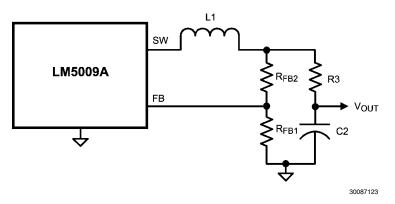

c) Alternate minimum ripple configuration: The circuit in Figure 9 is the same as that in the Block Diagram, except the output voltage is taken from the junction of R3 and C2. The ripple at  $V_{\text{OUT}}$  is determined by the inductor's ripple current

and C2's characteristics. However, R3 slightly degrades the load regulation. This circuit may be suitable if the load current is fairly constant.

FIGURE 9. Alternate Minimum Output Ripple

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com