# QPro Extended Temperature Platform Flash In-System Programmable Configuration PROM

DS541 (v1.0) November 27, 2006

**Product Specification**

#### **Features**

- In-System Programmable PROM for Configuration of Xilinx FPGAs

- Low-Power Advanced CMOS NOR FLASH Process

- Endurance of 20,000 Program/Erase Cycles

- Operation over Full Military Temperature Range (-55°C to +125°C)

- IEEE Standard 1149.1/1532 Boundary-Scan (JTAG)

Support for Programming, Prototyping, and Testing

- JTAG Command Initiation of Standard FPGA Configuration

- Cascadable for Storing Longer or Multiple Bitstreams

- Dedicated Boundary-Scan (JTAG) I/O Power Supply (V<sub>CCJ</sub>)

- I/O Pins Compatible with Voltage Levels Ranging From 1.5V to 3.3V

- Design Support Using the Xilinx Alliance ISE™ and Foundation ISE Series Software Packages

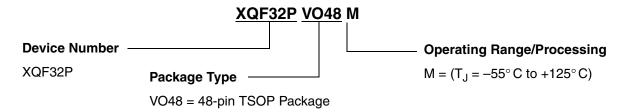

- XQF32P

- 1.8V Supply Voltage

- Serial or Parallel FPGA Configuration Interface (up to 33 MHz)

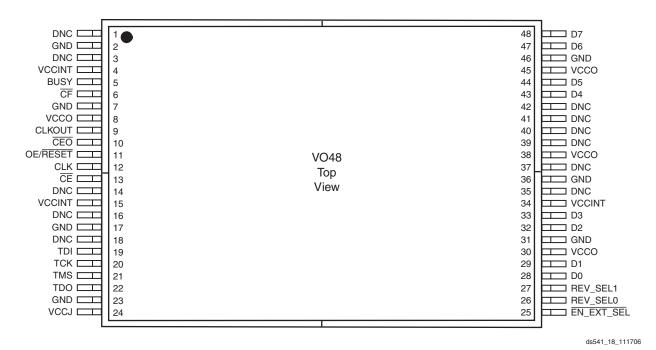

- Available in Small-Footprint VO48 Package

- Design Revision Technology Enables Storing and Accessing Multiple Design Revisions for Configuration

- Built-In Data Decompressor Compatible with Xilinx Advanced Compression Technology

Table 1: Xilinx QPro Platform Flash PROM Features

| Device | Density | V <sub>CCINT</sub> | V <sub>CCO</sub> Range | V <sub>CCJ</sub> Range | Packages | Program<br>In-system<br>via JTAG | Serial<br>Config. | Parallel<br>Config. | Design<br>Revisioning | Compression |

|--------|---------|--------------------|------------------------|------------------------|----------|----------------------------------|-------------------|---------------------|-----------------------|-------------|

| XQF32P | 32 Mbit | 1.8V               | 1.5V - 3.3V            | 2.5V - 3.3V            | VO48     | ✓                                | ✓                 | 1                   | ✓                     | <b>√</b>    |

## **Description**

Xilinx introduces the QPro version of the Platform Flash series of in-system programmable configuration PROMs. Available in 32 Megabit (Mbit) density, this PROM provides an easy-to-use, cost-effective, and reprogrammable method

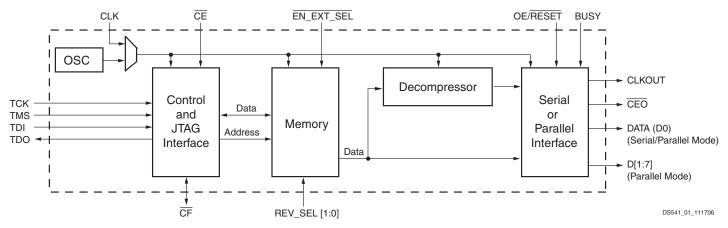

for storing large Xilinx FPGA configuration bitstreams. The 32-Mbit PROM supports Master Serial, Slave Serial, Master SelectMAP, and Slave SelectMAP FPGA configuration modes (Figure 1).

Figure 1: XQF32P Platform Flash PROM Block Diagram

© 2006 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners. All specifications are subject to change without notice.

When the FPGA is in Master Serial mode, it generates a configuration clock that drives the PROM. With  $\overline{\text{CF}}$  High, a short access time after  $\overline{\text{CE}}$  and OE are enabled, data is available on the PROM DATA (D0) pin that is connected to the FPGA DIN pin. New data is available a short access time after each rising clock edge. The FPGA generates the appropriate number of clock pulses to complete the configuration.

When the FPGA is in Slave Serial mode, the PROM and the FPGA are both clocked by an external clock source, or optionally, the PROM can be used to drive the FPGA's configuration clock.

The XQF32P QPro version of the Platform Flash PROM also supports Master SelectMAP and Slave SelectMAP (or Slave Parallel) FPGA configuration modes. When the FPGA is in Master SelectMAP mode, the FPGA generates a configuration clock that drives the PROM. When the FPGA is in Slave SelectMAP Mode, either an external oscillator generates the configuration clock that drives the PROM and the FPGA, or optionally, the XQF32P PROM can be used to drive the FPGA's configuration clock. With BUSY Low and  $\overline{\text{CF}}$  High, after  $\overline{\text{CE}}$  and OE are enabled, data is available on the PROM DATA (D0-D7) pins. New data is available a short access time after each rising clock edge. The data is clocked into the FPGA on the following rising edge of the CCLK. A free-running oscillator can be used in the Slave Parallel /Slave SelecMAP mode.

The XQF32P QPro version of the Platform Flash PROM provides additional advanced features. A built-in data decompressor supports utilizing compressed PROM files, and design revisioning allows multiple design revisions to be stored on a single PROM or stored across several PROMs. For design revisioning, external pins or internal control bits are used to select the active design revision.

Multiple Platform Flash PROM devices can be cascaded to support the larger configuration files required when targeting larger FPGA devices or targeting multiple FPGAs daisy chained together. When utilizing the advanced features for the XQF32P Platform Flash PROM, such as design revisioning, programming files which span cascaded PROM devices can only be created for cascaded chains containing only XQF32P PROMs.

The Platform Flash PROMs are compatible with all of the existing FPGA device families. A reference list of Xilinx FPGAs and the respective compatible Platform Flash PROMs is given in Table 2.

Table 2: Xilinx FPGAs and Compatible Platform Flash PROMs

| FPGA              | Configuration<br>Bitstream | Platform Flash PROM <sup>(1)</sup> |

|-------------------|----------------------------|------------------------------------|

| Virtex™-5 LX F    | amily                      |                                    |

| XC5VLX50          | 12,556,672                 | XCF32P                             |

| XC5VLX330         | 79,704,832                 | XCF32P+XCF32P+XCF32P               |

| Virtex-4 LX Fam   | nily                       |                                    |

| XC4VLX25          | 7,819,904                  | XCF32P                             |

| XC4VLX40          | 12,259,712                 | XCF16P                             |

| XC4VLX200         | 51,367,808                 | XCF32P+XCF32P                      |

| Virtex-4 FX Fam   | nily                       |                                    |

| XC4VFX60          | 21,002,880                 | XCF32P                             |

| XC4VFX140         | 47,856,896                 | XCF32P+XCF32P                      |

| Virtex-4 SX Fam   | nily                       |                                    |

| XC4VSX55          | 22,749,184                 | XCF32P                             |

| Virtex-II Pro Far | nily                       |                                    |

| XC2VP40           | 15,868,192                 | XCF16P                             |

| XC2VP70           | 26,098,976                 | XCF32P                             |

| Virtex-II (2) Fam | ily                        |                                    |

| XC2V2000          | 7,492,000                  | XQF32P                             |

| XC2V3000          | 10,494,368                 | XQF32P                             |

| XC2V6000          | 21,849,504                 | XQF32P                             |

| Virtex-E Family   |                            |                                    |

| XCV600E           | 3,961,632                  | XCF04S                             |

| XCV1000E          | 6,587,520                  | XCF08P                             |

| XCV2000E          | 10,159,648                 | XCF16P                             |

| Virtex Family     |                            |                                    |

| XCV100            | 781,216                    | XCF01S                             |

| XCV300            | 1,751,808                  | XCF02S                             |

| XCV600            | 3,607,968                  | XCF04S                             |

| XCV1000           | 6,127,744                  | XCF08P                             |

| XC2S200           | 1,335,840                  | XCF02S                             |

- 1. Assumes compression used.

- The largest possible Virtex-II bitstream sizes are specified. Refer to the <u>UG002</u>, Virtex-II Platform FPGA User Guide for information on bitgen options which affect bitstream size.

## **Programming**

## **In-System Programming**

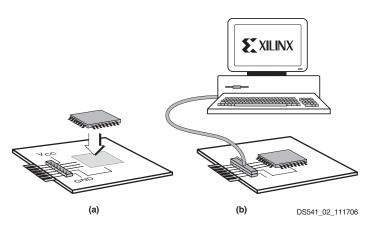

In-System Programmable PROMs can be programmed individually, or two or more can be daisy-chained together and programmed in-system via the standard 4-pin JTAG protocol as shown in Figure 2. In-system programming offers quick and efficient design iterations and eliminates unnecessary package handling or socketing of devices. The programming data sequence is delivered to the device using either Xilinx iMPACT software and a Xilinx download cable, a third-party JTAG development system, a JTAG-compatible board tester, or a simple microprocessor interface that emulates the JTAG instruction sequence. The iMPACT software also outputs serial vector format (SVF) files for use with any tools that accept SVF format, including automatic test equipment. During in-system programming, the CEO output is driven High. All other outputs are held in a high-impedance state or held at clamp levels during in-system programming. In-system programming is fully supported across the recommended operating voltage and temperature ranges.

Figure 2: JTAG In-System Programming Operation

(a) Solder Device to PCB

(b) Program Using Download Cable

### **External Programming**

Xilinx reprogrammable PROMs can also be programmed by the Xilinx MultiPRO Desktop Tool or a third-party device programmer. This provides the added flexibility of using pre-programmed devices with an in-system programmable option for future enhancements and design changes.

### **Reliability and Endurance**

Xilinx in-system programmable products provide a guaranteed endurance level of 20,000 in-system program/erase cycles and a minimum data retention of 20 years. Each device meets all functional, performance, and data retention specifications within this endurance limit.

## **Design Security**

The Xilinx in-system programmable Platform Flash PROM devices incorporate advanced data security features to fully protect the FPGA programming data against unauthorized reading via JTAG. The XQF32P PROMs can also be programmed to prevent inadvertent writing via JTAG. Table 3 shows the security settings available for the XQF32P PROM.

### **Read Protection**

The read protect security bit can be set by the user to prevent the internal programming pattern from being read or copied via JTAG. Read protection does not prevent write operations. For the XQF32P PROM the read protect security bit can be set for individual design revisions, and resetting the read protect bit requires erasing the particular design revision.

#### **Write Protection**

The XQF32P PROM device also allows the user to write protect (or lock) a particular design revision to prevent inadvertent erase or program operations. Once set, the write protect security bit for an individual design revision must be reset (using the UNLOCK command followed by ISC\_ERASE command) before an erase or program operation can be performed.

Table 3: XQF32P Design Revision Data Security Options

| Read Protect    | Write Protect   | Read/Verify<br>Inhibited | Program Inhibited | Erase Inhibited |

|-----------------|-----------------|--------------------------|-------------------|-----------------|

| Reset (default) | Reset (default) | _                        | _                 | -               |

| Reset (default) | Set             | _                        | /                 | ✓               |

| Set             | Reset (default) | 1                        | -                 | _               |

| Set             | Set             | 1                        | ✓                 | ✓               |

## **IEEE 1149.1 Boundary-Scan (JTAG)**

The Platform Flash PROM family is compatible with the IEEE 1149.1 boundary-scan standard and the IEEE 1532 in-system configuration standard. A Test Access Port (TAP) and registers are provided to support all required boundary scan instructions, as well as many of the optional instructions specified by IEEE Std. 1149.1. In addition, the JTAG interface is used to implement in-system programming (ISP) to facilitate configuration, erasure, and verification operations on the Platform Flash PROM device. Table 4, page 4 lists the required and optional boundary-scan instructions supported in the Platform Flash PROMs. Refer to the IEEE Std. 1149.1 specification for a complete description of boundary-scan architecture and the required and optional instructions.

**Caution!** The XQF32P JTAG TAP pause states are not fully compliant with the JTAG 1149.1 specification. If a temporary pause of a JTAG shift operation is required, then stop the JTAG TCK clock and maintain the JTAG TAP within the JTAG Shift-IR or Shift-DR TAP state. Do not transition the XQF32P JTAG TAP through the JTAG Pause-IR or Pause-DR TAP state to temporarily pause a JTAG shift operation.

## **Instruction Register**

The Instruction Register (IR) for the Platform Flash PROM is connected between TDI and TDO during an instruction scan sequence. In preparation for an instruction scan sequence, the instruction register is parallel loaded with a fixed instruction capture pattern. This pattern is shifted out

onto TDO (LSB first), while an instruction is shifted into the instruction register from TDI.

### XQF32P Instruction Register (16 bits wide)

The Instruction Register (IR) for the XQF32P PROM is sixteen bits wide and is connected between TDI and TDO during an instruction scan sequence. The detailed composition of the instruction capture pattern is illustrated in Table 5, page 5.

The instruction capture pattern shifted out of the XQF32P device includes IR[15:0]. IR[15:9] are reserved bits and are set to a logic 0. The ISC Error field, IR[8:7], contains a 10 when an ISC operation is a success; otherwise a 01 when an In-System Configuration (ISC) operation fails. The Erase/Program (ER/PROG) Error field, IR[6:5], contains a 10 when an erase or program operation is a success; otherwise a 01 when an erase or program operation fails. The Erase/Program (ER/PROG) Status field, IR[4], contains a logic 0 when the device is busy performing an erase or programming operation; otherwise, it contains a logic 1. The ISC Status field, IR[3], contains logic 1 if the device is currently in In-System Configuration (ISC) mode; otherwise, it contains logic 0. The DONE field, IR[2], contains logic 1 if the sampled design revision has been successfully programmed; otherwise, a logic 0 indicates incomplete programming. The remaining bits IR[1:0] are set to 01 as defined by IEEE Std. 1149.1.

Table 4: Platform Flash PROM Boundary Scan Instructions

| Boundary-Scan Command                     | XQF32P IR[15:0]<br>(hex) | Instruction Description                                                                                                                                                                                                                            |

|-------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Required Instructions                     |                          |                                                                                                                                                                                                                                                    |

| BYPASS                                    | FFFF                     | Enables BYPASS.                                                                                                                                                                                                                                    |

| SAMPLE/PRELOAD                            | 0001                     | Enables boundary-scan SAMPLE/PRELOAD operation.                                                                                                                                                                                                    |

| EXTEST                                    | 0000                     | Enables boundary-scan EXTEST operation.                                                                                                                                                                                                            |

| Optional Instructions                     |                          |                                                                                                                                                                                                                                                    |

| CLAMP                                     | 00FA                     | Enables boundary-scan CLAMP operation.                                                                                                                                                                                                             |

| HIGHZ                                     | 00FC                     | Places all outputs in high-impedance state simultaneously.                                                                                                                                                                                         |

| IDCODE                                    | 00FE                     | Enables shifting out 32-bit IDCODE.                                                                                                                                                                                                                |

| USERCODE                                  | 00FD                     | Enables shifting out 32-bit USERCODE.                                                                                                                                                                                                              |

| Platform Flash PROM Specific Instructions |                          |                                                                                                                                                                                                                                                    |

| CONFIG                                    | OOEE                     | Initiates FPGA configuration by pulsing $\overline{CF}$ pin Low once (for the XQF32P, this command also resets the selected design revision based on either the external REV_SEL[1:0] pins or on the internal design revision selection bits). (1) |

#### Notes:

1. For more information see "Initiating FPGA Configuration," page 11.

Table 5: XQF32P Instruction Capture Values Loaded into IR as part of an Instruction Scan Sequence

|       | IR[15:9] | IR[8:7]   | IR[6:5]          | IR[4]             | IR[3]      | IR[2] | IR[1:0] |       |

|-------|----------|-----------|------------------|-------------------|------------|-------|---------|-------|

| TDI → | Reserved | ISC Error | ER/PROG<br>Error | ER/PROG<br>Status | ISC Status | DONE  | 0 1     | → TDO |

## **Boundary Scan Register**

The boundary-scan register is used to control and observe the state of the device pins during the EXTEST,

SAMPLE/PRELOAD, and CLAMP instructions. Each output pin on the Platform Flash PROM has two register stages which contribute to the boundary-scan register, while each input pin has only one register stage. The bidirectional pins have a total of three register stages which contribute to the boundary-scan register. For each output pin, the register stage nearest to TDI controls and observes the output state, and the second stage closest to TDO controls and observes the High-Z enable state of the output pin. For each input pin, a single register stage controls and observes the input state of the pin. The bidirectional pin combines the three bits, the input stage bit is first, followed by the output enable stage bit is closest to TDO.

See the XQF32P Pin Names and Descriptions Tables in the "Pinouts and Pin Descriptions," page 33 section for the boundary-scan bit order for all connected device pins, or see the appropriate BSDL file for the complete boundary-scan bit order description under the "attribute

BOUNDARY\_REGISTER" section in the BSDL file. The bit assigned to boundary-scan cell 0 is the LSB in the boundary-scan register, and is the register bit closest to TDO.

## **Identification Registers**

### **IDCODE** Register

The IDCODE is a fixed, vendor-assigned value that is used to electrically identify the manufacturer and type of the device being addressed. The IDCODE register is 32 bits wide. The IDCODE register can be shifted out for examination by using the IDCODE instruction. The IDCODE is available to any other system component via JTAG.

The IDCODE register has the following binary format:

vvvv:ffff:ffff:aaaa:aaaa:cccc:cccc:ccc1

#### where

v = the die version number

f = the PROM family code

a = the specific Platform Flash PROM product ID

c = the Xilinx manufacturer's ID

The LSB of the IDCODE register is always read as logic 1 as defined by IEEE Std. 1149.1. The IDCODE register value for the XQ32PPlatform Flash PROM is <v>5059093.

**Note:** The  $<_{\rm U}>$  in the IDCODE field represents the device's revision code (in hex) and can vary.

#### **USERCODE** Register

The USERCODE instruction gives access to a 32-bit user programmable scratch pad typically used to supply information about the device's programmed contents. By using the USERCODE instruction, a user-programmable identification code can be shifted out for examination. This code is loaded into the USERCODE register during programming of the Platform Flash PROM. If the device is blank or was not loaded during programming, the USERCODE register contains FFFFFFFFh.

### **Customer Code Register**

For the XQF32P Platform Flash PROM, in addition to the USERCODE, a unique 32-byte Customer Code can be assigned to each design revision enabled for the PROM. The Customer Code is set during programming, and is typically used to supply information about the design revision contents. A private JTAG instruction is required to read the Customer Code. If the PROM is blank, or the Customer Code for the selected design revision was not loaded during programming, or if the particular design revision is erased, the Customer Code contains all ones.

# Platform Flash PROM TAP Characteristics

The Platform Flash PROM family performs both in-system programming and IEEE 1149.1 boundary-scan (JTAG) testing via a single 4-wire Test Access Port (TAP). This simplifies system designs and allows standard Automatic Test Equipment to perform both functions. The AC characteristics of the Platform Flash PROM TAP are described as follows.

### **TAP Timing**

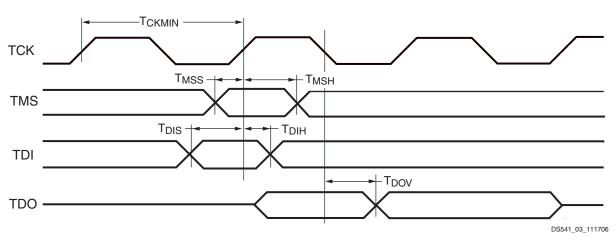

Figure 3, page 6 shows the timing relationships of the TAP signals. These TAP timing characteristics are identical for both boundary-scan and ISP operations.

Figure 3: Test Access Port Timing

#### **TAP AC Parameters**

Table 6 shows the timing parameters for the TAP waveforms shown in Figure 3.

Table 6: Test Access Port Timing Parameters

| Symbol             | Description                                                   | Min | Max | Units |

|--------------------|---------------------------------------------------------------|-----|-----|-------|

| T <sub>CKMIN</sub> | TCK minimum clock period when V <sub>CCJ</sub> = 2.5V or 3.3V | 100 | _   | ns    |

| T <sub>MSS</sub>   | TMS setup time when V <sub>CCJ</sub> = 2.5V or 3.3V           | 10  | _   | ns    |

| T <sub>MSH</sub>   | TMS hold time when V <sub>CCJ</sub> = 2.5V or 3.3V            | 25  | _   | ns    |

| T <sub>DIS</sub>   | TDI setup time when V <sub>CCJ</sub> = 2.5V or 3.3V           | 10  | _   | ns    |

| T <sub>DIH</sub>   | TDI hold time when V <sub>CCJ</sub> = 2.5V or 3.3V            | 25  | _   | ns    |

| T <sub>DOV</sub>   | TDO valid delay when V <sub>CCJ</sub> = 2.5V or 3.3V          | _   | 30  | ns    |

### Additional Features for the XQF32P

#### **Internal Oscillator**

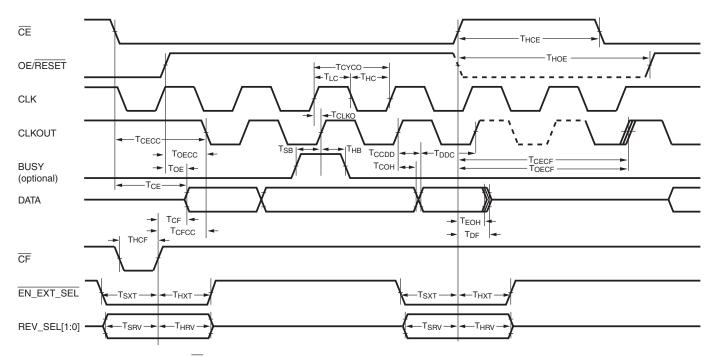

The 32-Mbit XQF32P Platform Flash PROMs include an optional internal oscillator which can be used to drive the CLKOUT and DATA pins on FPGA configuration interface. The internal oscillator can be enabled when programming the PROM, and the oscillator can be set to either the default frequency or to a slower frequency ("XQF32P PROM as Configuration Master with Internal Oscillator as Clock Source," page 30).

#### **CLKOUT**

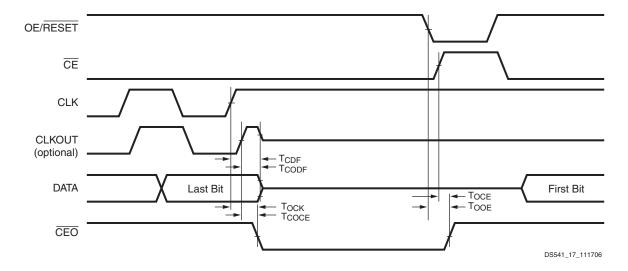

The 32-Mbit XQF32P Platform Flash PROMs include the programmable option to enable the CLKOUT signal which allows the PROM to provide a source synchronous clock aligned to the data on the configuration interface. The CLKOUT signal is derived from one of two clock sources: the CLK input pin or the internal oscillator. The input clock source is selected during the PROM programming sequence. Output data is available on the rising edge of CLKOUT.

The CLKOUT signal is enabled during programming, and is active when  $\overline{\text{CE}}$  is Low and  $\overline{\text{OE}/\text{RESET}}$  is High. On  $\overline{\text{CE}}$  rising edge transition, if  $\overline{\text{OE}/\text{RESET}}$  is High and the PROM terminal count has not been reached, then CLKOUT remains active for an additional eights clock cycles before being disabled. On a  $\overline{\text{OE}/\text{RESET}}$  falling edge transition, CLKOUT is immediately disabled. When disabled, the CLKOUT pin is put into a high-impedance state and should be pulled High externally to provide a known state.

When cascading Platform Flash PROMs with CLKOUT enabled, after completing it's data transfer, the first PROM disables CLKOUT and drives the  $\overline{\text{CEO}}$  pin enabling the next PROM in the PROM chain. The next PROM begins driving the CLKOUT signal once that PROM is enabled and data is available for transfer.

During high-speed parallel configuration without compression, the FPGA drives the BUSY signal on the configuration interface. When BUSY is asserted High, the PROMs internal address counter stops incrementing, and the current data value is held on the data outputs. While BUSY is High, the PROM continues driving the CLKOUT signal to the FPGA, clocking the FPGA's configuration logic.

When the FPGA deasserts BUSY, indicating that it is ready to receive additional configuration data, the PROM begins driving new data onto the configuration interface.

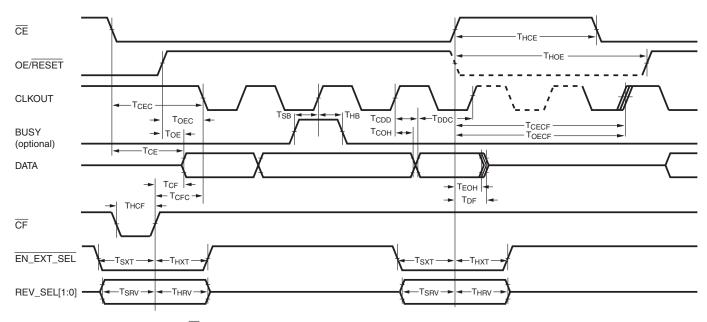

## **Decompression**

The 32-Mbit XQF32P Platform Flash PROMs include a built-in data decompressor compatible with Xilinx advanced compression technology. Compressed Platform Flash PROM files are created from the target FPGA bitstream(s) using the iMPACT software. Only Slave Serial and Slave SelectMAP (parallel) configuration modes are supported for FPGA configuration when using a XQF32P PROM programmed with a compressed bitstream. Compression rates vary depending on several factors, including the target device family and the target design contents.

The decompression option is enabled during the PROM programming sequence. The PROM decompresses the stored data before driving both clock and data onto the FPGA's configuration interface. If Decompression is enabled, then the Platform Flash clock output pin (CLKOUT) must be used as the clock signal for the configuration interface, driving the target FPGA's configuration clock input pin (CCLK). Either the PROM's CLK input pin or the internal oscillator must be selected as the source for CLKOUT. Any target FPGA connected to the PROM must operate as slave in the configuration chain, with the configuration mode set to Slave Serial mode or Slave SelectMap (parallel) mode.

When decompression is enabled, the CLKOUT signal becomes a controlled clock output with a reduced maximum frequency. When decompressed data is not ready, the CLKOUT pin is put into a high-Z state and must be pulled High externally to provide a known state.

The BUSY input is automatically disabled when decompression is enabled.

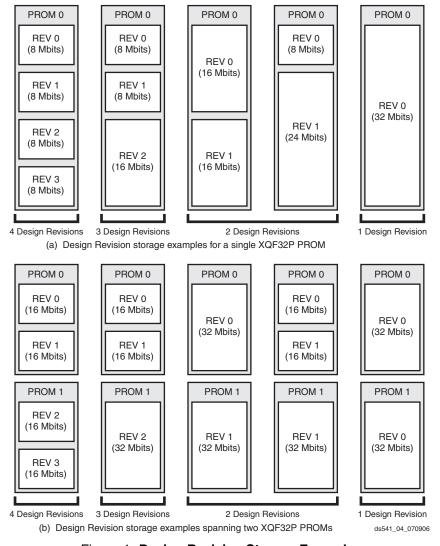

## **Design Revisioning**

Design Revisioning allows the user to create up to four unique design revisions on a single PROM or stored across multiple cascaded PROMs. Design Revisioning is supported for the XQF32P Platform Flash PROM in both serial and parallel modes. Design Revisioning can be used with compressed PROM files, and also when the CLKOUT feature is enabled. The PROM programming files along with the revision information files (.cfi) are created using the iMPACT software. The .cfi file is required to enable design revision programming in iMPACT.

A single design revision is composed of from 1 to n 8-Mbit memory blocks. If a single design revision contains less than 8 Mbits of data, then the remaining space is padded with all ones. A larger design revision can span several

8-Mbit memory blocks, and any space remaining in the last 8-Mbit memory block is padded with all ones.

- A single 32-Mbit PROM contains four 8-Mbit memory blocks, and can therefore store up to four separate design revisions: one 32-Mbit design revision, two 16-Mbit design revisions, three 8-Mbit design revisions, four 8-Mbit design revisions, and so on.

- Because of the 8-Mbit minimum size requirement for each revision, a single 16-Mbit PROM can only store up to two separate design revisions: one 16-Mbit design revision, one 8-Mbit design revision, or two 8-Mbit design revisions.

- A single 8-Mbit PROM can store only one 8-Mbit design revision.

Larger design revisions can be split over several cascaded PROMs. For example, two 32-Mbit PROMs can store up to four separate design revisions: one 64-Mbit design revision, two 32-Mbit design revisions, three 16-Mbit design revisions, four 16-Mbit design revisions, and so on.

See Figure 4, page 8 for a few basic examples of how multiple revisions can be stored. The design revision partitioning is handled automatically during file generation in iMPACT.

During the PROM file creation, each design revision is assigned a revision number:

Revision 0 = '00'

Revision 1 = '01'

Revision 2 = '10'

Revision 3 = '11'

After programming the Platform Flash PROM with a set of design revisions, a particular design revision can be selected using the external REV\_SEL[1:0] pins or using the internal programmable design revision control bits. The EN\_EXT\_SEL pin determines if the external pins or internal bits are used to select the design revision. When EN\_EXT\_SEL is Low, design revision selection is controlled by the external Revision Select pins, REV\_SEL[1:0]. When EN\_EXT\_SEL is High, design revision selection is controlled by the internal programmable Revision Select control bits. During power up, the design revision selection inputs (pins or control bits) are sampled internally. After power up, the design revision selection inputs are sampled again when any of the following events occur:

- On the rising edge of CE

- On the falling edge of OE/RESET (when CE is Low)

- On the rising edge of  $\overline{\mathsf{CF}}$  (when  $\overline{\mathsf{CE}}$  is Low)

- When reconfiguration is initiated by using the JTAG CONFIG instruction.

The data from the selected design revision is then presented on the FPGA configuration interface.

Figure 4: Design Revision Storage Examples

## **PROM to FPGA Configuration Mode and Connections Summary**

The FPGA's I/O, logical functions, and internal interconnections are established by the configuration data contained in the FPGA's bitstream. The bitstream is loaded into the FPGA either automatically upon power up, or on command, depending on the state of the FPGA's mode pins. Xilinx Platform Flash PROMs are designed to download directly to the FPGA configuration interface. FPGA configuration modes which are supported by the XQF32P Platform Flash PROMs include: Master Serial, Slave Serial, Master SelectMAP, and Slave SelectMAP. Below is a short summary of the supported FPGA configuration modes. See the respective FPGA data sheet for device configuration details, including which configuration modes are supported by the targeted FPGA device.

### **FPGA Master Serial Mode**

In Master Serial mode, the FPGA automatically loads the configuration bitstream in bit-serial form from external memory synchronized by the configuration clock (CCLK) generated by the FPGA. Upon power-up or reconfiguration, the FPGA's mode select pins are used to select the Master Serial configuration mode. Master Serial Mode provides a simple configuration interface. Only a serial data line, a clock line, and two control lines (INIT and DONE) are required to configure an FPGA. Data from the PROM is read out sequentially on a single data line (DIN), accessed via the PROM's internal address counter which is incremented on every valid rising edge of CCLK. The serial bitstream data must be set up at the FPGA's DIN input pin a short time before each rising edge of the FPGA's internally generated CCLK signal.

Typically, a wide range of frequencies can be selected for the FPGA's internally generated CCLK which always starts at a slow default frequency. The FPGA's bitstream contains configuration bits which can switch CCLK to a higher frequency for the remainder of the Master Serial configuration sequence. The desired CCLK frequency is selected during bitstream generation.

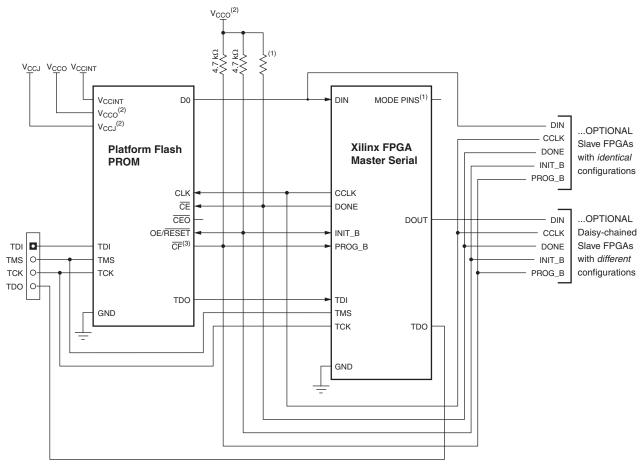

Connecting the FPGA device to the configuration PROM for Master Serial Configuration Mode (Figure 5, page 12):

- The DATA output of the PROM(s) drive the DIN input of the lead FPGA device.

- The Master FPGA CCLK output drives the CLK input(s) of the PROM(s)

- The CEO output of a PROM drives the CE input of the next PROM in a daisy chain (if any).

- The OE/RESET pins of all PROMs are connected to the INIT\_B pins of all FPGA devices. This connection assures that the PROM address counter is reset before the start of any (re)configuration.

- The PROM CE input can be driven from the DONE pin. The CE input of the first (or only) PROM can be driven by the DONE output of all target FPGA devices, provided that DONE is not permanently grounded. CE can also be permanently tied Low, but this keeps the DATA output active and causes an unnecessary I<sub>CC</sub> active supply current ("DC Characteristics Over Operating Conditions," page 24).

- The PROM CF pin is typically connected to the FPGA's PROG\_B (or PROGRAM) input. For the XQF32P only, the CF pin is a bidirectional pin. If the XQF32P CF pin is not connected to the FPGA's PROG\_B (or PROGRAM) input, then the pin should be tied High.

#### **FPGA Slave Serial Mode**

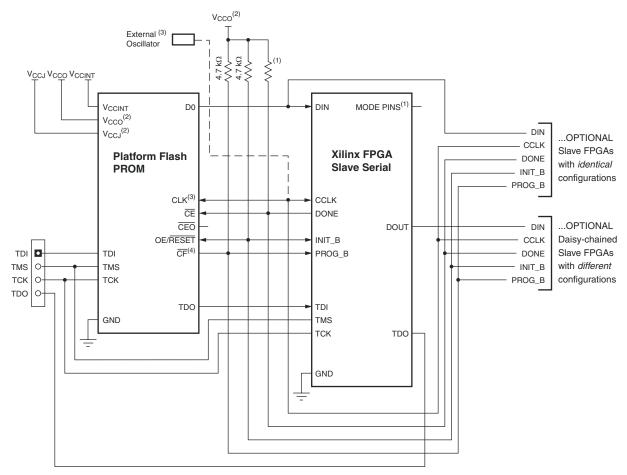

In Slave Serial mode, the FPGA loads the configuration bitstream in bit-serial form from external memory synchronized by an externally supplied clock. Upon power-up or reconfiguration, the FPGA's mode select pins are used to select the Slave Serial configuration mode. Slave Serial Mode provides a simple configuration interface. Only a serial data line, a clock line, and two control lines (INIT and DONE) are required to configure an FPGA. Data from the PROM is read out sequentially on a single data line (DIN), accessed via the PROM's internal address counter which is incremented on every valid rising edge of CCLK. The serial bitstream data must be set up at the FPGA's DIN input pin a short time before each rising edge of the externally provided CCLK.

Connecting the FPGA device to the configuration PROM for Slave Serial Configuration Mode (Figure 6, page 13):

The DATA output of the PROM(s) drive the DIN input of the lead FPGA device.

- The PROM CLKOUT (for XQF32P only) or an external clock source drives the FPGA's CCLK input.

- The CEO output of a PROM drives the CE input of the next PROM in a daisy chain (if any).

- The OE/RESET pins of all PROMs are connected to the INIT\_B (or INIT) pins of all FPGA devices. This connection assures that the PROM address counter is reset before the start of any (re)configuration.

- The PROM CE input can be driven from the DONE pin. The CE input of the first (or only) PROM can be driven by the DONE output of all target FPGA devices, provided that DONE is not permanently grounded. CE can also be permanently tied Low, but this keeps the DATA output active and causes an unnecessary I<sub>CC</sub> active supply current ("DC Characteristics Over Operating Conditions," page 24).

- The PROM CF pin is typically connected to the FPGA's PROG\_B (or PROGRAM) input. For the XQF32P only, the CF pin is a bidirectional pin. If the XQF32P CF pin is not connected to the FPGA's PROG\_B (or PROGRAM) input, then the pin should be tied High.

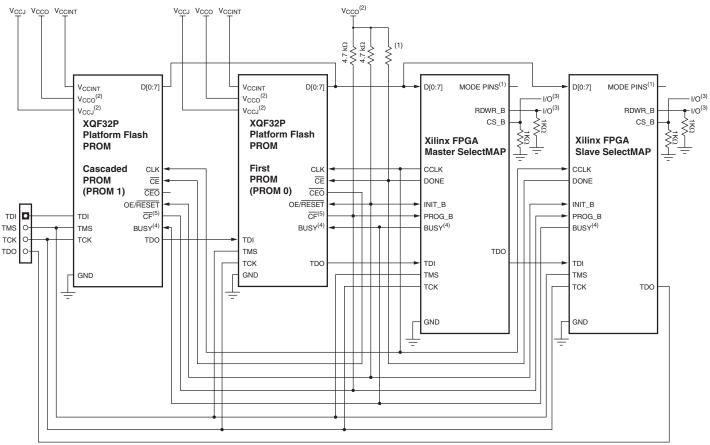

## **Serial Daisy Chain**

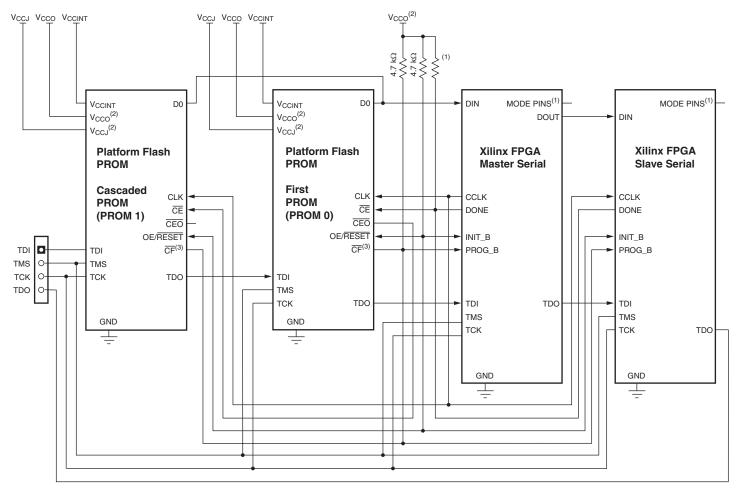

Multiple FPGAs can be daisy-chained for serial configuration from a single source. After a particular FPGA has been configured, the data for the next device is routed internally to the FPGA's DOUT pin. Typically the data on the DOUT pin changes on the falling edge of CCLK, although for some devices the DOUT pin changes on the rising edge of CCLK. Consult the respective device data sheets for detailed information on a particular FPGA device. For clocking the daisy-chained configuration, either the first FPGA in the chain can be set to Master Serial, generating the CCLK, with the remaining devices set to Slave Serial (Figure 7, page 14), or all the FPGA devices can be set to Slave Serial and an externally generated clock can be used to drive the FPGA's configuration interface (Figure 6, page 13 or Figure 11, page 18).

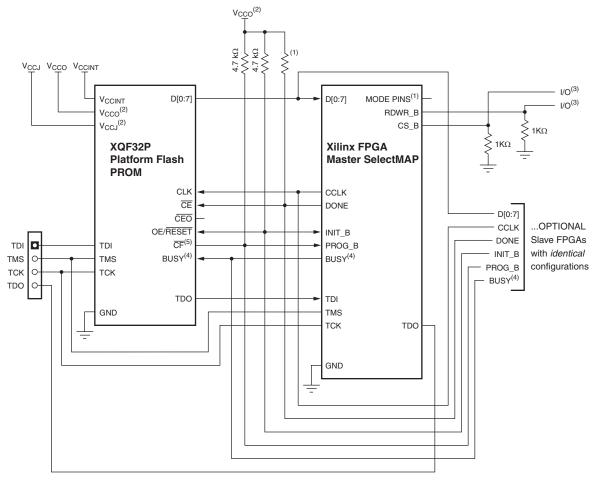

## FPGA Master SelectMAP (Parallel) Mode

In Master SelectMAP mode, byte-wide data is written into the FPGA, typically with a BUSY flag controlling the flow of data, synchronized by the configuration clock (CCLK) generated by the FPGA. Upon power-up or reconfiguration, the FPGA's mode select pins are used to select the Master SelectMAP configuration mode. The configuration interface typically requires a parallel data bus, a clock line, and two control lines (INIT and DONE). In addition, the FPGA's Chip Select, Write, and BUSY pins must be correctly controlled to enable SelectMAP configuration. The configuration data is read from the PROM byte by byte on pins [D0..D7], accessed via the PROM's internal address counter which is incremented on every valid rising edge of CCLK. The bitstream data must be set up at the FPGA's [D0..D7] input

pins a short time before each rising edge of the FPGA's internally generated CCLK signal. If BUSY is asserted (High) by the FPGA, the configuration data must be held until BUSY goes Low. An external data source or external pull-down resistors must be used to enable the FPGA's active Low Chip Select ( $\overline{CS}$  or  $CS_B$ ) and Write ( $\overline{WRITE}$  or RDWR\_B) signals to enable the FPGA's SelectMAP configuration process.

The Master SelectMAP configuration interface is clocked by the FPGA's internal oscillator. Typically, a wide range of frequencies can be selected for the internally generated CCLK which always starts at a slow default frequency. The FPGA's bitstream contains configuration bits which can switch CCLK to a higher frequency for the remainder of the Master SelectMAP configuration sequence. The desired CCLK frequency is selected during bitstream generation.

After configuration, the pins of the SelectMAP port can be used as additional user I/O. Alternatively, the port can be retained using the persist option.

Connecting the FPGA device to the configuration PROM for Master SelectMAP (Parallel) Configuration Mode (Figure 8, page 15):

- The DATA outputs of the PROM(s) drive the [D0..D7] input of the lead FPGA device.

- The Master FPGA CCLK output drives the CLK input(s) of the PROM(s)

- The CEO output of a PROM drives the CE input of the next PROM in a daisy chain (if any).

- The OE/RESET pins of all PROMs are connected to the INIT\_B pins of all FPGA devices. This connection assures that the PROM address counter is reset before the start of any (re)configuration.

- The PROM CE input can be driven from the DONE pin. The CE input of the first (or only) PROM can be driven by the DONE output of all target FPGA devices, provided that DONE is not permanently grounded. CE can also be permanently tied Low, but this keeps the DATA output active and causes an unnecessary I<sub>CC</sub> active supply current ("DC Characteristics Over Operating Conditions," page 24).

- For high-frequency parallel configuration, the BUSY pins of all PROMs are connected to the FPGA's BUSY output. This connection assures that the next data transition for the PROM is delayed until the FPGA is ready for the next configuration data byte.

- The PROM CF pin is typically connected to the FPGA's PROG\_B (or PROGRAM) input. For the XQF32P only, the CF pin is a bidirectional pin. If the XQF32P CF pin is not connected to the FPGA's PROG\_B (or PROGRAM) input, then the pin should be tied High.

### FPGA Slave SelectMAP (Parallel) Mode

In Slave SelectMAP mode, byte-wide data is written into the FPGA, typically with a BUSY flag controlling the flow of data, synchronized by an externally supplied configuration clock (CCLK). Upon power-up or reconfiguration, the FPGA's mode select pins are used to select the Slave SelectMAP configuration mode. The configuration interface typically requires a parallel data bus, a clock line, and two control lines (INIT and DONE). In addition, the FPGA's Chip Select, Write, and BUSY pins must be correctly controlled to enable SelectMAP configuration. The configuration data is read from the PROM byte by byte on pins [D0..D7], accessed via the PROM's internal address counter which is incremented on every valid rising edge of CCLK. The bitstream data must be set up at the FPGA's [D0..D7] input pins a short time before each rising edge of the provided CCLK. If BUSY is asserted (High) by the FPGA, the configuration data must be held until BUSY goes Low. An external data source or external pull-down resistors must be used to enable the FPGA's active Low Chip Select (CS or CS\_B) and Write (WRITE or RDWR B) signals to enable the FPGA's SelectMAP configuration process.

After configuration, the pins of the SelectMAP port can be used as additional user I/O. Alternatively, the port can be retained using the persist option.

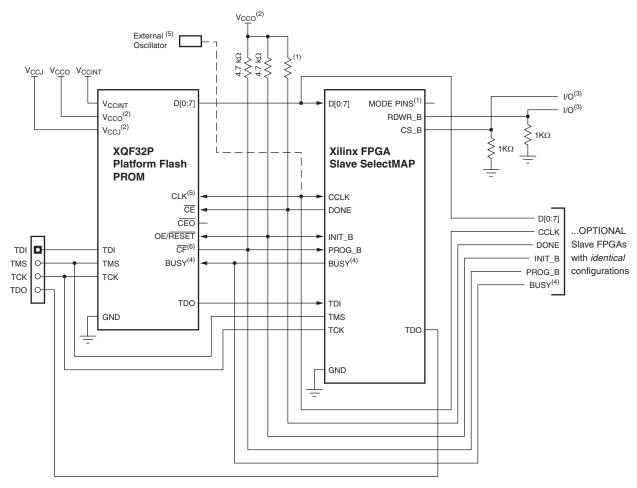

Connecting the FPGA device to the configuration PROM for Slave SelectMAP (Parallel) Configuration Mode (Figure 9, page 16):

- The DATA outputs of the PROM(s) drives the [D0..D7] inputs of the lead FPGA device.

- The PROM CLKOUT (for XQF32P only) or an external clock source drives the FPGA's CCLK input.

- The CEO output of a PROM drives the CE input of the next PROM in a daisy chain (if any).

- The OE/RESET pins of all PROMs are connected to the INIT\_B pins of all FPGA devices. This connection assures that the PROM address counter is reset before the start of any (re)configuration.

- The PROM CE input can be driven from the DONE pin. The CE input of the first (or only) PROM can be driven by the DONE output of all target FPGA devices, provided that DONE is not permanently grounded. CE can also be permanently tied Low, but this keeps the DATA output active and causes an unnecessary I<sub>CC</sub> active supply current ("DC Characteristics Over Operating Conditions," page 24).

- For high-frequency parallel configuration, the BUSY pins of all PROMs are connected to the FPGA's BUSY output. This connection assures that the next data transition for the PROM is delayed until the FPGA is ready for the next configuration data byte.

The PROM CF pin is typically connected to the FPGA's PROG\_B (or PROGRAM) input. For the XQF32P only, the CF pin is a bidirectional pin. If the XQF32P CF pin is not connected to the FPGA's PROG\_B (or PROGRAM) input, then the pin should be tied High.

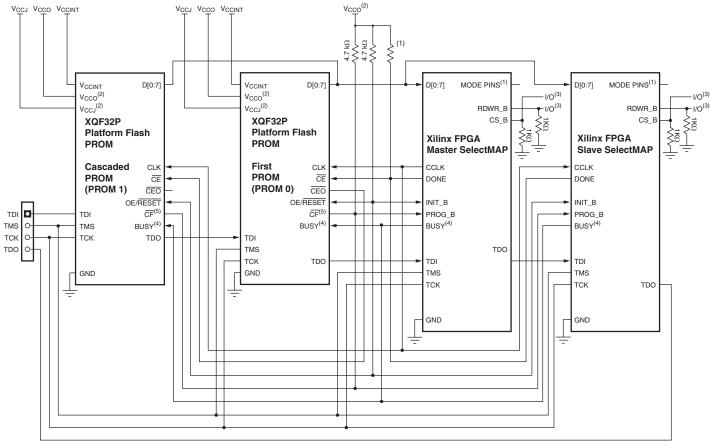

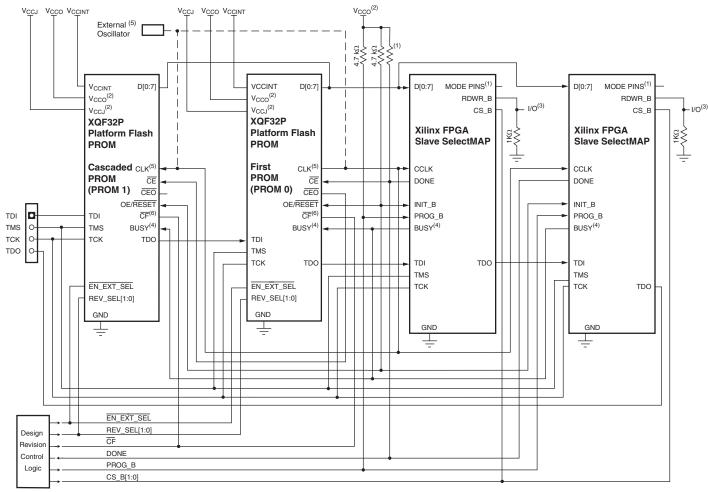

## FPGA SelectMAP (Parallel) Device Chaining

Multiple Virtex-II FPGAs can be configured using the SelectMAP mode, and be made to start up simultaneously. To configure multiple devices in this way, wire the individual CCLK, DONE, INIT, Data ([D0..D7]), Write (WRITE or RDWR\_B), and BUSY pins of all the devices in parallel. If all devices are to be configured with the same bitstream, readback is not being used, and the CCLK frequency selected does not require the use of the BUSY signal, the CS\_B pins can be connected to a common line so all of the devices are configured simultaneously (Figure 9, page 16).

With additional control logic, the individual devices can be loaded separately by asserting the CS\_B pin of each device in turn and then enabling the appropriate configuration data. The PROM can also store the individual bitstreams for each FPGA for SelectMAP configuration in separate design revisions. When design revisioning is utilized, additional control logic can be used to select the appropriate bitstream by asserting the EN\_EXT\_SEL pin, and using the REV\_SEL[1:0] pins to select the required bitstream, while asserting the CS\_B pin for the FPGA the bitstream is targeting (Figure 12, page 19).

For clocking the parallel configuration chain, either the first FPGA in the chain can be set to Master SelectMAP, generating the CCLK, with the remaining devices set to Slave SelectMAP, or all the FPGA devices can be set to Slave SelectMAP and an externally generated clock can be used to drive the configuration interface. Again, the respective device data sheets should be consulted for detailed information on a particular FPGA device, including which configuration modes are supported by the targeted FPGA device.

## **Cascading Configuration PROMs**

When configuring multiple FPGAs in a serial daisy chain, configuring multiple FPGAs in a SelectMAP parallel chain, or configuring a single FPGA requiring a larger configuration bitstream, cascaded PROMs provide additional memory (Figure 7, page 14, Figure 10, page 17, Figure 11, page 18, and Figure 12, page 19). Multiple Platform Flash PROMs can be concatenated by using the  $\overline{\text{CEO}}$  output to drive the  $\overline{\text{CE}}$  input of the downstream device. The clock signal and the data outputs of all Platform Flash PROMs in the chain are interconnected. After the last data

from the first PROM is read, the first PROM asserts its  $\overline{\text{CEO}}$  output Low and drives its outputs to a high-impedance state. The second PROM recognizes the Low level on its  $\overline{\text{CE}}$  input and immediately enables its outputs.

After configuration is complete, address counters of all cascaded PROMs are reset if the PROM OE/RESET pin goes Low or CE goes High.

When utilizing the advanced features for the XQF32P Platform Flash PROM, including the clock output (CLKOUT) option, decompression option, or design revisioning, programming files which span cascaded PROM devices can only be created for cascaded chains containing only XQF32P PROM.

### **Initiating FPGA Configuration**

The options for initiating FPGA configuration via the Platform Flash PROM include:

- Automatic configuration on power up

- Applying an external PROG\_B (or PROGRAM) pulse

- Applying the JTAG CONFIG instruction

Following the FPGA's power-on sequence or the assertion of the PROG\_B (or PROGRAM) pin the FPGA's configuration memory is cleared, the configuration mode is selected, and the FPGA is ready to accept a new configuration bitstream. The FPGA's PROG\_B pin can be controlled by an external source, or alternatively, the Platform Flash PROMs incorporate a  $\overline{\text{CF}}$  pin that can be tied to the FPGA's PROG\_B pin. Executing the CONFIG instruction through JTAG pulses the  $\overline{\text{CF}}$  output Low once for 300-500 ns, resetting the FPGA and initiating configuration. The iMPACT software can issue the JTAG CONFIG command to initiate FPGA configuration by setting the "Load FPGA" option.

When using the XQF32P Platform Flash PROM with design revisioning enabled, the  $\overline{\text{CF}}$  pin should always be connected to the PROG\_B (or  $\overline{\text{PROGRAM}}$ ) pin on the FPGA to ensure that the current design revision selection is sampled when the FPGA is reset. The XQF32P PROM samples the current design revision selection from the external REV\_SEL pins or the internal programmable Revision Select bits on the rising edge of  $\overline{\text{CF}}$ . When the JTAG CONFIG command is executed, the XQF32P samples the new design revision selection before initiating the FPGA configuration sequence. When using the XQF32P Platform Flash PROM without design revisioning, if the  $\overline{\text{CF}}$  pin is not connected to the FPGA PROG\_B (or  $\overline{\text{PROGRAM}}$ ) pin, then the XQF32P  $\overline{\text{CF}}$  pin must be tied High.

## **Configuration PROM to FPGA Device Interface Connection Diagrams**

Notes:

- 1 For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2 For compatible voltages, refer to the appropriate data sheet.

- 3 For the XQF32P the  $\overline{\text{CF}}$  pin is a bidirectional pin, and if  $\overline{\text{CF}}$  is not connected to PROGB, then it must be tied to V<sub>CCO</sub> via a 4.7 k $\Omega$  pull-up resistor.

ds541\_05\_070806

Figure 5: Configuring in Master Serial Mode

- 1 For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2 For compatible voltages, refer to the appropriate data sheet.

- 3 In Slave Serial mode, the configuration interface can be clocked by an external oscillator, or optionally the CLKOUT signal can be used to drive the FPGA's configuration clock (CCLK). If the XQF32P PROM's CLKOUT signal is used, then CLKOUT must be tied to a 4.7KΩ resistor pulled up to V<sub>CCO</sub>.

- 4 For the XQF32P the  $\overline{CF}$  pin is a bidirectional pin, and if  $\overline{CF}$  is not connected to PROGB, then must be tied to  $V_{CCO}$  via a 4.7 k $\Omega$  pull-up resistor.

ds541\_06\_070806

Figure 6: Configuring in Slave Serial Mode

- 1 For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2 For compatible voltages, refer to the appropriate data sheet.

- 3 For the XQF32P the  $\overline{CF}$  pin is a bidirectional pin, and if  $\overline{CF}$  is not connected to PROGB, then must be tied to V<sub>CCO</sub> via a 4.7 k $\Omega$  pull-up resistor.

ds541\_07\_070806

Figure 7: Configuring Multiple Devices in Master/Slave Serial Mode

- 1 For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2 For compatible voltages, refer to the appropriate data sheet.

3 CS\_B (or CS) and RDWR\_B (or WRITE) must be either driven Low or pulled down exernally. One option is shown.

4 The BUSY pin is only available with the XQF32P Platform Flash PROM, and the connection is only required for

- high-frequency SelectMAP mode configuration. For BUSY pin requirements, refer to the appropriate FPGA data sheet. 5 For the XQF32P the  $\overline{\text{CF}}$  pin is a bidirectional pin, and if  $\overline{\text{CF}}$  is not connected to PROGB, then must be tied to V<sub>CCO</sub> via

- a 4.7 k $\Omega$  pull-up resistor.

ds541\_08\_070806

Figure 8: Configuring in Master SelectMAP Mode

- 1 For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2 For compatible voltages, refer to the appropriate data sheet.

- 3 CS\_B (or  $\overline{\text{CS}}$ ) and RDWR\_B (or  $\overline{\text{WRITE}}$ ) must be either driven Low or pulled down externally. One option is shown.

- 4 The BUSY pin is only available with the XQF32P Platform Flash PROM, and the connection is only required for high-frequency SelectMAP mode configuration. For BUSY pin requirements, refer to the appropriate FPGA data sheet.

- 5 In Slave SelectMAP mode, the configuration interface can be clocked by an external oscillator, or, optionally, the CLKOUT signal can be used to drive the FPGA's configuration clock (CCLK). If the XQF32P PROM's CLKOUT signal is used, then CLKOUT must be tied to a 4.7 KΩ resistor pulled up to V<sub>CCO</sub>.

6 For the XQF32P the  $\overline{CF}$  pin is a bidirectional pin, and if  $\overline{CF}$  is not connected to PROGB, then must be tied to V<sub>CCO</sub> via

- a 4.7 k $\Omega$  pull-up resistor.

ds541 09 080406

Figure 9: Configuring in Slave SelectMAP Mode

- 1 For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2 For compatible voltages, refer to the appropriate data sheet.

- 3 CS\_B (or CS) and RDWR\_B (or WRITE) must be either driven Low or pulled down exernally. One option is shown.

- 4 The BUSY pin is only available with the XQF32P Platform Flash PROM, and the connection is only required for high-frequency SelectMAP mode configuration. For BUSY pin requirements, refer to the appropriate FPGA data sheet.

- 5 For the XQF32P the  $\overline{\text{CF}}$  pin is a bidirectional pin, and if  $\overline{\text{CF}}$  is not connected to PROGB, then it must be tied to VCCO via a 4.7 k $\Omega$  pull-up resistor.

ds541\_10\_080406

Figure 10: Configuring Multiple Devices with Identical Patterns in Master/Slave SelectMAP Mode

- 1 For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2 For compatible voltages, refer to the appropriate data sheet.

- 3 CS\_B (or CS) and RDWR\_B (or WRITE) must be either driven Low or pulled down exernally. One option is shown.

- 4 The BUSY pin is only available with the XQF32P Platform Flash PROM, and the connection is only required for high-frequency SelectMAP mode configuration. For BUSY pin requirements, refer to the appropriate FPGA data sheet.

- 5 For the XQF32P the  $\overline{\text{CF}}$  pin is a bidirectional pin, and if  $\overline{\text{CF}}$  is not connected to PROGB, then it must be tied to VCCO via a 4.7 k $\Omega$  pull-up resistor.

ds541\_11\_080406

Figure 11: Configuring Multiple Devices with Design Revisioning in Slave Serial Mode

- 1. For Mode pin connections and DONE pin pull-up value, refer to the appropriate FPGA data sheet.

- 2. For compatible voltages, refer to the appropriate data sheet.

- 3. RDWR\_B (or WRITE) must be either driven Low or pulled down exernally. One option is shown.

- 4. The BUSY pin is only available with the XQF32P Platform Flash PROM, and the connection is only required for high frequency SelectMAP mode configuration. For BUSY pin requirements, refer to the appropriate FPGA data sheet.

- 5. In Slave SelectMAP mode, the configuration interface can be clocked by an external oscillator, or optionally the CLKOUT signal can be used to drive the FPGA's configuration clock (CCLK). If the XQF32P PROM's CLKOUT signal is used, then it must be tied to a 4.7KΩ resistor pulled up to V<sub>CCO</sub>.

- 6 For the XQF32P the  $\overline{CF}$  pin is a bidirectional pin, and if  $\overline{CF}$  is not connected to PROGB, then must be tied to  $V_{CCO}$  via a 4.7 k $\Omega$  pull-up resistor

ds541\_12\_070906

Figure 12: Configuring Multiple Devices with Design Revisioning in Slave SelectMAP Mode

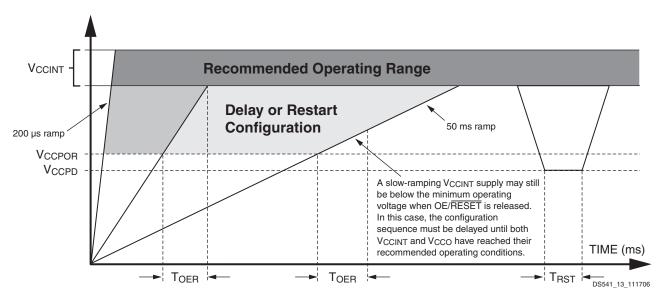

### **Reset and Power-On Reset Activation**

At power up, the device requires the V<sub>CCINT</sub> power supply to monotonically rise to the nominal operating voltage within the specified V<sub>CCINT</sub> rise time. If the power supply cannot meet this requirement, then the device might not perform power-on reset properly. During the power-up sequence, OE/RESET is held Low by the PROM. Once the required supplies have reached their respective POR (Power On Reset) thresholds, the OE/RESET release is delayed (TOER minimum) to allow more margin for the power supplies to stabilize before initiating configuration. The OE/RESET pin is connected to an external 4.7 k $\Omega$  pull-up resistor and also to the target FPGA's INIT pin. For systems utilizing slow-rising power supplies, an additional power monitoring circuit can be used to delay the target configuration until the system power reaches minimum operating voltages by holding the OE/RESET pin Low. When OE/RESET is

released, the FPGA's INIT pin is pulled High allowing the FPGA's configuration sequence to begin. If the power drops below the power-down threshold (V<sub>CCPD</sub>), the PROM resets and OE/RESET is again held Low until the after the POR threshold is reached. OE/RESET polarity is not programmable. These power-up requirements are shown graphically in Figure 13, page 20.

For a fully powered Platform Flash PROM, a reset occurs whenever OE/RESET is asserted (Low) or  $\overline{\text{CE}}$  is deasserted (High). The address counter is reset,  $\overline{\text{CEO}}$  is driven High, and the remaining outputs are placed in a high-impedance state.

**Note:** The XQF32P PROM requires both  $V_{CCINT}$  to rise above its POR threshold and for  $V_{CCO}$  to reach the recommended operating voltage level before releasing OE/RESET.

Figure 13: Platform Flash PROM Power-Up Requirements

## I/O Input Voltage Tolerance and Power Sequencing

The I/Os on each re-programmable Platform Flash PROM are fully 3.3V tolerant. This allows 3V CMOS signals to connect directly to the inputs without damage. The core power supply ( $V_{CCINT}$ ), JTAG pin power supply ( $V_{CCJ}$ ), output power supply ( $V_{CCO}$ ), and external 3V CMOS I/O signals can be applied in any order.

## **Standby Mode**

The PROM enters a low-power standby mode whenever  $\overline{\text{CE}}$  is deasserted (High). In standby mode, the address counter is reset,  $\overline{\text{CEO}}$  is driven High, and the remaining outputs are placed in a high-impedance state regardless of the state of the  $\overline{\text{OE/RESET}}$  input. For the device to remain in the low-power standby mode, the JTAG pins TMS, TDI, and

TDO must not be pulled Low, and TCK must be stopped (High or Low).

When using the FPGA DONE signal to drive the PROM CE pin High to reduce standby power after configuration, an external pull-up resistor should be used. Typically a  $330\Omega$  pull-up resistor is used, but refer to the appropriate FPGA data sheet for the recommended DONE pin pull-up value. If the DONE circuit is connected to an LED to indicate FPGA configuration is complete, and is also connected to the PROM  $\overline{\text{CE}}$  pin to enable low-power standby mode, then an external buffer should be used to drive the LED circuit to ensure valid transitions on the PROM's  $\overline{\text{CE}}$  pin. If low-power standby mode is not required for the PROM, then the  $\overline{\text{CE}}$  pin should be connected to ground.

Table 7: Truth Table for XQF32P PROM Control Inputs

|          | Control Inputs |      |                     | Internal Address                                                              | Outputs              |      |        |         |  |  |

|----------|----------------|------|---------------------|-------------------------------------------------------------------------------|----------------------|------|--------|---------|--|--|

| OE/RESET | CE             | CF   | BUSY <sup>(5)</sup> | internal Address                                                              | DATA                 | CEO  | CLKOUT | ICC     |  |  |

| High     | Low            | High | Low                 | If address < TC <sup>(2)</sup> and address < EA <sup>(3)</sup> : increment    | Active               | High | Active | Active  |  |  |

|          |                |      |                     | If address < TC <sup>(2)</sup> and address = EA <sup>(3)</sup> : don't change | High-Z               | High | High-Z | Reduced |  |  |

|          |                |      |                     | Else If address = TC <sup>(2)</sup> : don't change                            | High-Z               | Low  | High-Z | Reduced |  |  |

| High     | Low            | High | High                | Unchanged                                                                     | Active and Unchanged | High | Active | Active  |  |  |

| High     | Low            | -    | X <sup>(1)</sup>    | Reset <sup>(4)</sup>                                                          | Active               | High | Active | Active  |  |  |

| Low      | Low            | Х    | Х                   | Held reset <sup>(4)</sup>                                                     | High-Z               | High | High-Z | Active  |  |  |

| Х        | High           | Х    | Х                   | Held reset <sup>(4)</sup>                                                     | High-Z               | High | High-Z | Standby |  |  |

- 1. X = don't care.

- 2. TC = Terminal Count = highest address value.

- 3. For the XQF32P with Design Revisioning enabled, EA = end address (last address in the selected design revision).

- 4. For the XQF32P with Design Revisioning enabled, Reset = address reset to the beginning address of the selected bank. If Design Revisioning is not enabled, then Reset = address reset to address 0.

- 5. The BUSY input is only enabled when the XQF32P is programmed for parallel data output and decompression is not enabled.

### **DC Electrical Characteristics**

## **Absolute Maximum Ratings**

| Symbol             | Description                             |                                      | XQF32P       | Units |

|--------------------|-----------------------------------------|--------------------------------------|--------------|-------|

| V <sub>CCINT</sub> | Internal supply voltage relative to GND |                                      | -0.5 to +2.7 | V     |

| V <sub>CCO</sub>   | I/O supply voltage relative to GND      |                                      |              |       |

| V <sub>CCJ</sub>   | JTAG I/O supply voltage relative to GND |                                      |              |       |

| V <sub>IN</sub>    | Input voltage with respect to GND       | with respect to GND $V_{CCO} < 2.5V$ |              | V     |

|                    |                                         | $V_{CCO} \ge 2.5V$                   | -0.5 to +3.6 | V     |

| V <sub>TS</sub>    | Voltage applied to High-Z output        | V <sub>CCO</sub> < 2.5V              | -0.5 to +3.6 | V     |

|                    |                                         | $V_{CCO} \ge 2.5V$                   | -0.5 to +3.6 | V     |

| T <sub>STG</sub>   | Storage temperature (ambient)           | re (ambient)                         |              | °C    |

| T <sub>J</sub>     | Junction temperature                    |                                      | +125         | °C    |

#### Notes:

- Maximum DC undershoot below GND must be limited to either 0.5V or 10 mA, whichever is easier to achieve. During transitions, the device pins can undershoot to -2.0V or overshoot to +7.0V, provided this over- or undershoot lasts less then 10 ns and with the forcing current being limited to 200 mA.

- Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time adversely affects device reliability.

- 3. For soldering guidelines, see the information on "Packaging and Thermal Characteristics" at <a href="www.xilinx.com">www.xilinx.com</a>.

### Supply Voltage Requirements for Power-On Reset and Power-Down

| Symbol             | Description                                                                                                                    | XQI | Units |       |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|

| Syllibol           | Description                                                                                                                    | Min | Max   | Units |

| T <sub>VCC</sub>   | V <sub>CCINT</sub> rise time from 0V to nominal voltage <sup>(2)</sup>                                                         | 0.2 | 50    | ms    |

| V <sub>CCPOR</sub> | POR threshold for the V <sub>CCINT</sub> supply                                                                                | 0.5 | _     | V     |

| T <sub>OER</sub>   | OE/RESET release delay following POR <sup>(3)</sup>                                                                            | 0.5 | 30    | ms    |

| $V_{CCPD}$         | Power-down threshold for V <sub>CCINT</sub> supply                                                                             | _   | 0.5   | V     |

| T <sub>RST</sub>   | Time required to trigger a device reset when the $V_{\text{CCINT}}$ supply drops below the maximum $V_{\text{CCPD}}$ threshold | 10  | _     | ms    |

- 1.  $V_{CCINT}$ ,  $V_{CCO}$ , and  $V_{CCJ}$  supplies can be applied in any order.

- At power up, the device requires the V<sub>CCINT</sub> power supply to monotonically rise to the nominal operating voltage within the specified T<sub>VCC</sub> rise time. If the power supply cannot meet this requirement, then the device might not perform power-on-reset properly. See Figure 13, page 20.

- 3. If the V<sub>CCINT</sub> and V<sub>CCO</sub> supplies do not reach their respective recommended operating conditions before the OE/RESET pin is released, then the configuration data from the PROM is not be available at the recommended threshold levels. The configuration sequence must be delayed until both V<sub>CCINT</sub> and V<sub>CCO</sub> have reached their recommended operating conditions.

## **Recommended Operating Conditions**

| Ola a l            | D                                           | 1              |                      | XQF32P |                      | Unito |

|--------------------|---------------------------------------------|----------------|----------------------|--------|----------------------|-------|

| Symbol             | Descripti                                   | ion            | Min                  | Тур    | Max                  | Units |

| V <sub>CCINT</sub> | Internal voltage supply                     |                | 1.65                 | 1.8    | 2.0                  | V     |

| V <sub>CCO</sub>   | Supply voltage for output drivers           | 3.3V Operation | 3.0                  | 3.3    | 3.6                  | V     |

|                    |                                             | 2.5V Operation | 2.3                  | 2.5    | 2.7                  | V     |

|                    |                                             | 1.8V Operation | 1.7                  | 1.8    | 1.9                  | V     |

|                    |                                             | 1.5V Operation | TBD                  | 1.5    | TBD                  | ٧     |

| $V_{CCJ}$          | Supply voltage for JTAG output              | 3.3V Operation | 3.0                  | 3.3    | 3.6                  | ٧     |

|                    | drivers                                     | 2.5V Operation | 2.3                  | 2.5    | 2.7                  | ٧     |

| V <sub>IL</sub>    | Low-level input voltage                     | 3.3V Operation | 0                    | _      | 0.8                  | ٧     |

|                    |                                             | 2.5V Operation | 0                    | _      | 0.7                  | ٧     |

|                    |                                             | 1.8V Operation | _                    | _      | 20% V <sub>CCO</sub> | V     |

|                    |                                             | 1.5V Operation | 0                    | _      | TBD                  | ٧     |

| V <sub>IH</sub>    | High-level input voltage                    | 3.3V Operation | 2.0                  | -      | 3.6                  | V     |

|                    |                                             | 2.5V Operation | 1.7                  | _      | 3.6                  | ٧     |

|                    |                                             | 1.8V Operation | 70% V <sub>CCO</sub> | -      | 3.6                  | V     |

|                    |                                             | 1.5V Operation | TBD                  | _      | 3.6                  | ٧     |

| T <sub>IN</sub>    | Input signal transition time <sup>(1)</sup> |                | _                    | _      | 500                  | ns    |

| V <sub>O</sub>     | Output voltage                              |                | 0                    | -      | V <sub>CCO</sub>     | ٧     |

#### Notes:

## **Quality and Reliability Characteristics**

| Symbol           | Description                      | Min    | Max | Units  |

|------------------|----------------------------------|--------|-----|--------|

| T <sub>DR</sub>  | Data retention                   | 20     | _   | Years  |

| N <sub>PE</sub>  | Program/erase cycles (Endurance) | 20,000 | _   | Cycles |

| V <sub>ESD</sub> | Electrostatic discharge (ESD)    | 2,000  | _   | Volts  |

<sup>1.</sup> Input signal transition time measured between 10%  $V_{CCO}$  and 90%  $V_{CCO}$ .

## **DC Characteristics Over Operating Conditions**

|                                 |                                                                            |                                                                                                                 | XQF32P                 |          |       |

|---------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|----------|-------|

| Symbol                          | Description                                                                | Test<br>Conditions                                                                                              | Min                    | Max      | Units |

| V <sub>OH</sub>                 | High-level output voltage for 3.3V outputs                                 | I <sub>OH</sub> = -4 mA                                                                                         | 2.4                    | -        | V     |

|                                 | High-level output voltage for 2.5V outputs                                 | I <sub>OH</sub> = -500 μA                                                                                       | V <sub>CCO</sub> - 0.4 | -        | V     |

|                                 | High-level output voltage for 1.8V outputs                                 | I <sub>OH</sub> = -50 μA                                                                                        | V <sub>CCO</sub> - 0.4 | -        | V     |

|                                 | High-level output voltage for 1.5V outputs                                 | I <sub>OH</sub> = TBD                                                                                           | TBD                    | <u> </u> | V     |

| $V_{OL}$                        | Low-level output voltage for 3.3V outputs                                  | I <sub>OL</sub> = 4 mA                                                                                          | -                      | 0.4      | V     |

|                                 | Low-level output voltage for 2.5V outputs                                  | I <sub>OL</sub> = 500 μA                                                                                        | -                      | 0.4      | V     |

|                                 | Low-level output voltage for 1.8V outputs                                  | I <sub>OL</sub> = 50 μA                                                                                         | _                      | 0.4      | V     |

|                                 | Low-level output voltage for 1.5V outputs                                  | I <sub>OL</sub> = TBD                                                                                           | _                      | TBD      | V     |

| I <sub>CCINT</sub>              | Internal voltage supply current, active mode                               | 33 MHz                                                                                                          | _                      | 10       | mA    |

| I <sub>CCO</sub> <sup>(1)</sup> | Output driver supply current, active serial mode                           | 33 MHz                                                                                                          | _                      | 10       | mA    |

|                                 | Output driver supply current, active parallel mode                         | 33 MHz                                                                                                          | _                      | 40       | mA    |

| I <sub>CCJ</sub>                | JTAG supply current, active mode                                           | Note (2)                                                                                                        | _                      | 5        | mA    |

| I <sub>CCINTS</sub>             | Internal voltage supply current, standby mode                              | Note (3)                                                                                                        | _                      | 1        | mA    |

| I <sub>ccos</sub>               | Output driver supply current, standby mode                                 | Note (3)                                                                                                        | _                      | 1        | mA    |

| I <sub>CCJS</sub>               | JTAG supply current, standby mode                                          | Note (3)                                                                                                        | _                      | 1        | mA    |

| I <sub>ILJ</sub>                | JTAG pins TMS, TDI, and TDO pull-up current                                | $V_{CCJ} = max$<br>$V_{IN} = GND$                                                                               | -                      | 100      | μА    |

| I <sub>IL</sub>                 | Input leakage current                                                      | $V_{CCINT} = max$ $V_{CCO} = max$ $V_{IN} = GND \text{ or }$ $V_{CCO}$                                          | -10                    | 10       | μА    |

| I <sub>IH</sub>                 | Input and output High-Z leakage current                                    | $\begin{array}{c} V_{CCINT} = max \\ V_{CCO} = max \\ V_{IN} = GND \ or \\ V_{CCO} \end{array}$                 | -10                    | 10       | μА    |

| I <sub>ILP</sub>                | Source current through internal pull-ups on EN_EXT_SEL, REV_SEL0, REV_SEL1 | $\begin{aligned} & V_{CCINT} = max \\ & V_{CCO} = max \\ & V_{IN} = GND \text{ or } \\ & V_{CCO} \end{aligned}$ | -                      | 100      | μА    |

| I <sub>IHP</sub>                | Sink current through internal pull-down on BUSY                            | $V_{CCINT} = max$ $V_{CCO} = max$ $V_{IN} = GND \text{ or }$ $V_{CCO}$                                          | -100                   | _        | μА    |

| C <sub>IN</sub>                 | Input capacitance                                                          | V <sub>IN</sub> = GND<br>f = 1.0 MHz                                                                            | -                      | 8        | pF    |

| C <sub>OUT</sub>                | Output capacitance                                                         | V <sub>IN</sub> = GND<br>f = 1.0 MHz                                                                            | -                      | 14       | pF    |

- 1. Output driver supply current specification based on no load conditions.

- 2. TDI/TMS/TCK non-static (active).

- 3.  $\overline{\text{CE}}$  High, OE Low, and TMS/TDI/TCK static.

## **AC Electrical Characteristics**

## **AC Characteristics Over Operating Conditions**

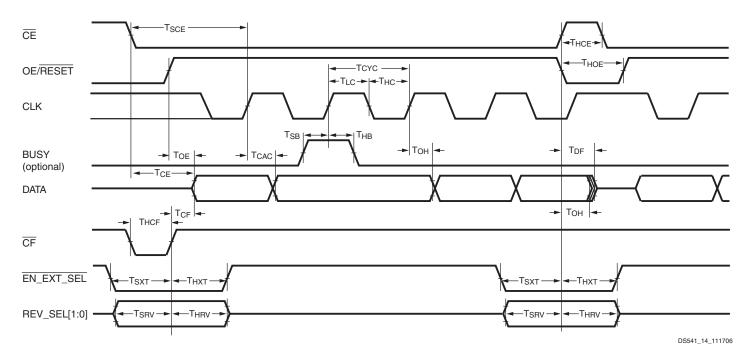

## XQF32P PROM as Configuration Slave with CLK Input Pin as Clock Source

| Cumbal           | Description                                                                                                                              | XQF32P |     | Units |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------|

| Symbol           | Description                                                                                                                              | Min    | Max | Units |

| T <sub>HCF</sub> | $\overline{\text{CF}}$ hold time to guarantee design revision selection is sampled when $V_{CCO} = 3.3 \text{V}$ or $2.5 \text{V}^{(9)}$ | 300    |     | ns    |

|                  | $\overline{\text{CF}}$ hold time to guarantee design revision selection is sampled when $V_{CCO} = 1.8V^{(9)}$                           | 300    |     | ns    |

| T <sub>CF</sub>  | CF to data delay when VCCO = 3.3V or 2.5V <sup>(8)</sup>                                                                                 | _      | 25  | ns    |