# TOSHIBA

## TC55257BPL/BFL/BSPL/BFTL/BTRL-85/10

## SILICON GATE CMOS

## 32,768 WORD x 8 BIT STATIC RAM

#### Description

The TC55257BPL is a 262,144 bit CMOS static random access memory organized as 32,768 words by 8 bits and operated from a single 5V power supply. Advanced circuit techniques provide both high speed and low power features with an operating current of 5mA/MHz (typ.) and a minimum cycle time of 85ns.

When  $\overline{\text{CE}}$  is a logical high, the device is placed in a low power standby mode in which the standby current is 100µA. The TC55257BPL has two control inputs. Chip enable ( $\overline{\text{CE}}$ ) allows for device selection and data retention control, while an output enable input ( $\overline{\text{OE}}$ ) provides fast memory access. The TC55257BPL is suitable for use in microprocessor systems where high speed, low power, and battery backup are required.

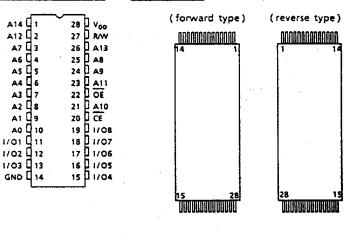

The TC55257BPL is offered in a standard dual-in-line 28-pin plastic package (0.6/0.3 inch width), a small outline plastic package, and a thin small outline plastic package (forward type, reverse type).

#### Features

- Low power dissipation:

- 27:5mW/MHz (typ.)

- Standby current:

- 100µA (max.)

- Single 5V power supply

- Access time (max.)

|                            | TC55257BPL/BFL/BSPL/BFTL/BTI |       |  |  |  |

|----------------------------|------------------------------|-------|--|--|--|

|                            | -85                          | -10   |  |  |  |

| Access Time                | 85ns                         | 100ns |  |  |  |

| Chip Enable<br>Access Time | 85ns                         | 100ns |  |  |  |

| Output Enable Time         | 45ns                         | 50ns  |  |  |  |

ĈĒ

- Power down feature:

- Data retention supply voltage: 2.0 ~ 5.5V

- Inputs and outputs TTL compatible

- Package TC55257BPL : DIP28-P-600

| - | TC55257BFL   | : SOP28-P-450   |

|---|--------------|-----------------|

|   | 1000201 DI L | . 001 20-1 -400 |

|   | TC55257BSPL  | : DIP28-P-300B  |

|   | TC55257BFTL  | : TSOP28-P      |

|   | TC55257BTRL  | : TSOP28-P-A    |

#### Pin Names

| A0 ~ A14        | Addres                        | Address Inputs           |    |                |                 |      |                 |                 |                 |                |                |                |                |                 |

|-----------------|-------------------------------|--------------------------|----|----------------|-----------------|------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|

| R/W             | Read/V                        | Read/Write Control Input |    |                |                 |      |                 |                 |                 |                |                |                |                |                 |

| ŌĒ              | Output                        | Output Enable Input      |    |                |                 |      |                 |                 |                 |                |                |                |                |                 |

| CE              | Chip E                        | Chip Enable Input        |    |                |                 |      |                 |                 |                 |                |                |                | ,              |                 |

| I/O1 ~ I/O8     | I/O1 ~ I/O8 Data Input/Output |                          |    |                |                 |      |                 |                 |                 |                |                |                |                |                 |

| V <sub>DD</sub> | Power                         | (+5V)                    |    |                |                 |      |                 |                 |                 |                |                |                |                |                 |

| GND             | Ground                        |                          |    |                |                 |      |                 |                 |                 |                |                |                |                |                 |

| PIN NO.         | 1                             | 2                        | 3  | 4              | 5               | 6    | 7               | 8               | 9               | 10             | 11             | 12             | 13             | 14              |

| PIN NAME        | OE                            | A <sub>11</sub>          | Ag | A <sub>8</sub> | A <sub>13</sub> | R/W  | V <sub>DD</sub> | A <sub>14</sub> | A <sub>12</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub>  |

| PIN NO.         | 15                            | 16                       | 17 | 18             | 19              | 20   | 21              | 22              | 23              | 24             | 25             | 26             | 27             | 28              |

|                 | A <sub>2</sub>                | A <sub>1</sub>           | Ao | 1/01           | 1/02            | 1/03 | GND             | 1/04            | 1/05            | 1/06           | 1/07           | 1/08           | CE             | A <sub>10</sub> |

This Material Copyrighted By Its Respective Manufacturer

#### Pin Connection (Top View)

o 28 PIN DIP & SOP o 28 PIN TSOP

A-1

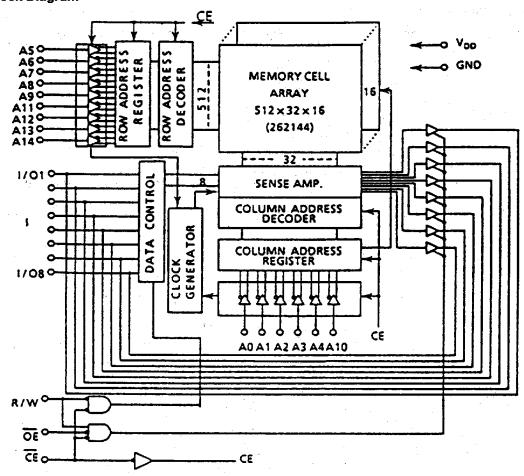

#### Block Diagram

#### **Operating Mode**

| MODE            | PIN | ĈĒ  | ŌĒ  | R/W | I/01 ~ I/08      | POWER            |

|-----------------|-----|-----|-----|-----|------------------|------------------|

| Read            |     | L 1 | . L | н   | D <sub>OUT</sub> | IDDO             |

| Write           |     | L . | *   | L   | D <sub>IN</sub>  | IDDO             |

| Output Deselect |     | L   | н   | н   | High-Z           | I <sub>DDO</sub> |

| Standby         |     | Н   | *   | *   | High-Z           | IDDS             |

\* H or L

#### Maximum Ratings

| SYMBOL              | ITEM                         | RATING                        | UNIT   |

|---------------------|------------------------------|-------------------------------|--------|

| V <sub>DD</sub>     | Power Supply Voltage         | -0.3 ~ 7.0                    | V      |

| V <sub>IN</sub>     | Input Voltage                | -0.3* ~ 7.0                   | V      |

| V <sub>I/O</sub>    | Input and Output Voltage     | -0.5* ~ V <sub>DD</sub> + 0.5 | V      |

| PD                  | Power Dissipation            | 1.0/0.8/0.6**                 | w      |

| T <sub>SOLDER</sub> | Soldering Temperature • Time | 260 • 10                      | °C•sec |

| TSTRG               | Storage Temperature          | -55 ~ 150                     | °C     |

| TOPR                | Operating Temperature        | 0 ~ 70                        | °C     |

-3.0V with a pulse width of 50ns

\*\* Package dependent: 0.6 inch 1.0W, 0.3 inch 0.8W, 0.45 inch 0.6W

A-2

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

9097248 0026157 697 🛛

#### DC Recommended Operating Conditions

| SYMBOL          | PARAMETER                     | MIN.  | TYP.  | MAX.                  | UNIT |

|-----------------|-------------------------------|-------|-------|-----------------------|------|

| V <sub>DD</sub> | Power Supply Voltage          | 4.5   | . 5.0 | 5.5                   |      |

| VIH             | Input High Voltage            | 2.2   | _     | V <sub>DD</sub> + 0.3 |      |

| VIL             | Input Low Voltage             | -0.3* | . –   | 0.8                   |      |

| V <sub>DH</sub> | Data Retention Supply Voltage | 2.0   | -     | 5.5                   |      |

\* -3.0V with a pulse width of 50ns

### DC Characteristics (Ta = 0 ~ 70°C, $V_{DD}$ = 5V±10%)

| SYMBOL            | PARAMETER              | TEST CON                                                                                                                     | IDITION                               | MIN. | TYP. | MAX.    | UNIT |

|-------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|---------|------|

| ار ا              | Input Leakage Current  | $V_{IN} = 0 \sim V_{DD}$                                                                                                     |                                       | -    | ·    | ±1.0    | μA   |

| ILO               | Output Leakage Current | $\overline{CE} = V_{IH} \text{ or } R/W = V_{IL}$ $V_{OUT} = 0 \sim V_{DD}$                                                  | or $\overline{OE} = V_{IH}$           | _    | -    | ±1.0    | μA   |

| l <sub>он</sub>   | Output High Current    | V <sub>OH</sub> = 2.4V                                                                                                       |                                       | -1.0 | -    | -       | mA   |

| I <sub>OL</sub>   | Output Low Current     | V <sub>OL</sub> = 0.4V                                                                                                       |                                       | 4.0  | -    | · · · - | mA   |

| N                 |                        | CE = V <sub>IL</sub>                                                                                                         | t <sub>cycle</sub> = 1μs              | —    | 10   |         |      |

| I <sub>DDO1</sub> |                        |                                                                                                                              | t <sub>cycle</sub> = Min. cycle       |      | · _  | 70      |      |

|                   | Operating Current      | CE = 0.2V                                                                                                                    | t <sub>cycle</sub> = 1µs              | —    | 5    | _       | mA   |

| I <sub>DDO2</sub> |                        | $\begin{aligned} R/W &= V_{DD} - 0.2V \\ \text{Other Input} \\ &= V_{DD} - 0.2V/0.2V \\ I_{OUT} &= 0\text{mA} \end{aligned}$ | t <sub>cycle</sub> = Min. cycle       | -    | -    | 60      |      |

| I <sub>DDS1</sub> |                        | CE = V <sub>IH</sub>                                                                                                         | · · · · · · · · · · · · · · · · · · · | -    | -    | - 3     | mA   |

|                   | Standby Current        | $\overline{CE} = V_{DD} - 0.2V$                                                                                              | Ta = 0 ~ 70°C                         | -    | -    | 100     |      |

| DDS2              |                        | $V_{DD} = 2.0V \sim 5.5V$                                                                                                    | Ta = 25°C                             | -    | 2    | -       | μΑ   |

## Capacitance\* (Ta = 25°C, f = 1MHz)

| SYMBOL           | PARAMETER          | TEST CONDITION         | MAX. | UNIT |

|------------------|--------------------|------------------------|------|------|

| CIN              | Input Capacitance  | V <sub>IN</sub> = GND  | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = GND | 10   | μr   |

\*This parameter is periodically sampled and is not 100% tested.

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

9097248 0026158 523 🔳

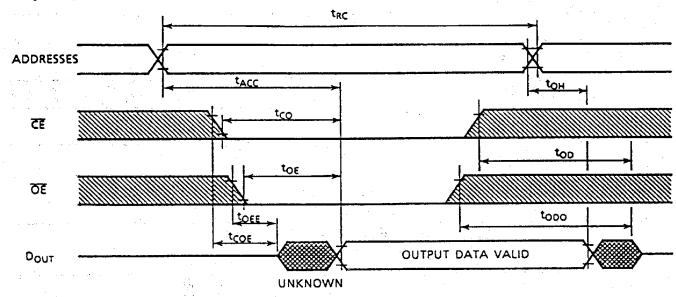

## AC Characteristics (Ta = 0 ~ 70°C, V<sub>DD</sub> = 5V $\pm$ 10%)

## Read Cycle

|                  |                                      | TC552  | 57BPL/BFL | /BSPL/BFT | L/BTRL |    |

|------------------|--------------------------------------|--------|-----------|-----------|--------|----|

| SYMBOL           | PARAMETER                            |        | <b>15</b> | -         | UNIT   |    |

|                  |                                      | MIN.   | MAX.      | MIN.      | MAX.   |    |

| t <sub>RC</sub>  | Read Cycle Time                      | 85     |           | 100       |        |    |

| tACC             | Address Access Time                  | -      | 85        | _         | 100    | 1  |

| t <sub>co</sub>  | CE Access Time                       |        | 85        | _         | 100    | 1  |

| tOE              | Output Enable to Output in Valid     |        | 45        | · · · ·   | 50     |    |

| t <sub>COE</sub> | Chip Enable (CE) to Output in Low-Z  | 10     | _         | 10        | -      | ns |

| t <sub>OEE</sub> | Output Enable to Output in Low-Z     | 5      |           | 5         | -      |    |

| t <sub>OD</sub>  | Chip Enable (CE) to Output in High-Z | n. — x | 30        | · _       | 50     | 1  |

| topo             | Output Enable to Output in High-Z    | -      | 30        | _         | 40     | ]  |

| toH              | Output Data Hold Time                | 10     |           | 10        | -      | 1  |

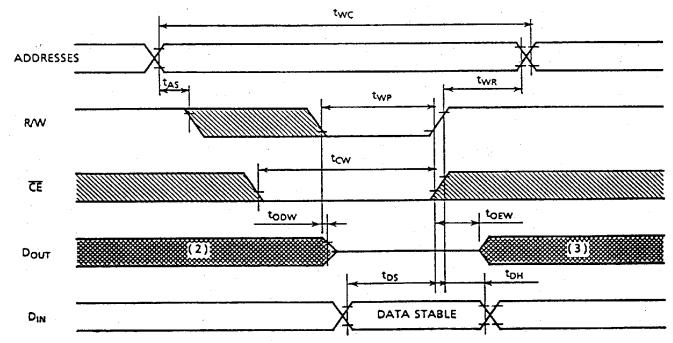

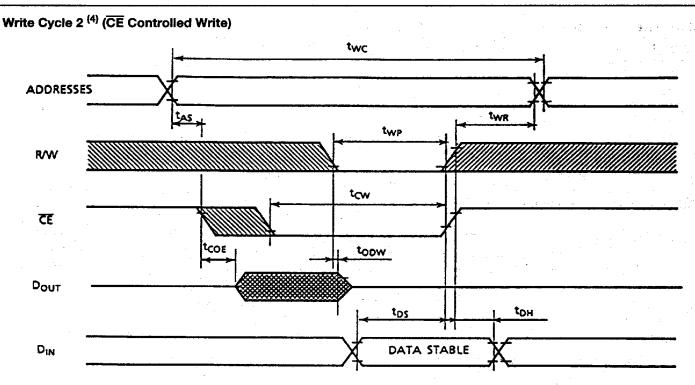

## Write Cycle

|                 |                                |     | TC552 | 57BPL/BFL | /BSPL/BFT | L/BTRL          |      |

|-----------------|--------------------------------|-----|-------|-----------|-----------|-----------------|------|

| SYMBOL          | PARAMETER                      |     | -85   |           | -10       |                 | UNIT |

|                 |                                |     | MIN.  | MAX.      | MIN.      | MAX.            | 1    |

| twc             | Write Cycle Time               |     | 85    |           | 100       | · -             |      |

| twp             | Write Pulse Width              |     | 60    |           | 70        | -               | 1    |

| tcw             | Chip Selection to End of Write | · . | 65    |           | 90        | -               |      |

| t <sub>AS</sub> | Address Setup Time             |     | 0     | · ·       | 0         | _               | 1    |

| twn             | Write Recovery Time            |     | 5     | _ ·       | 5         | _               | ns   |

| topw            | R/W to Output in High-Z        |     |       | 30        | -         | 50              | 1    |

| toew            | R/W to Output in Low-Z         |     | 5     | _         | 5         | . <b>–</b> 1775 |      |

| t <sub>DS</sub> | Data Setup Time                |     | 40    |           | 40        |                 |      |

| t <sub>DH</sub> | Data Hold Time                 | 1   | 0     |           | 0         | _               | 1    |

## **AC Test Conditions**

| Input Pulse Levels                         | 2.4V/0.6V                             |

|--------------------------------------------|---------------------------------------|

| Input Pulse Rise and Fall Time             | 5ns                                   |

| Input Timing Measurement Reference Levels  | 2.2V/0.8V                             |

| Output Timing Measurement Reference Levels | 2.2V/0.8V                             |

| Output Load                                | 1 TTL Gate and C <sub>L</sub> = 100pF |

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

| 90972480026159 46T 🎟

This Material Copyrighted By Its Respective Manufacturer

## **Timing Waveforms**

Write Cycle 1 <sup>(4)</sup> (R/W Controlled Write)

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

9097248 0026160 181 📖

#### Notes:

- 1. R/W is high for read cycles.

- 2. If the CE low transition occurs coincident with or after the R/W low transition, outputs remain in a high impedance state.

- 3. If the CE high transition occurs coincident with or prior to the R/W high transition, outputs remain in a high impedance state.

- 4. If  $\overline{\text{OE}}$  is high during a write cycle, the outputs are in a high impedance state during this period.

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

9097248 0026161 018 🔳

This Material Copyrighted By Its Respective Manufacturer

A-6

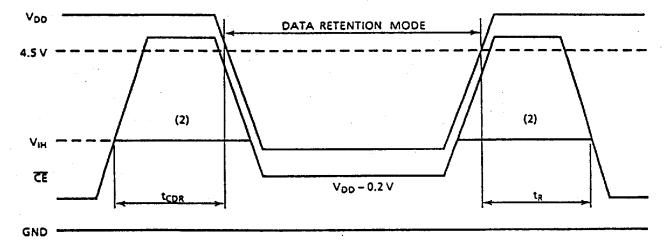

| SYMBOL           | PARAMETER                            | PARAMETER              |                    | TYP. | MAX. | UNIT |

|------------------|--------------------------------------|------------------------|--------------------|------|------|------|

| VDH              | Data Retention Supply Voltage        |                        | 2.0                | -    | 5.5  | V    |

|                  | Chandless Ossenant                   | V <sub>DH</sub> = 3.0V | -                  | -    | 50   |      |

| DDS2             | Standby Current                      | $V_{\rm DH} = 5.5V$    | -                  | -    | 100  | μΑ   |

| <sup>t</sup> CDR | Chip Deselect to Data Retention Mode |                        | 0                  | -    | -    |      |

| t <sub>R</sub>   | Recovery Time                        |                        | t <sub>RC(1)</sub> | _    | -    | μs   |

## Data Retention Characteristics (Ta = 0 ~ 70°C)

Note (1): Read Cycle Time

#### **CE** Controlled Data Retention Mode

Note (2): If the V<sub>IH</sub> of  $\overline{\text{CE}}$  is 2.2V in operation, I<sub>DDS1</sub> current flows during the period that the V<sub>DD</sub> voltage is going down from 4.5V to 2.4V.

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

9097248 0026162 T54 🔳

A-7