### IS42VS16100C1-DIE

# 512K Words x 16 Bits x 2 Banks (16-MBIT) SYNCHRONOUS DYNAMIC RAM

## ADVANCED INFORMATION JULY 2007

#### **FEATURES**

- Clock frequency: 100, 83, 66 MHz

- Power supply: 1.8V

- Fully synchronous; all signals referenced to a positive clock edge

- Two banks can be operated simultaneously and independently

- Dual internal bank controlled by A11 (bank select)

- Programmable burst length

(1, 2, 4, 8, full page)

- Programmable burst sequence: Sequential/Interleave

- 2048 refresh cycles every 32 ms

- · Random column address every clock cycle

- Programmable CAS latency (2, 3 clocks)

- Burst read/write and burst read/single write operations capability

- Burst termination by burst stop and precharge command

- Byte controlled by LDQM and UDQM

- Pads located along edges

#### PIN DESCRIPTIONS

| A0-A11      | Address Input                 |

|-------------|-------------------------------|

| A0-A10      | Row Address Input             |

| A11         | Bank Select Address           |

| A0-A7       | Column Address Input          |

| DQ0 to DQ15 | Data DQ                       |

| CLK         | System Clock Input            |

| CKE         | Clock Enable                  |

| CS          | Chip Select                   |

| RAS         | Row Address Strobe Command    |

| CAS         | Column Address Strobe Command |

| WE          | Write Enable                  |

|             |                               |

#### DESCRIPTION

ISSI's 16Mb Synchronous DRAM IS42VS16100C1 is organized as a 524,288-word x 16-bit x 2-bank for improved performance. The synchronous DRAMs achieve high-speed data transfer using pipeline architecture. All inputs and outputs signals refer to the rising edge of the clock input. Note: This is a summary datasheet specific to the die format. Please refer to the IS42VS16100C1 for complete device specification.

#### **KEY TIMING PARAMETERS**

| Parameter                    | -10 | -12 | Unit |

|------------------------------|-----|-----|------|

| Clock Cycle Time             |     |     |      |

| CAS Latency = 3              | 10  | 12  | ns   |

| $\overline{CAS}$ Latency = 2 | 12  | 15  | ns   |

| Clock Frequency              |     |     |      |

| CAS Latency = 3              | 100 | 83  | MHz  |

| $\overline{CAS}$ Latency = 2 | 83  | 66  | MHz  |

| Access Time from Clock       |     |     |      |

| $\overline{CAS}$ Latency = 3 | 7   | 9   | ns   |

| CAS Latency = 2              | 8   | 10  | ns   |

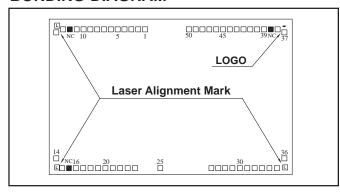

#### **BONDING DIAGRAM**

| LDQM | Lower Bye, Input/Output Mask |

|------|------------------------------|

| UDQM | Upper Bye, Input/Output Mask |

| VDD  | Power                        |

| GND  | Ground                       |

| VDDQ | Power Supply for DQ Pin      |

| GNDQ | Ground for DQ Pin            |

| NC   | No Connection                |

Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.