# SPICE Device Model Si5402DC

## **Vishay Siliconix**

## N-Channel 2.5-V (G-S) MOSFET

#### **CHARACTERISTICS**

- N-Channel Vertical DMOS

- Macro Model (Subcircuit Model)

- Level 3 MOS

- · Apply for both Linear and Switching Application

- Accurate over the -55 to 125°C Temperature Range

- Model the Gate Charge, Transient, and Diode Reverse Recovery Characteristics

#### **DESCRIPTION**

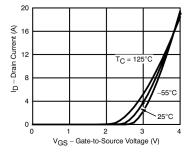

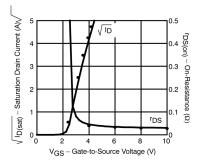

The attached spice model describes the typical electrical characteristics of the n-channel vertical DMOS. The subcircuit model is extracted and optimized over the -55 to  $125^{\circ}\text{C}$  temperature ranges under the pulsed 0-to-5V gate drive. The saturated output impedance is best fit at the gate bias near the threshold voltage.

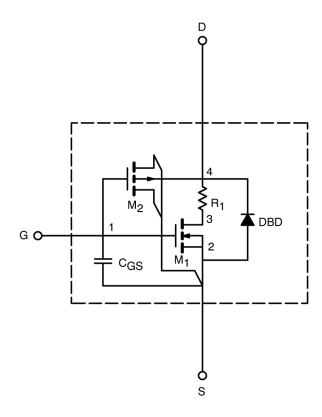

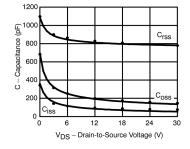

A novel gate-to-drain feedback capacitance network is used to model the gate charge characteristics while avoiding convergence difficulties of the switched  $C_{\rm gd}$  model. All model parameter values are optimized to provide a best fit to the measured electrical data and are not intended as an exact physical interpretation of the device.

### SUBCIRCUIT MODEL SCHEMATIC

This document is intended as a SPICE modeling guideline and does not constitute a commercial product data sheet. Designers should refer to the appropriate data sheet of the same number for guaranteed specification limits.

Document Number: 71572

www.vishay.com

07-Oct-99

1

## **SPICE Device Model Si5402DC**

## **Vishay Siliconix**

| SPECIFICATIONS (T <sub>J</sub> = 25°C UNLESS OTHERWISE NOTED) |                     |                                                                                                                                                                                                   |         |      |

|---------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| Parameter                                                     | Symbol              | Test Conditions                                                                                                                                                                                   | Typical | Unit |

| Static                                                        |                     |                                                                                                                                                                                                   |         |      |

| Gate Threshold Voltage                                        | $V_{GS(th)}$        | $V_{DS} = V_{GS}, I_{D} = 250 \mu A$                                                                                                                                                              | 1.76    | V    |

| On-State Drain Current <sup>a</sup>                           | I <sub>D(on)</sub>  | $V_{DS} \ge 5 \text{ V}, V_{GS} = 10 \text{ V}$                                                                                                                                                   | 147     | Α    |

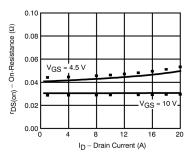

| Drain-Source On-State Resistance <sup>a</sup>                 | r <sub>DS(on)</sub> | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 4.9 A                                                                                                                                                    | 0.031   | Ω    |

|                                                               |                     | $V_{GS} = 4.5 \text{ V}, I_D = 3.9 \text{ A}$                                                                                                                                                     | 0.042   |      |

| Forward Transconductance <sup>a</sup>                         | g <sub>fs</sub>     | $V_{DS}$ = 10 V, $I_{D}$ = 4.9 A                                                                                                                                                                  | 15      | S    |

| Diode Forward Voltage <sup>a</sup>                            | V <sub>SD</sub>     | I <sub>S</sub> = 1.1 A, V <sub>GS</sub> = 0 V                                                                                                                                                     | 0.8     | V    |

| Dynamic <sup>b</sup>                                          |                     |                                                                                                                                                                                                   |         |      |

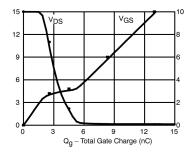

| Total Gate Charge                                             | Qg                  | $V_{DS}$ = 15 V, $V_{GS}$ = 10 V, $I_{D}$ = 4.9 A                                                                                                                                                 | 13.1    | nC   |

| Gate-Source Charge                                            | Q <sub>gs</sub>     |                                                                                                                                                                                                   | 3.11.3  |      |

| Gate-Drain Charg                                              | $Q_{gd}$            |                                                                                                                                                                                                   | 3.1     |      |

| Turn-On Delay Time                                            | t <sub>d(on)</sub>  | $V_{DD} = 15 \text{ V}, \text{ R}_L = 15 \Omega$ $I_D \cong 1 \text{ A}, \text{ V}_{GEN} = 10 \text{ V}, \text{ R}_G = 6 \Omega$ $I_F = 1.1 \text{ A}, \text{ di/dt} = 100 \text{ A/}\mu\text{s}$ | 8       | ns   |

| Rise Time                                                     | t <sub>r</sub>      |                                                                                                                                                                                                   | 11      |      |

| Turn-Off Delay Time                                           | t <sub>d(off)</sub> |                                                                                                                                                                                                   | 19      |      |

| Fall Time                                                     | t <sub>f</sub>      |                                                                                                                                                                                                   | 28      |      |

| Source-Drain Reverse Recovery Time                            | t <sub>rr</sub>     |                                                                                                                                                                                                   | 30      |      |

www.vishay.com Document Number: 71572 07-Oct-99

a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2%.

b. Guaranteed by design, not subject to production testing.

### COMPARISON OF MODEL WITH MEASURED DATA (TJ=25°C UNLESS OTHERWISE NOTED)

Note: Dots and squares represent measured data

Document Number: 71572 www.vishay.com 07-Oct-99 3