#### PRELIMINARY DATA SHEET

## **General Desription**

Using the IDT CMOS Oscillator technology, originally developed by Mobius Microsystems, the MM8202 replaces quartz crystal based resonators and oscillators with a monolithic CMOS IC at the thinnest possible form factors without the use of any mechanical frequency source or PLL. The product is specially designed to work with the next generation USB 2.0 High Speed, USB 2.0 Full/Low Speed and USB-IC (USB-InterChip) interface controller ICs, and high density SIM-, and smart-cards.

## **Ordering Information**

$\frac{8202}{1} - \frac{12}{2} \frac{\text{VP}}{3} \frac{\text{C}}{4} \frac{\text{NSG}}{5} \frac{\text{T}}{6}$

- 1) IDT Base Part Number

- 2) FF: Factory Programmed Frequency in MHz

- 3) Supply Voltage Configuration

- VP: 1.8V to 3.3V continuous operation

- V: 3.3V only operation

- T: 2.5V only operation

- P: 1.8V only operation

- 4) Output Signal Type

- C: CMOS Output

- 5) Package Options\*

- -D: Wafer form 200um thickness

- C: Wafer form 350um thickness

- -E: Wafer form 750um thickness

- NSG: 5x3.2, 4-Pin Package

- NVG: 2.5x2.0, 4-Pin Package

- M: SOIC, 8-Pin Package

- 6) Temperature Grade

- ": 0 to 70°C Commercial Temperature Range i.e. default is blank

- "R": -20 to 85°C Restricted Industrial Temperature Range

- 7) Tape & Reel Option

- ": Shipped in Tube i.e. default is blank

- T: Shipped in Tape & Reel

This product is rated "Green". Please contact factory for environmental compliancy information.

### **Features**

- · All-CMOS Temperature Compensated Oscillator

- TimeStak<sup>TM</sup>: Available in die form for the thinnest and smallest MCP options (-D package option)

- Ultra-low power operation (2mA typical at 1.8V supply)

- No quartz or PLL used: very low jitter performance leading to low link Bit Error Rates (BER)

- · Excellent reliability: Shock and vibration resistant

- · Many frequencies are supported

- · Factory programmable from 6 to 133MHz

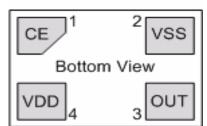

## Pin Assignment

**Table 1. Pin Descriptions**

| No | Name | Туре            | Description                                                                                                          |

|----|------|-----------------|----------------------------------------------------------------------------------------------------------------------|

| 1  | CE   | Input<br>Pullup | Chip Enable. Internal Pullup. MM8202 is<br>enabled when HIGH.When LOW, OUT has<br>a weak pull-down to GND internally |

| 2  | VSS  | Power           | System Ground                                                                                                        |

| 3  | OUT  | Output          | Frequency Output                                                                                                     |

| 4  | VDD  | Power           | Power Supply. Use a 0.1μF decoupling capacitor between VDD and VSS                                                   |

The Preliminary Information presented herein represents a product in pre-production. The noted characteristics are based on initial product characterization and/or qualification. Integrated Device Technology, Incorporated (IDT) reserves the right to change any circuitry or specifications without notice

## **Table 2. Pin Descriptions**

Below Pin Descriptions apply to SOIC-8 Package

| No      | Name | Туре            | Description                                                                                                          |

|---------|------|-----------------|----------------------------------------------------------------------------------------------------------------------|

| 1       | CE   | Input<br>Pullup | Chip Enable. Internal Pullup. MM8202 is<br>enabled when HIGH.When LOW, OUT has<br>a weak pull-down to GND internally |

| 4       | VSS  | Power           | System Ground                                                                                                        |

| 6       | OUT  | Output          | Frequency Output                                                                                                     |

| 8       | VDD  | Power           | Power Supply. Use a 0.1μF decoupling capacitor between VDD and VSS                                                   |

| 2,3,5,7 | NC   |                 | No Connect Pins. These pins may be left floating.                                                                    |

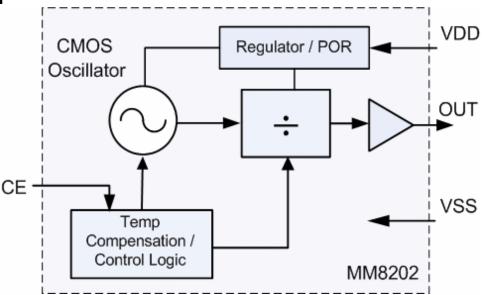

#### **Block Diagram**

## **Functional Description**

MM8202 is a monolithic all-CMOS frequency source. The internal CMOS Oscillator generates the factory-programmed frequencies with high accuracy and excellent phase noise and jitter. The device is a silicon alternative to quartz based crystal resonators and oscillators. Various programming and configuration options are supported as given in the Part Ordering Information section above. The easy-to-use device offers programmable frequencies and various supply voltage configurations. Offered in common crystal oscillator pin-outs, the MM8202 allows the designer to disable the oscillator via the CE pin to enter a very low current, quiescent state. The CMOS oscillator features very fast start-up time to enable rapid wake-up from the quiescent state. All required circuit elements other than those that are noted in the Pin Descriptions Table (Table.1) above are internal to the device.

In addition to common package options in 5x3.2mm and 2.5x2.0mm dimensions, the MM8202 is offered in "wafer" form to be used in Chipon-Board (CoB) and Multi-Chip-Package (MCP) configurations for space and cost-sensitive applications. IDT offers MM8202 in Known-Good-Die (KGD) format with all applicable test and manufacturing information to allow for rapid evaluation and use.

## **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                             | Rating              |

|----------------------------------|---------------------|

| Supply Voltage, VDD              | 4.6V                |

| Input, V <sub>I</sub> (CE pin)   | -0.5V to VDD + 0.5V |

| Output, V <sub>O</sub> (OUT pin) | -0.5V to VDD + 0.5V |

| Storage Temperature              | -65°C to 150°C      |

# Electrical Characteristics<sup>5</sup> [3.3V]

VDD=3.0V to 3.6V, T<sub>A</sub>=0 to 70°C unless otherwise noted. Typical values are measured at VDD=3.3V, T<sub>A</sub>=35°C

| Parameter               | Symbol                                                                                                          | Conditions                                                                                                                                      | Min     | Тур         | Max          | Units             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------------|-------------------|

| ElectroStaticDischa rge | ESD                                                                                                             | Human Body Model, tested per JESD D22-A114                                                                                                      |         |             |              | ٧                 |

| Supply Voltage          | VDD                                                                                                             | Normal Operation <sup>3</sup>                                                                                                                   | 3.0     | 3.3         | 3.6          | V                 |

| Input LOW level         | $V_{IL}$                                                                                                        | CE pin                                                                                                                                          | -0.3    |             | VDD*0.3      | V                 |

| Input HIGH level        | $V_{IH}$                                                                                                        | CE pin                                                                                                                                          | VDD*0.7 |             | VDD+0.3      | V                 |

| Supply Current          | IDD                                                                                                             | Active supply current, VDD=3.3V, T=35oC, no output load                                                                                         |         | 2.5         | 3.0          | mA                |

| Quiescent Current       | IDDQ                                                                                                            | CE=LOW, output disabled                                                                                                                         |         | 0.2         | 1            | μΑ                |

| Output LOW level        | $V_{OL}$                                                                                                        | I <sub>OL</sub> = -4mA                                                                                                                          |         |             | 0.5          | V                 |

| Output HIGH level       | V <sub>OH</sub>                                                                                                 | I <sub>OH</sub> = 4mA                                                                                                                           | VDD-0.5 |             |              | V                 |

| Output Frequency        | F <sub>OUT</sub>                                                                                                | Factory Programmable.Contact IDT for frequencies not listed                                                                                     | 6       | 12,24,25,50 | 133          | MHz               |

| Frequency Stability     | F <sub>TOT</sub>                                                                                                | Total Frequency Stability over temperature, supply variation, aging (1st year at 35oC), shock & vibration. "" device option, over 0-70°C range  |         |             | <u>+</u> 400 | ppm               |

| Trequency diability     |                                                                                                                 | Total Frequency Stability over temperature, supply variation, aging (1st year at 35oC), shock&vibration. "R" device option, over -20-85°C range |         |             | <u>+</u> 400 | ppm               |

| Rise Time               | RT                                                                                                              | 20% to 80% x VDD. Output load (C <sub>L</sub> ) =8pF, NSG-option                                                                                |         |             | 1.9          | ns                |

| Fall Time               | FT                                                                                                              | 80% to 20% x VDD. Output load (C <sub>L</sub> ) =8pF, NSG-option                                                                                |         |             | 1.9          | ns                |

| Duty Cycle              | DC                                                                                                              | Clock output duty cycle. Measured under 80MHz, VDD/2, $C_L$ =8pF                                                                                | 45      |             | 55           | %                 |

| Duty Cycle              |                                                                                                                 | Clock output duty cycle. Measured over 80MHz, VDD/2, $C_L$ =8pF                                                                                 | 40      |             | 60           | %                 |

| Power-up time           | t <sub>on</sub>                                                                                                 | Output valid time after VDD meets the specified range&CE transition                                                                             | 50      | 100         | 400          | μs                |

| Period Jitter           | PJ <sub>RMS</sub>                                                                                               | Total RMS Period Jitter (including random and deterministic) <sup>1,2</sup>                                                                     |         | 3.5         |              | ps <sub>RMS</sub> |

| Cycle-cycle Jitter      | Cycle-cycle Jitter CJ The absolute value of max change in the periods of any 2 adjacent cycles <sup>1,2,4</sup> |                                                                                                                                                 |         |             | 50           | ps                |

| Phase Noise             | PN                                                                                                              | 1MHz offset from carrier <sup>1,2</sup>                                                                                                         |         | -140        | -135         | dBc/Hz            |

Notes 1. Measured with a  $50\Omega$  to GND termination

<sup>2:</sup> Measured at 48MHz output frequency

<sup>3.</sup> The MM8202 will support continuous VDD operation from 1.62 to 3.6V. The device can be powered up with a supply voltage at any of the 3 main supply rails of 1.8V, 2.5V or 3.3V.

<sup>4.</sup> Measured over 1000 cycles per JEDEC standard 65

<sup>5.</sup> Electrical parameters are guaranteed by design and characterization over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

# Electrical Characteristics<sup>5</sup> [2.5V]

VDD=2.25V to 2.75V,  $T_A$ =0 to 70°C unless otherwise noted. Typical values are measured at VDD=2.5V,  $T_A$ =35°C

| Parameter               | Symbol                                                                                                          | Conditions                                                                                                                                      | Min     | Тур         | Max          | Units             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------------|-------------------|

| ElectroStaticDischa rge | ESD                                                                                                             | Human Body Model, tested per JESD D22-A114                                                                                                      |         |             |              | V                 |

| Supply Voltage          | VDD                                                                                                             | Normal Operation <sup>3</sup>                                                                                                                   | 2.25    | 2.5         | 2.75         | V                 |

| Input LOW level         | $V_{IL}$                                                                                                        | CE pin                                                                                                                                          | -0.3    |             | VDD*0.3      | V                 |

| Input HIGH level        | $V_{IH}$                                                                                                        | CE pin                                                                                                                                          | VDD*0.7 |             | VDD+0.3      | V                 |

| Supply Current          | IDD                                                                                                             | Active supply current, VDD=2.5V, T=35oC, no output load                                                                                         |         | 2.25        | 2.75         | mA                |

| Quiescent Current       | IDDQ                                                                                                            | CE=LOW, output disabled                                                                                                                         |         | 0.2         | 1            | μΑ                |

| Output LOW level        | $V_{OL}$                                                                                                        | I <sub>OL</sub> = -3mA                                                                                                                          |         |             | 0.4          | V                 |

| Output HIGH level       | V <sub>OH</sub>                                                                                                 | I <sub>OH</sub> = 3mA                                                                                                                           | VDD-0.4 |             |              | V                 |

| Output Frequency        | F <sub>OUT</sub>                                                                                                | Factory Programmable.Contact IDT for frequencies not listed                                                                                     | 6       | 12,24,25,50 | 133          | MHz               |

| 5 0.130                 | F <sub>TOT</sub>                                                                                                | Total Frequency Stability over temperature, supply variation, aging (1st year at 35oC), shock & vibration. "" device option, over 0-70°C range  |         |             | <u>+</u> 400 | ppm               |

| Frequency Stability     |                                                                                                                 | Total Frequency Stability over temperature, supply variation, aging (1st year at 35oC), shock&vibration. "R" device option, over -20-85°C range |         |             | <u>+</u> 400 | ppm               |

| Rise Time               | RT                                                                                                              | 20% to 80% x VDD. Output load (C <sub>L</sub> ) =7pF, NSG-option                                                                                |         |             | 2.3          | ns                |

| Fall Time               | FT                                                                                                              | 80% to 20% x VDD. Output load (C <sub>L</sub> ) =7pF, NSG-option                                                                                |         |             | 2.3          | ns                |

| Duty Cycle              | DC                                                                                                              | Clock output duty cycle. Measured under 100MHz at VDD/2, $C_L$ =7pF                                                                             | 45      |             | 55           | %                 |

| Duty Cycle              |                                                                                                                 | Clock output duty cycle. Measured over 100MHz at VDD/2, C <sub>L</sub> =7pF                                                                     | 40      |             | 60           | %                 |

| Power-up time           | t <sub>on</sub>                                                                                                 | Output valid time after VDD meets the specified range&CE transition                                                                             | 50      | 100         | 400          | μs                |

| Period Jitter           | PJ <sub>RMS</sub>                                                                                               | Total RMS Period Jitter (including random and deterministic) <sup>1,2</sup>                                                                     |         | 3.5         |              | ps <sub>RMS</sub> |

| Cycle-cycle Jitter      | Cycle-cycle Jitter CJ The absolute value of max change in the periods of any 2 adjacent cycles <sup>1,2,4</sup> |                                                                                                                                                 |         |             | 50           | ps                |

| Phase Noise             | PN                                                                                                              | 1MHz offset from carrier <sup>1,2</sup>                                                                                                         |         | -140        | -135         | dBc/Hz            |

Notes 1. Measured with a  $50\Omega$  to GND termination

<sup>2:</sup> Measured at 48MHz output frequency

<sup>3.</sup> The MM8202 will support continuous VDD operation from 1.62 to 3.6V. The device can be powered up with a supply voltage at any of the 3 main supply rails of 1.8V, 2.5V or 3.3V.

<sup>4.</sup> Measured over 1000 cycles per JEDEC standard 65

<sup>5.</sup> Electrical parameters are guaranteed by design and characterization over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

# Electrical Characteristics<sup>5</sup> [1.8V]

VDD=1.62V to 1.98V,  $T_A$ =0 to 70°C unless otherwise noted. Typical values are measured at VDD=1.8V,  $T_A$ =35°C

| Parameter               | Symbol            | Conditions                                                                                                                                      | Min     | Тур         | Max          | Units             |

|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------------|-------------------|

| ElectroStaticDischa rge | ESD               | Human Body Model, tested per JESD D22-A114                                                                                                      | 4000    |             |              | V                 |

| Supply Voltage          | VDD               | Normal Operation <sup>3</sup>                                                                                                                   | 1.62    | 1.8         | 1.98         | V                 |

| Input LOW level         | $V_{IL}$          | CE pin                                                                                                                                          | -0.3    |             | VDD*0.3      | V                 |

| Input HIGH level        | $V_{IH}$          | CE pin                                                                                                                                          | VDD*0.7 |             | VDD+0.3      | V                 |

| Supply Current          | IDD               | Active supply current, VDD=1.8V, T=35oC, no output load                                                                                         |         | 2.0         | 2.5          | mA                |

| Quiescent Current       | IDDQ              | CE=LOW, output disabled                                                                                                                         |         | 0.2         | 1            | μΑ                |

| Output LOW level        | $V_{OL}$          | I <sub>OL</sub> = -1.8mA                                                                                                                        |         |             | 0.3          | V                 |

| Output HIGH level       | V <sub>OH</sub>   | I <sub>OH</sub> = 1.8mA                                                                                                                         | VDD-0.3 |             |              | V                 |

| Output Frequency        | F <sub>OUT</sub>  | Factory Programmable.Contact IDT for frequencies not listed                                                                                     | 6       | 12,24,25,50 | 133          | MHz               |

| Frequency Stability     | F <sub>TOT</sub>  | Total Frequency Stability over temperature, supply variation, aging (1st year at 35oC), shock & vibration. "" device option, over 0-70°C range  |         |             | <u>+</u> 400 | ppm               |

|                         |                   | Total Frequency Stability over temperature, supply variation, aging (1st year at 35oC), shock&vibration. "R" device option, over -20-85°C range |         |             | <u>+</u> 400 | ppm               |

| Rise Time               | RT                | 20% to 80% x VDD. Output load (C <sub>L</sub> ) =4pF, NSG-option                                                                                |         |             | 2.75         | ns                |

| Fall Time               | FT                | 80% to 20% x VDD. Output load ( $C_L$ ) =4pF, NSG-option                                                                                        |         |             | 2.75         | ns                |

| Duty Cycle              | DC                | Clock output duty cycle. Measured at VDD/2, C <sub>L</sub> =4pF                                                                                 | 45      |             | 55           | %                 |

| Power-up time           | t <sub>on</sub>   | Output valid time after VDD meets the specified range&CE transition                                                                             | 50      | 100         | 400          | μs                |

| Period Jitter           | PJ <sub>RMS</sub> | Total RMS Period Jitter (including random and deterministic) <sup>1,2</sup>                                                                     |         | 3.5         |              | ps <sub>RMS</sub> |

| Cycle-cycle Jitter      | CJ                | The absolute value of max change in the periods of any 2 adjacent cycles <sup>1,2,4</sup>                                                       |         |             | 50           | ps                |

| Phase Noise             | PN                | 1MHz offset from carrier <sup>1,2</sup>                                                                                                         |         | -140        | -135         | dBc/Hz            |

Notes 1. Measured with a  $50\Omega$  to GND termination

- 2: Measured at 48MHz output frequency

- 3. The MM8202 will support continuous VDD operation from 1.62 to 3.6V. The device can be powered up with a supply voltage at any of the 3 main supply rails of 1.8V, 2.5V or 3.3V.

- 4. Measured over 1000 cycles per JEDEC standard 65

- 5. Electrical parameters are guaranteed by design and characterization over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

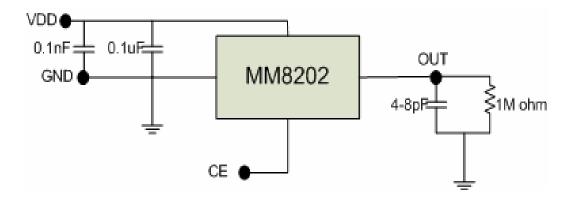

## **Application Diagram**

Below is a representative application diagram to evaluate the MM8202. For 50Ohm terminated measurements, a balun is necessary to provide proper impedance matching

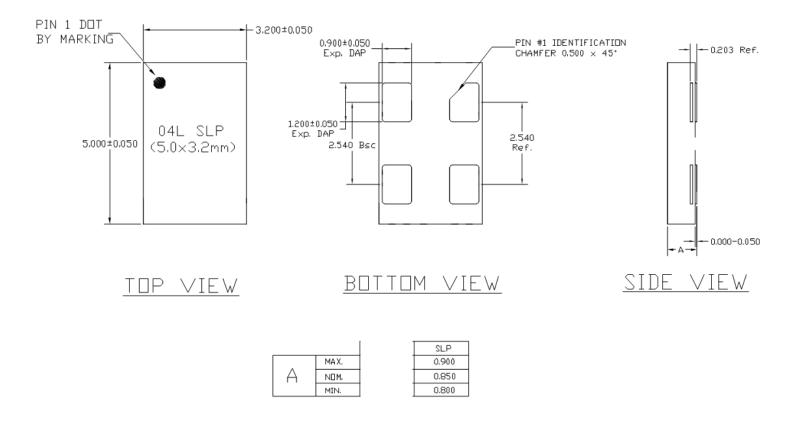

# **Package Outline and Package Dimensions**

Package Outline for NSG -5.0x3.2x0.9mm, 4-pin package:

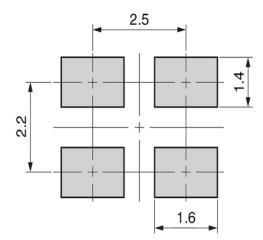

Below is the recommended PCB land pattern for the MM8202 NSG package:

## **Package Outline and Package Dimensions**

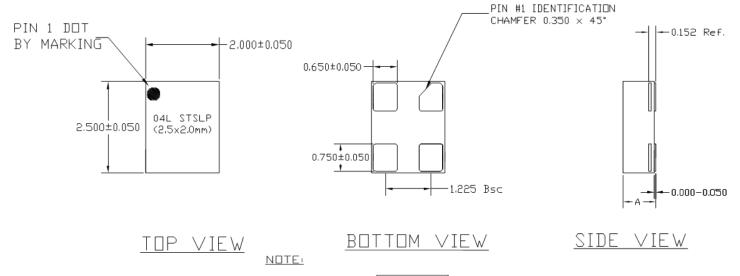

Package Outline for NVG -2.5x2.0x0.55mm, 4-pin package:

|      | STSLP |

|------|-------|

| MAX. | 0.600 |

| NDM. | 0.550 |

| MIN. | 0.500 |

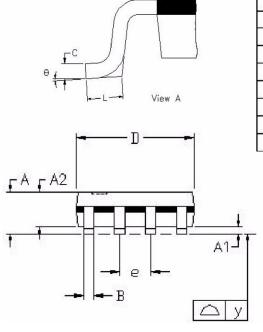

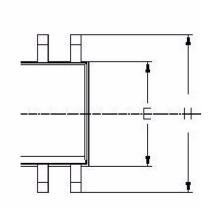

Package Outline for SOIC, 8-pin package:

0.015 X

| Service Control | MILLIMETERS |                                         |           |  |  |

|-----------------|-------------|-----------------------------------------|-----------|--|--|

| DIMS.           | MIN         | NOM                                     | MAX       |  |  |

| Α               | 1.35        | 1.B0                                    | 1.75      |  |  |

| A1              | 0.10        | 3-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2 | 0.25      |  |  |

| A2              | <u> </u>    | 1,45                                    | 100/20201 |  |  |

| В               | 0.33        |                                         | 0.51      |  |  |

| С               | 0.19        | 6. <del>776.66.6</del>                  | 0.25      |  |  |

| D               | 4.80        |                                         | 5.00      |  |  |

| Ε               | 3.80        |                                         | 4.00      |  |  |

| Ð               |             | 1.27                                    |           |  |  |

| Н               | 5.80        | 0.000                                   | 8.20      |  |  |

| L               | 0.40        | 37.7505033                              | 1.27      |  |  |

| У               |             | 60 <del>-30-20-20</del>                 | 0.10      |  |  |

| θ               | 0 Degree    | ·                                       | 8 degrees |  |  |

- 1. ALL DIMENSIONS IN MILLIMETER. (see Table for mils equivalent)

2. PACKAGE SURFACE FINISH: MATTE, CHARMILLES #24~27.

3. DIMENSION "D" DOES NOT INCLUDE MOLD FLASH, PROTRUSION.

- OR GATE BURRS.

4. DIMENSION "E" DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- TOLERANCE: +/- 0.1mm UNLESS OTHERWISE SPECIFIED.

- 6. OTHER DIMENSIONS FOLLOW ACCEPTABLE SPEC.

### Die Information:

MM8202 is offered in "wafer" form (-E, -D and -C package options) to be used in Chip-on-Board (CoB) and Multi-Chip-Package (MCP) designs. Please contact your IDT sales representative to obtain further information.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications, such as those requiring extended temperature ranges, high reliability or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

6024 Silver Creek Valley Road San Jose, California 95138 **Sales** 800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com Technical Support mobius@idt.com +408-739-5400

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

Copyright 2010. All rights reserved.