August 1986 Revised May 2000

# DM74S299 3-STATE 8-Bit Universal Shift/Storage Register

## **General Description**

This Schottky TTL eight-bit universal register features multiplexed inputs/outputs to achieve full eight bit data handling in a single 20-pin package. Two function-select inputs and two output-control inputs can be used to choose the modes of operation listed in the function table.

Synchronous parallel loading is accomplished by taking both function-select lines, S0 and S1, HIGH. This places the 3-STATE outputs in a high-impedance state, which permits data that is applied on the input/output lines to be clocked into the register. Reading out of the register can be accomplished while the outputs are enabled in any mode. A direct overriding input is provided to clear the register whether the outputs are ENABLED or OFF.

#### **Features**

- Multiplexed inputs/outputs provide improved bit density

- Four modes of operation:

Hold (Store) Shift Left

Shift Right Load Data

- 3-STATE outputs drive bus lines directly

- Can be cascaded for N-bit word lengths

- Operates with outputs enabled or at high Z

- Guaranteed shift (clock) frequency 50 MHz

- Typical power dissipation 700 mW

## **Ordering Code:**

|   | Order Number | Package Number | Package Description                                                   |

|---|--------------|----------------|-----------------------------------------------------------------------|

| ľ | DM74S299N    | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

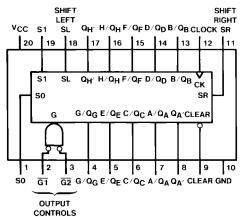

### **Connection Diagram**

© 2000 Fairchild Semiconductor Corporation

DS006485

www.fairchildsemi.com

## **Function Table**

|                |       |    |              | Inp            | uts            |       |    |      |                  |                   | In               | puts/0           | Outpu             | ts               |                  |                  | Out                        | puts     |

|----------------|-------|----|--------------|----------------|----------------|-------|----|------|------------------|-------------------|------------------|------------------|-------------------|------------------|------------------|------------------|----------------------------|----------|

| Mode           | Clear |    | ction<br>ect | Out<br>Con     | •              | Clock | Se | rial | A/Q <sub>A</sub> | B/Q <sub>B</sub>  | C/Q <sub>C</sub> | D/Q <sub>D</sub> | E/Q <sub>E</sub>  | F/Q <sub>F</sub> | G/Q <sub>G</sub> | H/Q <sub>H</sub> | $\mathbf{Q}_{\mathbf{A}'}$ | $Q_{H'}$ |

|                |       | S1 | S0           | G1<br>(Note 1) | G2<br>(Note 1) |       | SL | SR   |                  |                   |                  |                  |                   |                  |                  |                  |                            |          |

| Clear          | L     | Х  | L            | L              | L              | Χ     | Χ  | Χ    | L                | L                 | L                | L                | L                 | L                | L                | L                | L                          | L        |

|                | L     | L  | Χ            | L              | L              | Х     | Χ  | Χ    | L                | L                 | L                | L                | L                 | L                | L                | L                | L                          | L        |

| Hold           | Н     | L  | L            | L              | L              | Χ     | Χ  | Χ    | $Q_{A0}$         | $Q_{B0}$          | $Q_{C0}$         | $Q_{D0}$         | $Q_{E0}$          | $Q_{F0}$         | $Q_{G0}$         | Q <sub>H0</sub>  | $Q_{A0}$                   | $Q_{H0}$ |

|                | Н     | Х  | Χ            | L              | L              | L     | Χ  | Χ    |                  |                   |                  |                  |                   |                  |                  | $Q_{H0}$         | $Q_{A0}$                   | $Q_{H0}$ |

| Shift<br>Right | Н     | L  | Н            | L              | L              | 1     | Х  | Н    | Н                | Q <sub>An</sub>   | Q <sub>Bn</sub>  | Q <sub>Cn</sub>  | $Q_{Dn}$          | Q <sub>En</sub>  | Q <sub>Fn</sub>  | $Q_{Gn}$         | Н                          | $Q_{Gn}$ |

|                | Н     | L  | Н            | L              | L              | 1     | Χ  | L    | L                | $Q_{An}$          | $Q_{Bn}$         | $Q_Cn$           | $\mathbf{Q}_{Dn}$ | $Q_{En}$         | $Q_{Fn}$         | $Q_Gn$           | L                          | $Q_{Gn}$ |

| Shift<br>Left  | Н     | Н  | L            | L              | L              | 1     | Н  | Х    |                  |                   |                  | Q <sub>En</sub>  | Q <sub>Fn</sub>   | $Q_{Gn}$         | Q <sub>Hn</sub>  | Н                | Q <sub>Bn</sub>            |          |

|                | Н     | Н  | L            | L              | L              | 1     | L  | Χ    | $Q_{Bn}$         | $\mathbf{Q}_{Cn}$ | $Q_Dn$           | $Q_{En}$         | $Q_{Fn}$          | $Q_Gn$           | $Q_{Hn}$         | L                | $Q_{Bn}$                   | L        |

| Load           | Н     | Н  | Н            | X              | X              | 1     | Χ  | Χ    | а                | b                 | С                | d                | е                 | f                | g                | h                | а                          | h        |

a...h = The level of the steady-state input at inputs A through H, respectively. These data are loaded into the flip-flops while the flip-flop outputs are isolated from the input/output terminals.

Note 1: When one or both output controls are HIGH the eight input/output terminals are disabled to the high-impedance state; however, sequential operation or clearing of the register is not affected

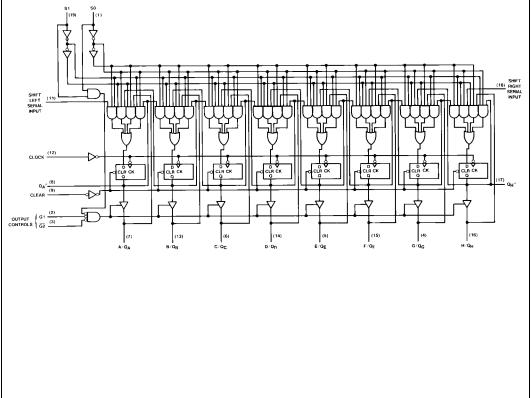

# **Logic Diagram**

www.fairchildsemi.com

H = HIGH Level

L = LOW Logic Level X = Either LOW or HIGH Logic Level

$Q_{A0}...Q_{H0}$  = The output logic level of  $Q_X$  before the indicated input conditions were established.

$Q_{An}...Q_{Hn}$  = The output logic level before the active transition (↑) of the clock input.

# **Absolute Maximum Ratings**(Note 2)

Supply Voltage 7V Input Voltage 5.5V Operating Free Air Temperature Range  $0^{\circ}$ C to +70°C Storage Temperature Range  $-65^{\circ}$ C to +150°C

Note 2: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# **Recommended Operating Conditions**

| Symbol           | Parameter                                                      |                | Min  | Nom  | Max  | Units |

|------------------|----------------------------------------------------------------|----------------|------|------|------|-------|

| V <sub>CC</sub>  | Supply Voltage                                                 |                | 4.75 | 5    | 5.25 | V     |

| V <sub>IH</sub>  | HIGH Level Input Voltage                                       |                | 2    |      |      | V     |

| V <sub>IL</sub>  | LOW Level Input Voltage                                        |                |      |      | 0.8  | V     |

| I <sub>OH</sub>  | HIGH Level Output Current (QA thru Q                           | ۱)             |      |      | -6.5 | mA    |

|                  | HIGH Level Output Current (QA', QH')                           |                |      | -0.5 | IIIA |       |

| I <sub>OL</sub>  | LOW Level Output Current (Q <sub>A</sub> thru Q <sub>H</sub>   | <sub>1</sub> ) |      |      | 20   | mA    |

|                  | HIGH Level Output Current (Q <sub>A'</sub> , Q <sub>H'</sub> ) |                |      |      | 6    | IIIA  |

| f <sub>CLK</sub> | Clock Frequency (Note 3)                                       |                | 0    | 70   | 50   | MHz   |

| f <sub>CLK</sub> | Clock Frequency (Note 4)                                       |                | 0    | 60   | 40   | MHz   |

| t <sub>W</sub>   | Pulse Width (Note 5)                                           | Clock HIGH     | 10   |      |      |       |

|                  |                                                                | Clock LOW      | 10   |      |      | ns    |

|                  |                                                                | Clear LOW      | 10   |      |      |       |

| t <sub>SU</sub>  | Setup Time (Note 6)(Note 5)(Note 7)                            | Select         | 15↑  |      |      |       |

|                  |                                                                | Data HIGH      | 7↑   |      |      | ns    |

|                  |                                                                | Data LOW       | 5↑   |      |      |       |

| t <sub>H</sub>   | Hold Time (Note 5)(Note 7)                                     | •              | 5↑   |      |      | ns    |

| t <sub>REL</sub> | Clear Release Time (Note 5)                                    |                | 10↑  |      |      | ns    |

| T <sub>A</sub>   | Free Air Operating Temperature                                 |                | 0    |      | 70   | °C    |

**Note 3:**  $C_L = 15 \text{ pF}, R_L = 280\Omega, T_A = 25^{\circ}\text{C} \text{ and } V_{CC} = 5\text{V}.$

Note 4:  $C_L = 50$  pF,  $R_L = 280\Omega$ ,  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

Note 5:  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

Note 6: The symbol  $(\uparrow)$  indicates the rising edge of the clock pulse is used for reference.

Note 7: Data includes the two serial inputs and the eight input/output data lines.

## **Electrical Characteristics**

over recommended operating free air temperature (unless otherwise noted)

| Symbol           | Parameter Conditions                          |                                              | s                                  | Min | Typ<br>(Note 8) | Max   | Units |

|------------------|-----------------------------------------------|----------------------------------------------|------------------------------------|-----|-----------------|-------|-------|

| VI               | Input Clamp Voltage                           | $V_{CC} = Min, I_I = -18 \text{ mA}$         |                                    |     | -1.2            | V     |       |

| V <sub>OH</sub>  | HIGH Level                                    | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max | Q <sub>A</sub> thru Q <sub>H</sub> | 2.4 | 3.2             |       | V     |

|                  | Output Voltage                                | $V_{IL} = Max, V_{IH} = Min$                 | $Q_{A'}, Q_{H'}$                   | 2.7 | 3.4             |       | v     |

| V <sub>OL</sub>  | LOW Level                                     | V <sub>CC</sub> = Min, I <sub>OL</sub> = Max | •                                  |     |                 | 0.5   | V     |

|                  | Output Voltage                                | $V_{IH} = Min, V_{IL} = Max$                 |                                    |     |                 |       | V     |

| I <sub>I</sub>   | Input Current @ Max Input Voltage             | $V_{CC} = Max, V_I = 5.5V$                   |                                    |     |                 | 1     | mA    |

| I <sub>IH</sub>  | HIGH Level                                    | V <sub>CC</sub> = Max                        | A thru H,                          |     |                 | 100   |       |

|                  | Input Current                                 | $V_I = 2.7V$                                 | S0, S1                             |     |                 |       | μΑ    |

|                  |                                               |                                              | Any Other                          |     |                 | 50    | 1     |

| I <sub>IL</sub>  | LOW Level                                     | V <sub>CC</sub> = Max                        | Clock, Clear                       |     |                 | -2    |       |

|                  | Input Current                                 | $V_I = 0.5V$                                 | S0, S1                             |     |                 | -0.5  | mA    |

|                  |                                               |                                              | Other                              |     |                 | -0.25 | 1     |

| I <sub>OZH</sub> | Off-State Output Current with                 | $V_{CC} = Max, V_O = 2.4V$                   |                                    |     |                 |       |       |

|                  | HIGH Level Output Voltage                     | $V_{IH} = Min, V_{IL} = Max$                 |                                    |     |                 | 100   | μΑ    |

|                  | Applied (Q <sub>A</sub> thru Q <sub>H</sub> ) |                                              |                                    |     |                 |       |       |

| I <sub>OZL</sub> | Off-State Output Current with                 | $V_{CC} = Max, V_O = 0.5V$                   |                                    |     |                 |       |       |

|                  | LOW Level Output Voltage                      | $V_{IH} = Min, V_{IL} = Max$                 |                                    |     |                 | -250  | μΑ    |

|                  | Applied (Q <sub>A</sub> thru Q <sub>H</sub> ) |                                              |                                    |     |                 |       |       |

| Ios              | Short Circuit Output                          | V <sub>CC</sub> = Max                        |                                    | -40 |                 | -100  |       |

|                  | Current (Q <sub>A</sub> thru Q <sub>H</sub> ) | (Note 10)                                    |                                    | -40 |                 | -100  | mA    |

|                  | Short Circuit Output                          | V <sub>CC</sub> = Max                        |                                    | -20 |                 | 100   | mA    |

|                  | Current (Q <sub>A'</sub> , Q <sub>H'</sub> )  | (Note 10)                                    |                                    | -20 |                 | -100  |       |

| I <sub>CC</sub>  | Supply Current                                | V <sub>CC</sub> = Max                        |                                    |     | 140             | 225   | mA    |

Note 8:  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

Note 9: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 10: Not more than one output should be shorted at a time, and the duration should not exceed one second.

## **Switching Characteristics**

at  $\text{V}_{CC} = 5\text{V}$  and  $T_A = 25^{\circ}\text{C}$  (See Section 1 for Test Waveforms and Output Load)

|                  | ol Parameter                                                 |                                               |                  |       |                        |     |       |

|------------------|--------------------------------------------------------------|-----------------------------------------------|------------------|-------|------------------------|-----|-------|

| Symbol           |                                                              | From (Input)                                  | C <sub>L</sub> = | 15 pF | C <sub>L</sub> = 50 pF |     | Units |

|                  |                                                              | To (Output)                                   | Min              | Max   | Min                    | Max |       |

| f <sub>MAX</sub> | Maximum Clock Frequency                                      | (Note 13)                                     | 50               |       | 40                     |     | MHz   |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output (Note 12) | Clock to Q <sub>A'</sub> or Q <sub>H'</sub>   |                  | 20    |                        | 22  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output (Note 12) | Clock to Q <sub>A</sub> ' or Q <sub>H</sub> ' |                  | 20    |                        | 23  | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output           | Clock to Q <sub>A</sub> thru Q <sub>H</sub>   |                  |       |                        | 21  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output           | Clock to Q <sub>A</sub> thru Q <sub>H</sub>   |                  |       |                        | 21  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output (Note 12) | Clear to Q <sub>A</sub> or Q <sub>H</sub>     |                  | 21    |                        | 24  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output           | Clear to Q <sub>A</sub> thru Q <sub>H</sub>   |                  |       |                        | 24  | ns    |

| t <sub>PZH</sub> | Output Enable Time to HIGH Level Output                      | G1, G2 to Q <sub>A</sub> thru Q <sub>H</sub>  |                  |       |                        | 18  | ns    |

| t <sub>PZL</sub> | Output Enable Time to LOW Level Output                       | G1, G2 to Q <sub>A</sub> thru Q <sub>H</sub>  |                  |       |                        | 18  | ns    |

| t <sub>PHZ</sub> | Output Disable Time to HIGH Level Output (Note 11)           | G1, G2 to Q <sub>A</sub> thru Q <sub>H</sub>  |                  | 12    |                        |     | ns    |

| t <sub>PLZ</sub> | Output Disable Time to LOW Level Output (Note 11)            | G1, G2 to Q <sub>A</sub> thru Q <sub>H</sub>  |                  | 12    |                        |     | ns    |

Note 11: C<sub>L</sub> = 5 pF.

Note 12:  $R_L = 1 K \Omega$  for delays measured to  ${\bf Q}_{A'}$  and  ${\bf Q}_{H'}.$

Note 13: For testing  $f_{\mbox{\scriptsize MAX}}$  all outputs are loaded simultaneously.

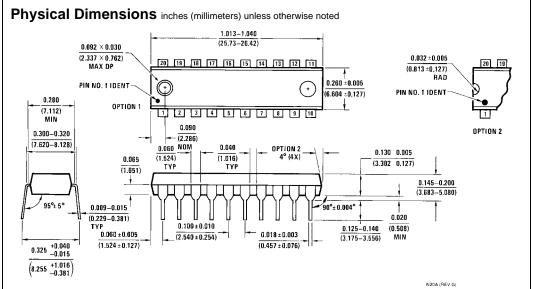

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N20A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

www.fairchildsemi.com