#### PRELIMINARY

# DS1543 64k NV Timekeeping RAM

#### www.dalsemi.com

### **FEATURES**

- Integrated NV SRAM, real time clock, crystal, power-fail control circuit and lithium energy source

- Clock registers are accessed identical to the static RAM. These registers are resident in the sixteen top RAM locations

- Totally nonvolatile with over 10 years of operation in the absence of power

- Precision Power-On Reset

- Programmable Watchdog Timer and RTC Alarm

- BCD coded year, month, date, day, hours, minutes, and seconds with automatic leap year compensation valid up to the year 2100

- Battery voltage level indicator flag

- Power-fail write protection allows for ±10%

Vcc power supply tolerance

- Lithium energy source is electrically disconnected to retain freshness until power is applied for the first time

#### **ORDERING INFORMATION**

DS1543-XXX

(5V) -70 70 ns access -100 100 ns access

\*DS1543W-XXX

(3.3V) -120 120 ns access -150 150 ns access

### **PIN ASSIGNMENT**

| RST<br>A12<br>A7<br>A6<br>A5<br>A4<br>A2<br>A1<br>A2<br>A1<br>A2<br>DQ0<br>DQ1<br>DQ2 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | 28 V <sub>CC</sub><br>27 WE<br>26 RQ/FT<br>25 A8<br>24 A9<br>23 A11<br>22 OE<br>21 A10<br>20 CE<br>19 DQ7<br>18 DQ6<br>17 DQ5<br>16 DQ4 |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| DQ2                                                                                   | 13                                                                | 16 🗖 DQ4                                                                                                                                |

| GND 🗆                                                                                 | 14                                                                | 15 🗆 DQ3                                                                                                                                |

28-Pin Encapsulated Package (700 Mil Extended)

#### **PIN DESCRIPTION**

| A0-A12          | - Address Input                                    |

|-----------------|----------------------------------------------------|

| DQ0-DQ7         | - Data Input/Outputs                               |

| IRQ\FT          | - Interrupt, Frequency Test<br>Output (Open-Drain) |

| RST             | - Power-On Reset Output<br>(Open-Drain)            |

| $\overline{CE}$ | - Chip Enable                                      |

| ŌĒ              | - Output Enable                                    |

| WE              | - Write Enable                                     |

| V <sub>CC</sub> | - Power Supply Input                               |

| GND             | - Ground                                           |

| NC              | - No Connection                                    |

#### DESCRIPTION

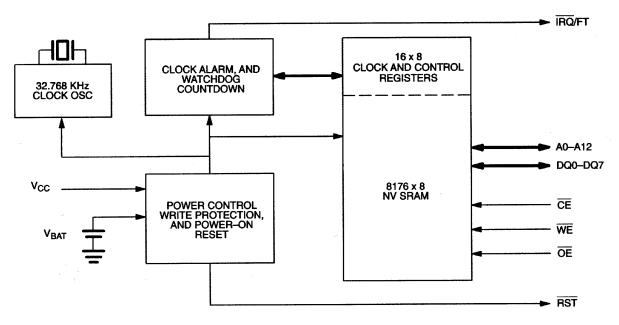

The DS1543 is a full-function real-time clock/calendar (RTC) with a RTC alarm, watchdog timer, poweron reset, battery monitor, and 8k x 8 non-volatile static RAM. User access to all registers within the DS1543 is accomplished with a bytewide interface as shown in Figure 1. The RTC registers contain year, month, date, day, hours, minutes, and seconds data in 24-hour BCD format. Corrections for day of month and leap year are made automatically.

The RTC registers are double-buffered into an internal and external set. The user has direct access to the external set. Clock/calendar updates to the external set of registers can be disabled and enabled to allow the user to access static data. Assuming the internal oscillator is turned on, the internal set of registers are continuously updated; this occurs regardless of external registers settings to guarantee that accurate RTC information is always maintained.

The DS1543 has interrupt ( $\overline{IRQ}/FT$ ) and reset ( $\overline{RST}$ ) outputs which can be used to control CPU activity. The  $\overline{IRQ}/FT$  interrupt output can be used to generate an external interrupt when the RTC register values match user programmed alarm values. The interrupt is always available while the device is powered from the system supply and can be programmed to occur when in the battery backed state to serve as a system wake-up. Either the  $\overline{IRQ}/FT$  or  $\overline{RST}$  outputs can also be used as a CPU watchdog timer, CPU activity is monitored and an interrupt or reset output will be activated if the correct activity is not detected within programmed limits. The DS1543 power-on reset can be used to detect a system power down or failure and hold the CPU in a safe reset state until normal power returns and stabilizes; the  $\overline{RST}$  output is used for this function.

The DS1543 also contains its own power fail circuitry which automatically deselects the device when the  $V_{CC}$  supply enters an out of tolerance condition. This feature provides a high degree of data security during unpredictable system operation brought on by low  $V_{CC}$  levels.

### PACKAGES

The DS1543 is available in two packages (28-pin DIP and 34-pin PowerCap module). The 28-pin DIP style module integrates the crystal, lithium energy source, and silicon all in one package. The 34-pin PowerCap module board is designed with contacts for connection to a separate PowerCap (DS9034PCX) that contains the crystal and battery. This design allows the Power-Cap to be mounted on top of the DS1543P after the completion of the surface mount process. Mounting the PowerCap after the surface mount process prevents damage to the crystal and battery due to the high temperatures required for solder reflow. The PowerCap is keyed to prevent reverse insertion. The PowerCap Module board and PowerCap are ordered separately and shipped in separate containers. The part number for the PowerCap is DS9034PCX.

### DS1543 BLOCK DIAGRAM Figure 1

#### DS1543 OPERATING MODES Table 1

| V <sub>CC</sub>      | CE              | ŌĒ              | WE              | DQ0-DQ7          | A0-A12          | MODE      | POWER        |

|----------------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------|--------------|

|                      | V <sub>IH</sub> | Х               | Х               | HIGH-Z           | Х               | DESELECT  | STANDBY      |

| In Tolerance         | V <sub>IL</sub> | Х               | V <sub>IL</sub> | D <sub>IN</sub>  | A <sub>IN</sub> | WRITE     | ACTIVE       |

| III Tolefance        | V <sub>IL</sub> | V <sub>IL</sub> | $V_{IH}$        | D <sub>OUT</sub> | A <sub>IN</sub> | READ      | ACTIVE       |

|                      | V <sub>IL</sub> | V <sub>IH</sub> | $V_{IH}$        | HIGH-Z           | A <sub>IN</sub> | READ      | ACTIVE       |

| $V_{BAT} < V_{CC} <$ | Х               | Х               | Х               | HIGH-Z           | Х               | DESELECT  | CMOS STANDBY |

| Tolerance            |                 |                 |                 |                  |                 |           |              |

| <v<sub>BAT</v<sub>   | X               | Х               | Х               | HIGH-Z           | Х               | DATA      | BATTERY      |

|                      |                 |                 |                 |                  |                 | RETENTION | CURRENT      |

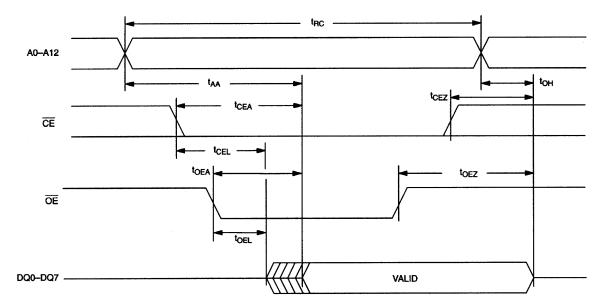

## DATA READ MODE

The DS1543 is in the read mode whenever  $\overline{CE}$  (chip enable) is low and  $\overline{WE}$  (write enable) is high. The device architecture allows ripple through access to any valid address location. Valid data will be available at the DQ pins within  $t_{AA}$  after the last address input is stable, providing that  $\overline{CE}$  and  $\overline{OE}$  access times are satisfied. If  $\overline{CE}$  or  $\overline{OE}$  access times are not met, valid data will be available at the latter of chip enable access ( $t_{CEA}$ ) or at output enable access time ( $t_{OEA}$ ). The state of the data input/output pins (DQ) is controlled by  $\overline{CE}$  and  $\overline{OE}$ . If the outputs are activated before  $t_{AA}$ , the data lines are driven to an intermediate state until  $t_{AA}$ . If the address inputs are changed while  $\overline{CE}$  and  $\overline{OE}$  remain valid, output data will remain valid for output data hold time ( $t_{OH}$ ) but will then go indeterminate until the next address access.

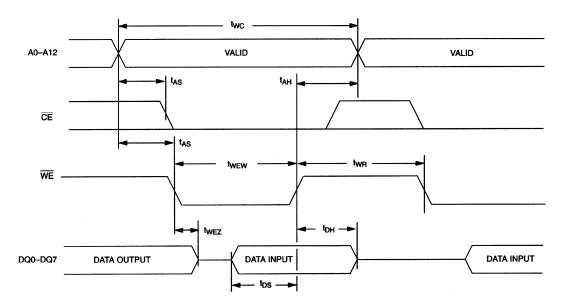

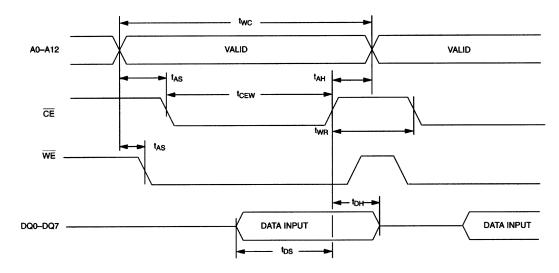

### DATA WRITE MODE

The DS1543 is in the write mode whenever  $\overline{WE}$  and  $\overline{CE}$  are in their active state. The start of a write is referenced to the latter occurring transition of  $\overline{WE}$  or  $\overline{CE}$ . The addresses must be held valid throughout the cycle.  $\overline{CE}$  and  $\overline{WE}$  must return inactive for a minimum of  $t_{WR}$  prior to the initiation of a subsequent read or write cycle. Data in must be valid  $t_{DS}$  prior to the end of the write and remain valid for  $t_{DH}$  afterward. In a typical application, the  $\overline{OE}$  signal will be high during a write cycle. However,  $\overline{OE}$  can be

active provided that care is taken with the data bus to avoid bus contention. If  $\overline{OE}$  is low prior to  $\overline{WE}$  transitioning low, the data bus can become active with read data defined by the address inputs. A low transition on  $\overline{WE}$  will then disable the outputs t<sub>WEZ</sub> after  $\overline{WE}$  goes active.

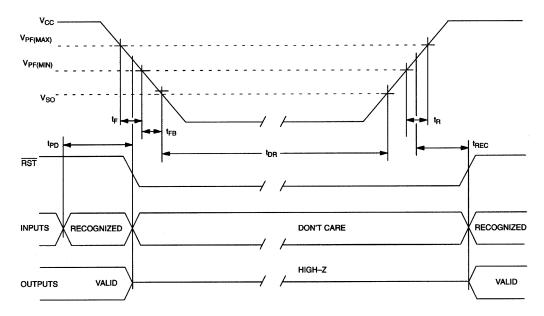

#### DATA RETENTION MODE

The 5-volt device is fully accessible and data can be written and read only when  $V_{CC}$  is greater than  $V_{PF}$ . However, when  $V_{CC}$  is below the power-fail point  $V_{PF}$  (point at which write protection occurs) the internal clock registers and SRAM are blocked from any access. When  $V_{CC}$  falls below the battery switch point  $V_{SO}$  (battery supply level), device power is switched from the  $V_{CC}$  pin to the internal backup lithium battery. RTC operation and SRAM data are maintained from the battery until  $V_{CC}$  is returned to nominal levels.

The 3.3-volt device is fully accessible and data can be written and read only when  $V_{CC}$  is greater than  $V_{PF}$ . When  $V_{CC}$  falls below  $V_{PF}$ , access to the device is inhibited. If  $V_{PF}$  is less than  $V_{BAT}$ , the device power is switched from  $V_{CC}$  to the internal backup lithium battery when  $V_{CC}$  drops below  $V_{PF}$  If  $V_{PF}$  is greater than  $V_{BAT}$ , the device power is switched from  $V_{CC}$  to the internal backup lithium battery when  $V_{CC}$  drops below  $V_{PF}$  If  $V_{PF}$  is greater than  $V_{BAT}$ , the device power is switched from  $V_{CC}$  to the internal backup lithium battery when  $V_{CC}$  drops below  $V_{BAT}$ . RTC operation and SRAM data are maintained from the battery until  $V_{CC}$  is returned to nominal levels.

All control, data, and address signals must be powered down when  $V_{CC}$  is powered down.

### BATTERY LONGEVITY

The DS1543 has a lithium power source that is designed to provide energy for the clock activity, and clock and RAM data retention when the  $V_{CC}$  supply is not present. The capability of this internal power supply is sufficient to power the DS1543 continuously for the life of the equipment in which it is installed. For specification purposes, the life expectancy is 10 years at 25°C with the internal clock oscillator running in the absence of  $V_{CC}$  Each DS1543 is shipped from Dallas Semiconductor with its lithium energy source disconnected, guaranteeing full energy capacity. When  $V_{CC}$  is first applied at a level greater than  $V_{PF}$  the lithium energy source is enabled for battery backup operation. Actual life expectancy of the DS1543 will be much longer than 10 years since no internal battery energy is consumed when  $V_{CC}$  is present. In fact, in most applications, the life expectancy of the DS1543 will be approximately equal to the shelf life (expected useful life of the internal lithium battery with no load attached) of the battery which may prove to be as long as 20 years.

#### **INTERNAL BATTERY MONITOR**

The DS15433 constantly monitors the battery voltage of the internal batter. The Battery Low Flag (BLF) bit of the Flags register (B4 of 1FF0h) is not writable and should always be a 0 when read. If a 1 is ever present, an exhausted lithium energy source is indicated and both the contents of the RTC and RAM are questionable.

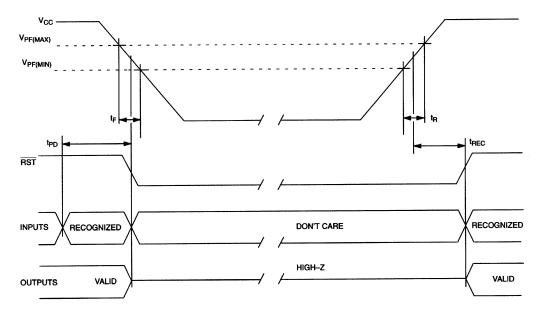

### **POWER-ON RESET**

A temperature-compensated comparator circuit monitors the level of  $V_{CC}$  When  $V_{CC}$  falls to the power fail trip point, the  $\overline{RST}$  signal (open-drain) is pulled low. When  $V_{CC}$  returns to nominal levels, the  $\overline{RST}$  signal continues to be pulled low for a period of 40 ms to 200 ms. The power-on reset function is independent of the RTC oscillator and thus is operational whether or not the oscillator is enabled.

## **CLOCK OPERATIONS**

Table 2 and the following paragraphs describe the operation of RTC, Alarm, and Watchdog functions.

#### DS1543 REGISTER MAP Table 2

| ADDDESS |                       |                |                       | DAT                   | 4                     |                       |                       |                |               |       |

|---------|-----------------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|---------------|-------|

| ADDRESS | <b>B</b> <sub>7</sub> | B <sub>6</sub> | <b>B</b> <sub>5</sub> | <b>B</b> <sub>4</sub> | <b>B</b> <sub>3</sub> | <b>B</b> <sub>2</sub> | <b>B</b> <sub>1</sub> | B <sub>0</sub> | FUNCTION/RAN  | GE    |

| 1FFFh   |                       | 10             | Year                  |                       |                       | YEA                   | R                     |                | YEAR          | 00-99 |

| 1FFEh   | Х                     | Х              | Х                     | 10 M                  |                       | MONT                  | ГН                    |                | MONTH         | 01-12 |

| 1FFDh   | X                     | X              | 10 I                  | Date                  |                       | DAT                   | Е                     |                | DATE          | 01-31 |

| 1FFCh   | X                     | FT             | Х                     | X                     | X                     |                       | DAY                   |                | DAY           | 01-07 |

| 1FFBh   | X                     | Х              | 10 H                  | OUR                   |                       | HOU                   | R                     |                | HOUR          | 00-23 |

| 1FFAh   | X                     | 1              | 0 MINUT               | ES                    |                       | MINUT                 | TES                   |                | MINUTES       | 00-59 |

| 1FF9h   | OSC                   | 10             | ) SECONI              | DS                    |                       | SECON                 | IDS                   |                | SECONDS       | 00-59 |

| 1FF8h   | W                     | R              | Y                     | Y                     | Y                     | Y                     | Y                     | Y              | CONTROL       |       |

| 1FF7h   | WDS                   | BMB4           | BMB3                  | BMB2                  | BMB1                  | BMB0                  | RB1                   | RB0            | WATCHDOG      |       |

| 1FF6h   | AE                    | Y              | ABE                   | Y                     | Y                     | Y                     | Y                     | Y              | INTERRUPTS    |       |

| 1FF5h   | AM4                   | Y              | 10 D                  | ATE                   |                       | DAT                   | Е                     |                | ALARM DATE    | 01-31 |

| 1FF4h   | AM3                   | Y              | 10 H0                 | OURS                  |                       | HOUF                  | RS                    |                | ALARM HOURS   | 00-23 |

| 1FF3h   | AM2                   | 1              | 0 MINUT               | ES                    |                       | MINUTES               |                       |                | ALARM MINUTES | 00-59 |

| 1FF2h   | AM1                   | 10             | ) SECONI              | DS                    | SECONDS               |                       |                       |                | ALARM SECONDS | 00-59 |

| 1FF1h   | Y                     | Y              | Y                     | Y                     | Y Y Y Y               |                       | UNUSED                |                |               |       |

| 1FF0h   | WF                    | AF             | 0                     | BLF                   | 0                     | 0                     | 0                     | 0              | FLAGS         |       |

X = Unused, read/writable under Write and Read bit control

FT = Frequency Test bit

$\overline{\text{OSC}}$  = Oscillator start/stop bit

W = Write bit

$\mathbf{R} = \mathbf{Read}$  bit

WDS = Watchdog Steering bit

BMB0-BMB4 = Watchdog Multiplier bits

RB0-RB1 = Watchdog Resolution bits

#### **CLOCK OSCILLATOR CONTROL**

#### AE = Alarm Flag Enable

Y = Unused, read/writable without Write and bit control

ABE = Alarm in battery Back-up mode enable

AM1-AM4 = Alarm Mask bits

WF = Watchdog Flag

AF = Alarm Flag

0 = "0" and are read only

BLF = Battery Low Flag

The Clock oscillator may be stopped at any time. To increase the shelf life of the backup lithium battery source, the oscillator can be turned off to minimize current drain from the battery. The  $\overline{OSC}$  bit is the MSB of the seconds register (B7 of 1FF9h). Setting it to a 1 stops the oscillator, setting to a 0 starts the oscillator. The DS1543 is shipped from Dallas Semiconductor with the clock oscillator turned off,  $\overline{OSC}$  bit set to a 1.

## **READING THE CLOCK**

When reading the RTC data, it is recommended to halt updates to the external set of double-buffered RTC registers. This puts the external registers into a static state allowing data to be read without register values changing during the read process. Normal updates to the internal registers continue while in this state. External updates are halted when a 1 is written into the read bit, B6 of the Control register (1FF8h). As long as a 1 remains in the Control register read bit, updating is halted. After a halt is issued, the registers reflect the RTC count (day, date, and time) that was current at the moment the halt command was issued. Normal updates to the external set of registers will resume within 1 second after the read bit is set to a 0.

## SETTING THE CLOCK

The 8<sup>th</sup> bit, B7 of the control register is the write bit. Setting the write bit to a 1, like the read bit, halts updates to the DS1543 (1FF8h-1FFFh) registers. After setting the write bit to a 1, RTC registers can be loaded with the desired RTC count (day, date, and time) in 24-hour BCD format. Setting the write bit to a 0 then transfers the values written to the internal RTC registers and allows normal operation to resume.

## **CLOCK ACCURACY (DIP MODULE)**

The DS1543 is guaranteed to keep time accuracy to within  $\pm 1$  minute per month at 25°C. The RTC is calibrated at the factory by Dallas Semiconductor using nonvolatile tuning elements. The DS1543 does not require additional calibration and, in most applications, temperature deviations will have a negligible effect on accuracy. For this reason, methods of field clock calibration are not available and not necessary. Attempts to calibrate the RTC that may be used with similar device types (M48T5x family) will not have any effect even though the DS1543 appears to accept calibration data.

## **CLOCK ACCURACY (POWERCAP MODULE)**

The DS1543 and DS9034PCX are each individually tested for accuracy. Once mounted together, the module is guaranteed to keep time accuracy to within  $\pm 1.53$  minutes per month (35 ppm) at 25°C.

## FREQUENCY TEST MODE

The DS1543 frequency test mode uses the open-drain  $\overline{IRQ}/FT$  output. With the oscillator running, the  $\overline{IRQ}/FT$  output will toggle at 512 Hz when the FT bit is a 1, the Alarm Flag Enable bit (AE) is a 0, and the Watchdog Steering bit (WDS) is a 1 or the Watchdog Register is reset (register 1FF7h = 00h). The  $\overline{IRQ}/FT$  output and the frequency test mode can be used as a measure of the actual frequency of the 32.768 kHz RTC oscillator. The  $\overline{IRQ}/FT$  pin is an open-drain output which requires a pullup resistor for proper operation. The FT bit is cleared to a 0 on power-up.

## USING THE CLOCK ALARM

The alarm settings and control for the DS1543 reside within registers 1FF2h - 1FF5h. Register 1FF6h contains two alarm enable bits: Alarm Enable (AE) and Alarm in Backup Enable (ABE). The AE and ABE bits must be set as described below for the  $\overline{IRQ}$ /FT output to be activated for a matched alarm condition.

The alarm can be programmed to activate on a specific day of the month or repeat every day, hour, minute, or second. It can also be programmed to go off while the DS1543 is in the battery-backed state of operation to serve as a system wake-up. Alarm mask bits AM1-AM4 control the alarm mode. Table 3 shows the possible settings. Configurations not listed in the table default to the once per second mode to notify the user of an incorrect alarm setting.

| AM4 | AM3 | AM2 | AM1 | ALARM RATE                                   |  |  |  |  |

|-----|-----|-----|-----|----------------------------------------------|--|--|--|--|

| 1   | 1   | 1   | 1   | Once per second                              |  |  |  |  |

| 1   | 1   | 1   | 0   | When seconds match                           |  |  |  |  |

| 1   | 1   | 0   | 0   | When minutes and seconds match               |  |  |  |  |

| 1   | 0   | 0   | 0   | When hours, minutes, and seconds match       |  |  |  |  |

| 0   | 0   | 0   | 0   | When date, hours, minutes, and seconds match |  |  |  |  |

## ALARM MASK BITS Table 3

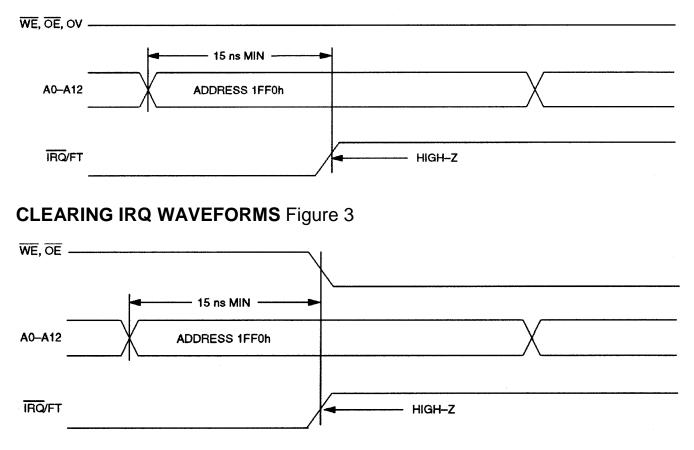

When the RTC register values match alarm register settings, the Alarm Flag bit (AF) is set to a 1. If Alarm Flag Enable (AE) is also set to a 1, the alarm condition activates the  $\overline{IRQ}/FT$  pin. The  $\overline{IRQ}/FT$  signal is cleared by a read or write to the Flags register (Address 1FF0h) as shown in Figure 2. The  $\overline{IRQ}/FT$  signal may be cleared by having the address stable for as short as 15 ns and either  $\overline{CE}$  or  $\overline{WE}$  active, but is not guaranteed to be cleared unless  $t_{RC}$  is fulfilled. The alarm flag is also cleared by a read or write to the Flags register, but the flag will not change states until the end of the read/write cycle and the  $\overline{IRQ}/FT$  signal has been cleared.

## CLEARING IRQ WAVEFORMS Figure 2

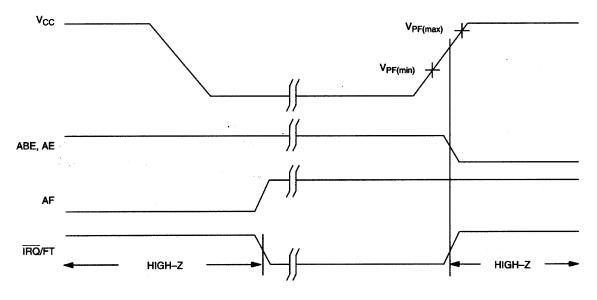

The  $\overline{IRQ}/FT$  pin can also be activated in the battery-backed mode. The  $\overline{IRQ}/FT$  will go low if an alarm occurs and both ABE and AE are set. The ABE and AE bits are cleared during the power-up transition, however an alarm generated during power-up will set AF. Therefore the AF bit can be read after system power-up to determine if an alarm was generated during the power-up sequence. Figure 4 illustrates alarm timing during the battery backup mode and power-up states.

### BACK-UP MODE ALARM WAVEFORMS Figure 4

#### **USING THE WATCHDOG TIMER**

The watchdog timer can be used to detect an out-of-control processor. The user programs the watchdog timer by setting the desired amount of time-out into the 8-bit Watchdog Register (Address 1FF7h). The five Watchdog Register bits BMB4-BMB0 store a binary multiplier and the two lower order bits RB1-RB0 select the resolution, where 00=1/16 second, 01=1/4 second, 10=1 second, and 11=4 seconds. The watchdog time-out value is then determined by the multiplication of the 5-bit multiplier value with the 2-bit resolution value. (For example: writing 00001110 in the watchdog Register = 3 X 1 second or 3 seconds). If the processor does not reset the timer within the specified period, the Watchdog Flag (WF) is set and a processor interrupt is generated and stays active until either the Watchdog Flag (WF) is read or the watchdog register (1FF7) is read or written.

The most significant bit of the Watchdog Register is the Watchdog Steering Bit (WDS). When set to a 0, the watchdog will activate the  $\overline{\text{IRQ}}$ /FT output when the watchdog times out.

When WDS is set to a 1, the watchdog will output a negative pulse on the  $\overline{\text{RST}}$  output for a duration of 40 ms to 200 ms. The Watchdog register (1FF7) and the FT bit will reset to a 0 at the end of a watchdog time-out when the WDS bit is set to a 1.

The watchdog timer resets when the processor performs a read or write of the Watchdog register. The time-out period then starts over. The watchdog timer is disabled by writing a value of 00h to the watchdog register. The watchdog function is automatically disabled upon power-up and the Watchdog register is cleared. If the watchdog function is set to output to the  $\overline{IRQ}$ /FT output and the frequency test function is activated, the watchdog function prevails and the frequency test function is denied.

#### **POWER-ON DEFAULT STATES**

Upon application of power to the device, the following register bits are set to 0: WDS=0, BMB0-BMB4=0, RB0-RB1=0, AE=0, ABE=0.

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground Operating Temperature Storage Temperature Soldering Temperature -5.0V to +6.0V 0°C to 70°C -55°C to +125°C 260°C for 10 seconds (DIP Package) (See Note 8) See IPC/JEDEC Standard J-STD-020A for Surface Mount Devices

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### **OPERATING RANGE**

| Range      | Temperature                      | V <sub>CC</sub>                  |

|------------|----------------------------------|----------------------------------|

| Commercial | $0^{\circ}$ C to $+70^{\circ}$ C | $3.3V \pm 10\%$ or $5V \pm 10\%$ |

| Industrial | -40°C to +85°C                   | $3.3V \pm 10\%$ or $5V \pm 10\%$ |

#### **RECOMMENDED DC OPERATING CONDITIONS** (Over the Operating Range)

| PARAMETER                  | SYMBOL            | MIN  | ТҮР | MAX                   | UNITS | NOTES |

|----------------------------|-------------------|------|-----|-----------------------|-------|-------|

| Logic 1 Voltage All Inputs |                   |      |     |                       |       |       |

| $V_{CC} = 5V \pm 10\%$     | V <sub>IH</sub>   | 2.2  |     | V <sub>CC</sub> +0.3V | V     | 1     |

| $V_{CC} = 3.3V \pm 10\%$   | $V_{\mathrm{IH}}$ | 2.0  |     | $V_{CC}$ +0.3V        | V     | 1     |

| Logic 0 Voltage All Inputs |                   |      |     |                       |       |       |

| $V_{CC} = 5V \pm 10\%$     | V <sub>IL</sub>   | -0.3 |     | 0.8                   |       | 1     |

| $V_{CC} = 3.3V \pm 10\%$   | V <sub>IL</sub>   | -0.3 |     | 0.6                   |       | 1     |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5.0V \pm 10\%)$

| $\frac{1}{\sqrt{CC}} = 3.00 \pm 100$                            |                  |      |                  |      |       |       |  |  |  |

|-----------------------------------------------------------------|------------------|------|------------------|------|-------|-------|--|--|--|

| PARAMETER                                                       | SYMBOL           | MIN  | ТҮР              | MAX  | UNITS | NOTES |  |  |  |

| Active Supply Current                                           | I <sub>CC</sub>  |      | 15               | 50   | mA    | 2, 3  |  |  |  |

| TTL Standby Current ( $\overline{CE} = V_{IH}$ )                | I <sub>CC1</sub> |      | 1                | 3    | mA    | 2, 3  |  |  |  |

| CMOS Standby Current                                            | I <sub>CC2</sub> |      | 1                | 3    | mA    | 2, 3  |  |  |  |

| $(\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2\text{V})$ |                  |      |                  |      |       |       |  |  |  |

| Input Leakage Current                                           | I <sub>IL</sub>  | -1   |                  | +1   | μΑ    |       |  |  |  |

| (any input)                                                     |                  |      |                  |      | -     |       |  |  |  |

| Output Leakage Current                                          | I <sub>OL</sub>  | -1   |                  | +1   | μA    |       |  |  |  |

| (any output)                                                    |                  |      |                  |      |       |       |  |  |  |

| Output Logic 1 Voltage                                          | V <sub>OH</sub>  | 2.4  |                  |      | V     | 1     |  |  |  |

| $(I_{OUT} = -1.0 \text{ mA})$                                   |                  |      |                  |      |       |       |  |  |  |

| Output Logic 0 Voltage                                          |                  |      |                  |      |       |       |  |  |  |

| $(I_{OUT} = 2.1 \text{ mA}, DQ0-7 \text{ Outputs})$             | V <sub>OL1</sub> |      |                  | 0.4  | V     | 1     |  |  |  |

| $(I_{OUT} = 10.0 \text{ mA}, \overline{IRQ}/FT \text{ and})$    | V <sub>OL2</sub> |      |                  | 0.4  | V     | 1, 5  |  |  |  |

| RST outputs)                                                    |                  |      |                  |      |       |       |  |  |  |

| Write Protection Voltage                                        | V <sub>PF</sub>  | 4.25 | 4.37             | 4.50 | V     | 1     |  |  |  |

| Battery Switch Over Voltage                                     | V <sub>SO</sub>  |      | V <sub>BAT</sub> |      | V     | 1, 4  |  |  |  |

| DC ELECTRICAL CHARAC                                            | C ELECTRICAL CHARACTERISTICS |      |                    |      |       |       |  |

|-----------------------------------------------------------------|------------------------------|------|--------------------|------|-------|-------|--|

| PARAMETER                                                       | SYMBOL                       | MIN  | ТҮР                | MAX  | UNITS | NOTES |  |

| Active Supply Current                                           | I <sub>CC</sub>              |      | 10                 | 30   | mA    | 2, 3  |  |

| TTL Standby Current ( $\overline{CE} = V_{IH}$ )                | I <sub>CC1</sub>             |      | 0.7                | 2    | mA    | 2, 3  |  |

| CMOS Standby Current                                            | I <sub>CC2</sub>             |      | 0.7                | 2    | mA    | 2, 3  |  |

| $(\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2\text{V})$ |                              |      |                    |      |       |       |  |

| Input Leakage Current (any input)                               | I <sub>IL</sub>              | -1   |                    | +1   | μA    |       |  |

| Output Leakage Current                                          | I <sub>OL</sub>              | -1   |                    | +1   | μA    |       |  |

| (any output)                                                    |                              |      |                    |      |       |       |  |

| Output Logic 1 Voltage                                          | V <sub>OH</sub>              | 2.4  |                    |      | V     | 1     |  |

| $(I_{OUT} = -1.0 \text{ mA})$                                   |                              |      |                    |      |       |       |  |

| Output Logic 0 Voltage                                          |                              |      |                    |      |       |       |  |

| (I <sub>OUT</sub> =2.1 mA, DQ0-7 Outputs)                       | V <sub>OL1</sub>             |      |                    | 0.4  | V     | 1     |  |

| $(I_{OUT} = 10.0 \text{ mA}, \overline{IRQ}/FT \text{ and})$    | V <sub>OL2</sub>             |      |                    | 0.4  | V     | 1, 5  |  |

| RST Outputs)                                                    |                              |      |                    |      |       |       |  |

| Write Protection Voltage                                        | V <sub>PF</sub>              | 2.80 | 2.88               | 2.97 | V     | 1     |  |

| Battery Switch Over Voltage                                     | V <sub>SO</sub>              |      | V <sub>BAT</sub>   |      | V     | 1, 4  |  |

|                                                                 |                              |      | or V <sub>PF</sub> |      |       |       |  |

# READ CYCLE TIMING DIAGRAM Figure 5

## **READ CYCLE, AC CHARACTERISTICS**

| $(V_{CC} = 5.0V \pm 10\%)$ |

|----------------------------|

|----------------------------|

|                                      |                  | 70 ns access |     | 100 ns access |     |       |       |

|--------------------------------------|------------------|--------------|-----|---------------|-----|-------|-------|

| PARAMETER                            | SYMBOL           | MIN          | MAX | MIN           | MAX | UNITS | NOTES |

| Read Cycle Time                      | t <sub>RC</sub>  | 70           |     | 100           |     | ns    |       |

| Address Access Time                  | t <sub>AA</sub>  |              | 70  |               | 100 | ns    |       |

| $\overline{CE}$ to DQ Low-Z          | t <sub>CEL</sub> | 5            |     | 5             |     | ns    |       |

| $\overline{CE}$ Access Time          | t <sub>CEA</sub> |              | 70  |               | 100 | ns    |       |

| $\overline{CE}$ Data Off time        | t <sub>CEZ</sub> |              | 25  |               | 35  | ns    |       |

| $\overline{\text{OE}}$ to DQ Low-Z   | t <sub>OEL</sub> | 5            |     | 5             |     | ns    |       |

| OE Access Time                       | t <sub>OEA</sub> |              | 35  |               | 55  | ns    |       |

| $\overline{\text{OE}}$ Data Off Time | t <sub>OEZ</sub> |              | 25  |               | 35  | ns    |       |

| Output Hold from Address             | t <sub>OH</sub>  | 5            |     | 5             |     | ns    |       |

## **READ CYCLE, AC CHARACTERISTICS**

$(V_{CC} = 3.3V \pm 10\%)$

|                                      |                  | 120 ns access |     | 150 ns access |     |       |       |

|--------------------------------------|------------------|---------------|-----|---------------|-----|-------|-------|

| PARAMETER                            | SYMBOL           | MIN           | MAX | MIN           | MAX | UNITS | NOTES |

| Read Cycle Time                      | t <sub>RC</sub>  | 120           |     | 150           |     | ns    | 5     |

| Address Access Time                  | t <sub>AA</sub>  |               | 120 |               | 150 | ns    | 5     |

| $\overline{CE}$ to DQ Low-Z          | t <sub>CEL</sub> | 5             |     | 5             |     | ns    | 5     |

| CE Access Time                       | t <sub>CEA</sub> |               | 120 |               | 150 | ns    | 5     |

| $\overline{CE}$ Data Off time        | t <sub>CEZ</sub> |               | 40  |               | 50  | ns    | 5     |

| OE to DQ Low-Z                       | t <sub>OEL</sub> | 5             |     | 5             |     | ns    | 5     |

| OE Access Time                       | t <sub>OEA</sub> |               | 100 |               | 130 | ns    | 5     |

| $\overline{\text{OE}}$ Data Off Time | t <sub>OEZ</sub> |               | 35  |               | 35  | ns    | 5     |

| Output Hold from Address             | t <sub>OH</sub>  | 5             |     | 5             |     | ns    | 5     |

### WRITE CYCLE, AC CHARACTERISTICS

| (V <sub>CC</sub> | = 5. | 0V | ±1( | 0%) |

|------------------|------|----|-----|-----|

|                                   |                  |              |     |               |     |       | • = • • / • / |

|-----------------------------------|------------------|--------------|-----|---------------|-----|-------|---------------|

|                                   |                  | 70 ns access |     | 100 ns access |     |       |               |

| PARAMETER                         | SYMBOL           | MIN          | MAX | MIN           | MAX | UNITS | NOTES         |

| Write Cycle Time                  | t <sub>WC</sub>  | 70           |     | 100           |     | ns    |               |

| Address Access Time               | t <sub>AS</sub>  | 0            |     | 0             |     | ns    |               |

| WE Pulse Width                    | t <sub>WEW</sub> | 50           |     | 70            |     | ns    |               |

| $\overline{\text{CE}}$ Pulse Time | t <sub>CEW</sub> | 60           |     | 75            |     | ns    |               |

| Data Setup Time                   | t <sub>DS</sub>  | 30           |     | 40            |     | ns    |               |

| Data Hold time                    | t <sub>DH</sub>  | 0            |     | 0             |     | ns    |               |

| Address Hold Time                 | t <sub>AH</sub>  | 5            |     | 5             |     | ns    |               |

| WE Data Off Time                  | t <sub>WEZ</sub> |              | 25  |               | 35  | ns    |               |

| Write Recovery Time               | t <sub>WR</sub>  | 5            |     | 5             |     | ns    |               |

## WRITE CYCLE, AC CHARACTERISTICS

$(V_{CC} = 3.3V \pm 10\%)$

|                             |                  | 120 ns access |     | 150 ns access |     |       |       |

|-----------------------------|------------------|---------------|-----|---------------|-----|-------|-------|

| PARAMETER                   | SYMBOL           | MIN           | MAX | MIN           | MAX | UNITS | NOTES |

| Write Cycle Time            | t <sub>WC</sub>  | 120           |     | 150           |     | ns    | 5     |

| Address Setup Time          | t <sub>AS</sub>  | 0             |     | 0             |     | ns    | 5     |

| WE Pulse Width              | t <sub>WEW</sub> | 100           |     | 130           |     | ns    | 5     |

| $\overline{CE}$ Pulse Width | t <sub>CEW</sub> | 110           |     | 140           |     | ns    | 5     |

| Data Setup Time             | t <sub>DS</sub>  | 80            |     | 90            |     | ns    | 5     |

| Data Hold Time              | t <sub>DH</sub>  | 0             |     | 0             |     | ns    | 5     |

| Address Hold Time           | t <sub>AH</sub>  | 0             |     | 0             |     | ns    | 5     |

| WE Data Off Time            | t <sub>WEZ</sub> |               | 40  |               | 50  | ns    | 5     |

| Write Recovery Time         | t <sub>WR</sub>  | 10            |     | 10            |     | ns    | 5     |

## WRITE CYCLE TIMING, WRITE ENABLE CONTROLLED Figure 6

## WRITE CYCLE TIMING, CHIP ENABLE CONTROLLED Figure 7

| POWER-UP/DOWN CHARACTERISTICS                                                              |                  |     |     |     | $(V_{CC} = 5.0V \pm 10\%)$ |       |  |  |

|--------------------------------------------------------------------------------------------|------------------|-----|-----|-----|----------------------------|-------|--|--|

| PARAMETER                                                                                  | SYMBOL           | MIN | ТҮР | MAX | UNITS                      | NOTES |  |  |

| $\overline{\text{CE}}$ or $\overline{\text{WE}}$ at V <sub>IH</sub> , Before<br>Power-Down | t <sub>PD</sub>  | 0   |     |     | μs                         |       |  |  |

| $V_{CC}$ Fall Time: $V_{PF(MAX)}$ to $V_{PF(Min)}$                                         | t <sub>F</sub>   | 300 |     |     | μs                         |       |  |  |

| $V_{CC}$ Fall Time: $V_{PF(MIN)}$ to $V_{SO}$                                              | t <sub>FB</sub>  | 10  |     |     | μs                         |       |  |  |

| V <sub>CC</sub> Rise Time: V <sub>PF(MIN)</sub> to<br>V <sub>PF(MAX)</sub>                 | t <sub>R</sub>   | 0   |     |     | μs                         |       |  |  |

| V <sub>PF</sub> to RST High                                                                | t <sub>REC</sub> | 40  |     | 200 | ms                         |       |  |  |

| Expected Data Retention Time<br>(Oscillator On)                                            | t <sub>DR</sub>  | 10  |     |     | years                      | 6, 7  |  |  |

# POWER-UP/DOWN WAVEFORM TIMING 5-VOLT DEVICE Figure 8

| <b>POWER-UP/DOWN CHARA</b>                                                                 | $(V_{CC} = 3.3V \pm 10\%)$ |     |     |     |       |       |

|--------------------------------------------------------------------------------------------|----------------------------|-----|-----|-----|-------|-------|

| PARAMETER                                                                                  | SYMBOL                     | MIN | ТҮР | MAX | UNITS | NOTES |

| $\overline{\text{CE}}$ or $\overline{\text{WE}}$ at V <sub>IH</sub> , Before<br>Power-Down | t <sub>PD</sub>            | 0   |     |     | μs    |       |

| $V_{CC}$ Fall Time: $V_{PF(MAX)}$ to $V_{PF(Min)}$                                         | t <sub>F</sub>             | 300 |     |     | μs    |       |

| $V_{CC}$ Rise Time: $V_{PF(MIN)}$ to $V_{PF(MAX)}$                                         | t <sub>R</sub>             | 0   |     |     | μs    |       |

| V <sub>PF</sub> to RST High                                                                | t <sub>REC</sub>           | 40  |     | 200 | ms    |       |

| Expected Data Retention Time<br>(Oscillator On)                                            | t <sub>DR</sub>            | 0   |     |     | years | 6, 7  |

# POWER-UP/DOWN WAVEFORM TIMING 3.3-VOLT DEVICE Figure 9

| CAPACITANCE                                                         |                 |     |     |     | (T    | <sub>A</sub> = 25°C) |

|---------------------------------------------------------------------|-----------------|-----|-----|-----|-------|----------------------|

| PARAMETER                                                           | SYMBOL          | MIN | ТҮР | MAX | UNITS | NOTES                |

| Capacitance on all input pins                                       | C <sub>IN</sub> |     |     | 7   | pF    | 1                    |

| Capacitance on $\overline{IRQ}/FT$ , $\overline{RST}$ , and DQ pins | C <sub>IO</sub> |     |     | 10  | pF    | 1                    |

## AC TEST CONDITIONS

Output Load: 100 pF + 1TTL Gate Input Pulse Levels: 0.0 to 3.0V Timing Measurement Reference Levels: Input: 1.5V Output: 1.5V Input Pulse Rise and Fall Times: 5 ns

### NOTES:

- 1. Voltage referenced to ground.

- 2. Typical values are at 25°C and nominal supplies.

- 3. Outputs are open.

- 4. Battery switch over occurs at the lower of either the battery voltage or  $V_{PF}$ .

- 5. The  $\overline{IRQ}$ /FT and  $\overline{RST}$  outputs are open-drain.

- 6. Data retention time is at 25°C.

- 7. Each DS1543 has a built-in switch that disconnects the lithium source until  $V_{CC}$  is first applied by the user. The expected  $t_{DR}$  is defined for DIP modules as a cumulative time in the absence of  $V_{CC}$  starting from the time power is first applied by the user.

- 8. Real Time Clock Modules (DIP) can be successfully processed through conventional wave-soldering techniques as long as temperature exposure to the lithium energy source contained within does not exceed +85°C. Post-solder cleaning with water washing techniques is acceptable, provided that ultrasonic vibration is not used.

In addition, for the PowerCap:

- a. Dallas Semiconductor recommends that PowerCap Module bases experience one pass through solder reflow oriented with the label side up ("live bug").

- b. Hand Soldering and touch-up: Do not touch or apply the soldering iron to leads for more than 3 seconds. To solder, apply flux to the pad, heat the lead frame pad and apply solder. To remove the part, apply flux, heat the lead frame pad until the solder reflow and use a solder wick to remove solder.

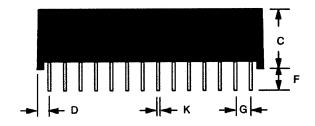

## DS1543 28-PIN PACKAGE

| PKG   | 28          | PIN   |  |  |

|-------|-------------|-------|--|--|

| DIM   | MIN         | MAX   |  |  |

| A IN. | 1.470       | 1.490 |  |  |

| MM    | 37.34       | 37.85 |  |  |

| B IN. | 0.675       | 0.740 |  |  |

| MM    | 17.75       | 18.80 |  |  |

| C IN. | 0.315       | 0.335 |  |  |

| MM    | 8.51        | 9.02  |  |  |

| D IN. | 0.075       | 0.105 |  |  |

| MM    | 1.91        | 2.67  |  |  |

| E IN. | 0.015       | 0.030 |  |  |

| MM    | 0.38        | 0.76  |  |  |

| F IN. | 0.140       | 0.180 |  |  |

| MM    | 3.56        | 4.57  |  |  |

| GIN.  | 0.090       | 0.110 |  |  |

| MM    | 2.29        | 2.79  |  |  |

| H IN. | 0.590       | 0.630 |  |  |

| MM    | 14.99       | 16.00 |  |  |

| J IN. | 0.010       | 0.018 |  |  |

| MM    | 0.25        | 0.45  |  |  |

| K IN. | 0.015 0.025 |       |  |  |

| MM    | 0.43 0.58   |       |  |  |