April 1984 Revised March 2000

# DM74AS373 Octal D-Type Transparent Latch with 3-STATE Outputs

## **General Description**

These 8-bit registers feature totem-pole 3-STATE outputs designed specifically for driving highly-capacitive or relatively low-impedance loads. The high-impedance state and increased high-logic-level drive provide these registers with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for interface or pull-up components. They are particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

The eight latches of the DM74AS373 are transparent D-type latches, meaning that while the enable (G) is HIGH the Q outputs will follow the data (D) inputs. When the enable is taken LOW the output will be latched at the level of the data that was set up.

A buffered output control input can be used to place the eight outputs in either a normal logic state (HIGH or LOW logic levels) or a high impedance state. In the high-impedance state the outputs neither load nor drive the bus lines significantly.

The output control does not affect the internal operation of the latches. That is, the old data can be retained or new data can be entered even while the outputs are OFF.

#### **Features**

- Switching specifications at 50 pF

- $\blacksquare$  Switching specifications guaranteed over full temperature and  $V_{CC}$  range

- Advanced oxide-isolated, ion-implanted Schottky TTL process

- Functionally and pin for pin compatible with LS and ALS TTL counterparts

- Improved AC performance over LS and ALS TTL counterparts

- 3-STATE buffer-type outputs drive bus lines directly

#### **Ordering Code:**

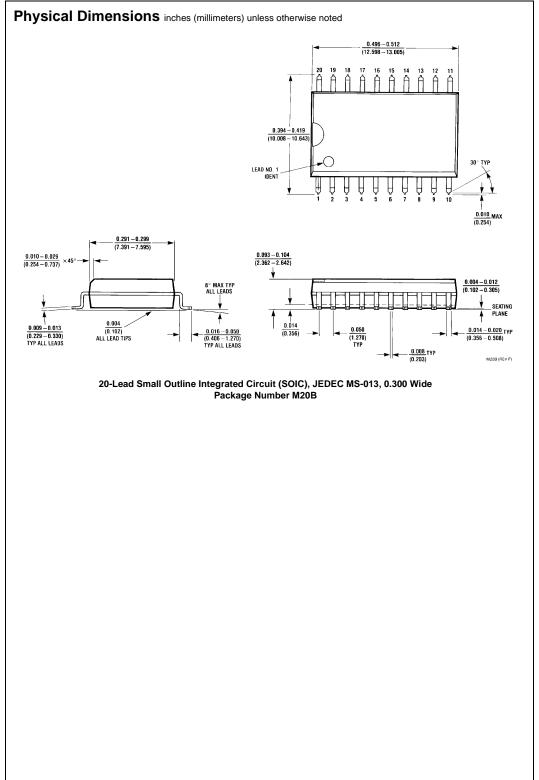

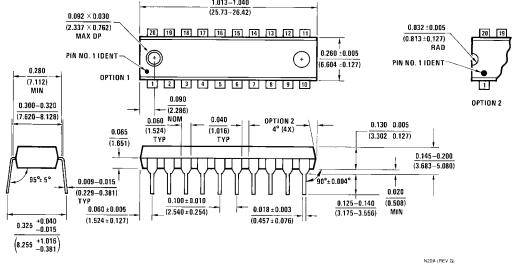

| Order Number | Package Number | Package Description                                                       |

|--------------|----------------|---------------------------------------------------------------------------|

| DM74AS373WM  | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

| DM74AS373N   | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0,300 Wide     |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

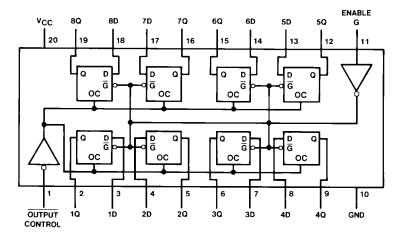

### **Connection Diagram**

© 2000 Fairchild Semiconductor Corporation

DS006309

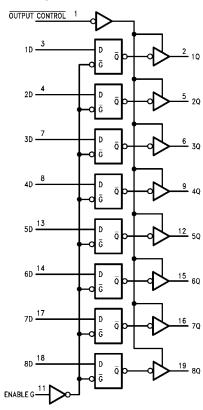

# **Logic Diagram**

# **Function Table**

| Output  | Enable |   | Output |

|---------|--------|---|--------|

| Control | G      | D | Q      |

| L       | Н      | Н | Н      |

| L       | Н      | L | L      |

| L       | L      | Χ | $Q_0$  |

| Н       | Χ      | Χ | Z      |

- L = LOW State

H = HIGH State

X = Don't Care

Z = High Impedance State

Q<sub>0</sub> = Previous Condition of Q

# **Absolute Maximum Ratings**(Note 1)

Supply Voltage 7V Input Voltage 7V Voltage Applied to Disabled Output 5.5V Operating Free Air Temperature Range  $0^{\circ}\text{C to } + 70^{\circ}\text{C}$

Operating Free Air Temperature Range  $0^{\circ}$ C to +70°C Storage Temperature Range  $-65^{\circ}$ C to +150°C

Typical  $\theta_{JA}$

N Package

52.5°C/W

M Package

70.5°C/W

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min | Nom | Max | Units |

|-----------------|--------------------------------|-----|-----|-----|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.5 | 5   | 5.5 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage       | 2   |     |     | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |     |     | 0.8 | V     |

| I <sub>ОН</sub> | HIGH Level Output Current      |     |     | -15 | mA    |

| I <sub>OL</sub> | LOW Level Output Current       |     |     | 48  | mA    |

| tw              | Width of Enable Pulse, HIGH    | 4.5 |     |     | ns    |

| t <sub>su</sub> | Data Setup Time (Note 2)       | 2↓  |     |     | ns    |

| t <sub>H</sub>  | Data Hold Time (Note 2)        | 3↓  |     |     | ns    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0   |     | 70  | °C    |

**Note 2:** The  $(\downarrow)$  arrow indicates the negative edge of the enable is used for reference.

### **Electrical Characteristics**

over recommended operating free air temperature range. All typical values are measured at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

| Symbol           | Parameter                          | Conditions                                                       |                  | Min                 | Тур  | Max  | Units |

|------------------|------------------------------------|------------------------------------------------------------------|------------------|---------------------|------|------|-------|

| V <sub>IK</sub>  | Input Clamp Voltage                | $V_{CC} = 4.5V$ , $I_I = -18 \text{ mA}$                         |                  |                     | -1.2 | V    |       |

| V <sub>OH</sub>  | HIGH Level Output                  | $V_{CC} = 4.5V$ , $I_{OH} = Max$                                 |                  | 2.4                 | 3.2  |      | V     |

|                  | Voltage                            | $I_{OH} = -2 \text{ mA}, V_{CC} = 4.5 \text{V to } 5.5 \text{V}$ | •                | V <sub>CC</sub> – 2 |      |      | v     |

| V <sub>OL</sub>  | LOW Level Output Voltage           | $V_{CC} = 4.5V$ , $I_{OL} = Max$                                 |                  | 0.35                | 0.5  | V    |       |

| I <sub>I</sub>   | Input Current at Max Input Voltage | $V_{CC} = 5.5V, V_{IH} = 7V$                                     |                  |                     | 0.1  | mA   |       |

| I <sub>IH</sub>  | HIGH Level Input Current           | $V_{CC} = 5.5V, V_{IH} = 2.7V$                                   |                  |                     | 20   | μΑ   |       |

| I <sub>IL</sub>  | LOW Level Input Current            | $V_{CC} = 5.5V, V_{IL} = 0.4V$                                   |                  |                     |      | -0.5 | mA    |

| Io               | Output Drive Current               | $V_{CC} = 5.5V, V_{O} = 2.25V$                                   |                  | -30                 |      | -112 | mA    |

| I <sub>OZH</sub> | OFF-State Output Current with      | $V_{CC} = 5.5V, V_{O} = 2.7V$                                    |                  |                     |      | 50   | μΑ    |

|                  | HIGH Level Voltage Applied         |                                                                  |                  |                     |      |      |       |

| I <sub>OZL</sub> | OFF-State Output Current with      | $V_{CC} = 5.5V, V_{O} = 0.4V$                                    |                  |                     |      | -50  | μΑ    |

|                  | LOW Level Voltage Applied          |                                                                  |                  |                     |      |      |       |

| I <sub>CC</sub>  | Supply Current                     | V <sub>CC</sub> = 5.5V                                           | Outputs HIGH     |                     | 55   | 90   |       |

|                  |                                    | Outputs Open                                                     | Outputs LOW      |                     | 55   | 85   | mA    |

|                  |                                    |                                                                  | Outputs Disabled |                     | 65   | 100  |       |

#### **Switching Characteristics** over recommended operating free air temperature range Conditions Min Symbol Parameter From То Max Units V<sub>CC</sub> = 4.5V to 5.5V Propagation Delay Time $t_{PLH}$ Any Q 3.5 6 Data LOW-to-HIGH Level Output $R_L = 500\Omega$ C<sub>L</sub> = 50 pF Propagation Delay Time $t_{\mathsf{PHL}}$ 6 Data Any Q 3.5 ns HIGH-to-LOW Level Output $t_{\mathsf{PLH}}$ Propagation Delay Time Enable Any Q ns LOW-to-HIGH Level Output $t_{PHL}$ Propagation Delay Time Any Q 7.5 Enable ns HIGH-to-LOW Level Output Output Enable Time Output $t_{PZH}$ Any Q 6.5 ns to HIGH Level Output Control $t_{PZL}$ Output Enable Time Output Any Q 4.5 9.5 ns to LOW Level Output Control Output Disable Time Output $t_{\text{PHZ}}$ Any Q 3 6.5 ns from HIGH Level Output Control $t_{PLZ}$ Output Disable Time Output Any Q from LOW Level Output Control

5

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N20A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com