# 74ABT3284 18-Bit Synchronous Datapath Multiplexer

# **General Description**

The 74ABT3284 is a synchronous datapath buffer designed to transmit four 9-bit bytes of data onto one or two 9-bit bytes in 2:1 or 4:1 multiplexed configurations. In addition, the non-inverting transceiver supports bidirectional data transfer in transparent or registered modes. A data byte from any one of the six ports can be stored during transparent operation for later recall. Data input to any port may also be read back to itself for byte manipulation or system self-diagnostic purposes.

The 74ABT3284 is useful for interleaving data in memory applications or for use in bus-to-bus communications where variations in data word length or construction are required.

- 18-bit 2:1 or 9-bit 4:1 multiplexed modes

- Registered or transparent datapath operation

- Output enables and select lines have the option of being synchronized for pipelined operation

- Independent input, output register and control synchronizing clocks insure maximum timing flexibility

- Independent control signals insure functional flexibility

- Guaranteed simultaneous switching noise level and dynamic threshold performance

- Guaranteed latchup protection

- High impedance glitch free bus loading during entire power up and power down cycle

- Non-destructive hot insertion capability

#### **Features**

■ Advanced BiCMOS technology provides high speed at low power consumption

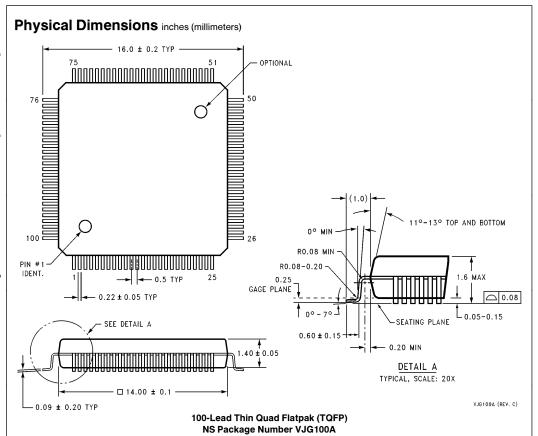

| Commercial   | Package Number | Package Description                                       |  |  |  |  |  |  |

|--------------|----------------|-----------------------------------------------------------|--|--|--|--|--|--|

| 74ABT3284VJG | VJG100A        | 100-Lead (14mm x 14mm) Molded Plastic Quad Flatpak, JEDEC |  |  |  |  |  |  |

# **Connection Diagram**

# Pin Assignment

| Pin |                                | Pin |                 | Pin |                | Pin |                 |  |

|-----|--------------------------------|-----|-----------------|-----|----------------|-----|-----------------|--|

| 1   | Mode_SO                        | 26  | V <sub>CC</sub> | 51  | CP_IN          | 76  | $V_{CC}$        |  |

| 2   | CP_AX                          | 27  | A <sub>8</sub>  | 52  | OEB            | 77  | D <sub>8</sub>  |  |

| 3   | OEC                            | 28  | A <sub>7</sub>  | 53  | LDBI           | 78  | $D_7$           |  |

| 4   | LDCI                           | 29  | A <sub>6</sub>  | 54  | LDBO           | 79  | D <sub>6</sub>  |  |

| 5   | LDCO                           | 30  | GND             | 55  | ModeW          | 80  | GND             |  |

| 6   | SA <sub>2</sub> X <sub>1</sub> | 31  | A <sub>5</sub>  | 56  | YSEL           | 81  | D <sub>5</sub>  |  |

| 7   | SA <sub>2</sub> X <sub>0</sub> | 32  | A <sub>4</sub>  | 57  | OEY            | 82  | $D_4$           |  |

| 8   | X <sub>0</sub>                 | 33  | A <sub>3</sub>  | 58  | Y <sub>8</sub> | 83  | $D_3$           |  |

| 9   | X <sub>1</sub>                 | 34  | A <sub>2</sub>  | 59  | Y <sub>7</sub> | 84  | D <sub>2</sub>  |  |

| 10  | GND                            | 35  | GND             | 60  | GND            | 85  | GND             |  |

| 11  | X <sub>2</sub>                 | 36  | A <sub>1</sub>  | 61  | Y <sub>6</sub> | 86  | D <sub>1</sub>  |  |

| 12  | X <sub>3</sub>                 | 37  | A <sub>0</sub>  | 62  | Y <sub>5</sub> | 87  | D <sub>0</sub>  |  |

| 13  | $X_4$                          | 38  | V <sub>CC</sub> | 63  | Y <sub>4</sub> | 88  | $V_{CC}$        |  |

| 14  | X <sub>5</sub>                 | 39  | B <sub>0</sub>  | 64  | Y <sub>3</sub> | 89  | C <sub>0</sub>  |  |

| 15  | X <sub>6</sub>                 | 40  | B <sub>1</sub>  | 65  | Y <sub>2</sub> | 90  | C <sub>1</sub>  |  |

| 16  | GND                            | 41  | GND             | 66  | GND            | 91  | GND             |  |

| 17  | X <sub>7</sub>                 | 42  | B <sub>2</sub>  | 67  | Y <sub>1</sub> | 92  | C <sub>2</sub>  |  |

| 18  | X <sub>8</sub>                 | 43  | B <sub>3</sub>  | 68  | Y <sub>0</sub> | 93  | C <sub>3</sub>  |  |

| 19  | OEX                            | 44  | B <sub>4</sub>  | 69  | LDDO           | 94  | C <sub>4</sub>  |  |

| 20  | XSEL <sub>0</sub>              | 45  | B <sub>5</sub>  | 70  | LDDI           | 95  | C <sub>5</sub>  |  |

| 21  | XSEL <sub>1</sub>              | 46  | GND             | 71  | ASEL1          | 96  | GND             |  |

| 22  | LDAO                           | 47  | B <sub>6</sub>  | 72  | ASEL0          | 97  | C <sub>6</sub>  |  |

| 23  | LDAI                           | 48  | B <sub>7</sub>  | 73  | OED            | 98  | C <sub>7</sub>  |  |

| 24  | OEA                            | 49  | B <sub>8</sub>  | 74  | CP_XA          | 99  | C <sub>8</sub>  |  |

| 25  | $V_{CC}$                       | 50  | V <sub>CC</sub> | 75  | Mode_SC        | 100 | V <sub>CC</sub> |  |

TRI-STATE® is a registered trademark of National Semiconductor Corporation

© 1995 National Semiconductor Corporation TL/F/11582

RRD-B30M125/Printed in U. S. A.

# **Functional Description**

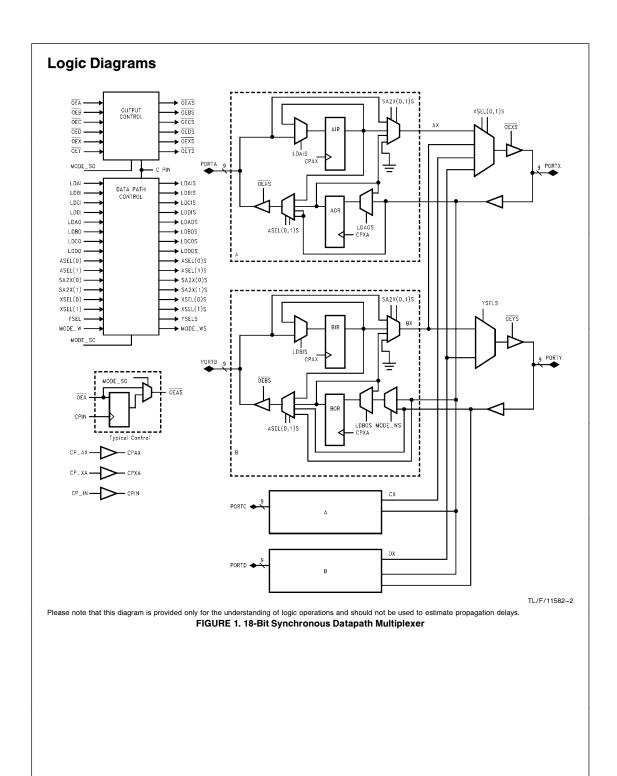

The 74ABT3284 is a bi-directional registered data-path routing device which can multiplex/de-multiplex four 9-bit "Aside" data ports (Ports A, B, C, D) onto/from one 9-bit "Xside" port (Port X). Alternatively, it can be configured for mux/demux of two 18-bit data paths (Ports A and C, B and D) onto/from one 18-bit data path (Ports X and Y).

Each of the six 9-bit I/O ports have independent active low TRI-STATE® output enable control logic which can be configured to operate asynchronously or synchronously. With MODE\_SO low, direct asynchronous output control is provided. With MODE\_SO high, output enable control is asserted synchronously on the positive edge of the CP\_IN clock. All I/O port inputs are continuously active allowing output state feedback.

The four A-side ports (A, B, C, D) contain independently enabled input and output data registers for storage of data passing in either direction. The input register (AIR, BIR, CIR, DIR) is loaded/held on the positive edge of CP\_AX when the respective Load Control pin (LDAI, LDBI, LDCI, LDDI) is asserted high/low. The Input Registers can be loaded with data from the corresponding A-side port. The output register (AOR, BOR, COR, DOR) is loaded/held on the positive edge of CP\_XA when the respective Load Control pin (LDAO, LDBO, LDCO, LDDO) is asserted high/low. The Output Registers can be loaded with data from Port X when MODE\_WS is asserted low. When MODE\_WS is asserted high, the Output Registers A and C can be loaded with Port X data and the B and D Output Registers can be loaded with data from Port Y.

When routing data from A-side to X-side, Data Path Control is provided for the following options via the SA2X inputs; Transparent mode where Input Register is bypassed but can simultaneously monitor A-side data; Registered Mode where X-side receives data from the selected Input Registers; Readback Mode where X-side receives data from the selected Output Registers. A-side data from Ports A, B, C, or D can be selected to Port X via the XSEL data path select inputs. Ports B or D can be selected to Port Y via the YSEL data path select input.

When routing data from X-side to A-side, Data Path Control is provided for the following options via the ASEL inputs; Transparent mode where Output Register is bypassed but can simultaneously monitor X-side data; Registered Mode where the A-side Port receives data from the corresponding Output Register; Readback Mode where the A-side Port receives data from the corresponding Input Registers. MODE\_WS asserted low selects Port X data to be passed to Ports A, B, C, and D. With MODE\_WS asserted high, Port X data is passed to Ports A and C with Port Y data passed to Ports B and D.

All Data Path Control Inputs and Input/Output Register Load Enable Inputs are active high and can be asserted asynchronously or synchronously. When MODE\_SC is low, these inputs operate asynchronously. When MODE\_SC is high, the inputs are asserted synchronously on the positive edge of the CP\_IN clock.

When operating the Data Path Control and/or the Output Enable Input groups with MODE\_SC and/or MODE\_SO "hard wired" high for synchronous mode, a single pre-clock of CP\_IN will be required following power-up to insure that all internal synchronous control registers are in the appropriate known state. If the application requires "on the fly" changes from asynchronous to synchronous operation, then the respective control/enable pin data must be pre-clocked via CP\_IN and held steady prior to and during any low to high transition of the MODE\_SO or MODE\_SC to properly initiate the sync control registers for synchronous control mode.

# **Pin Descriptions**

| Pin Name  | Description                                                    | Operation  |

|-----------|----------------------------------------------------------------|------------|

| OEa       | Output Enable Inputs<br>(Active Low)                           | Sync/Async |

| LDal      | Load Enable Inputs for the Input Registers                     | Sync/Async |

| LDaO      | Load Enable Inputs for the<br>Output Registers                 | Sync/Async |

| ASEL(0,1) | A-Side Data Path Select Inputs                                 | Sync/Async |

| SA2X(0,1) | X-Side Data Path Select Inputs                                 | Sync/Async |

| XSEL(0,1) | X-Port Data Path Select Inputs                                 | Sync/Async |

| YSEL      | Y-Port Data Path Select Input                                  | Sync/Async |

| MODE_W    | Word Mode Select Input for the X/Y to A-Side Direction         | Sync/Async |

| MODE_SO   | Enable Input for Synchronous<br>Output Enable Control          | Async      |

| MODE_SC   | Enable Input for Synchronous<br>Data Path Control              | Async      |

| CP_IN     | Clock Input for Synchronous<br>Control (Positive Edge Trigger) |            |

| CP_AX     | Clock Input for Input Registers (Positive Edge Trigger)        |            |

| CP_XA     | Clock Input for Output Registers (Positive Edge Trigger)       |            |

## **Function Tables**

#### **Output Enable Control Table**

| In                    | puts       |       | Outputs                  | Control |                                          |

|-----------------------|------------|-------|--------------------------|---------|------------------------------------------|

| OE (A, B, C, D, X, Y) | MODE_SO    | CP_IN | Port<br>A, B, C, D, X, Y | Mode    | Function                                 |

|                       |            |       | A, B, C, D, A, 1         |         |                                          |

| L                     | L          | Х     | ENABLE                   | ASYNC   | ENABLED OUTPUT, I/O input always active  |

| Н                     | L          | Х     | DISABLE                  | ASYNC   | DISABLED OUTPUT, I/O input always active |

| (Notes 2, 3)          | H (Note 1) |       | (Note 3)                 | SYNC    | (Note 3)                                 |

Note 1: Low to High transitions of MODE\_SO must be immediately preceded by a low to high transition (clock edge) on CP\_IN while holding Synchronous Control Inputs OE (A, B, C, D, X, Y) steady to preset internal registers and assure predictable operation during the control mode change from asynchronous to synchronous.

Note 2:  $\overline{\text{OE}}$  (A, B, C, D, X, Y) levels are synchronously asserted by the positive transition of CP\_IN when MODE\_SO is high.

Note 3: Synchronous Control Mode Functions are same as Asynchronous at time T + 1 of CP\_IN.

#### A Side Data Path Select Function Table

|              | Input        | ts         |       | Data P           | ath          | 0               |                                                                                      |  |

|--------------|--------------|------------|-------|------------------|--------------|-----------------|--------------------------------------------------------------------------------------|--|

| ASEL(1)      | ASEL(0)      | MODE_SC    | CP_IN | From<br>Reg/Port | To<br>Port   | Control<br>Mode | Function                                                                             |  |

| L            | L            | L          | X     | (A, B, C, D) IR  | A, B, C, D   | ASYNC           | Readback; Contents of Input Register (A, B, C, D) IR to Port (A, B, C, D)            |  |

| L            | Н            | L          | X     | (A, B, C, D) OR  | A, B, C, D   | ASYNC           | Clocked Path; Contents of Output<br>Register (A, B, C, D) OR to Port (A, B,<br>C, D) |  |

| Н            | L            | L          | Х     | Port X           | A, B, C, & D | ASYNC           | Transparent Path; Port X to Port A, B, C, & D                                        |  |

| Н            | Н            | L          | Х     | Port X           | A&C          | ASYNC           | Transparent Path; Port X to Port A & C                                               |  |

|              |              |            |       | Port Y           | B&D          |                 | Transparent Path; Port Y to Port B & D                                               |  |

| (Notes 2, 3) | (Notes 2, 3) | H (Note 1) |       | (Note 3)         | (Note 3)     | SYNC            | (Note 3)                                                                             |  |

Note 1: Low to High transitions of MODE\_SC must be immediately preceded by a low to high transition (clock edge) on CP\_IN while holding Synchronous Control Inputs ASEL(0) and ASEL(1) steady to preset internal registers and assure predictable operation during the control mode change from asynchronous to synchronous.

Note 2: ASEL(0) and ASEL(1) levels are synchronously asserted by the positive transition of CP\_IN when MODE\_SC is high.

Note 3: Synchronous Control Mode Functions are same as Asynchronous at time T + 1 of CP\_IN.

#### Input Register Control Table

|                      | Ir               | nputs      |       |          | Register        | Control | Function                                                                                      |  |

|----------------------|------------------|------------|-------|----------|-----------------|---------|-----------------------------------------------------------------------------------------------|--|

| Port<br>(A, B, C, D) | LD(A, B, C, D) I | MODE_SC    | CP_IN | CP_XA    | (A, B, C, D) IR | Mode    |                                                                                               |  |

| Х                    | L                | L          | Х     |          | HOLD            | ASYNC   | HOLD; Input Register holds previous state.                                                    |  |

| L (H)                | Н                | L          | Х     |          | L (H)           | ASYNC   | LOAD; Port A, B, C, D clocked to Input<br>Register (A, B, C, D) IR via CP_AX<br>positive edge |  |

| (Note 3)             | (Notes 2, 3)     | H (Note 1) |       | (Note 3) | (Note 3)        | SYNC    | (Note 3)                                                                                      |  |

Note 1: Low to High transitions of MODE\_SO must be immediately preceded by a low to high transition (clock edge) on CP\_IN while holding Synchronous Control Inputs LDAI, LDBI, LDCI, and LDDI steady to preset internal registers and assure predictable operation during the control mode change from asynchronous to synchronous.

Note 2: LDAI, LDBI, LDCI and LDDI levels are synchronously asserted by the positive transition of CP\_IN when MODE\_SC is high.

Note 3: Synchronous Control Mode Functions are same as Asynchronous at time T + 1 of CP\_IN.

# Function Tables (Continued)

## **Output Register Control Table**

|          |          |                  | Inputs       |            |       |          | Output I  | Register  | Control | Function                                        |

|----------|----------|------------------|--------------|------------|-------|----------|-----------|-----------|---------|-------------------------------------------------|

| Port X   | Port Y   | LD(A, B, C, D) O | MODE_W       | MODE_SC    | CP_IN | CP_XA    | (A, C) OR | (B, D) OR | Mode    | Function                                        |

| Х        | Х        | L                | Х            | L          | Х     |          | HOLD      | HOLD      | ASYNC   | HOLD<br>OR                                      |

| L (H)    | х        | н                | L            | L          | х     | <i></i>  | L (H)     | L (H)     | ASYNC   | LOAD<br>OR<br>Port X to<br>OR (A, B,<br>C, D)   |

| L (H)    | L (H)    | Н                | Н            | L          | Х     | 5        | L (H)     | L (H)     | ASYNC   | LOAD OR Port X to OR (A, C) Port Y to OR (B, D) |

| (Note 3) | (Note 3) | (Notes 2, 3)     | (Notes 2, 3) | H (Note 1) |       | (Note 3) | (Note 3)  | (Note 3)  | SYNC    | (Note 3)                                        |

Note 1: Low to High transitions of MODE\_SC must be immediately preceded by a low to high transition (clock edge) on CP\_IN while holding Synchronous Control Inputs LDAO, LDBO, LDCO, LDDO and MODE\_W steady to preset internal registers and assure predictable operation during the control mode change from asynchronous to synchronous.

Note 2: LDAO, LDBO, LDCO, LDDO and MODE\_W levels are synchronously asserted by the positive transition of CP\_IN when MODE\_SC is high.

Note 3: Synchronous Control Mode Functions are same as Asynchronous at time T + 1 of CP\_IN.

# Function Tables (Continued)

#### 1st Level X Side Data Path Select Function Table

| Inputs       |              |            |       | Data             | Path                | Control |                                                                                                |  |

|--------------|--------------|------------|-------|------------------|---------------------|---------|------------------------------------------------------------------------------------------------|--|

| SA2X(1)      | SA2X(0)      | MODE_SC    | CP_IN | From<br>Reg/Port | To<br>Internal Node | Mode    | Function                                                                                       |  |

| L            | L            | L          | X     | A, B, C, D       | (A, B, C, D) X      | ASYNC   | Transparent datapath from Port (A, B, C, D) to internal node (A, B, C, D) X                    |  |

| L            | Н            | L          | X     | (A, B, C, D) IR  | (A, B, C, D) X      | ASYNC   | Clocked Path; Contents of Input<br>Register (A, B, C, D) IR to internal<br>node (A, B, C, D) X |  |

| н            | L            | L          | X     | (A, B, C, D) OR  | (A, B, C, D) X      | ASYNC   | Readback; contents of Output<br>register (A, B, C, D) OR to internal<br>node (A, B, C, D) X    |  |

| Н            | Н            | L          | Х     | GND              | (A, B, C, D) X      | ASYNC   | Diagnostic; Select all 36 bits as low<br>and pass to the internal node (A,<br>B, C, D) X       |  |

| (Notes 2, 3) | (Notes 2, 3) | H (Note 1) |       | (Note 3)         | (Note 3)            | SYNC    | (Note 3)                                                                                       |  |

Note 1: Low to High transitions of MODE\_SC must be immediately preceded by a low to high transition (clock edge) on CP\_IN while holding Synchronous Control Inputs SA2X(0) and SA2X(1) steady to preset internal sync registers and assure predictable operation during the control mode change from asynchronous to synchronous.

Note 2: SA2X(0) and SA2X(1) levels are synchronously asserted by the positive transition of CP\_IN when MODE\_SC is high.

Note 3: Synchronous Control Mode Functions are same as Asynchronous at time T  $\,+\,$  1 of CP\_IN.

#### 2nd Level X Side Data Path Select Function Table for Port X

|              | Input        | ts         |       | Data Pa               | th         | Control | Function                   |  |

|--------------|--------------|------------|-------|-----------------------|------------|---------|----------------------------|--|

| XSEL(1)      | XSEL(0)      | MODE_SC    | CP_IN | From<br>Internal Node | To<br>Port | Mode    |                            |  |

| L            | L            | L          | Х     | AX                    | Х          | ASYNC   | Internal Node AX to Port X |  |

| L            | Н            | L          | Х     | BX                    | Х          | ASYNC   | Internal Node BX to Port X |  |

| Н            | L            | L          | Х     | CX                    | Х          | ASYNC   | Internal Node CX to Port X |  |

| Н            | Н            | L          | Х     | DX                    | Х          | ASYNC   | Internal Node DX to Port X |  |

| (Notes 2, 3) | (Notes 2, 3) | H (Note 1) |       | (Note 3)              | (Note 3)   | SYNC    | (Note 3)                   |  |

**Note 1:** Low to High transitions of MODE\_SC must be immediately preceded by a low to high transition (clock edge) on CP\_IN while holding Synchronous Control Inputs XSEL(0) and XSEL(1) steady to preset internal sync registers and assure predictable operation during the control mode change from asynchronous to synchronous.

Note 2: XSEL(0) and XSEL(1) levels are synchronously asserted by the positive transition of CP\_IN when MODE\_SC is high.

Note 3: Synchronous Control Mode Functions are same as Asynchronous at time T + 1 of CP\_IN.

### 2nd Level X Side Data Path Select Function Table for Port Y

| Inputs       |            |       | Data Pa            | th         | Control |                            |  |  |  |

|--------------|------------|-------|--------------------|------------|---------|----------------------------|--|--|--|

| YSEL         | MODE_SC    | CP_IN | From Internal Node | To<br>Port | Mode    | Function                   |  |  |  |

| L            | L          | Х     | BX                 | Υ          | ASYNC   | Internal Node BX to Port Y |  |  |  |

| Н            | L          | х     | DX                 | Υ          | ASYNC   | Internal Node DX to Port Y |  |  |  |

| (Notes 2, 3) | H (Note 1) |       | (Note 3)           | (Note 3)   | SYNC    | (Note 3)                   |  |  |  |

Note 1: Low to High transitions of MODE\_SC must be immediately preceeded by a low to high transition (clock edge) on CP\_IN while holding Synchronous Control Inputs YSEL steady to preset internal registers and assure predictable operation during the control mode change from asynchronous to synchronous.

Note 2: YSEL levels are synchronously asserted by the positive transition of CP\_IN when MODE\_SC is high.

Note 3: Synchronous Control Mode Functions are same as Asynchronous at time T + 1 of CP\_IN.

# Logic Diagrams (Continued) SA2X(0,1)S XSEL(0,1)S PORTX OEAS LDAOS CPXA ASEL(0,1)S PORT A Note: Port C configured identical to Port A. TL/F/11582-3 FIGURE 2. Synchronous Bus Multiplexer A-X Datapath XSEL(0,1)S SA2X(0,1)S LDBIS PORTB PORTX LDBOS MODE\_WS YSELS ASEL(0,1)S <del>OEYS</del> PORT B PORTY TL/F/11582-4 Note: Port D configured identical to Port B. FIGURE 3. Synchronous Bus Multiplexer B PORT Datapath

## **Absolute Maximum Ratings** (Note 1)

Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ Ambient Temperature under Bias  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

Junction Temperature under Bias

$\begin{array}{ll} \text{Ceramic} & -55^{\circ}\text{C to } +175^{\circ}\text{C} \\ \text{Plastic} & -55^{\circ}\text{C to } +150^{\circ}\text{C} \end{array}$

V<sub>CC</sub> Pin Potential to Ground Pin -0.5V to +7.0V Input Voltage (Note 2) -0.5V to +7.0V Input Current (Note 2) -30 mA to +5.0 mA

Voltage Applied to Any Output

% in the Disabled or Power-off State -0.5 V to +5.5 V in the HIGH STATE -0.5 V to  $V_{CC}$

Current Applied to Output

in LOW State (Max) twice the rated I<sub>OL</sub> (mA)

DC Latchup Source Current -300 mA

Over Voltage Latchup (I/O) 10V

**Note 1:** Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

# Recommended Operating Conditions

Free Air Ambient Temperature

Commercial  $-40^{\circ}\text{C to} + 85^{\circ}\text{C}$

Supply Voltage

Commercial +4.5V to +5.5V

## **DC Electrical Characteristics**

| Symbol                                | Parameter                                  |            | ABT328 | 4    | Units      | .,              | Conditions                                                                                 |  |  |

|---------------------------------------|--------------------------------------------|------------|--------|------|------------|-----------------|--------------------------------------------------------------------------------------------|--|--|

| Symbol                                | Parameter                                  | Min        | Тур    | Max  | Units      | V <sub>CC</sub> | Conditions                                                                                 |  |  |

| V <sub>IH</sub>                       | Input HIGH Voltage                         | 2.0        |        |      | V          |                 | Recognized HIGH Signal                                                                     |  |  |

| V <sub>IL</sub>                       | Input LOW Voltage                          |            |        | 0.8  | V          |                 | Recognized LOW Signal                                                                      |  |  |

| V <sub>CD</sub>                       | Input Clamp Voltage                        |            |        | -1.2 | V          | Min             | $I_{IN} = -18 \text{ mA}$                                                                  |  |  |

| V <sub>OH</sub>                       | Output HIGH Voltage                        | 2.5<br>2.0 |        |      | V          | Min             | $I_{OH} = -3 \text{ mA}$<br>$I_{OH} = -32 \text{ mA (Note 3)}$                             |  |  |

| V <sub>OL</sub>                       | Output LOW Voltage                         |            |        | 0.55 | V          | Min             | I <sub>OL</sub> = 64 mA (Note 4)                                                           |  |  |

| I <sub>IH</sub>                       | Input HIGH Current                         |            |        | 5    | μΑ         | Max             | $V_{IN} = V_{CC}$                                                                          |  |  |

| I <sub>BVI</sub>                      | Input HIGH Current<br>Breakdown Test       |            |        | 7    | μΑ         | Max             | V <sub>IN</sub> = 7.0V Control Inputs                                                      |  |  |

| I <sub>BVIT</sub>                     | Input HIGH Current<br>Breakdown Test (I/O) |            |        | 100  | μΑ         | Max             | $V_{IN} = 5.5V (A_n, B_n, C_n, D_n, X_n, Y_n)$                                             |  |  |

| I <sub>IL</sub>                       | Input LOW Current                          |            |        | -5   | μΑ         | Max             | V <sub>IN</sub> = 0.5V Control Inputs                                                      |  |  |

| V <sub>ID</sub>                       | Input Leakage Test                         | 4.75       |        |      | V          | 0.0             | $I_{ID}=1.9~\mu A$ Control Inputs All Data Pins Grounded                                   |  |  |

| I <sub>IH</sub> +<br>I <sub>OZH</sub> | Output Leakage Current                     |            |        | 50   | μΑ         | 0-5.5           | $V_{OUT} = 2.7V (A_n, B_n, C_n, D_n, X_n, Y_n)$<br>All Output Enables = 2.0V               |  |  |

| I <sub>IL</sub> +                     | Output Leakage Current                     |            |        | -50  | μΑ         | 0-5.5           | $V_{OUT} = 0.5V (A_n, B_n, C_n, D_n, X_n, Y_n)$<br>All Output Enables = 2.0V               |  |  |

| los                                   | Output Short-Circuit Current               | -100       |        | -275 | mA         | Max             | $V_{OUT} = 0.0V (A_n, B_n, C_n, D_n, X_n, Y_n) (Note 5)$                                   |  |  |

| I <sub>CEX</sub>                      | Output High Leakage Current                |            |        | 50   | μΑ         | Max             | $V_{OUT} = V_{CC} (A_n, B_n, C_n, D_n, X_n, Y_n)$                                          |  |  |

| I <sub>ZZ</sub>                       | Bus Drainage Test                          |            |        | 100  | μΑ         | 0.0             | $V_{OUT} = 5.5V (A_n, B_n, C_n, D_n, X_n, Y_n)$                                            |  |  |

| ICCH                                  | Power Supply Current                       |            |        | 2.5  | mA         | Max             | All Outputs HIGH                                                                           |  |  |

| I <sub>CCL</sub>                      | Power Supply Current                       |            |        | 140  | mA         | Max             | 36 Outputs LOW                                                                             |  |  |

| I <sub>CCZ</sub>                      | Power Supply Current                       |            |        | 2.5  | mA         | Max             | Output Enables = V <sub>CC</sub> ;<br>All Others at GND                                    |  |  |

| ICCT                                  | Additional I <sub>CC</sub> /Input          |            |        | 2.5  | mA         | Max             | V <sub>IN</sub> = V <sub>CC</sub> - 2.1V<br>All Others at V <sub>CC</sub> or GND           |  |  |

| ICCD                                  | Dynamic I <sub>CC</sub> No Load            |            |        | 0.35 | mA/<br>MHz | Max             | Outputs Open, Transparent Mode<br>Output Enables = GND<br>One Bit Toggling, 50% Duty Cycle |  |  |

Note 3: Up to 18 outputs can each source 32 mA continuously, or any combination of outputs can source up to a total of 324 mA. For example, 36 outputs can continuously each source 16 mA.

Note 4: Up to 18 outputs can each sink 64 mA continuously, or any combination of outputs can sink up to a total of 648 mA. For example, 36 outputs can continuously each sink 32 mA.

Note 5: One output at a time, duration 1 second maximum.

# DC Electrical Characteristics (Continued)

| Symbol           | Parameter                                    | Min  | Тур  | Max | Units | v <sub>cc</sub> |                                |

|------------------|----------------------------------------------|------|------|-----|-------|-----------------|--------------------------------|

| V <sub>OLP</sub> | Quiet Output Maximum Dynamic V <sub>OL</sub> |      | 0.7  | 1.0 | V     | 5.0             | T <sub>A</sub> = 25°C (Note 1) |

| V <sub>OLV</sub> | Quiet Output Minimum Dynamic VOL             | -0.8 | -0.5 |     | V     | 5.0             | T <sub>A</sub> = 25°C (Note 1) |

| V <sub>OHV</sub> | Minimum High Level Dynamic Output Voltage    | 2.5  | 3.0  |     | V     | 5.0             | T <sub>A</sub> = 25°C (Note 3) |

| V <sub>IHD</sub> | Minimum High Level Dynamic Input Voltage     | 2.0  | 1.7  |     | V     | 5.0             | T <sub>A</sub> = 25°C (Note 2) |

| V <sub>ILD</sub> | Maximum Low Level Dynamic Input Voltage      |      | 1.2  | 8.0 | V     | 5.0             | T <sub>A</sub> = 25°C (Note 2) |

Note 1: Max number of outputs defined as (n). n-1 data inputs are driven 0V to 3V. One output at LOW. Guaranteed, but not tested.

Note 2: Max number of data inputs (n) switching. n-1 inputs switching 0V to 3V. Input-under-test switching: 3V to the shold ( $V_{ILD}$ ), 0V to threshold ( $V_{IHD}$ ). Guaranteed, but not tested.

Note 3: Max number of outputs defined as (n). n-1 data inputs are driven 0V to 3V. One output HIGH. Guaranteed, but not tested.

# AC Electrical Characteristics Single Output Switching

| Symbol                               | Parameter                                                                                   | $74ABT$ $T_A = 25^{\circ}C$ $V_{CC} = 5.0V$ $C_L = 50 \text{ pF}$ |     | $74ABT$ $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ $V_{CC} = 4.5\text{V to } 5.5\text{V}$ $C_L = 50\text{pF}$ |     | Units |

|--------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------|-----|-------|

|                                      |                                                                                             |                                                                   |     |                                                                                                                        |     |       |

| $f_{MAX}$                            | Max Operating Frequency                                                                     | 150                                                               |     |                                                                                                                        |     |       |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay A, B, C, D or X<br>Inputs to X or A, B, C, D Outputs.<br>Transparent Mode | 1.5                                                               | 5.5 | 1.5                                                                                                                    | 5.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay B, D or Y Inputs to Y or B, D Outputs. Transparent Mode                   | 1.0                                                               | 5.0 | 1.0                                                                                                                    | 5.0 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay CP_XA ↑ to A, B, C, or D. Registered Mode                                 | 1.5                                                               | 6.0 | 1.5                                                                                                                    | 6.0 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay CP_AX ↑ to X. Registered Mode                                             | 1.5                                                               | 7.0 | 1.5                                                                                                                    | 7.0 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay CP_AX ↑ to Y. Registered Mode                                             | 1.5                                                               | 6.5 | 1.5                                                                                                                    | 6.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay ASELn to<br>A, B, C or D. Asynchronous Mode                               | 2.0                                                               | 7.5 | 2.0                                                                                                                    | 7.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay CP_IN↑ to<br>A, B, C or D. ASELn Synchronous Mode                         | 2.5                                                               | 8.5 | 2.5                                                                                                                    | 8.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay SA2Xn to X or Y. Asynchronous Mode                                        | 1.5                                                               | 7.5 | 1.5                                                                                                                    | 7.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay CP_IN↑ to X or Y. SA2Xn Synchronous Mode                                  | 2.0                                                               | 8.5 | 2.0                                                                                                                    | 8.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay XSELn to<br>X. Asynchronous Mode                                          | 1.5                                                               | 6.0 | 1.5                                                                                                                    | 6.0 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay CP_IN↑ to X. XSELn Synchronous Mode                                       | 2.0                                                               | 7.5 | 2.0                                                                                                                    | 7.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay YSELn to<br>Y. Asynchronous Mode                                          | 1.0                                                               | 5.5 | 1.0                                                                                                                    | 5.5 | ns    |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay CP_IN↑ to<br>Y. YSELn Synchronous Mode                                    | 1.5                                                               | 6.5 | 1.5                                                                                                                    | 6.5 | ns    |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Asynchronous Enable Time                                                                    | 1.0                                                               | 6.0 | 1.0                                                                                                                    | 6.0 | ns    |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Synchronous Enable Time                                                                     | 1.5                                                               | 7.0 | 1.5                                                                                                                    | 7.0 | ns    |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Asynchronous Disable Time                                                                   | 1.0                                                               | 7.5 | 1.0                                                                                                                    | 7.5 | ns    |

| t <sub>PHZ</sub>                     | Synchronous Disable Time                                                                    | 1.5                                                               | 8.5 | 1.5                                                                                                                    | 8.5 | ns    |

# AC Operating Requirements Single Output Switching

|                                          |                                                                                      | 74ABT                                                                     | 74ABT                                                                                                            | 1     |

|------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|

| Symbol                                   | Parameter                                                                            | T <sub>A</sub> = 25°C<br>V <sub>CC</sub> = 5.0V<br>C <sub>L</sub> = 50 pF | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ $V_{CC} = 4.5\text{V to } 5.5\text{V}$ $C_L = 50 \text{ pF}$ | Units |

|                                          |                                                                                      | Min                                                                       | Max                                                                                                              |       |

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup Time High or Low A, B, C, D X or Y. Data to CP_AX↑ or CP_XA↑ (Registered Mode) | 4.0                                                                       | 4.0                                                                                                              | ns    |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time High or Low A, B, C, D X or Y. Data to CP_AX↑ or CP_XA↑ (Registered Mode)  | 0.0                                                                       | 0.0                                                                                                              | ns    |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time High or Low Control Inputs to CP_IN ↑. (Synchronous Mode)                 | 3.0                                                                       | 3.0                                                                                                              | ns    |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time High or Low Control Inputs to CP_IN ↑. (Synchronous Mode)                  | 0.0                                                                       | 0.0                                                                                                              | ns    |

| t <sub>s</sub> (H)                       | Setup Time High, CP_IN↑ to CP_AX↑ or CP_XA↑.                                         | 5.0                                                                       | 5.0                                                                                                              | ns    |

| t <sub>h</sub> (L)                       | Hold Time Low, CP_IN ↑ to CP_AX ↑ or CP_XA ↑.                                        | 0.0                                                                       | 0.0                                                                                                              | ns    |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CLK Pulsewidth High<br>CLK Pulsewidth Low                                            | 3.0<br>4.0                                                                | 3.0<br>4.0                                                                                                       | ns    |

# Capacitance

| Symbol                    | Parameter         | Тур | Units | Conditions<br>T <sub>A</sub> = 25°C                                                                                       |  |

|---------------------------|-------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------|--|

| C <sub>IN</sub>           | Input Capacitance | 5   | pF    | V <sub>CC</sub> = 0V Control Inputs                                                                                       |  |

| C <sub>I/O</sub> (Note 1) | I/O Capacitance   | 11  | pF    | $V_{CC} = 5.0V$<br>(A <sub>n</sub> , B <sub>n</sub> , C <sub>n</sub> , D <sub>n</sub> , X <sub>n</sub> , Y <sub>n</sub> ) |  |

Note 1:  $C_{I/O}$  is measured at frequency f = 1 MHz, per MIL-STD-883B, Method 3012.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications