# PNX8510; PNX8511

Analog companion chip Rev. 04 – 12 January 2004

**Product data**

# 1. General description

The PNX8510; PNX8511 is an analog backend companion chip to digital ICs processing video and audio signals.

The primary difference between the PNX8510 and the PNX8511 is:

- PNX8510 includes the Macrovision<sup>™</sup> pay-per-view copy protection system

- PNX8511 does not include Macrovision<sup>™</sup>

PNX8510/11 provides two video encoders through two standardized D1 interfaces. The encoders can be bypassed to get direct access to the video DACs for higher resolution displays. PNX8510/11 also contains a sophisticated sync raster engine which can be utilized to generate various synchronization patterns for interlaced and non-interlaced image formats. The sync raster engine together with an up-sampling filter and a sync insertion unit compose a complete HDTV-capable data path including tri-level sync generation.

PNX8510/11 also provides two independent pairs of stereo audio DACs with two corresponding  $I^2S$ -bus interfaces.

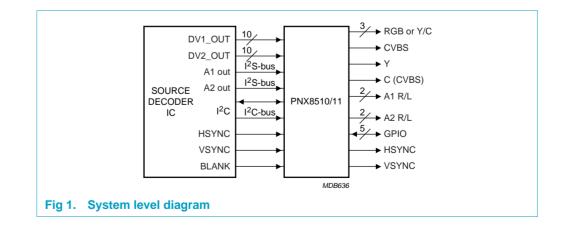

Figure 1 shows the PNX8510/11 with a typical source decoder.

# 2. Features

# 2.1 PNX8510

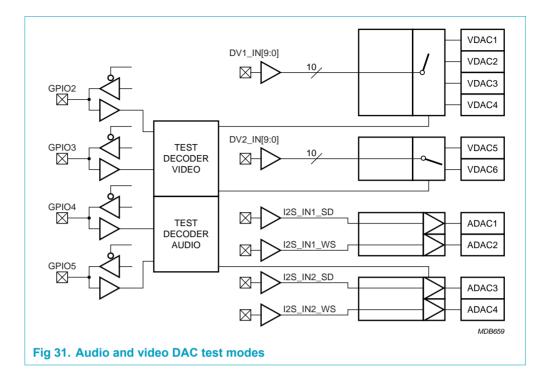

- Six 10-bit video DACs running at up to 135 MHz 1LSB DNL

- Four audio DACs arranged as two stereo pairs

- Two built-in digital video encoders

- PAL B/G, NTSC-M and SECAM encoding

- Two 10-bit D1 inputs with embedded VBI data

- Two I<sup>2</sup>S-bus independent audio input ports

- I<sup>2</sup>C-bus programmable (slave interface)

- Support for high resolution video out up to 81 MHz interface clock rate

- Support for input modes 2xD1, RGB, 1x 2D1 muxed, 24/30-bit RGB, DD1

- Programmable generation of embedded analog and external digital sync signals compliant to VESA and SMPTE 274 standards

- VBI encoding for standard definition video out

- Teletext insertion for PAL-WST, NTSC-WST, NABTS

- VPS video programming service encoding

- Closed caption encoding

- CGMS copy generation management system according to CPR-1204

- Internal color bar generator for standard definition video out

- JTAG-controlled test signals on video and audio converters

- Macrovision<sup>™</sup> pay-per-view copy protection system, rev. 7.1 (SCART support with Macrovision<sup>™</sup> copy protection on the RGB lines)

# 2.2 PNX8511

■ PNX8511 has all the features of PNX8510 with the exception of Macrovision<sup>™</sup>

# 3. Applications

- Digital Television

- Set-top Box

- Multimedia Applications

# 4. Ordering information

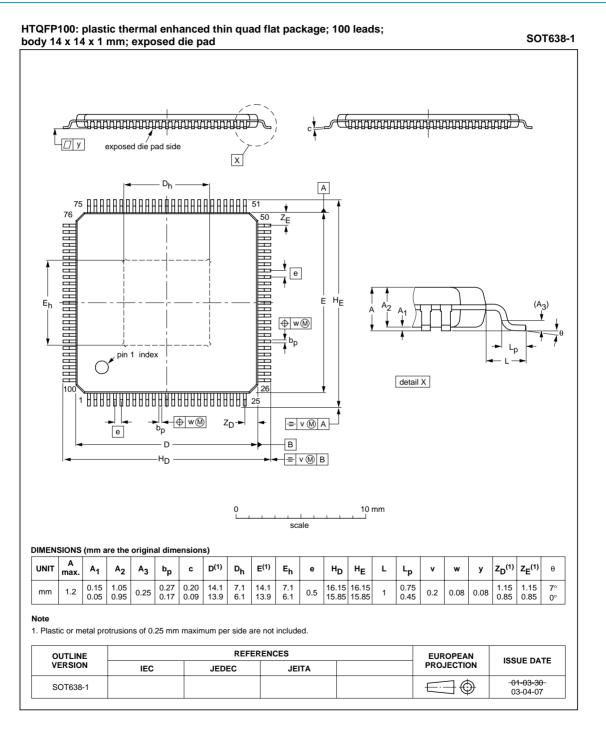

#### Table 1:Ordering information

| Type number  | Package  |                                                                                                  |          |  |  |

|--------------|----------|--------------------------------------------------------------------------------------------------|----------|--|--|

|              | Name     | Description                                                                                      | Version  |  |  |

| PNX8510HW/B1 | HTQFP100 | Plastic thermal enhanced thin quad flat package; 100 leads, body 14 x 14 x 1 mm, exposed die pad | SOT638-1 |  |  |

| PNX8511HW/B1 | HTQFP100 | Plastic thermal enhanced thin quad flat package; 100 leads, body 14 x 14 x 1 mm, exposed die pad | SOT638-1 |  |  |

# 5. Block diagram

# 6. Pinning information

# 6.1 Pin description

| Table 2: Pi            | n descript | ion  |                                   |

|------------------------|------------|------|-----------------------------------|

| Symbol                 | Pin        | Туре | Description                       |

| V <sub>DD(ADAC)</sub>  | 1          | -    | Audio DAC analog supply           |

| V <sub>SS(ADAC)</sub>  | 2          | -    | Audio DAC analog ground           |

| JTAG_RST               | 3          | -    | JTAG reset                        |

| RESET_N                | 4          | -    | Chip reset in signal (low active) |

| V <sub>SS(AUD)</sub>   | 5          | -    | Audio digital ground              |

| V <sub>SS(AUD)</sub>   | 6          | -    | Audio digital ground              |

| V <sub>DDD(ADAC)</sub> | 7          | -    | Audio DAC digital supply          |

| V <sub>SS</sub>        | 8          | -    | Digital ground                    |

| TEST1                  | 9          | I    | JTAG controller test data input   |

| TEST2                  | 10         | 0    | JTAG controller test data output  |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

| Table 2: Pin d         | escrip | tionc | ontinued                                             |

|------------------------|--------|-------|------------------------------------------------------|

| Symbol                 | Pin    | Туре  | Description                                          |

| TEST3                  | 11     | Ι     | JTAG controller test clock input                     |

| TEST4                  | 12     |       | JTAG controller test mode select input               |

| V <sub>SS</sub>        | 13     | -     | Digital ground                                       |

| V <sub>DD</sub>        | 14     | -     | Digital supply                                       |

| I2S_IN2_SCK            | 15     | I/O   | Bit clock IO for secondary audio channel             |

| I2S_IN2_WS             | 16     | I/O   | Word select IO for secondary audio channel           |

| I2S_IN2_SD             | 17     | I     | Serial data in for secondary audio channel           |

| V <sub>SS</sub>        | 18     | -     | Digital ground                                       |

| I2S_AOS2_CLK           | 19     | I     | Oversampling clock input for secondary audio channel |

| I2S_IN1_SCK            | 20     | I/O   | Bit clock IO for primary audio channel               |

| I2S_IN1_WS             | 21     | I/O   | Word select IO for primary audio channel             |

| I2S_IN1_SD             | 22     | I     | Serial data in for primary audio channel             |

| I2S_AOS1_CLK           | 23     | I     | Oversampling clock input for primary audio channel   |

| V <sub>SS</sub>        | 24     | -     | Digital ground                                       |

| V <sub>DD</sub>        | 25     | -     | Digital supply                                       |

| I2C_SDA                | 26     | I/O   | I <sup>2</sup> C data line (bi-directional)          |

| I2C_SCL                | 27     | I     | I <sup>2</sup> C clock line (input)                  |

| VSYNC_IN               | 28     | I     | Vertical sync input for primary video interface      |

| HSYNC_IN               | 29     | I     | Horizontal sync input for primary video interface    |

| BLANK_IN               | 30     | I     | Blanking input signal for primary video pipeline     |

| V <sub>SS</sub>        | 31     | -     | Digital ground                                       |

| VSYNC_OUT              | 32     | 0     | Vertical sync output for primary video pipeline      |

| HSYNC_OUT              | 33     | 0     | Horizontal sync output for primary video pipeline    |

| V <sub>DD</sub>        | 34     | -     | Digital supply                                       |

| V <sub>SS</sub>        | 35     | -     | Digital ground                                       |

| V <sub>DD</sub>        | 36     | -     | Digital supply                                       |

| V <sub>DDA(VDAC)</sub> | 37     | -     | Analog supply for video DACs                         |

| VOUT5                  | 38     | 0     | Video output for secondary channel, Y/CVBS-DAC       |

| IRTN2                  | 39     | -     | Current return path for C-DAC and CVBS/Y-DAC         |

| VOUT6                  | 40     | 0     | Video output for secondary channel, C-DAC            |

| RESET2                 | 41     | -     | Current setting resistor for secondary channel DACs  |

| V <sub>SSA(VDAC)</sub> | 42     | -     | Analog ground for video DACs                         |

| V <sub>DDA(VDAC)</sub> | 43     | -     | Analog supply for video DACs                         |

| VOUT1                  | 44     | 0     | Video output for primary video DAC 1 (CVBS/Y)        |

| V <sub>DDA(VDAC)</sub> | 45     | -     | Analog supply for video DACs                         |

| VOUT4                  | 46     | 0     | Video output for primary video DAC 4 (Blue)          |

| VOUT3                  | 47     | 0     | Video output for primary video DAC 3 (Y/Green)       |

| IRTN1                  | 48     | -     | Current return path for all primary channel DACs     |

| VOUT2                  | 49     | 0     | Video output for primary video DAC 2 (C/red)         |

| V <sub>DDA(VDAC)</sub> | 50     | -     | Analog supply for video DACs                         |

| RSET_DAC1              | 50     |       | Current setting resistor for primary channel DACs    |

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

| Table 2: Pin            | descript | t <mark>ion</mark> c | continued                                      |

|-------------------------|----------|----------------------|------------------------------------------------|

| Symbol                  | Pin      | Туре                 | Description                                    |

| n.c.                    | 52       | -                    | No connection (leave floating)                 |

| V <sub>SSA(VDAC)</sub>  | 53       | -                    | Analog ground for video DACs                   |

| V <sub>SS</sub>         | 54       | -                    | Digital ground                                 |

| V <sub>DD</sub>         | 55       | -                    | Digital supply                                 |

| DV_CLK1                 | 56       | -                    | Primary video interface clock                  |

| DV9_IN1                 | 57       | Ι                    | Primary video D1 input                         |

| DV8_IN1                 | 58       | Ι                    | Primary video D1 input                         |

| DV7_IN1                 | 59       | Ι                    | Primary video D1 input                         |

| DV6_IN1                 | 60       | Ι                    | Primary video D1 input                         |

| DV5_IN1                 | 61       | Ι                    | Primary video D1 input                         |

| DV4_IN1                 | 62       | I                    | Primary video D1 input                         |

| DV3_IN1                 | 63       | Ι                    | Primary video D1 input                         |

| DV2_IN1                 | 64       | Ι                    | Primary video D1 input                         |

| DV1_IN1                 | 65       | I                    | Primary video D1 input                         |

| DV0_IN1                 | 66       | I                    | Primary video D1 input                         |

| V <sub>SS</sub>         | 67       | -                    | Digital ground                                 |

| V <sub>DD</sub>         | 68       | -                    | Digital supply                                 |

| DV_CLK2                 | 69       | -                    | Secondary video interface clock                |

| DV9_IN2                 | 70       | I                    | Secondary video D1 input                       |

| DV8_IN2                 | 71       | I                    | Secondary video D1 input                       |

| DV7_IN2                 | 72       | I                    | Secondary video D1 input                       |

| DV6_IN2                 | 73       | I                    | Secondary video D1 input                       |

| DV5_IN2                 | 74       | I                    | Secondary video D1 input                       |

| DV4_IN2                 | 75       | I                    | Secondary video D1 input                       |

| DV3_IN2                 | 76       | I                    | Secondary video D1 input                       |

| DV2_IN2                 | 77       | I                    | Secondary video D1 input                       |

| DV1_IN2                 | 78       | I                    | Secondary video D1 input                       |

| DV0_IN2                 | 79       | I                    | Secondary video D1 input                       |

| V <sub>SS</sub>         | 80       | -                    | Digital ground                                 |

| V <sub>DD</sub>         | 81       | -                    | Digital supply                                 |

| V <sub>SS</sub>         | 82       | -                    | Digital ground                                 |

| V <sub>DD</sub>         | 83       | -                    | Digital supply                                 |

| GPIO1                   | 84       | I/O                  | General purpose input/output                   |

| GPIO2                   | 85       | I/O                  | General purpose input/output                   |

| GPIO3                   | 86       | I/O                  | General purpose input/output                   |

| GPIO4                   | 87       | I/O                  | General purpose input/output                   |

| GPIO5                   | 88       | I/O                  | General purpose input/output                   |

| V <sub>SS02(ADAC)</sub> | 89       | -                    | Audio DAC output buffer supply                 |

| V <sub>DD2(ADAC)</sub>  | 90       | -                    | Audio DAC supply                               |

| AOUT_R2                 | 91       | 0                    | Audio output for right secondary audio channel |

| V <sub>SS2(ADAC)</sub>  | 92       | -                    | Audio DAC ground                               |

# Table 0. Divide a singl

| Table 2:         Pin descriptioncontinued |     |      |                                               |  |

|-------------------------------------------|-----|------|-----------------------------------------------|--|

| Symbol                                    | Pin | Туре | Description                                   |  |

| V <sub>REF2(AUD)</sub>                    | 93  | -    | Audio DAC reference                           |  |

| V <sub>DD02(ADAC)</sub>                   | 94  | -    | Audio DAC output buffer supply                |  |

| AOUT_L2                                   | 95  | 0    | Audio output for left secondary audio channel |  |

| AOUT_R1                                   | 96  | 0    | Audio output for right primary audio channel  |  |

| V <sub>REF1(AUD)</sub>                    | 97  | -    | Audio DAC reference                           |  |

| V <sub>DDO1(ADAC)</sub>                   | 98  | -    | Audio DAC output buffer supply                |  |

| V <sub>SS1(ADAC)</sub>                    | 99  | -    | Audio DAC ground                              |  |

| AOUT_L1                                   | 100 | 0    | Audio output for left primary audio channel   |  |

|                                           |     |      |                                               |  |

# 7. Functional description

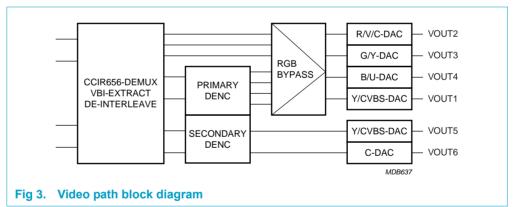

# 7.1 Video pipeline

The video pipeline contains two independent video channels. The primary channel is used to display graphic or video content on a standard television, CRT monitor or an HDTV system. The secondary video channel may connect to a VCR or a second standard TV for recording or secondary display purposes. No high definition or RGB output is available through the second video channel.

The two video pipelines are driven by two standard D1 interfaces, which can operate in various modes in 8 or 10-bit precision. The video modes are described below.

#### 7.1.1 Video modes

The video interfaces and sync raster engines are designed in a generic way. The only limiting factor is the data rate of the received video streams. All formats with a total interface speed requirement below 81 MHz can be displayed by the PNX8510/11.

Table 3:

Primary video channel standard interface modes

| Interface modes                    | Mode                            | Interface speed |

|------------------------------------|---------------------------------|-----------------|

| 4:4:4 RGB or YUV or YCrCb or YPrPb | 4:4:4 Muxed Components 10/8-bit | up to 81 MHz    |

| 4:2:2 YUV or YCrCb or YPrPb        | 4:2:2 Muxed components 10/8-bit | up to 81 MHz    |

#### Table 4: Primary video channel standard display modes

| Display modes                                                                                         | Mode                                                        | Interface<br>speed | Used data path |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------|----------------|

| PAL/NTSC/SECAM 4:2:2 YUV                                                                              | 4:2:2 Muxed components                                      | 27 MHz             | SD-CVBS-data   |

| i.e. PAL:                                                                                             | 10/8-bit                                                    |                    | path           |

| 864 pixel/line x 312.5 lines/field x 50Hz = 13.5 MHz/Y samples                                        |                                                             |                    |                |

| 6.75 MHz/U samples 6.75 MHz/V samples                                                                 |                                                             |                    |                |

| PAL/NTSC/SECAM RGB/YUV                                                                                | 4:2:2 Muxed components                                      | 27 MHz             | SD-CVBS and    |

| i.e. PAL:                                                                                             | 10/8-bit                                                    |                    | RGB/YUV        |

| 864 pixel/line x 312.5 lines/field x 50 Hz = 13.5 MHz/Y samples                                       |                                                             |                    | data paths     |

| 6.75 MHz/U samples 6.75 MHz/V samples                                                                 |                                                             |                    |                |

| 2FH PAL/NTSC/SECAM 4:4:4<br>RGB/YUV/YCrCb/YPrPb                                                       | 4:4:4 Muxed Components<br>10/8-bit                          | 81 MHz             | HD-data path   |

| i.e. PAL:                                                                                             |                                                             |                    |                |

| 864 pixel/line x 312.5 lines/field x 50 Hz x2 =<br>27 MHz/component                                   |                                                             |                    |                |

| 480P PAL/NTSC/SECAM 4:4:4<br>RGB/YUV/YCrCb/YPrPb                                                      | 4:4:4 Muxed Components<br>10/8-bit                          | 81 MHz             | HD-data path   |

| i.e. PAL:                                                                                             |                                                             |                    |                |

| 864 pixel/line x 625 lines/field x 50 Hz =<br>27 MHz/component                                        |                                                             |                    |                |

| Generic D1 mode; the interface clock can run up to 81                                                 | 4:4:4 Muxed components/                                     | up to              | HD-data path   |

| MHz, the components can have either 4:2:2 or 4:4:4 color resolution, but must be in the correct color | 4:2:2 Muxed components (use of both D1 interfaces required) | 81 MHz             |                |

| space.                                                                                                | 10/8-bit                                                    |                    |                |

| Table 5. Secondary video c  | namer standard interface modes  |                 |

|-----------------------------|---------------------------------|-----------------|

| Interface modes             | Mode                            | Interface speed |

| 4:2:2 YUV or YCrCb or YPrPb | 4:2:2 Muxed components 10/8-bit | 27 MHz          |

#### Table 6: 24/30-Bit RGB/YUV mode

Both D1 interfaces and the secondary audio channel are combined to provide high-speed direct access to video DACs

| Display/int                        | erface mode                        | Mode          | Interface<br>speed |

|------------------------------------|------------------------------------|---------------|--------------------|

| Pin assignment 24-bit mode         | Pin assignment 30-bit mode         |               |                    |

| 24/30-bit I                        | RGB/YUV <sup>[1]</sup>             | 24-bit direct | up to 81           |

| red[7] - I <sup>2</sup> S_IN2_SD   | red[9] - I <sup>2</sup> S_IN2_SD   | RGB/YUV       | MHz                |

| red[6] - I <sup>2</sup> S_IN2_WS   | red[8] - I <sup>2</sup> S_IN2_WS   | 8/10-bit      |                    |

| red[5] - I <sup>2</sup> S_IN2_SCK  | red[7] - I <sup>2</sup> S_IN2_SCK  |               |                    |

| red[4] - I <sup>2</sup> S_AOS2_CLK | red[6] - I <sup>2</sup> S_AOS2_CLK |               |                    |

| red[3] - DV_IN1[9]                 | red[5] - DV_IN1[9]                 |               |                    |

| red[2] - DV_IN1[8]                 | red[4] - DV_IN1[8]                 |               |                    |

| red[1] - DV_IN1[7]                 | red[3] - DV_IN1[7]                 |               |                    |

| red[0] - DV_IN1[6]                 | red[2] - DV_IN1[6]                 |               |                    |

|                                    | red[1] - GPIO[5]                   |               |                    |

| green[7] - DV_IN1[5]               | red[0] - GPIO[4]                   |               |                    |

| green[6] - DV_IN1[4]               |                                    |               |                    |

| green[5] - DV_IN1[3]               | green[9] - DV_IN1[5]               |               |                    |

| green[4] - DV_IN1[2]               | green[8] - DV_IN1[4]               |               |                    |

| green[3] - DV_IN1[1]               | green[7] - DV_IN1[3]               |               |                    |

| green[2] - DV_IN1[0]               | green[6] - DV_IN1[2]               |               |                    |

| green[1] - DV_IN2[9]               | green[5] - DV_IN1[1]               |               |                    |

| green[0] - DV_IN2[8]               | green[4] - DV_IN1[0]               | _             |                    |

|                                    | green[3] - DV_IN2[9]               |               |                    |

| blue[7] - DV_IN2[7]                | green[2] - DV_IN2[8]               |               |                    |

| blue[6] - DV_IN2[6]                | green[1] - GPIO[3]                 |               |                    |

| blue[5] - DV_IN2[5]                | green[0] - GPIO[2]                 |               |                    |

| blue[4] - DV_IN2[4]                |                                    |               |                    |

| blue[3] - DV_IN2[3]                | blue[9] - DV_IN2[7]                |               |                    |

| blue[2] - DV_IN2[2]                | blue[8] - DV_IN2[6]                |               |                    |

| blue[1] - DV_IN2[1]                | blue[7] - DV_IN2[5]                |               |                    |

| blue[0] - DV_IN2[0]                | blue[6] - DV_IN2[4]                | —             |                    |

|                                    | blue[5] - DV_IN2[3]                |               |                    |

|                                    | blue[4] - DV_IN2[2]                |               |                    |

|                                    | blue[3] - DV_IN2[1]                |               |                    |

|                                    | blue[2] - DV_IN2[0]                |               |                    |

|                                    | blue[1] - GPIO[1]                  |               |                    |

|                                    | blue[0] - DV_CLK2                  |               |                    |

[1] In case of the 24/30-bit full parallel input, no secondary audio channel is available.

#### Table 7: Single interface mode 2 (D1)

| Display/interface mode                                  | Mode           | Interface<br>speed |

|---------------------------------------------------------|----------------|--------------------|

| Single Interface Mode 2 (D1)                            | 2x muxed 4:2:2 | 54 MHz             |

| Accommodates 2 synchronous multiplexed D1 streams       | single D1      |                    |

| for low cost applications (both streams are extracted). | 8/10-bit       |                    |

#### Table 8: Interleaved interface mode

| Display/interface mode                                                                                                               | Mode                                               | Interface<br>speed                  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------|

| Interleaved interface mode                                                                                                           | 2x muxed 4:2:2                                     | 54 MHz or                           |

| Same formats as in single interface mode 1 and 2 but<br>only one of the two interleaved video streams is<br>extracted per interface. | single D1 or 2x<br>muxed 4:4:4<br>RGB/YUV 8/10-bit | 81 MHz or<br>pos-neg<br>edge 27 MHz |

| Selection of the extracted slice is possible by software,                                                                            |                                                    | (SAA7128<br>compliant)              |

| Usage of two PNX8510/11 chips possible to support up to 4 display/record devices                                                     |                                                    | compliant)                          |

#### Table 9: Combined double D1 mode

| Display/interface mode                                                                                                                      | Mode                      | Interface<br>speed     |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|

| Combined double D1 mode: <sup>[1]</sup> the two D1 interfaces are combined to carry a single HDTV stream in 4:2:2 YUV or 4:2:2 YPrPb format | 2 combined D1<br>8/10-bit | up to 81 MHz<br>per D1 |

| primary D1: Y channel                                                                                                                       |                           |                        |

| secondary D1: muxed UV or PrPb channel                                                                                                      |                           |                        |

| i.e.: 1920x1080 60 Hz interlaced                                                                                                            |                           |                        |

| 2200 pixel/line x 562.5 lines/field x 60 Hz = 74.25 MHz/Y samples                                                                           |                           |                        |

| 37.125 MHz/Cr/Pr samples                                                                                                                    |                           |                        |

| 37.125 MHz/Cb/Pb samples                                                                                                                    |                           |                        |

[1] In case of the combined double D1 mode, no secondary display channel is available

The PNX8510/11 supports color space conversion only in the primary RGB standard definition data path. For the high definition part of the primary video data path and for the secondary video data path no color space conversion is available. Hence the video data has to be provided in the display destination color space.

Aside from built-in video encoders, which generate all necessary timing and filtering for an appropriate sync raster for PAL, NTSC and SECAM, the PNX8510/11 contains a separate raster-generation engine which also supports but is not limited to the HD-formats, such as the SMPTE 274M. The PNX8510/11 also contains an up-sampling filter to convert 4:2:2 formats (other than standard definition formats) to 4:4:4.

In the case of combined double D1 mode, no secondary display channel is available.

If the interface is operated in D1 mode, the data stream presented to the interface has to be D1 compliant i.e., the maximum and minimum codes (8-bit 0x00 0xFF, 10-bit 0x000 0x3FF) must not occur during active video.

A detailed description of video input data formats can be found in Section 7.1.2. The video modes listed correspond to the settings of the DEMUX\_MODE bits in the register 0x95 VMUXCTL Section 8.1. If the video interface clock frequency is not equivalent to the processing and the video DAC operation frequency the appropriate divider registers in the audio/clock register section have to be programmed. As a general rule the settings in Table 10 should be used:

#### Table 10: Clock frequency settings

| Mode                                  | Interface<br>clock | Processing<br>clock | DAC clock |

|---------------------------------------|--------------------|---------------------|-----------|

| 4:2:2 YUV SD Single Interface Mode    | 27 MHz             | 27 MHz              | 27 MHz    |

| 4:4:4 RGB 2FH Single Interface Mode   | 81 MHz             | 27 MHz              | 27 MHz    |

| 4:2:2 YUV 1080i Double Interface Mode | 74.25 MHz          | 74.25 MHz           | 74.25 MHz |

### 7.1.2 Video input modes

The PNX8510/11 video interface supports a wide variety of video formats. The video interface is designed in a generic fashion. It is de-coupled from the actual video data paths in the system and imposes only a few restrictions on the video data streams provided to the chip.

This section explains the possible video stream formats and provides details on synchronizing the PNX8510/11 with respect to a particular video data format.

The PNX8510/11 accepts the video formats shown in Figure 4 to Figure 10 on a single interface with up to 81 MHz interface clock:

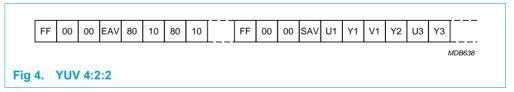

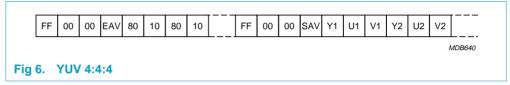

#### YUV 4:2:2

This is the CCIR-656 compliant format and will mainly be used at an interface speed of 27 MHz to feed the video encoder modules in the chip.

This is the standard interface format for the secondary video encoder pipeline unless the chip is used in High Definition (HD) mode.

The YUV 4:2:2 format can also be used to feed the HD data path as long as the pixel clock rate stays below 81 MHz. To operate the HD data path with 4:2:2 source material the 4:2:2 to 4:4:4 filter should be enabled to achieve the best video quality.

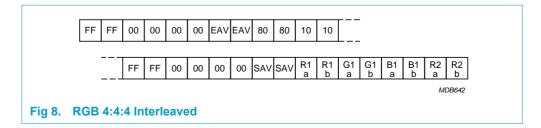

RGB 4:4:4

|        |     |       |     |    |    |    |    | <br> |    |    |     |    |    |    |    |    |    |        |

|--------|-----|-------|-----|----|----|----|----|------|----|----|-----|----|----|----|----|----|----|--------|

| FF     | 00  | 00    | EAV | 80 | 10 | 80 | 10 | FF   | 00 | 00 | SAV | R1 | G1 | B1 | R2 | G2 | B2 |        |

|        |     |       | ·   |    |    |    |    | <br> |    |    | •   |    | -  |    |    |    | 1  | /DB639 |

| g 5. I | RGE | 3 4:4 | 4:4 |    |    |    |    |      |    |    |     |    |    |    |    |    |    |        |

This mode is only useful if the HD data path in the PNX8510/11 is in operation. The RGB 4:4:4 interface mode is not applicable to the standard definition RGB path operation due to the implicit clocking requirements. The data rate for standard definition RGB 4:4:4 data would be 13.5 MHz per component resulting in an interface speed of 40.5 MHz. Because the chip does not contain any PLLs, it is not possible to extract 27 MHz out of the interface clock.

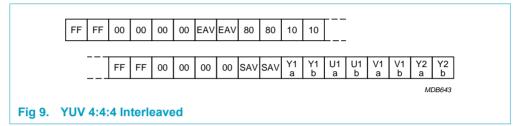

#### YUV 4:4:4

This mode is useful only if the HD data path in the PNX8510/11 is in operation.

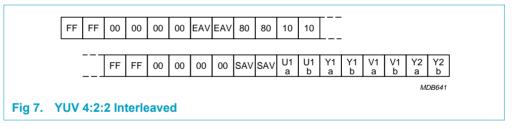

#### YUV 4:2:2 Interleaved

This mode supports two video data streams through one physical video interface. It can be used to utilize both video encoder channels in the chip with one interface only or to hook up two PNX8510/11 devices to one source providing an interleaved data stream. Each chip extracts one slice from the interleaved stream. This video format is useful for the encoder standard definition data path only.

#### RGB 4:4:4 Interleaved

This mode supports two video data streams through one physical video interface. It can be used to utilize both video encoder channels in the chip with one interface only or to hook up two PNX8510/11 devices to one source providing an interleaved data stream. Each chip extracts one slice from the interleaved stream. This video format is useful for the standard definition RGB data path as well as for the HD data path.

#### YUV 4:4:4 Interleaved

This mode supports two video data streams through one physical video interface. It can be used to utilize both video encoder channels with one interface only or to hook up two PNX8510/11 devices to one source providing an interleaved data stream. Each chip extracts one slice from the interleaved stream. This video format is useful for the HD data path only.

There are two modes defined for interleaved data streams. One is to run the interface at twice the speed and provide a qualifier on the HSYNC input to qualify a certain slice. The qualifier is essentially the interface clock divided by two.

The other interleaved interface format works on both clock edges of the interface clock, so one slice is latched at the positive edge and the other slice is latched at the negative edge of the interface clock.

### YUV 4:2:2 HD two-channel format

| FF | 00 | 00 | EAV | 80 | 10 | 80 | 10 | FF | 00 | 00 | SAV | Y1 | Y2 | Y3 | Y4 | U5 | Y6 |

|----|----|----|-----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|    |    |    |     |    |    |    |    |    |    |    |     |    |    |    |    |    |    |

| FF | 00 | 00 | EAV | 80 | 10 | 80 | 10 | FF | 00 | 00 | SAV | U1 | V2 | U3 | V3 | U5 | V5 |

Fig 10. YUV 4:2:2 HD two-channel format

This format is used only for high definition video modes that exceed interface clock requirements of 81 MHz. For this video interface mode, both physical interfaces of the chip are utilized. The primary interface gets a D1-like data stream, which only contains the luminance information, while the secondary D1 interface carries the chrominance information.

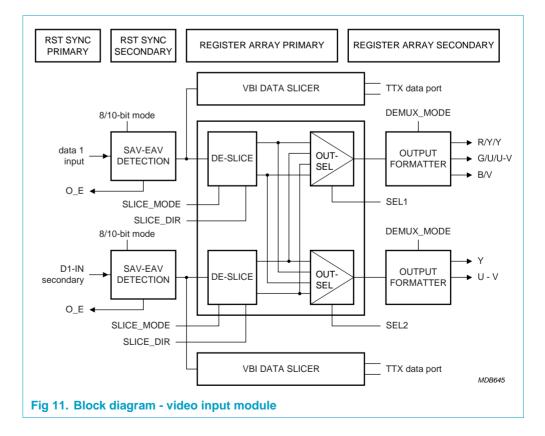

### 7.1.3 Video input module

The video input module is responsible for accommodating all supported video data formats. It delivers a de-multiplexed and de-sliced data stream to the video processing modules.

As depicted in Figure 11, the IC has two video input ports which can accommodate 8 or 10-bit wide video data streams.

9397 750 12612

The normal mode of operation is that the DV1 interface is routed to the primary video data paths and the DV2 interface is routed to the secondary video data paths. The IC however accepts also so called sliced data formats. A sliced data format contains two single video data streams multiplexed together on a component basis. A more detailed description of the arrangement of the components can be found in Section 7.1.2. To enable sliced data formats the SLICE\_MODE bit of the register VMUXCTL (register offset 0x95) has to be set.

The De-Slice module essentially takes the two data streams apart by simply two to one de-multiplexing. The routing of the resulting two video data streams is determined by setting the SEL register bits in the primary and secondary video data path apertures appropriately. Sliced data formats come in two different flavors: double edge and qualified.

The double edge slice format has data changes on the positive and the negative clock edge where as the qualified mode qualifies one data stream of the two multiplexed ones with an active high on the HSYNC signal. To use this mode the USE\_QUALIFIER bit in the register INPCTL (offset 0x3A) must be set. The order of the slice qualification can be changed by setting the QUAL\_INVERT bit of the same register (offset 0x3A).

Since each of the video input interfaces can accept sliced data formats a total of four video data streams could be routed into the IC and two of them can be selected to be forwarded to the primary and the secondary video display pipeline.

The structure of the video input module is shown in Figure 11.

#### 7.1.4 Video DAC control

The PNX8510/11 contains six video DACs, four dedicated to the primary video pipeline and two to the secondary video processing path.

The first DAC of the primary video channel (VOUT1) is always assigned to the primary standard definition data path. The output of the DAC can be changed from CVBS to Y by resetting the CVBSEN bit of the register DACCTRL (offset 0x2D) to zero.

The second DAC of the primary video channel (VOUT2) is assigned to either the standard definition (SD) data path or High Definition (HD) data path. In the SD mode, it carries the chrominance, C (Y/C operation) if the CEN bit in the DACCTRL (offset 0x2D) is set or the Red/V channel (RGB/Component mode operation) if the CEN bit of the DACCTRL (offset 0x2D) is reset. In HD mode (SD\_HD bit of INPCTL register, offset 0x3A is set to zero) this DAC carries either the Red channel or the Y channel depending on whether the HD path is operated in RGB or YUV mode. Note that the CEN bit must be reset for HD operation.

The third DAC of the primary video channel (VOUT3) is also assigned to either the standard definition (SD) data path or High Definition (HD) data path. In SD mode, it carries the luminance channel if the VBSEN bit in the DACCTRL (offset 0x2D) is set or the Green/Y channel if the VBSEN bit is reset (RGB/Component mode operation). If the high definition data path is operational (SD\_HD=1'b0) this DAC carries the Green or U channel depending on whether the HD path is operated in YUV or RGB mode.

The configuration of the fourth DAC in the primary video data path (VOUT4) can not be changed with a programming register. This DAC carries the Blue or U channel in standard definition mode and the Blue or V channel if the high definition data path is active.

The configuration of the DACs for the secondary video data path is limited to the CVBS/Y DAC (VOUT5). If the CVBSEN bit in the DACCTRL register (offset 0x2D) is set, this DAC carries the CVBS signal. Resetting the bit results in the Y signal being assigned to this DAC.

The second DAC of the secondary video pipeline (VDAC6) always carries the chrominance signal.

#### 7.1.5 VBI data

VBI data extraction from a D1 data stream is only supported for standard definition formats. The extraction follows the concept of Philips video decoders, such as the SAA7114. Both video interfaces can carry VBI data information. The content of the VBI data is entirely determined by the source decoder chip software driver.

The PNX8510/11 supports two VBI data streams. The limitation to two VBI data streams implies certain limitations when using multiple PNX8510/11 chips in a system. In this case one PNX8510/11 gets either one or two (all) VBI data streams. The other PNX8510/11 IC would get one or none.

Only the ANC/SAV-EAV header style VBI data encoding mode is supported in the PNX8510/11. According to these standards VBI data is always inserted in the horizontal blanking interval of a line. The data is preceded by an ANC header which is

9397 750 12612

programmable. An internal header following the ANC contains a programmable sliced data identifier with the number of data bytes transmitted and two internal identification tokens containing data type, field type and line number. Figure 12 illustrates how the data is encoded in the horizontal blanking interval.

**Remark:** In standard definition mode, only 8 of the 10 available signal lines of the D1 interface are used. The two LSB lines are fixed to zero.

| FF                                | 00                                                                      | 00 | EAV | FF | FF | 00  | DID         | SDID | вс | IDI1 | IDI2 | D1                                             | D2 |  | DDC1 | DDC | FF | 00 | 00 | SAV |

|-----------------------------------|-------------------------------------------------------------------------|----|-----|----|----|-----|-------------|------|----|------|------|------------------------------------------------|----|--|------|-----|----|----|----|-----|

|                                   | timing reference<br>code<br>end active video ANC header internal header |    |     |    |    | ler | sliced data |      |    |      |      | timing reference<br>code<br>start active video |    |  |      |     |    |    |    |     |

| horizontal line blanking interval |                                                                         |    |     |    |    |     |             |      |    |      |      |                                                |    |  |      |     |    |    |    |     |

See Table 11 to Table 16 for code description

Fig 12. ANC VBI data insertion in D1

#### Table 11: VBI header/data codes

| Name   | Function                                                         |

|--------|------------------------------------------------------------------|

| SAV    | start of active video                                            |

| DID    | data identifier: ignored, has to be set to 0x11h                 |

| SDID   | sliced data identification: ignored, has to be set to 0x11h      |

| BC     | byte count describes the number of succeeding decoded data bytes |

| IDI1   | internal data identification 1: OP, FID, LineNumber[8:3]         |

| IDI2   | internal data identification 2: OP, LineNumber[2:0], Data Type   |

| D1-Ddc | data bytes                                                       |

| EAV    | end of active video                                              |

#### Table 12: VBI data header format

*LN* = *Line Number, BC* = *Byte Count, DT* = *Data Type*

|      | ,  |                                    |     | = = = = |     |     |     |     |

|------|----|------------------------------------|-----|---------|-----|-----|-----|-----|

| Code | D9 | D8                                 | D7  | D6      | D5  | D4  | D3  | D2  |

| SDID | 1  | 1                                  | 1   | 1       | 1   | 1   | 1   | 1   |

| DID  | 1  | 1                                  | 1   | 1       | 1   | 1   | 1   | 1   |

| BC   | -  | -                                  | BC5 | BC4     | BC3 | BC2 | BC1 | BC0 |

| IDI1 | -  | field ID<br>0=field 1<br>1=field 2 | LN8 | LN7     | LN6 | LN5 | LN4 | LN3 |

| IDI2 | -  | LN2                                | LN1 | LN0     | DT3 | DT2 | DT1 | DT0 |

#### Table 13: SAV/EAV codes NTSC

| Line Number | F | V | H (EAV) | H (SAV) |

|-------------|---|---|---------|---------|

| 1-3         | 1 | 1 | 1       | 0       |

| 4-19        | 0 | 1 | 1       | 0       |

| 20-263      | 0 | 0 | 1       | 0       |

#### Table 13: SAV/EAV codes NTSC...continued

| Line Number | F | V | H (EAV) | H (SAV) |

|-------------|---|---|---------|---------|

| 264-265     | 0 | 1 | 1       | 0       |

| 266-282     | 1 | 1 | 1       | 0       |

| 283-525     | 1 | 0 | 1       | 0       |

#### Table 14: SAV/EAV codes PAL

| Line Number | F | V | H (EAV) | H (SAV) |

|-------------|---|---|---------|---------|

| 1-22        | 0 | 1 | 1       | 0       |

| 23-310      | 0 | 0 | 1       | 0       |

| 311-312     | 0 | 1 | 1       | 0       |

| 313-335     | 1 | 1 | 1       | 0       |

| 336-623     | 1 | 0 | 1       | 0       |

| 624-625     | 1 | 1 | 1       | 0       |

### Table 15: SAV/EAV sequence

| SAV/EAV     | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------|----|----|----|----|----|----|----|----|----|----|

| preamble    | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

|             | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|             | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| status word | 1  | F  | V  | Н  | P3 | P2 | P1 | P0 | 0  | 0  |

[1] P0 to P3 are protection bits and calculated in the following way: P3=V^H, P2=F^H, P1=F^V, P0=F^V^H

#### Table 16: Supported data types

| Data Type | Standard                                    |

|-----------|---------------------------------------------|

| 0000      | Teletext EuroWST                            |

| 0010      | VPS video programming service               |

| 0011      | WSS wide screen signalling                  |

| 0100      | closed caption                              |

| 1100      | US NABTS                                    |

| 1111      | Programming (SubAddr1-Data1-SubAddr2-Data2) |

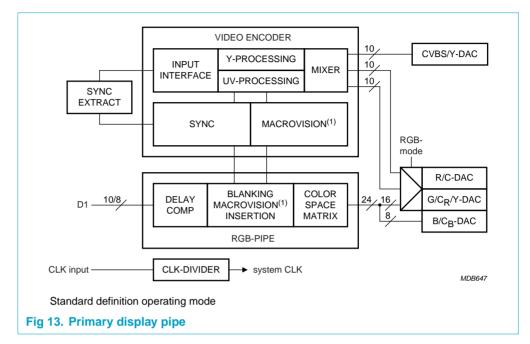

### 7.1.6 Primary video channel

Figure 13 illustrates the different modes of operation for the primary video channel.

PNX8510/11 supports color space conversion only in the primary RGB Standard definition data path. The fixed coefficients of this color space matrix are as follows:

R = Y + 1.371 x Cr

$G = Y - (0.336 \times Cb + 0.698 \times Cr)$

$B = Y + 1.732 \times Cb$

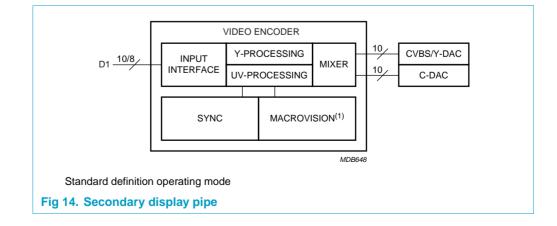

### 7.1.7 Secondary video channel

The secondary display consists of the Y and UV processing data path of a video encoder only. The synchronization information will be extracted from the incoming D1 data stream. The structure of the secondary display pipe is shown in Figure 14.

### 7.1.8 PAL/NTSC/SECAM encoder

The PAL/NTSC/SECAM encoder accepts the YUV data and encodes it into an NTSC, PAL or SECAM video signal. From Y, U and V data, the encoder generates luminance, chrominance and subcarrier output signals, suitable for use as CVBS or separate Y and C signals.

Luminance is modified in gain and in offset (offset is programmable to enable different black level setups). In order to enable easy analog post filtering, luminance is interpolated from a 13.5 MHz data rate to a 27 MHz data rate, providing luminance in 10-bit resolution. This filter is also used to define smoothed transients for synchronization pulses and the blanking period. Chrominance is modified in gain (programmable separately for U and V). The standard dependent burst is inserted before baseband color signals are interpolated from a 6.75 MHz data rate to a 27 MHz data rate.

One of the interpolation stages can be bypassed providing a higher color bandwidth, which can be used for Y and C output. The register bits FSC0 to FSC3 set the subcarrier frequency. To make sure the subcarrier is locked to the line frequency, as the standards require, the sync generator is able to reset the subcarrier generation periodically. This feature is controlled by the PHRES (register MULTICTL, offset 0x6E) programming bits. These features are available to generate a standard interlaced signal; they will not work in non-interlaced mode.

A crystal-stable master clock of 27 MHz, which is twice the CCIR line-locked pixel clock of 13.5 MHz, is received from the interface clock pins. The encoder synthesizes all necessary internal signals, color subcarrier frequency, and synchronization signals from that clock.

For ease of analog post filtering, the signals are twice oversampled with respect to the pixel clock before digital-to-analog conversion.

PNX8510/11

Analog companion chip

Programming flexibility includes NTSC-M, PAL-B, SECAM main standards as well as other variations. A number of possibilities are provided for setting different video parameters, such as:

- Black and blanking level control

- Color subcarrier frequency

- Variable burst amplitude

The sync generator generates all the signals required to control the signal processing, provide the composite sync signal, insert the color burst, etc.

The encoder includes a cross-color reduction filter to reduce cross talk between the luminance and chrominance channels. In the CVBS signal, the signal amplitude is reduced by 15/16 to avoid overflow.

#### 7.1.9 Luminance and Chrominance Processing

The Y processing provides a high performance 5 MHz lowpass filter. It adjusts the level range according to the standard and inserts the sync and blanking pulses. The insertion stage generates the correct pulse shapes. No further processing is necessary of the D/A converters for this purpose.

Chroma processing operates on the baseband signals as long as possible. At first, the signal amplitudes are adjusted and the burst is inserted. Afterwards the signals are passed through a 1.4 MHz lowpass filter. This filter can be switched to a higher cut-off frequency to allow more chroma bandwidth with S-Video. The quadrature modulator uses a DTO (Discrete Time Oscillator) with 32-bit resolution for the subcarrier generation. Even with this high resolution, the DTO cannot generate the carrier locked to the line frequency as the standards require without further means. So the sync generator is able to reset the DTO periodically. This feature is controlled by the PHRES programming bits. These modes may only be switched on if the encoder is programmed to generate a standard signal; they will not work in non-interlaced mode.

PNX8510/11

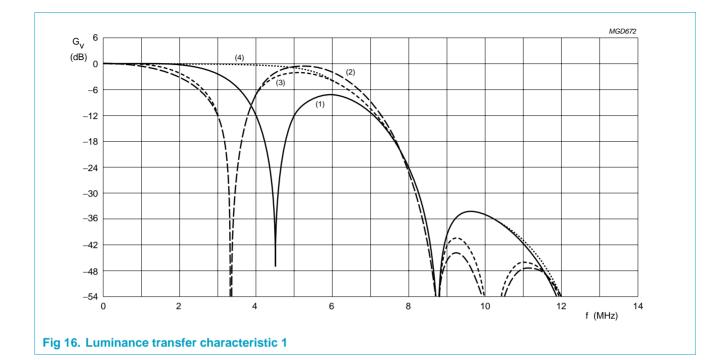

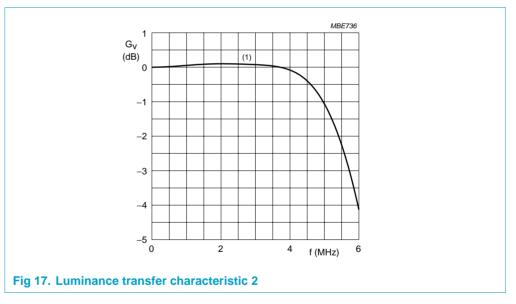

Table 17:

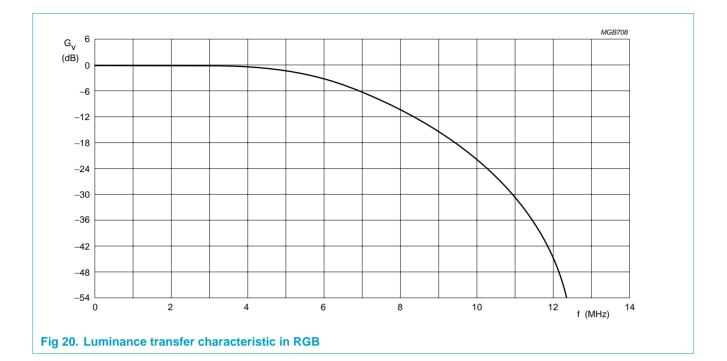

Luminance transfer characteristics

Register CCRS, offset 0x5f defines the luminance transfer characteristics

| CCRS | Luminance Transfer Characteristics |

|------|------------------------------------|

| 01   | (1)                                |

| 10   | (2)                                |

| 11   | (3)                                |

| 00   | (4)                                |

PNX8510/11

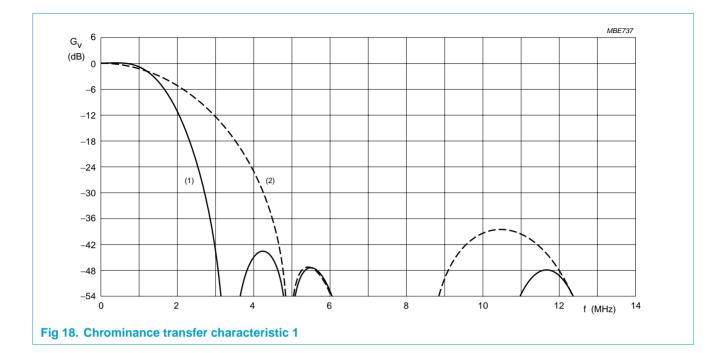

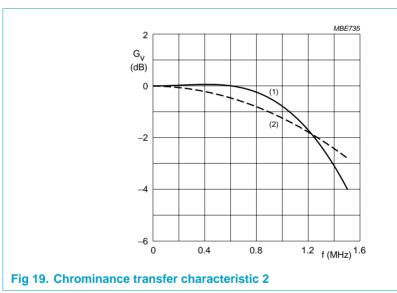

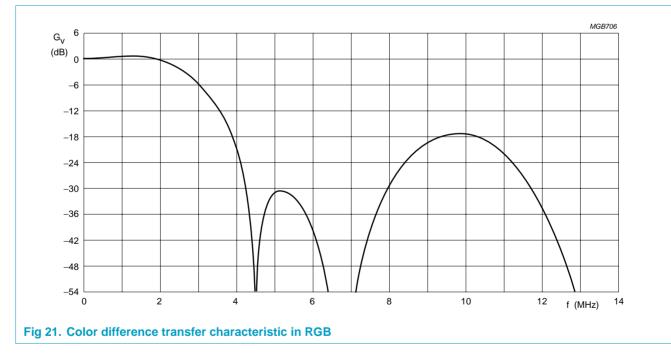

# Table 18: Chrominance transfer characteristics

Register SCBW, offset 0x61 defines the chrominance transfer characteristics

| SCBW | Chrominance Transfer Characteristics |

|------|--------------------------------------|

| 1    | (1)                                  |

| 0    | (2)                                  |

# PNX8510/11 Analog companion chip

#### 7.1.10 Sync generator

The sync generator is the timing master of the encoder. It generates all the signals required to control the signal processing, provide the composite sync signal, insert the color burst, etc. Via the FISE control bit (register STDCTL, offset 0x61), the circuit can be set to generate 50 Hz patterns for e.g., PAL B or 60 Hz patterns (NTSC M). It is possible to modify the number of lines per field by  $\pm 0.5$  lines to generate a non-interlaced output signal. The sync generator also provides HS (Horizontal Sync), VS (Vertical Sync) and O\_E (Odd/Even) signals to control the rest of the encoder.

### 7.1.11 Macrovision<sup>™</sup> - PNX8510

The encoder supports Macrovision<sup>™</sup> Anti-Taping for both NTSC and PAL. There is no Macrovision<sup>™</sup> insertion for SECAM defined, however for AGC Pseudo Sync and BP pulses the same settings used for PAL could be used for SECAM. The different steps of this process can be programmed separately. The Macrovision<sup>™</sup> control block provides all necessary timing and level information for inserting the correct pulses in the CVBS/Y/C/RGB/YUV data stream. Furthermore it provides the signals used to modify the subcarrier generator according to the Macrovision<sup>™</sup> Burst Inversion requirements.

The encoder uses a blanking level during the vertical blanking interval that is defined by the value of BLNVB, thus providing two different programmable blanking levels. Outside vertical blanking, value of BLNNL is effective, which should be reduced according to Macrovision<sup>™</sup> requirements. The copy protection means can be activated independently by the respective control bits. The Macrovision<sup>™</sup> registers and definition of each of these registers are defined in a separate Macrovision<sup>™</sup> Supplement document.

**Remark:** Macrovision<sup>™</sup> is not available in PNX8511.

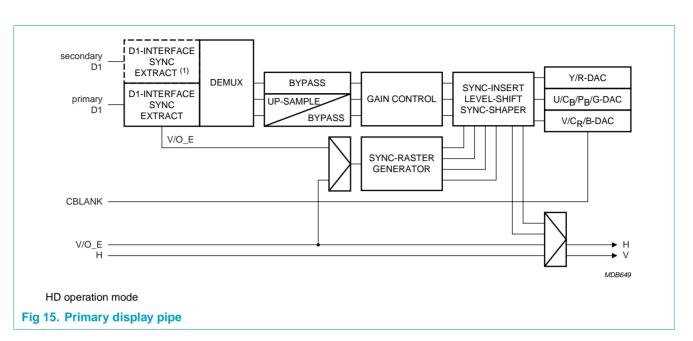

# 7.2 HD data path

The high definition data path of the PNX8510/11 IC features an up-sampling filter, gain control and a universal sync insertion engine.

Input formats supported by the high definition data path are:

- Double D1 mode:16/20 bit 422 (8/10 bit for Y and 8/10 bit for U/V); DEMUX\_MODE of Register VMUXCTL, offset 0x95 is set to 3'b011

- Single interface HD 422 mode (UYVY 422 D1 format); DEMUX\_MODE of Register VMUXCTL, offset 0x95 is set to 3'b100

- Single interface 444 (RGB/YUV 444 format); DEMUX\_MODE of Register VMUXCTL, offset 0x95 is set to 3'b001

- Full 24/30 bit parallel input mode (YUV/RGB 444 formats); VMODE of Register MISCCTRL, offset 0xA5 is set to zero

RGB and YUV data types are accepted. However, there is no color space conversion in the HD data path so the input data type has to match the display data type.

The up-sampling filter can be applied to convert incoming 422 data formats to 444.

The data path also provides individual gain control for RGB/YUV which allows a +/-0.5x amplitude change (HD\_GAIN\_RY, HD\_GAIN\_GU, HD\_GAIN\_BV control registers).

The HD sync insertion module following the filter and gain control circuits provides flexible insertion of synchronization signals into the Y, Y and V or R, G and B data paths. The insertion can be chosen on a component basis (Y/R\_SYNC\_INS\_EN, U/G\_SYNC\_INS\_EN, V/B\_SYNC\_INS\_EN control registers) and the sync generator provides individual tables for the components. A more detailed description of the sync generator can be found in the next paragraph.

### 7.2.1 HD-sync generator module

This section describes the operation and programming of the high definition (HD) video data path sync unit.

The module's purpose is to provide the video data path that bypasses the digital video encoders with the appropriate synchronization pattern. The module design provides maximum flexibility in terms of raster generation for all interlaced and non-interlaced ATSC formats. The sync engine is capable of providing a combination of event-value pairs which can be used to insert certain values at specified times in the outgoing data stream. It can also be used to generate digital signals associated with time events. They can be used as digital Horizontal and Vertical synchronization signals.

The sync raster generation is fully programmable to accommodate different requirements. The raster generation can be either progressive or interlaced. Digital sync signal generation (Horizontal, Vertical and Blank) as well as analog embedded sync generation are supported. The picture position is adjustable through the programmable relation between the sync pulses and the video contents.

The generation of embedded analog sync pulses is bound to a number of events which can be defined for a line. Several of these line-timing definitions can exist in parallel. For the final sync raster composition a certain sequence of lines with different sync event properties has to be defined. The sequence specifies a series of line types and the number of occurrences of this specific line type.

After the sequence has completed, it restarts from the beginning. In this way, the sync raster generation is generic and can be adopted to different standards (different sync shapes, various H-timing, interlaced, progressive...). However, to generate a stable picture, it is important that the sequence fits precisely to the incoming data stream in terms of the total number of pixels per frame.

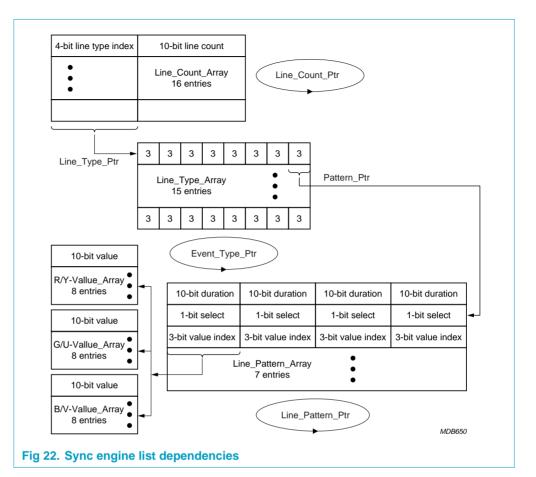

The sync engine's flexibility is achieved by using a sequence of linked lists carrying the properties for the image, the lines as well as fractions of lines. The list dependencies are illustrated in Figure 22.

# PNX8510/11 Analog companion chip

The first table is called "Line\_Count\_Array" and serves as an array to hold the correct sequence of lines composing the synchronization raster. It can contain up to 16 entries. Each entry holds a 4-bit index (counted from 1 through 16)) and a 10-bit counter value.

The 4-bit index is a pointer to a line in the next table called "Line\_Type\_Array." A 10-bit counter value specifies how often this particular line is repeated. If the necessary line count for a particular line exceeds the 10 bits, it has to use two table entries. This table has to be terminated with a dummy entry containing a '0' index and '0' line count.

The second table, "Line\_Type\_Array" holds up to 15 entries (counted from 1 through 15). Each entry can contain up to eight index pointers which point to another table called, "Line\_Pattern\_Array." These pointers represent parts of a line raster. A line may be split up into a sync, a blank and an active portion followed by another blank portion, which would require four index pointers in one entry of the table. It is possible to have less than eight index pointers in any entry, in which case those index pointers should be filled with '0.

The third table is called "Line\_Pattern\_Array" and it can contain a maximum of seven entries (counted from 1 though 7). The entries are used to define portions of a line representing a certain value for a certain number of clock cycles. Each of these seven entries can store up to four groups of "duration, select and value index." It is possible to have less than four groups in any entry, in which case those groups should be filled

9397 750 12612

with 0. "Duration" is a 10-bit value representing the number of clock cycles. "Select" indicates whether the value is actually inserted into the video data stream or not. "Value index" is a 3-bit index into the next table in the linked list called "Value array." Certain bits of the "value index" can also be used to generate a digital sync raster provided at the H- and V-sync outputs of the PNX8510/11.

"Value array" can hold up to 8 values (counted from 0 though 7) which are 10-bit signed 2's complement.

### 7.2.2 Trigger generation

To ease the trigger setup for the sync generation module, a set of registers is provided to set up the screen raster defined as width and height. A trigger position can be specified as an x, y coordinate within the overall dimensions of the screen raster. If the x, y counter matches the specified coordinates, a trigger pulse is generated which pre-loads the tables with their initial values. Refer to the 1080i example for the trigger programming.

#### **Important Notes**

- The "duration" in the "Line\_Pattern\_Array" that needs to be programmed should be 1 cycle less than the actual duration required.

- For the registers LCNT\_ARRAY\_ADR (offset 0x82), LTYPE\_ARRAY\_ADR (offset 0x86), LPATT\_ARRAY\_ADR (offset 0x8E), "addr+1" should be written to finish writing the data meant for "addr," for example:

For the registers LCNT\_ARRAY\_ADR (offset 0x82), LTYPE\_ARRAY\_ADR (offset 0x86), LPATT\_ARRAY\_ADR (offset 0x8E), "addr+1" should be written to finish writing the data meant for "addr," for example:

LTYPE\_ARRAY\_LINE1 = 0x14

LTYPE\_ARRAY\_LINE2 = 0x05

LTYPE\_ARRAY\_LINE3 = 0x00

LTYPE\_ARRAY\_LINE\_ADR = 0x01

Note the next address, 0x02, is written to finish writing to the previous address 0x01.

LTYPE\_ARRAY\_LINE\_ADR = 0x02

LTYPE\_ARRAY\_LINE1 = 0x14

LTYPE\_ARRAY\_LINE2 = 0x03

LTYPE\_ARRAY\_LINE3 = 0x00

LTYPE\_ARRAY\_LINE\_ADR = 0x02

Note the write to next address, 0x03

LTYPE\_ARRAY\_LINE\_ADR = 0x03

LTYPE\_ARRAY\_LINE1 = 0x0C

$LTYPE_ARRAY_LINE2 = 0x03$

LTYPE\_ARRAY\_LINE3 = 0x00

LTYPE\_ARRAY\_LINE\_ADR = 0x03

Note the write to next address, 0x04

LTYPE\_ARRAY\_LINE\_ADR = 0x04

The HD Sync Generator inserts a definable sync pattern (that normally includes blanking) into the video line. This includes a 'Select' bit [in the Line\_Pattern\_Array] which determines whether the current portion of the line should display video or generated sync. Each portion of the line has a color value defined, which will be displayed if Select=1. There is a 1 pixel path difference between 'Select' and 'Value', resulting in the momentary display of the color value for 1 pixel width until the Select bit switches active video to the output display.

The work around for the above problem is to ensure that the Value array entry for the 'active' portion of the line is set the same as the previous portion of the line. This will normally mean setting the value to blanking level. This will ensure that during the 1 clock path difference, the color value output will be the same as for the previous portion of the line. This will remove the observed spike.

The listing below outlines an example on how to set up the sync tables for a 1080i HD raster:

// hd-sync config file for 1080i

#line\_count\_array

//index //line\_count

25//5 lines vsync 41//1 line sync-black-sync-black 614//14 lines blank 1537//537 lines active video 65//5 lines blank 51//1 line sync-black-sync-blank 24//4 lines sync 31//1 line sync blank sync black 615//15 lines blank 1537//537 lines active video 65//5 lines blank 00//dummy lines 00//dummy lines 00//dummy lines 00//dummy lines 00//dummy lines #line type array //p8p7p6p5p4p3p2p1

00000034 //sync-full active line 00002424 //sync-half blank-sync-half blank 00001424 //sync-half blank-sync-half black 00001414 //sync-half black-sync-half blank 000002414 //sync-full black-sync-half blank 00000054 //sync-full line black 00000000 00000000

PNX8510/11

Analog companion chip

0000000 00000000 00000000 0000000 0000000 0000000 0000000 #line pattern array //d=duration s=select v=value //d4s4v4d3s3v3d2s2v2d1s1v1 -----000000431387913 //half line black 000000431387910 //half line blank 431395906959065913 //full active line 000871343124311 //sync pulse 431395913959135913 //full line black 000000000000 000000000000 #value array //signed values // YUV ------51200//broad pulse level -512-432-432//lower sync tip 102432432//upper sync tip -20400//black/blank level org 000 000 000 000 #other //trigger\_line // preload of the line count in //addr 0x9a-0x99 -hex values 993 9a 00

//trigger\_duration

// preload of duration of the line pattern array

//addr 0x9c-0x9b -hex values

9c 0

9b 2

//trigger pointer

9d 0x11

// bit 1:0 loads the counter value of line count array

// bit 7:4 loads the counter value of the line pattern array

//sync raster

//sync height

ae 0x64

af 0x04

//sync width

b0 0x97

b1 0x08

//sync trigger pos

//trigger pos x

b4 0x15

b5 0x00

//trigger pos y

b2 0x15

b3 0x00

A complete example of register settings for 1080i is given in Section 9.

The listing below outlines an example on how to set up the sync tables for a 720p raster:

// hd-syn config file for 720p

\_\_\_\_\_

#line count array

//index line\_count

25//5 lines vsync 320//20 lines blank 1360//360 lines active video 1360//360 lines active video 35//5 lines blank 00//dummy lines 00//dummy lines 00//dummy lines 00//dummy lines 00//dummy lines

#line\_type\_array

//p8p7p6p5p4p3p2p1

00000034 //sync-full line active 00000024 //sync-full line blank (vsync) 00000054 //sync-full line black (v-blanking) 00000000 0000000 0000000 0000000 0000000 0000000 0000000 0000000 0000000 00000000 0000000 #line pattern array //dur4sel4val4dur3sel3val3dur2sel2val2dur1sel1val 1 00000000000 //empty 00069137141071410 //full line blank 6913639006390014913 //full line active 000691339123911 //sync pulse 6913639136391314913 //full line black 000000000000 0000000000000 #value array Y //signed values YUV \_\_\_\_\_ -51200//broad pulse level -512-432-432//lower sync tip 102432432//black/blank level org 000 000 000 000

#### 7.2.3 Signature analysis

PNX8510/11 allows the signature analysis to be done on both primary and the secondary video channels and read the two signatures separately. The signature analysis is done on the upper 8 bits of the interface. The video channel select for the signature analysis is defined by the "SIG\_SELECT" of the SIGCTRL (offset 0xBA) register.

The signature is calculated as per the following CRC algorithm:

// \* This is a simple table based CRC-16 that computes the CRC

// \* four bits at a time. This requires a small (16 entry) lookup table.

// \* lookup table for non-reversed parallel CRC algorithms

- // unsigned int crc16\_table[16]={

- // 0x0000, 0x8005, 0x800f, 0x000a,

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

```

//

0x801b, 0x001e, 0x0014, 0x8011,

//

0x8033, 0x0036, 0x003c, 0x8039,

//

0x0028, 0x802d, 0x8027, 0x0022

// };

//

// * Unlike the serial method, this algorithm does not require any additional

// * operations to finish the CRC after the message is processed

// * This routine uses crc1 to hold the crc.

// */

//

// void parallel_crc1(c)

// int c;

// {

//

int r1;

//

//

/* calculate CRC using the 4 bit LUT method */

//

/* upper 4 bits */

r1 = crc16_table[((crc1>>12) \& 0xF) \land ((c \& 0xf0) >> 4)];

//

//

crc1 = ((crc1 << 4) & 0xFFF0) ^ r1;

//

//

/* lower 4 bits */

//

r1 = crc16 table[((crc1>>12) \& 0xF) \land (c \& 0x0f)];

crc1 = ((crc1 << 4) \& 0xFFF0) ^ r1;

//

// }

```

### 7.2.4 Limitations of the video pipe

In all HD modes, the video encoder will be switched off. Either a separate sync signal or the embedded syncs of the D1 input can be used to generate the sync raster driving the display device.

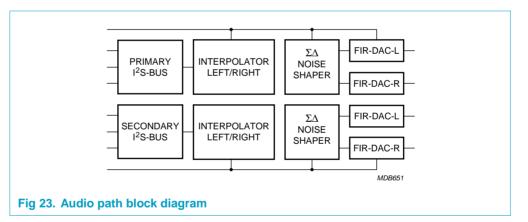

# 7.3 Audio pipeline

The PNX8510/11 has two independent stereo channels, each connected to a separate audio interface. The primary audio channel is usually associated with the primary video channel and carries the accompanying sound information. The

secondary audio channel usually carries the audio belonging to the record (secondary) video channel. Because they might originate from different sources, the two interfaces are operated by independent clocks.

Mute on/off is programmable by a register setting. Table 19 describes the expected audio performance.

#### Table 19: Audio performance

| Parameter     | QFP100 |

|---------------|--------|

| Dynamic range | 85dB   |

| S/(N+Disto.)  | >85dB  |

The audio path has three general blocks: input, interpolation, and DAC.

- The input is, by default, a 24-bit I<sup>2</sup>S interface. However, it can be programmed to accept other formats.

- The interpolator scales, filters and oversamples the incoming data by 64 x its sampling frequency. The result goes to a Noise Shaper, which shifts in-band noise to frequencies well above the audio spectrum. This provides a very high signal-to-noise ratio.

- Finite Impulse Response DACs convert the 1-bit data stream to analog output voltage.

#### 7.3.1 Audio interface operation

The audio interfaces can be operated in either slave or master mode:

- In slave mode, all required clocks (System CLK, SCK and WS) must be generated externally and must be synchronous with each other.

- In master mode, the PNX8510/11 only gets the System CLK and generates SCK and WS clocks synchronously to the applied System CLK. In this mode, System CLK is equal to 128 x Fs where Fs is the audio sampling frequency.

#### Audio input timing

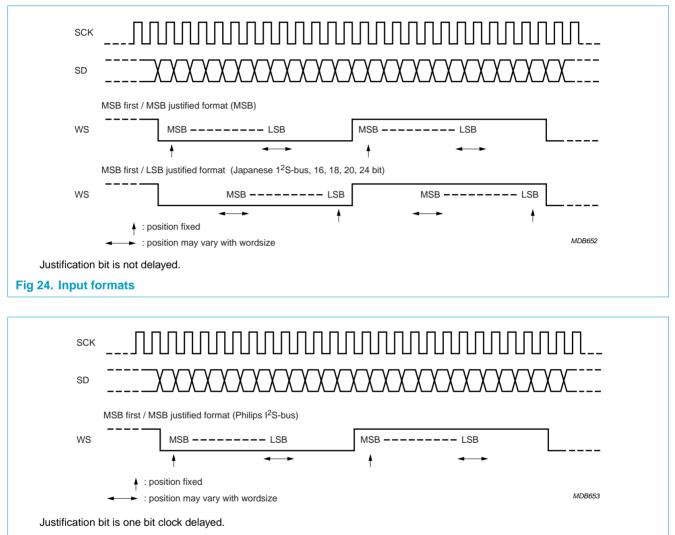

Figure 24 and Figure 25 illustrate the different modes of operation for the I<sup>2</sup>S interface used in the PNX8510/11.

#### Fig 25. Input format

| Table 20: | I <sup>2</sup> S signals                                       |

|-----------|----------------------------------------------------------------|

| Port      | Description                                                    |

| SCK       | Bit clock                                                      |

| SD        | PCM data                                                       |

| WS        | Word Select; left and right clock is equal to the sample rate. |

#### 7.3.2 Mute modes

The audio modules of the PNX8510/11 have several mute functions. The mute operation is controlled via the bits "quickmute, and mutemode" of the programming register, INTERPOLATOR\_REG2(offset 0x00FD).

#### **Quick mute**

This is an overriding quickmute on the master channel, which mutes the interpolator output signal in 32 samples using the cosine roll-off coefficients instead of 32x32 samples to mute the output. This means whenever the quickmute register is set to one, independent of what the mute setting of the micro controller is, the output is muted.

#### Mute mode

This register sets the mute mode for the MASTER MUTE to either soft mute (setting is '0') or to quick mute (setting = '1'). For the master channel the quickmute function and the micro controller mute function are OR'd.

| Table 21. Mute mode control |                       |                                                                     |

|-----------------------------|-----------------------|---------------------------------------------------------------------|

| Quick mute                  | Micro controller mute | Function                                                            |

| 0                           | 0                     | No mute                                                             |

| 0                           | 1                     | 1 micro controller mutemute mode depends on the 'mutemode' setting. |

| 1                           | Х                     | Overriding quick mute function                                      |

|                             |                       |                                                                     |

#### Table 22: Mute Mode Function

Table 21: Mute mode control

While in Mute Mode, releasing the 'mute' bit applies a graduated cosine startup

| Mute mode | Function                                                             |

|-----------|----------------------------------------------------------------------|

| 0         | Mute function via micro controller interface is set to "soft mute."  |

| 1         | Mute function via micro controller interface is set to "quick-mute." |

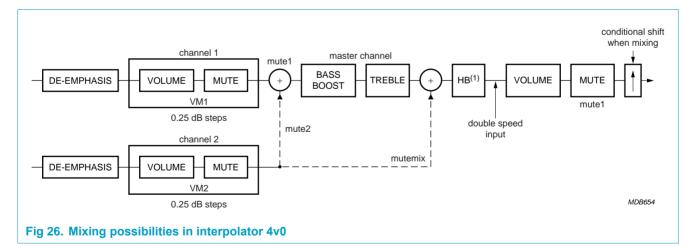

Figure 26 shows the signal flow for the mute control.

### 7.4 Programming interface

The configuration of the various interface modes and the digital video encoder setup can be controlled via an I<sup>2</sup>C interface or a special VBI data packet sent during the horizontal blanking interval. With the VBI programming interface, a reliable real-time programming for the PNX8510/11 video blocks can be accomplished. For instance, this mode makes it very easy to carry the necessary programming data over to the digital encoder to encode a certain teletext packet in a specific scanline without

extensive buffering. The format for programming registers in the PNX8510/11 via the VBI interface can be found in Section 7.1.5. Note that reprogramming clocks and audio registers are not possible via the VBI interface.

The PNX8510/11 is an  $I^2C$  slave device only. It uses four dedicated slave addresses to address the primary, secondary, audio and remaining control registers. The  $I^2C$  address set can be configured during reset with a pull-up or pull-down combination of GPIO pins.

Table 23 shows the register sets and the relationship with the 'xy' bits in the address structure.

Table 23: Relation of 'xy' with register sets Address= GPI05-GPI04-XY-GPI03-GPI02-GPI01-R/W

| Register Set                         | x | У |

|--------------------------------------|---|---|

| VIDEO 1                              | 0 | 0 |

| VIDEO 2                              | 0 | 1 |

| AUDIO 1 / VIDEO 1 and AUDIO 1 clocks | 1 | 0 |

| AUDIO 2/ VIDEO 2 and AUDIO 2 clocks  | 1 | 1 |

Table 24 shows an example of how the I<sup>2</sup>C device addresses are determined.

| Table 24: | I <sup>2</sup> C Address determination | on |

|-----------|----------------------------------------|----|

|-----------|----------------------------------------|----|

| Selection Example                                                |

|------------------------------------------------------------------|

| IIC address selection example:                                   |

| GPIO5-2 are set to logic one and GPIO1 is set to zero during the |

| PNX8510/11rest.                                                  |

| Address = GPI05-GPI04-XY-GPI03-GPI02-GPI01-R/W                   |

| Address = 1-1-XY-1-1-0-R/W                                       |

| VIDEO1 = 1-1-0-0-1-1-0-R/W = 0xCC(write), 0xCD(read)             |

| VIDEO2 = 1-1-0-1-1-0-R/W = 0xDC (write), 0xDD(read)              |

| AUDIO1 = 1-1-1-0-1-1-0-R/W = 0xEC(write), 0xED(read)             |

| AUDIO2 = 1-1-1-1-1-0-R/W = 0xFC(write), 0xFD(read)               |

|                                                                  |

A detailed description of all programming registers can be found in Section 8.

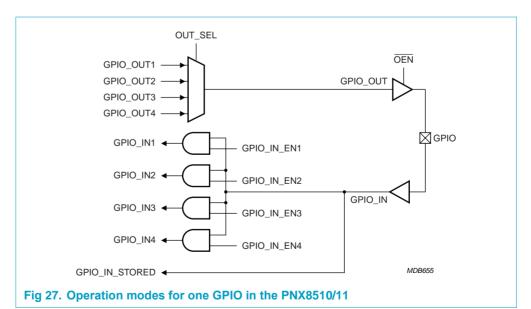

# 7.5 GPIO block

GPIOs are multi-purpose pins. They may be programmed as input/output and used to carry signals into the IC or to monitor the status of the IC. The selection of these I/O pins is controlled through programmable registers. The GPIO module can be programmed via subaddress 90-95 of the primary video pipe.

The GPIO pins operate in two basic modes; Bootstrap mode and GPIO mode. During chip reset the GPIOs are in bootstrap mode. The status of all GPIO pins is monitored and used to determine the set of  $I^2C$  device addresses the IC responds to.

After the chip reset is released, the GPIO pins may be used in GPIO mode. In output mode each GPIO pin can be set to logic one or zero by programming the appropriate register. In input mode the status of each GPIO can be monitored by reading the

appropriate status register. In addition to the register-driven I/O mode, some of the GPIO pins are used to reflect the status of internal signals. Some GPIO pins are also used as additional inputs to functional units if operated in input mode.

#### 7.5.1 Operation

#### **GPIO** set during reset

During reset the GPIO output is disabled. GPIO\_in is stored as gpio\_in\_stored and retains its value until the next reset. This stored value determines the I<sup>2</sup>C device addresses. After reset, GPIO pins can be programmed for output with the OEN and OUT\_SEL bits.

#### Checking/setting the GPIO status

Each GPIO pin is multiplexed four times to increase usability. Figure 27 outlines the internal structure of one GPIO pin. In output mode the selection of the signal routed out to a GPIO pin is performed with the OUT\_SEL register bits. The OEN bit is low active and enables the GPIO output mode. If OUT\_SEL is set to 2'b11 and the OEN bit is set to zero, the GPIO pin can be set or reset by writing a one or zero into the STATUS location of the GPIO register. All other OUT\_SEL settings are listed in Table 29.

To read the external status of a GPIO pin, the OEN needs to be set to one to avoid conflicts with signals routed out of the chip. If GPIO\_IN\_EN4 is set to one, the status of the GPIO pin can be monitored by reading the STATUS bit of the appropriate GPIO register. The function of all relevant GPIO\_IN/OUT signals are listed in Figure 27 and Table 25.

#### Table 25: Specific GPIO assignments

| Signal     | Description                                            |

|------------|--------------------------------------------------------|

| gpio5_out1 | Composite sync secondary encoder                       |

| gpio5_out2 | Vertical sync primary encoder                          |

| gpio5_in3  | 30-bit parallel video input mode: bit[1] = red channel |

9397 750 12612

Analog companion chip

| Table 25: Sp | ecific GPIO assignmentscontinued                                    |