This data sheet contains advance information and specifications are subject to change without notice.

# SMALL SIGNAL COMBINATION FOR COLOUR TV

#### GENERAL DESCRIPTION

The integration into a single package of all small signal functions required for colour TV reception is achieved in the TDA4502A. The only additional circuits required for colour TV reception are the deflection output stages, a sound detector and amplifier, and a colour decoder.

The IC includes a vision IF amplifier and video switching circuit, AFC circuit, AGC detector with tuner output, an integral three-level sandcastle pulse generator, fully synchronized vertical and horizontal drive outputs and a mute circuit with external availability. A triggered vertical divider automatically adapts to 50 or 60 Hz operating mode thereby eliminating the need for external vertical frequency control. The sound signal must be demodulated and amplified externally.

#### **Features**

- Vision IF amplifier with synchronous demodulator

- AGC detector, suitable for negative modulation

- AGC output to tuner

- AFC circuit with ON/OFF switch

- Video preamplifier

- Video switch to select the internal, or an external, video signal

- Horizontal synchronization circuit with two control loops

- Vertical synchronization (divider system) and sawtooth generation with automatic amplitude adjustment for 50 and 60 Hz

- Transmitter identification (mute)

- Sandcastle pulse generator

#### QUICK REFERENCE DATA

| parameter                           | symbol           | min. | typ. | max.  | unit |

|-------------------------------------|------------------|------|------|-------|------|

| Supply voltage (pin 7)              | V <sub>7</sub>   | 9.5  | 12   | 13.2  | ٧    |

| Supply current (pin 7)              | 17               | _    | 125  | -     | mA   |

| Supply current (pin 11)             | V <sub>11</sub>  | _    | 6.0  | 8.5   | mA   |

| Operating ambient temperature range | T <sub>amb</sub> | -25  | _    | + 65  | oC   |

| Storage temperature range           | T <sub>stg</sub> | 25   | -    | + 150 | oC   |

| Total power dissipation             | P <sub>tot</sub> | -    | -    | 2.3   | W    |

#### PACKAGE OUTLINE

28-lead DIL; plastic with internal heat spreader (SOT117).

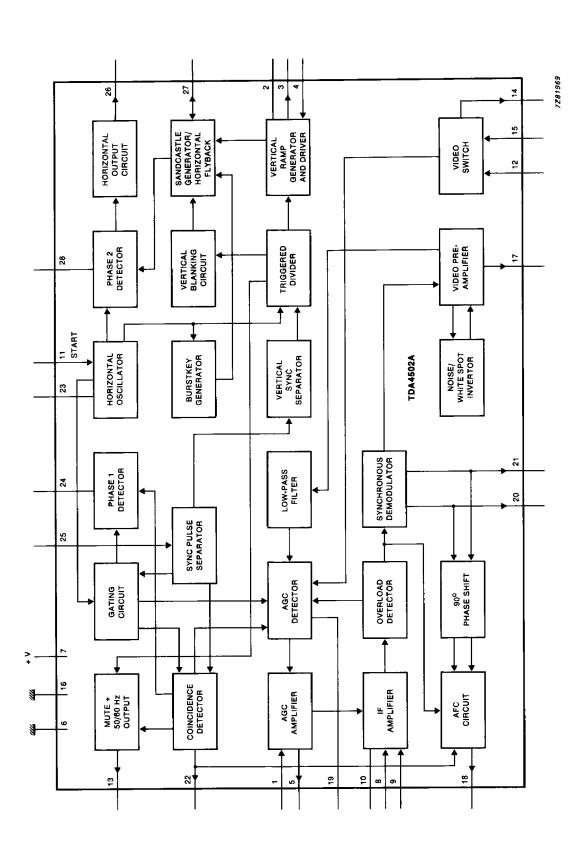

Fig. 1 Block diagram.

#### **PINNING**

- 1. AGC take over input

- 2. Ramp generator

- 3. Vertical drive output

- 4. Vertical feedback input

- 5. Tuner AGC output

- 6. Ground

- 7. Supply

- 8. IF input

- 9. IF input

- 10. Decoupling capacitor

- 11. Start horizontal oscillator input

- 12. External video input

- 13. Mute output

- 14. Video switch output

- 15. Internal video and switch input

- 16. Ground

- 17. Video output

- 18. AFC output

- 19. AGC detection

- 20. Synchronous demodulator output

- 21. Synchronous demodulator output

- 22. Coincidence detector output

- 23. Horizontal oscillator

- 24. Phase 1 detector

- 25. Sync separator

- 26. Horizontal drive output

- 27. Sandcastle output/flyback input

- 28. Phase 2 detector

#### **FUNCTIONAL DESCRIPTION**

### IF amplifier, synchronous demodulator and AFC

The IF amplifier (pins 8 and 9) has a symmetrical input, the impedance of which enables SAW-filtering to be used. The synchronous demodulator and the AFC circuit share an external reference tuned circuit (pins 20 and 21). An internal RC-network provides the necessary phase-shift for AFC operation. The AFC circuit provides a control voltage output with a voltage swing greater than 9 V at pin 18. In the internal and external mode the AFC can be switched OFF when pin 22 is connected to positive supply.

#### **AGC** circuit

AGC gating is performed to reduce sensitivity of the IF amplifier to external noise. The AGC time constant is provided by an RC-circuit connected to pin 19. The tuner AGC voltage is supplied from pin 5. The point of tuner take-over is preset by the voltage level at pin 1.

#### Video switch circuit

The IC has a video switch with two video inputs and one video output. One input is connected to the demodulated IF signal which is also fed to the video output pin of the peritelevision connector. The other input can be switched to an external signal which is applied to the video input of the peritelevision connector. The video output signal of the switch is fed to pin 25 of the IC, which is the synchronization part and, to the colour decoder. When the video switch is in the external mode, the synchronization circuit is switched to the external signal. The vision IF, AGC and AFC circuits will not be affected by the switching action and will, therefore, operate in the normal mode. Gating for the AGC detector is switched OFF when the switch is in the external mode. The first control loop is not switched to a low time constant when weak signals are received.

#### Horizontal oscillator start function

The horizontal oscillator start function is achieved by applying a current of 8.5 mA to pin 11 during the switch-on period. This current can be taken from the mains rectifier. The main supply, pin 7, can then be obtained from the horizontal output stage. The load current of the driver has to be added to the start current.

#### Horizontal synchronization

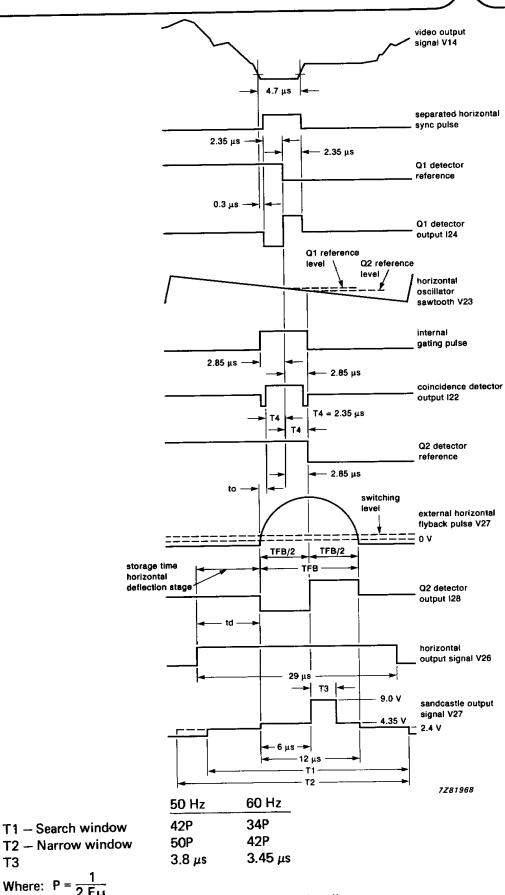

The positive video input signal is applied to pin 25. The horizontal synchronization has two control loops which have been introduced to generate a sandcastle pulse. By using the oscillator sawtooth, an accurate timing of the burst-key pulse can be made. Therefore, the phase of this sawtooth pulse must have a fixed relationship to the sync pulse.

#### Horizontal phase detector

The circuit has two operating conditions:

- (a) Synchronized

- The first loop has a fixed time constant and a gated phase detector, this enables optimum performance for co-channel interference. The VCR mode is obtained by an additional load on pin 22.

- (b) Non-synchronized In this condition the time constant is the same as during the VCR mode.

#### Vertical sync pulse

The vertical sync pulse integrator will not be disturbed when the vertical sync pulses have a width of  $10 \mu s$  and a separation of 22  $\mu s$ . This type of vertical sync pulse is generated by video tapes with anti-copy guard.

#### Vertical divider system

A synchronized divider system generates the vertical sawtooth waveforms at pin 2. The system uses an internal frequency doubler circuit to enable the horizontal oscillator to operate at its normal line frequency. One line period equals 2 clock pulses.

Using the divider system avoids the requirement for vertical frequency adjustment. The divider has a discriminator window for automatic switching from 50 Hz to 60 Hz mode. When the trigger pulse arrives before line 576 the 60 Hz mode is selected, if not, the 50 Hz mode is selected.

The divider system operates with two different reset windows to give maximum interference/disturbance protection. The windows are activated via an up/down counter.

The counter is increased by 1 each time the separated vertical sync pulse is within the narrow window. When the sync pulse is not within the narrow window the counter is decreased by 1.

The operation modes of the divider system are as follows:

#### Mode A

Large (search) window (divider ratio between 488 and 722)

This mode is valid for the following conditions:

- Divider is looking for a new transmitter

- Divider ratio found not within the narrow window limits

- A non-standard composite video signal is detected when a double or enlarged vertical sync pulse is detected after the internally generated anti-top-flutter pulse has ended. This means a vertical sync pulse width > 10 clock pulses (50 Hz); > 12 clock pulses (60 Hz). This mode is normally activated for video tape recorders operating in the feature trick mode

- Up/down counter value of the divider system, operating in the narrow window mode, drops below count 6

#### Mode B

Narrow window (divider ratio between 522 to 528 (60 Hz) or 622 to 628 (50 Hz))

The divider system switches over to this mode when the up/down counter has reached its maximum value of 15 approved vertical sync pulses. When the divider operates in this mode and, a vertical sync pulse is missing within the window, the divider is reset at the end of the window and the counter value is decreased by 1. At a counter value below 6 the divider system switches over to the large window mode.

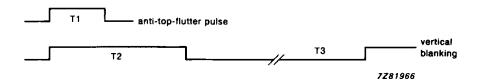

The divider system also generates an anti-top-flutter pulse which inhibits the Phase 1 detector during the vertical sync pulse. The pulse width is dependent on the divider mode. In 'Mode A' the start is generated by resetting the divider. In 'Mode B' the anti-top-flutter pulse starts at the beginning of the first equalizing pulse. The anti-top-flutter pulse ends at count 10 for the 50 Hz mode and count 12 for the 60 Hz mode.

The vertical blanking pulse is also generated via the divider system. The start is initiated by resetting the divider while the blanking pulse width is at count 34, (17 lines), for the 60 Hz mode and at count 42, (21 lines), for the 50 Hz mode. The vertical blanking pulse, at the sandcastle output (pin 27), is generated by adding the anti-top-flutter pulse to the blanking pulse. When the divider operates in 'Mode B', the vertical blanking pulse starts at the beginning of the first equalizing pulse. The length of the vertical blanking in this condition is 21 lines in the 60 Hz mode and 25 lines in the 50 Hz mode.

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                           | symbol                            | min. | max.  | unit     |

|-------------------------------------|-----------------------------------|------|-------|----------|

| Supply voltage                      | V <sub>P</sub> = V <sub>7-6</sub> | _    | 13.2  | <b>V</b> |

| Total power dissipation             | P <sub>tot</sub>                  | -    | 2.3   | w        |

| Operating ambient temperature range | T <sub>amb</sub>                  | -25  | + 65  | оС       |

| Storage temperature range           | T <sub>stg</sub>                  | -25  | + 150 | °C       |

#### **CHARACTERISTICS**

$V_P = V_7 = 12 \text{ V}$ ;  $T_{amb} = 25 \, ^{o}\text{C}$ ; unless otherwise specified; all voltages are referenced to ground (pin 6) unless otherwise specified

| parameter                                                         | conditions | symbol               | min. | typ. | max. | unit |

|-------------------------------------------------------------------|------------|----------------------|------|------|------|------|

| Supplies                                                          |            |                      |      |      |      |      |

| Supply voltage (pin 7)                                            |            | V7                   | 9.5  | 12.0 | 13.2 | V    |

| Supply current (pin 7)                                            |            | 17                   | -    | 125  | -    | mA   |

| Supply current (pin 11)                                           | note 1     | 111                  | _    | 6    | 8.5  | mA   |

| Vision IF amplifier (pins 8 and 9)                                |            |                      |      |      |      |      |

| Input sensitivity at 38.9 MHz                                     | note 2     | V <sub>8</sub>       | 40   | 80   | 120  | μV   |

| Input sensitivity at 45.75 MHz                                    | note 2     | V <sub>8</sub>       | -    | 100  | -    | μV   |

| Differential input resistance (pin 8 to pin 9)                    | note 3     | R <sub>8-9</sub>     | 0.8  | 1.3  | 1.8  | kΩ   |

| Differential input capacitance (pin 8 to pin 9)                   | note 3     | C <sub>8-9</sub>     | _    | 5    | _    | pF   |

| Gain control range                                                |            | G <sub>8-9</sub>     | _    | 62   | -    | dB   |

| Maximum input signal                                              |            | V <sub>8-9</sub>     | 50   | 100  | -    | mV   |

| Expansion of output signal for 50 dB variation of input signal    | note 4     | ΔV <sub>17</sub>     | _    | 1    | _    | dB   |

| Video amplifier                                                   | note 5     |                      |      |      |      |      |

| Output level for zero signal input                                | note 6     | V <sub>17</sub>      | 3.3  | 3.7  | 4.1  | V    |

| Output signal top sync level                                      |            | V <sub>17</sub>      | 1.5  | 1.7  | 1.9  | V    |

| Amplitude of video output signal (peak-to-peak value)             | note 7     | V <sub>17(p-p)</sub> | 1.4  | 1.8  | 2.2  | v    |

| Internal bias current of output transistor (npn emitter follower) |            | <sup>1</sup> 17(int) | 1.4  | 2.0  |      | mA   |

| Bandwidth of demodulated<br>output signal                         |            | В                    | 4.0  | 5.0  | _    | MHz  |

| Differential gain                                                 | note 8     | G <sub>17</sub>      | -    | 5    | 10   | %    |

| Differential phase                                                | note 8     | $\varphi$            |      | 5    | 10   | %    |

| parameter                                                                                                    | conditions            | symbol                | min.                 | typ.                 | max.         | unit                 |

|--------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------|----------------------|--------------|----------------------|

| Video non-linearity                                                                                          | note 9                | NL                    | _                    | 5                    | 12           | %                    |

| Intermodulation  f = 1.1 MHz; blue  f = 1.1 MHz; yellow  f = 3.3 MHz; blue  f = 3.3 MHz; yellow              | note 10               |                       | 47<br>45<br>50<br>48 | 50<br>47<br>55<br>52 | <br> -<br> - | dB<br>dB<br>dB<br>dB |

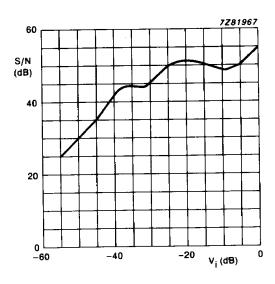

| Signal-to-noise ratio<br>input signal = 10 mV<br>end of gain control range as<br>a function of input voltage | note 11 see Fig. 5    | S/N<br>S/N            | 45<br>50             | 50<br>55             | <br> -<br> - | dB<br>dB             |

| Residual carrier signal                                                                                      | 1                     |                       | -                    | 7                    | 30           | mV                   |

| Residual 2nd harmonic of carrier signal                                                                      |                       |                       | _                    | 15                   | 30           | mV                   |

| Video switching circuit External video input (positive video; pin 12)                                        | note 12               |                       |                      |                      |              |                      |

| Input signal (peak-to-peak value)                                                                            | $V_0 = 2.4 V_{(p-p)}$ | V <sub>12</sub> (p-p) | -                    | 0.9                  | -            | V                    |

| Input current                                                                                                |                       | 112                   | -                    | 3.5                  | -            | μΑ                   |

| Top sync clamping level                                                                                      |                       | V <sub>12</sub>       | -                    | 3.4                  | -            | V                    |

| Video output<br>(positive video; pin 14)                                                                     |                       |                       |                      |                      |              |                      |

| Output signal                                                                                                |                       | V <sub>14</sub>       | 2.2                  | 2.4                  | 2.6          | V                    |

| Top sync level                                                                                               |                       | V <sub>14</sub>       | 2.4                  | 3.0                  | 3.6          | V                    |

| Internal bias current npn<br>output transistor                                                               |                       | 114                   | 0.8                  | -                    | -            | mA                   |

| Crosstalk of video signal                                                                                    | measured at 4.4 MHz   |                       |                      |                      |              |                      |

| external to internal internal to external                                                                    |                       | αα                    | 50<br>42             | 55<br>46             | _            | dB<br>dB             |

| Internal video and switch input (pin 15)                                                                     |                       |                       |                      |                      |              |                      |

| Amplitude of input signal (peak-to-peak value)                                                               | $V_0 = 2.4 V_{(p-p)}$ | V <sub>15</sub> (p-p) | _                    | 1.8                  | -            | v                    |

| Input current                                                                                                |                       | 1 <sub>15</sub>       | -                    | 7                    | -            | μΑ                   |

| Top sync clamping level (via 100 kΩ to ground)                                                               |                       | V <sub>15</sub>       | -                    | 4.2                  | -            | V                    |

| Condition for internal signal                                                                                | note 12               |                       |                      |                      |              |                      |

| Condition for external signal (via 100 kΩ to positive supply)                                                |                       | V <sub>15</sub>       |                      | 10                   | 12           | V                    |

### **CHARACTERISTICS** (continued)

| parameter                                                       | conditions             | symbol               | min.       | typ.       | max.  | unit             |

|-----------------------------------------------------------------|------------------------|----------------------|------------|------------|-------|------------------|

| Tuner AGC                                                       |                        |                      |            |            |       |                  |

| Minimum starting point take over* (RMS value)                   | I = 0.2 mA             | V <sub>1(rms)</sub>  | _          | _          | 0.5   | m∨               |

| Maximum starting point take over* (RMS value)                   | I = 0.2 mA             | V <sub>1(rms)</sub>  | 50         | 100        | _     | mV               |

| Maximum output swing                                            |                        | 1 <sub>5max</sub>    | 6          | 8          | -     | mA               |

| Output saturation voltage                                       | l = 2 mA               | V <sub>5(sat)</sub>  | -          | 100        | 300   | mV               |

| Leakage current                                                 |                        | 15                   | -          | 0.7        | 1.0   | μΑ               |

| Input signal variation complete tuner control                   | ∆l <sub>5</sub> = 2 mA | ΔVi                  | 0.1        | 2.0        | 5.0   | dB               |

| Minimum voltage take over (pin 1)                               |                        | V <sub>1</sub>       | _          | _          | 1     | V                |

| AFC circuit (pin 18)                                            | note 13                |                      |            |            |       |                  |

| AFC output voltage swing (peak-to-peak value)                   |                        | V <sub>18(p-p)</sub> | 9.5        | 10.2       | 11.5  | v                |

| Available output current                                        |                        | l <sub>18</sub>      | -          | ± 2.2      |       | mA               |

| Control steepness                                               |                        |                      | 70         | 100        | 150   | mV/kHz           |

| Output voltage at nominal tuning of the reference tuned circuit |                        | V <sub>18</sub>      | -          | 6          | _     | v                |

| Offset current AFC output (pins 20 and 21 short-circuited)      |                        | 118                  | _          | 0          | ± 220 | μΑ               |

| Horizontal synchronization                                      | Fig. 7                 |                      |            |            |       |                  |

| Sync separator and first control loop (pin 25)                  |                        |                      |            |            |       |                  |

| Sync pulse amplitude                                            | note 14                | V <sub>25</sub>      | 200        | _          | -     | mV               |

| Input current                                                   | $V_{25} = > 5 V$       | 125                  | -          | 10         | _     | μΑ               |

| Input current                                                   | V <sub>25</sub> = 0 V  | 125                  | -          | -10        | _     | mA               |

| Holding range PLL                                               |                        | ∆f                   | -          | ± 1.1      | ± 1.5 | kHz              |

| Catching range PLL                                              |                        | ∆f                   | + 0.6      | ± 1.0      | -     | kHz              |

| Control sensitivity in sync condition in non-sync condition     | note 15                | $\Delta_{	ext{td}}$  | <br> -<br> | 2.5<br>7.5 | _<br> | kHz/μs<br>kHz/μs |

| Second control loop<br>(positive edge)                          |                        |                      |            |            |       |                  |

| Control sensitivity                                             | note 16                | ∆t <sub>d</sub> /∆to | -          | 50         | -     |                  |

| Control range                                                   |                        | td                   |            | 25         | -     | μs               |

<sup>\*</sup> Take over to be adjusted by a potentiometer with a value of 47 k $\Omega$ .

| parameter                                                                                          | conditions              | symbol                                                | min.              | typ.               | max.            | unit   |

|----------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------|-------------------|--------------------|-----------------|--------|

| Phase adjustment (via second control loop)                                                         |                         |                                                       | i                 |                    |                 |        |

| Control sensitivity                                                                                |                         |                                                       | -                 | 25                 | -               | μΑ/μs  |

| Maximum allowed phase shift                                                                        |                         | α                                                     | -                 | ± 2                | -               | μs     |

| Horizontal oscillator (pin 23)                                                                     |                         |                                                       |                   |                    |                 |        |

| Free running frequency                                                                             | R = *;<br>C = 2.7 nF    | ffr                                                   | _                 | 15625              | _               | Hz     |

| Spread with fixed external components                                                              | į                       | $\Delta_{f}$                                          | _                 | -                  | 4               | %      |

| Frequency variation due to<br>change of supply voltage<br>from 9.5 to 13.2 V                       |                         | ∆ffr                                                  | _                 | 0                  | 0.5             | %      |

| Frequency variation with temperature                                                               |                         | тс                                                    | _                 | _                  | 1.6             | Hz/°C  |

| Maximum frequency shift                                                                            |                         | $\Delta f_{fr}$                                       | -                 | 4                  | 10              | %      |

| Maximum frequency deviation<br>at start horizontal out                                             |                         | $\Delta f_{fr}$                                       | 0                 | + 8                | + 10            | %      |

| Horizontal output (pin 26)                                                                         |                         |                                                       |                   |                    |                 |        |

| Output voltage high                                                                                |                         | V <sub>26</sub>                                       | -                 | _                  | 13.2            | V      |

| Output voltage at which protection commences                                                       |                         | V <sub>26</sub>                                       | _                 | _                  | 15.8            | v      |

| Output voltage low                                                                                 | I <sub>26</sub> = 10 mA | V <sub>26</sub>                                       | -                 | 0.3                | 0.5             | ٧      |

| Duty factor of horizontal output signal                                                            | $t_p = 10 \mu s$        | d                                                     | _                 | 45                 | _               | %      |

| Duty factor during start-up                                                                        |                         | d                                                     | -                 | 52                 | -               | %      |

| Rise time of output pulse                                                                          |                         | t <sub>r</sub>                                        | -                 | 260                | -               | ns     |

| Fall time of output pulse                                                                          |                         | tf                                                    | -                 | 100                | -               | ns     |

| Horizontal flyback input and sandcastle output                                                     | note 17                 |                                                       |                   |                    |                 |        |

| Input current required during flyback pulse                                                        |                         | 127                                                   | 0.1               | -                  | 2.0             | mA     |

| Output voltage<br>during burst-key pulse<br>during horizontal blanking<br>during vertical blanking |                         | V <sub>27</sub><br>V <sub>27</sub><br>V <sub>27</sub> | 8.4<br>4.1<br>2.1 | 9.0<br>4.35<br>2.4 | -<br>5.0<br>2.7 | V<br>V |

<sup>\*</sup> Value to be fixed.

## CHARACTERISTICS (continued)

| parameter                                                  | conditions     | symbol               | min.   | typ.     | max.       | unit   |

|------------------------------------------------------------|----------------|----------------------|--------|----------|------------|--------|

| Horizontal flyback input and sandcastle output (continued) |                |                      |        |          |            |        |

| Pulse width                                                |                |                      |        | 0.45     | 2.0        | _      |

| burst-key pulse                                            | 60 Hz          | tw                   | 3.1    | 3.45     | 3.9        | μs     |

| burst-key pulse                                            | 50 Hz          | t <sub>w</sub>       | 3.5    | 3.8      | 4.4        | μs     |

| horizontal blanking pulse                                  |                |                      | TIYDAC | k pulser | <br>       | I      |

| vertical blanking pulse<br>50 Hz divider in search         |                |                      |        |          |            |        |

| window                                                     |                |                      | -      | 21       | _          | lines  |

| 60 Hz divider in search                                    |                |                      |        |          | 1          |        |

| window                                                     |                |                      | -      | 17       | -          | lines  |

| 50 Hz divider in narrow                                    |                |                      |        | 0.5      |            |        |

| window                                                     |                |                      | -      | 25       | -          | lines  |

| 60 Hz divider in narrow                                    |                |                      | _      | 21       |            | lines  |

| window                                                     |                |                      |        | - '      |            | 111103 |

| Delay between start of sync pulse                          |                |                      |        |          |            |        |

| at video output and trailing edge of burst-key pulse       |                |                      | _      | _        | 9.2        | μs     |

| eage of burst-key pulse                                    |                |                      |        |          | 0.2        |        |

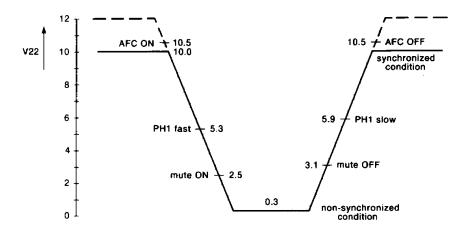

| Coincidence detector mute                                  |                |                      |        |          |            |        |

| output (pin 22)                                            | Fig 6; note 18 |                      |        |          |            |        |

| Voltage for in-sync condition                              | 1              | V <sub>22</sub>      | 8.5    | 10.0     | 10.5       | V      |

| Voltage for no-sync condition                              | no signal      | V <sub>22</sub>      | 0      | 0.3      | 0.6        | V      |

| Switching level to switch phase                            |                |                      |        |          |            |        |

| detector from slow to fast                                 |                | V <sub>22</sub>      | 4.9    | 5.3      | 5.8        | V      |

| Hysteresis                                                 |                | V <sub>22</sub>      | -      | 0.6      | -          | \ \    |

| Voltage for AFC switch-off                                 |                | V <sub>22</sub>      | -      | 10.5     | 11.0       | V      |

| Switching level to activate mute                           |                |                      |        |          |            |        |

| function                                                   |                | V <sub>22</sub>      | 2.25   | 2.5      | 2.75       | ٧      |

| Hysteresis mute function                                   |                | V <sub>22</sub>      | -      | 0.6      | -          | ٧      |

| Output current                                             |                |                      |        |          |            |        |

| (peak-to-peak value)                                       | in-sync        | <sup>1</sup> 22(p-p) | 0.7    | 1.0      | <u> </u> — | mA     |

| Discharge current                                          |                |                      |        |          | ]          |        |

| (peak-to-peak value)                                       |                | 122(p-p)             | -      | 0.5      | -          | mA     |

| Video transmitter identification                           |                |                      |        |          |            |        |

| output (pin 13)                                            |                |                      |        |          |            |        |

| Output voltage active                                      | no-sync;       |                      |        |          |            |        |

|                                                            | I = 5 mA       | V <sub>13</sub>      |        | 0.3      | 0.5        | V      |

| Output current active                                      |                | 113                  | _      | _        | 5          | mA     |

| Output current inactive                                    | sync           |                      | _      | l_       | 1          | μА     |

| Output current mactive                                     | SYIIC          | 113                  |        |          | 1'         | , m,   |

| parameter                                                   | conditions              | symbol                             | min. | typ.      | max.     | unit   |

|-------------------------------------------------------------|-------------------------|------------------------------------|------|-----------|----------|--------|

| 50/60 Hz identification (pin 13)                            |                         |                                    |      |           |          |        |

| Output voltage<br>50 Hz<br>60 Hz                            |                         | V <sub>13</sub><br>V <sub>13</sub> | 9    | 12<br>6.0 | -<br>6.4 | v<br>v |

| Vertical ramp generator (pin 2)                             | note 19                 |                                    |      |           |          |        |

| Input current during scan                                   |                         | 12                                 | -    | 1         | 2        | μΑ     |

| Discharge current during retrace                            |                         | 12                                 | 0.3  | 0.35      | -        | mA     |

| Sawtooth amplitude (peak-to-peak value)                     |                         | V <sub>2(p-p)</sub>                | -    | 0.8       | 1.1      | V      |

| Vertical drive output (pin 3)                               |                         | ,                                  |      |           |          |        |

| Maximum available output current                            |                         | lз                                 | 1.5  | 3.5       | -        | mA     |

| Maximum output voltage                                      |                         | V <sub>3</sub>                     | -    | 4         | -        | V      |

| Vertical feedback input (pin 4)                             | <u> </u>                |                                    |      |           |          |        |

| Input voltage DC component                                  |                         | V4                                 | 2.4  | 3.0       | 4.1      | V      |

| AC component (peak-to-peak value)                           |                         | V <sub>4(p-p)</sub>                | -    | 1.2       | _        | V      |

| Input current                                               |                         | 14                                 | -    | -         | 12       | μΑ     |

| Internal precorrection to sawtooth                          |                         | Δt <sub>p</sub>                    |      | 6         | _        | %      |

| Deviation amplitude                                         | 50/60 Hz                |                                    | -    | -         | 2        | %      |

| Vertical guard                                              | note 20                 |                                    |      |           |          |        |

| Active at a deviation with respect to the DC feedback level | V <sub>27</sub> = 2.5 V |                                    |      |           |          |        |

| switching voltage level LOW switching voltage level HIGH    |                         | ΔV <sub>4</sub><br>ΔV <sub>4</sub> | 0.6  | 0.9       | <br> -   | V      |

#### Notes to the characteristics

- 1. The horizontal oscillator can be started when a current of 8.5 mA is applied to pin 11; this current can be taken from the mains rectifier. The main supply (pin 7) can then be derived from the horizontal output stage. The load current of the driver must be added to the start current (8.5 mA).

- 2. On set AGC.

- 3. Input impedance selected so that a SAW-filter can be applied.

- 4. Measured with 0 dB = 150  $\mu$ V.

- 5. Measured at 10 mV(rms) top sync input signal.

- 6. Projected zero point with switched demodulator.

- 7. Signal with negative going sync top white level 10% of the top sync amplitude.

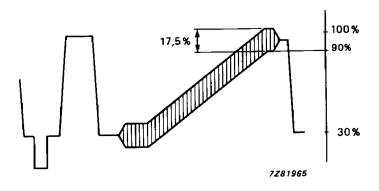

- 8. Measured in accordance with the test line given in Fig. 2. The differential gain is expressed as a percentage of the difference in peak amplitudes between the largest and smallest value relative to the subcarrier amplitude at blanking level. The differential phase is defined as the difference in degrees between the largest and smallest phase angle.

#### Notes to the characteristics (continued)

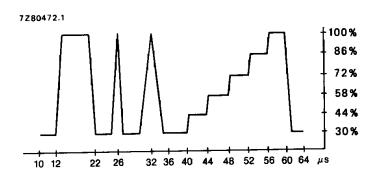

- 9. This figure is valid for the complete video signal amplitude (peak white to black) and measured with a 6.6 k $\Omega$  damping resistor connected between pins 20 and 21 (see Fig. 3).

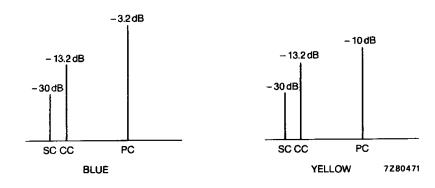

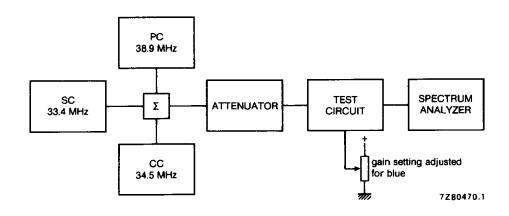

- 10. The test set-up and input conditions are given in Fig. 4. The figures are measured at an input signal of 10 mV(rms).

- 11. Measured with a source impedance of 75  $\Omega$ , where:

$$S/N = 20 log \frac{V_0 black-to-white}{V_{n(rms)} at B = 5 MHz}.$$

- 12. The internal video and video switch inputs are applied to pin 15. By externally connecting the internal video signal to the video switch enables the sound trap to be connected between pins 15 and 17. When the video signal is applied internally to the switch then sound traps are required at two outputs. The switch is activated via a 100 kΩ resistor. When the resistor is connected to ground or left open-circuit the internal video signal is available at pin 14. When the resistor is connected to + V<sub>S</sub> the external video signal is available at pin 14. When the video switch is in the external mode the AFC can still be switched off when pin 22 is connected to the supply voltage.

- 13. The measured figures are obtained at an input signal of 10 mV(rms) and the AFC output loaded with 2 x 100 k $\Omega$  between the supply voltage and ground. The unloaded Q-factor of the reference tune circuit is 70. The AFC is switched off when pin 22 is connected to the supply voltage.

- 14. The minimum value is obtained by connecting a 1.8 k $\Omega$  series resistor between pins 14 and 25. The slicing level can be varied by changing the value of this resistor (a higher resistor value will result in a higher value of the minimum sync pulse amplitude). The slicing level is independent of the video information.

- 15. Frequency control is obtained by supplying a correction current to the oscillator RC network via a resistor between pins 23 and 24. The oscillator can be adjusted to the correct frequency using either of the following methods:

- (a) Interrupt the resistor between pins 23 and 24.

- (b) Short-circuit the sync separator bias network (pin 25 to supply voltage).

- The device uses a long time constant for the first phase detector. The phase detector is gated to obtain optimal performance for co-channel interference. The VCR mode must be switched on via pin 22.

- 16. This figure is valid for an external load impedance of 82 k $\Omega$  connected between pin 28 and the shift-adjustment potentiometer.

- 17. The flyback input and sandcastle output are combined at pin 27. The flyback pulse is clamped to a level of 4.35 V. The minimum current required to drive the second control loop is 0.1 mA.

- 18. The functions in-sync/out-of-sync and transmitter identification are combined at pin 22. The 22 nF capacitor is charged during the sync pulse and discharged during the time difference between gating and sync pulse.

- 19. Because the vertical scan is synchronized via a divider system, no adjustment is required for the ramp generator. The divider system detects whether the incoming signal has a vertical frequency of 50 or 60 Hz and subsequently corrects the vertical amplitude.

- 20. To avoid screenburn, due to a collapse of the vertical deflection, a continuous blanking level is inserted in the sandcastle pulse when the feedback voltage from the vertical deflection is not within the specified limits.

Fig. 2 Video output signal.

Fig. 3 EBU test signal waveform (line 330).

Downloaded from Elcodis.com electronic components distributor

Input signal conditions:

SC = sound carrier

CC = chrominance carrier

PC = picture carrier

all with respect to top sync level.

Where:

Value at 1.1 MHz: 20 log  $\frac{V_0 \text{ at } 4.4 \text{ MHz}}{V_0 \text{ at } 1.1 \text{ MHz}} + 3.6 \text{ dB}$

Value at 3.3 MHz:  $20 \log \frac{V_0 \text{ at } 4.4 \text{ MHz}}{V_0 \text{ at } 3.3 \text{ MHz}}$

Fig. 4 Test set-up intermodulation.

Fig. 5 S/N ratio as a function of the input voltage (0 dB = 100 mV).

| condition                                        | control<br>horizontal os | vertical sync<br>separator |               |

|--------------------------------------------------|--------------------------|----------------------------|---------------|

|                                                  | T2 – <b>T</b> 1          | T3 = scan                  | pulse after   |

| V22 > 5.9<br>and<br>strong signal<br>weak signal | 2.5<br>2.5               | 2.5<br>2.5                 | 16 μs<br>9 μs |

| V22 < 5.3<br>and<br>strong signal<br>weak signal | 7.5<br>7.5               | 7.5<br>7.5                 | 16 μs<br>9 μs |

Fig. 6 Switching levels coincidence detector.

Where: P =

T1 - Search window

Fig. 7 Timing diagram.

Fig. 8 Application diagram.

Downloaded from Elcodis.com electronic components distributor