February 1989 Revised January 1999

## 74ACT2708 64 x 9 First-In, First-Out Memory

## **General Description**

The ACT2708 is an expandable first-in, first-out memory organized as 64 words by 9 bits. An 85 MHz shift-in and 60 MHz shift-out typical data rate makes it ideal for high-speed applications. It uses a dual port RAM architecture with pointer logic to achieve the high speed with negligible fall-through time.

Separate Shift-In (SI) and Shift-Out (SO) clocks control the use of synchronous or asynchronous write or read. Other controls include a Master Reset  $(\overline{MR})$  and Output Enable  $(\overline{OE})$  for initializing the internal registers and allowing the data outputs to be 3-STATE. Input Ready (IR) and Output Ready (OR) signal when the FIFO is ready for I/O operations. The status flags HF and FULL indicate when the FIFO is full, empty or half full.

The FIFO can be expanded to provide different word lengths by tying off unused data inputs.

#### **Features**

- 64-words by 9-bit dual port RAM organization

- 85 MHz shift-in, 60 MHz shift-out data rate, typical

- Expandable in word width only

- TTL-compatible inputs

- Asynchronous or synchronous operation

- Asynchronous master reset

- Outputs source/sink 8 mA

- 3-STATE outputs

- Full ESD protection

- Input and output pins directly in line for easy board layout

- TRW 1030 work-alike operation

## **Applications**

- · High-speed disk or tape controllers

- A/D output buffers

- High-speed graphics pixel buffer

- · Video time base correction

- · Digital filtering

## **Ordering Code:**

| Order Number | Package Number | Package Description                                                    |

|--------------|----------------|------------------------------------------------------------------------|

| 74ACT2708PC  | N28B           | 28-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600" Wide |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

## **Connection Diagram**

## **Pin Descriptions**

|    | Pin Names                    | Description         |  |  |  |  |  |

|----|------------------------------|---------------------|--|--|--|--|--|

| D  | <sub>0</sub> –D <sub>8</sub> | Data Inputs         |  |  |  |  |  |

| M  | R                            | Master Reset        |  |  |  |  |  |

| O  | Ē                            | Output Enable Input |  |  |  |  |  |

| SI |                              | Shift-In            |  |  |  |  |  |

| S  | 0                            | Shift-Out           |  |  |  |  |  |

| IR | !                            | Input Ready         |  |  |  |  |  |

| 0  | R                            | Output Ready        |  |  |  |  |  |

| н  | F                            | Half Full Flag      |  |  |  |  |  |

| Fl | JLL                          | Full Flag           |  |  |  |  |  |

| 0, | <sub>0</sub> –O <sub>8</sub> | Data Outputs        |  |  |  |  |  |

$\mathsf{FACT^{\scriptscriptstyle\mathsf{TM}}}$  is a trademark of Fairchild Semiconductor Corporation.

© 1999 Fairchild Semiconductor Corporation

DS010144.prf

## **Functional Description**

## **INPUTS**

#### Data Inputs (D<sub>0</sub>-D<sub>8</sub>)

Data inputs for 9-bit wide data are TTL-compatible. Word width can be reduced by trying unused inputs to ground and leaving the corresponding outputs open.

#### Reset (MR)

Reset is accomplished by pulsing the  $\overline{\text{MR}}$  input LOW. During normal operation  $\overline{\text{MR}}$  is HIGH. A reset is required after power up to guarantee correct operation. On reset, the data outputs go LOW, IR goes HIGH, OR goes LOW, FH and FULL go LOW. During reset, both internal read and write pointers are set to the first location in the array.

#### Shift-In (SI)

Data is written into the FIFO by pulsing SI HIGH. When Shift-In goes HIGH, the data is loaded into an internal data latch. Data setup and hold times need to be adhered to with respect to the falling edge of SI. The write cycle is complete after the falling edge of SI. The shift-in is independent of any ongoing shift-out operation. After the first word has been written into the FIFO, the falling edge of SI makes HF go HIGH, indicating a non-empty FIFO. The first data word appears at the output after the falling edge of SI. After half the memory is filled, the next rising edge of SI makes FULL go HIGH indicating a half-full FIFO. When the FIFO is full, any further shift-ins are disabled.

When the FIFO is empty and  $\overline{OE}$  is LOW, the falling edge of the first SI will cause the first data word just shifted-in to appear at the output, even though SO may be LOW.

#### Shift-Out (SO)

Data is read from the FIFO by the Shift-Out signal provided the FIFO is not empty. SO going HIGH causes OR to go LOW indicating that output stage is busy. On the falling edge of SO, new data reaches the output after propagation delay  $t_{\rm D}$ . If the last data has been shifted-out of the memory, OR continues to remain LOW, and the last word shifted-out remains on the output pins.

## Output Enable (OE)

$\overline{\text{OE}}$  LOW enables the 3-STATE output buffers. When  $\overline{\text{OE}}$  is HIGH, the outputs are in a 3-STATE mode.

## **OUTPUTS**

### Data Outputs (O<sub>0</sub>-O<sub>8</sub>)

Data outputs are enabled when  $\overline{OE}$  is LOW and in the 3-STATE condition when  $\overline{OE}$  is HIGH.

#### Input Ready (IR)

IR HIGH indicates data can be shifted-in. When SI goes HIGH, IR goes LOW, indicating input stage is busy. IR stays LOW when the FIFO is full and goes HIGH after the falling edge of the first shift-out.

## Output Ready (OR)

OR HIGH indicates data can be shifted-out from the FIFO. When SO goes HIGH, OR goes LOW, indicating output stage is busy. OR is LOW when the FIFO is reset or empty and goes HIGH after the falling edge of the first shift-in.

#### Half-Full (HF)

This status flag along with the FULL status flag indicates the degree of fullness of the FIFO. On reset, HF is LOW; it rises on the falling edge of the first SI. The rising edge of the SI pulse that fills up the FIFO makes HF go LOW. Going from the empty to the full state with SO LOW, the falling edge of the first SI causes HF to go HIGH, and the rising edge of the 33rd SI causes FULL to go HIGH, and the rising edge of the 64th SI causes HF to go LOW.

When the FIFO is full, HF is LOW and the falling edge of the first shift-out causes HF to go HIGH indicating a "nonfull" FIFO.

#### Full Flag (FULL)

This status flag along with the HF status flag indicates the degree of fullness of the FIFO. On reset, FULL is LOW. When half the memory is filled, on the rising edge of the next SI, the FULL flag goes HIGH. It remains set until the difference between the write pointer and the read pointer is less than or equal to one-half of the total memory of the device. The FULL flag then goes LOW on the rising edge of the next SO

## Status Flags Truth Table

| HF | FULL | Status Flag Condition |

|----|------|-----------------------|

| L  | L    | Empty                 |

| L  | Н    | Full                  |

| Н  | L    | <32 Locations Filled  |

| Н  | Н    | ≥32 Locations Filled  |

H = HIGH Voltage Level L = LOW Voltage Level

## Reset Truth Table

| Inputs |    |    | Outputs |    |    |      |                                |

|--------|----|----|---------|----|----|------|--------------------------------|

| MR     | SI | so | IR      | OR | HF | FULL | O <sub>0</sub> -O <sub>8</sub> |

| Н      | Х  | Х  | Х       | Х  | Х  | Х    | Х                              |

| L      | Χ  | Χ  | Н       | L  | L  | L    | L                              |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immateria

3

## **MODES OF OPERATION**

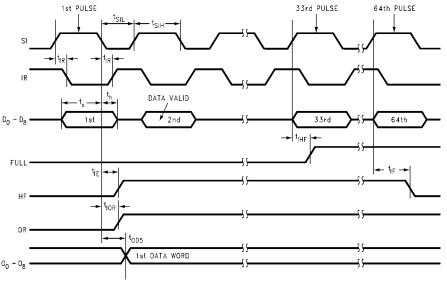

# Mode 1: Shift in Sequence for FIFO Empty to Full Sequence of Operation

- Input Ready is initially HIGH; HF and FULL flags are LOW. The FIFO is empty and prepared for valid data.

OR is LOW indicating that the FIFO is not yet ready to output data.

- 2. Shift-In is set HIGH, and data is loaded into the FIFO. Data has to be settled  $\rm t_s$  before the falling edge of SI and held  $\rm t_h$  after.

- 3. Input Ready (IR) goes LOW propagation delay  $t_{\rm IR}$  after SI goes HIGH: input stage is busy.

- 4. Shift-In is set LOW; IR goes HIGH indicating the FIFO is ready for additional data. Data just shifted-in arrives at output propagation delay t<sub>OD5</sub> after SI falls. OR goes HIGH propagation delay t<sub>IOR</sub> after SI goes LOW, indicating the FIFO has valid data on its outputs. HF goes HIGH propagation delay t<sub>IE</sub>after SI falls, indicating the FIFO is no longer empty.

- 5. The process is repeated through the 64th data word. On the rising edge of the 33rd SI, FULL flag goes HIGH propagation delay t<sub>IHF</sub> after SI, indicating a half-full FIFO. HF goes LOW propagation delay t<sub>IF</sub> after the rising edge of the 64th pulse indicating that the FIFO is full. Any further shift-ins are disabled.

Note: SO and  $\overline{\text{OE}}$  are LOW;  $\overline{\text{MR}}$  is HIGH.

FIGURE 1. Modes of Operation Mode 1

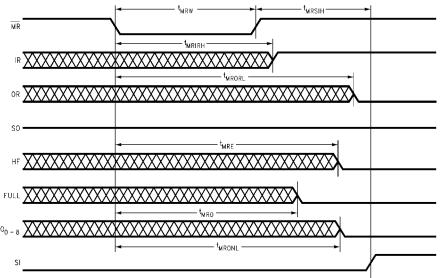

## Mode 2: Master Reset

#### Sequence of Operation

- 1. Input and Output Ready, HF and FULL can be in any state before the reset sequence with Master Reset  $(\overline{\rm MR})$  HIGH.

- Master Reset goes LOW and clears the FIFO, setting up all essential internal states. Master Reset must be LOW pulse width t<sub>MRW</sub> before rising again.

- 3. Master Reset rises.

- 4. IR rises (if not HIGH already) to indicate ready to write state recovery time t<sub>MRIRH</sub> after the falling edge of MR. Both HF and FULL will go LOW indicating an empty FIFO, occurring recovery times t<sub>MRE</sub> and t<sub>MRO</sub> respectively after the falling edge of MR. OR falls recovery time t<sub>MRORL</sub> after MR falls. Data at outputs goes LOW recovery time t<sub>MRONL</sub> after MR goes LOW.

- Shift-In can be taken HIGH after a minimum recovery time t<sub>MRSIH</sub> after MR goes HIGH.

FIGURE 2. Mode of Operation Mode 2

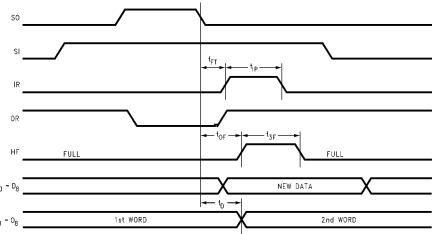

# Mode 3: With FIFO Full, Shift-In is Held HIGH in Anticipation of an Empty Location

### Sequence of Operation

- The FIFO is initially full and Shift-In goes HIGH. OR is initially HIGH. Shift-Out is LOW. IR is LOW.

- Shift-Out is pulsed HIGH, Shift-Out pulse propagates and the first data word is latched on the rising edge of SO. OR falls on this edge. On the falling edge of SO, the second data word appears after propagation delay

- $\ensuremath{t_{\text{D}}}.$  New data is written into the FIFO after SO goes LOW.

- 3. Input Ready goes HIGH one fall-through time,  $t_{\rm FT}$ , after the falling edge of SO. Also, HF goes HIGH one  $t_{\rm OF}$  after SO falls, indicating that the FIFO is no longer full.

- 4. IR returns LOW pulse width  $t_{\,\,|P}$  after rising and shifting new data in. Also, HF returns LOW pulse width  $t_{3F}$  after rising, indicating the FIFO is once more full.

- 5. Shift-In is brought LOW to complete the shift-in process and maintain normal operation.

Note:  $\overline{\text{MR}}$  and FULL are HIGH;  $\overline{\text{OE}}$  is LOW.

FIGURE 3. Modes of Operation Mode 3

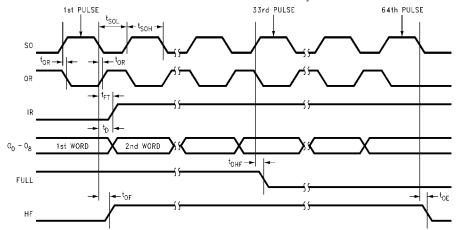

# Mode 4: Shift-Out Sequence, FIFO Full to Empty Sequence of Operation

- FIFO is initially full and OR is HIGH, indicating valid data is at the output. IR is LOW.

- SO goes HIGH, resulting in OR going LOW one propagation delay, t<sub>OR</sub>, after SO rises. OR LOW indicates output stage is busy.

- 3. SO goes LOW, new data reaches output one propagation delay,  $t_D$ , after SO falls; OR goes HIGH one propagation delay,  $t_{OR}$ , after SO falls and HF rises one

- propagation delay,  $t_{OF}$ , after SO falls. IR rises one fall-through time,  $t_{FT}$ , after SO falls.

- 4. Repeat process through the 64th SO pulse. FULL flag goes LOW one propagation delay, t<sub>OHF</sub>, after the rising edge of 33rd SO, indicating that the FIFO is less than half full. On the falling edge of the 64th SO, HF goes LOW one propagation delay, t<sub>OE</sub>, after SO, indicating the FIFO is empty. The SO pulse may rise and fall again with an attempt to unload an empty FIFO. This results in no change in the data on the outputs as the 64th word stays latched.

Note: SI and  $\overline{\text{OE}}$  are LOW;  $\overline{\text{MR}}$  is HIGH; D<sub>0</sub>–D<sub>8</sub> are immaterial.

FIGURE 4. Modes of Operation Mode 4

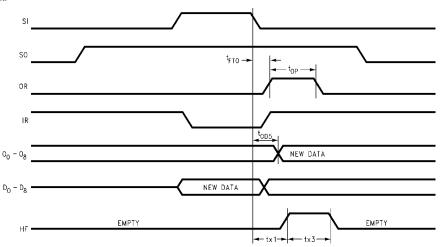

# Mode 5: With FIFO Empty, Shift-Out is Held HIGH in Anticipation of Data

### **Sequence of Operation**

- 1. FIFO is initially empty; Shift-Out goes HIGH.

- 2. Shift-In pulse loads data into the FIFO and IR falls. HF rises propagation delay  $t_{\rm X1}$  after the falling edge of SI.

- OR rises a fall-through time of t<sub>FTO</sub> after the falling edge of Shift-In, indicating that new data is ready to be output.

- 4. Data arrives at output one propagation delay,  $t_{\rm OD5}$ , after the falling edge of Shift-In.

- 5. OR goes LOW pulse width  $t_{OP}$  after rising and HF goes LOW pulse width  $t_{X3}$  after rising, indicating that the FIFO is empty once more.

- 6. Shift-Out goes LOW, necessary to complete the Shift-Out process.

$\textbf{Note:} \ \textbf{FULL} \ \text{is LOW;} \ \overline{\textbf{MR}} \\ \textbf{is HIGH;} \ \overline{\textbf{OE}} \ \text{is LOW;} \ t_{DOF} \\ = t_{FTO} - t_{OD5}. \ Data \ \text{output transition} \\ \textbf{we have all data arrives at output stage} \ t_{DOF} \ \text{after OR is HIGH.} \\ \textbf{OR} \ \textbf{O$

FIGURE 5. Modes of Operation Mode 5

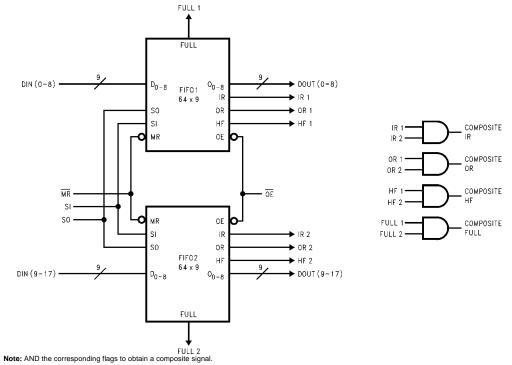

## **FIFO Expansion**

#### Word Width Expansion

Word width can be increased by connecting the corresponding input control signals of multiple devices. Flags can be monitored to obtain a composite signal by ANDing the corresponding flags.

## FIGURE 6. Word Width Expansion—64 x 18 FIFO

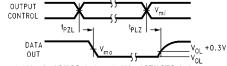

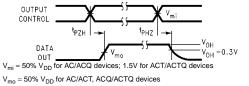

$V_{mi} = 50\% V_{DD}$  for AC/ACQ devices; 1.5V for ACT/ACTQ devices

$V_{mo} = 50\%\ V_{DD}$  for AC/ACT, ACQ/ACTQ devices

FIGURE 7. 3-STATE Output Low Enable and Disable Times for AC/ACT, ACQ/ACTQ

FIGURE 8. 3-STATE Output High Enable and Disable Times for AC/ACT, ACQ/ACTQ

## Absolute Maximum Ratings(Note 1)

Supply Voltage (V $_{CC}$ ) -0.5V to +7.0V

DC Input Diode Current (I<sub>IK</sub>)

$\begin{array}{ccc} V_I = -0.5 V & -20 \text{ mA} \\ V_I = V_{CC} + 0.5 V & +20 \text{ mA} \\ \text{DC Input Voltage (V_I)} & -0.5 V \text{ to } V_{CC} + 0.5 V \end{array}$

DC Output Diode Current (I<sub>OK</sub>)

$\begin{aligned} \text{V}_{\text{O}} &= -0.5 \text{V} & -20 \text{ mA} \\ \text{V}_{\text{O}} &= \text{V}_{\text{CC}} + 0.5 \text{V} & +20 \text{ mA} \\ \text{DC Output Voltage (V}_{\text{O}}) & -0.5 \text{V to V}_{\text{CC}} + 0.5 \text{V} \end{aligned}$

DC Output Source

or Sink Current ( $I_O$ )  $\pm 32 \text{ mA}$

${\rm DC}\ {\rm V}_{\rm CC}\ {\rm or}\ {\rm Ground}\ {\rm Current}$

per Output Pin ( $I_{CC}$  or  $I_{GND}$ )  $\pm 32$  mA Storage Temperature ( $T_{STG}$ )  $-65^{\circ}$ C to +150 $^{\circ}$ C

Junction Temperature  $(T_J)$  PDIP

# Recommended Operating Conditions

140°C

$V_{\mbox{\footnotesize{IN}}}$  from 0.8V to 2.0V

V<sub>CC</sub> @ 4.5V, 5.5V

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT™ circuits outside databook specifications.

## **DC Electrical Characteristics**

| Symbol           | Parameter                      | V <sub>CC</sub> | T <sub>A</sub> = 25°C |      | T <sub>A</sub> = -40° to +85°C | Units | Conditions                        |

|------------------|--------------------------------|-----------------|-----------------------|------|--------------------------------|-------|-----------------------------------|

|                  |                                | (V)             | Тур                   | Gu   | aranteed Limits                |       |                                   |

| V <sub>IH</sub>  | Minimum High Level             | 4.5             | 1.5                   | 2.0  | 2.0                            | V     | V <sub>OUT</sub> = 0.1V           |

|                  | Input Voltage                  | 5.5             | 1.5                   | 2.0  | 2.0                            |       | or V <sub>CC</sub> -0.1V          |

| V <sub>IL</sub>  | Maximum Low Level              | 4.5             | 1.5                   | 0.8  | 0.8                            |       | V <sub>OUT</sub> = 0.1V           |

|                  | Input Voltage                  | 5.5             | 1.5                   | 0.8  | 0.8                            |       | or V <sub>CC</sub> -0.1V          |

| V <sub>OH</sub>  | Minimum High Level             | 4.5             | 4.49                  | 4.4  | 4.4                            | V     | $I_{OUT} = -50 \mu A$             |

|                  |                                | 5.5             | 5.49                  | 5.4  | 5.4                            |       |                                   |

|                  |                                |                 |                       |      |                                |       | $V_{IN} = V_{IL}$ or $V_{IH}$     |

|                  |                                | 4.5             |                       | 3.86 | 3.76                           | V     | $I_{OH} = -8 \text{ mA}$          |

|                  |                                | 5.5             |                       | 4.86 | 4.76                           |       | $I_{OH} = -8 \text{ mA (Note 2)}$ |

| V <sub>OL</sub>  | Maximum Low Level              | 4.5             | 0.001                 | 0.1  | 0.1                            | V     | I <sub>OUT</sub> = 50 μA          |

|                  | Output Voltage                 | 5.5             | 0.001                 | 0.1  | 0.1                            |       |                                   |

|                  |                                |                 |                       |      |                                |       | $V_{IN} = V_{IL}$ or $V_{IH}$     |

|                  |                                | 4.5             |                       | 0.36 | 0.44                           | V     | $I_{OL} = 8 \text{ mA}$           |

|                  |                                | 5.5             |                       | 0.36 | 0.44                           |       | I <sub>OL</sub> = 8 mA (Note 2)   |

| I <sub>IN</sub>  | Maximum Input                  | 5.5             |                       | ±0.1 | ±1.0                           | μΑ    | $V_I = V_{CC}$ , GND              |

| l <sub>OZ</sub>  | Maximum                        | 5.5             |                       | ±0.5 | ±5.0                           | μΑ    | $V_I = V_{IL}, V_{IH}$            |

|                  | 3-STATE Current                |                 |                       |      |                                |       | $V_O = V_{CC}$ , GND              |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input | 5.5             | 0.6                   | 1.0  | 1.5                            | mA    | $V_I = V_{CC} - 2.1V$             |

| I <sub>OLD</sub> | Maximum Dynamic                | 5.5             |                       |      | 32                             | mA    | V <sub>OLD</sub> = 1.65V          |

| I <sub>OHD</sub> | Output Current (Note 3)        | 5.5             |                       |      | -32                            | mA    | $V_{OHD} = 3.85V$                 |

| I <sub>CC</sub>  | Maximum Quiescent              | 5.5             |                       | 8.0  | 80                             | μΑ    | $V_{IN} = V_{CC}$                 |

|                  | Supply Current                 |                 |                       |      |                                |       | or GND                            |

| I <sub>CCD</sub> | Supply Current                 | 5.5             | 125                   | 150  | 150                            | mA    | f = 20 MHz                        |

|                  | 20 MHz Loaded                  |                 |                       |      |                                |       | (Note 4)                          |

Note 2: All outputs loaded; thresholds on input associated with output under test.

Note 3: Maximum test duration 2.0 ms, one output loaded at a time.

Note 4: Test load 50 pF,  $500\Omega$  to ground

|                                     |                                       | v <sub>cc</sub> |     | $\textbf{T}_{\boldsymbol{A}} = +25^{\circ}\boldsymbol{C}$ |      | T <sub>A</sub> = -40°0 | C to +85°C |       |

|-------------------------------------|---------------------------------------|-----------------|-----|-----------------------------------------------------------|------|------------------------|------------|-------|

| Symbol                              | Parameter                             | (V)             |     | <b>C</b> <sub>L</sub> = 50 pF                             |      | C <sub>L</sub> =       | 50 pF      | Units |

|                                     |                                       | (Note 5)        | Min | Тур                                                       | Max  | Min                    | Max        |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>IR</sub>    | 5.0             | 2.0 | 6.5                                                       | 11.0 | 1.5                    | 12.5       | ns    |

|                                     | SI to IR                              |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>IR</sub>    | 5.0             | 2.0 | 6.5                                                       | 11.0 | 1.5                    | 12.0       | ns    |

|                                     | SI to IR                              |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>IHF</sub>   | 5.0             | 4.0 | 10.5                                                      | 17.0 | 4.0                    | 19.5       | ns    |

|                                     | SI to > HF                            |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>IF</sub>    | 5.0             | 4.5 | 10.5                                                      | 16.5 | 4.5                    | 19.5       | ns    |

|                                     | SI to Full Condition                  |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>IE</sub>    | 5.0             | 4.0 | 10.0                                                      | 15.5 | 4.0                    | 17.5       | ns    |

|                                     | SI to Not Empty                       |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>IOR</sub>   | 5.0             | 4.0 | 13.5                                                      | 16.5 | 4.0                    | 19.0       | ns    |

|                                     | SI to OR                              |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay t <sub>MRIRH</sub>  | 5.0             | 3.0 | 8.5                                                       | 13.5 | 3.0                    | 15.5       | ns    |

|                                     | MR to IR                              |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>MRORL</sub> | 5.0             | 7.0 | 16.5                                                      | 25.5 | 7.0                    | 29.0       | ns    |

|                                     | MR to OR                              |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>MRO</sub>   | 5.0             | 3.5 | 9.0                                                       | 14.0 | 3.5                    | 16.0       | ns    |

|                                     | MR to Full Flag                       |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>MRE</sub>   | 5.0             | 8.0 | 17.5                                                      | 27.5 | 8.0                    | 30.5       | ns    |

|                                     | MR to HF Flag                         |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>MRONL</sub> | 5.0             | 3.0 | 9.0                                                       | 15.0 | 3.0                    | 17.0       | ns    |

|                                     | MR to O <sub>n</sub> , LOW            |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>D</sub>     | 5.0             | 6.5 | 18.5                                                      | 27.0 | 6.5                    | 31.0       | ns    |

|                                     | SO to Data Out                        |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>D</sub>     | 5.0             | 6.5 | 18.5                                                      | 29.5 | 6.5                    | 34.5       | ns    |

|                                     | SO to Data Out                        |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>OHF</sub>   | 5.0             | 3.5 | 8.5                                                       | 13.5 | 3.5                    | 15.5       | ns    |

|                                     | SO to < HF                            |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>OF</sub>    | 5.0             | 5.0 | 12.5                                                      | 19.5 | 5.0                    | 22.0       | ns    |

|                                     | SO to Not Full                        |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay, t <sub>OR</sub>    | 5.0             | 2.5 | 7.0                                                       | 11.5 | 2.5                    | 13.5       | ns    |

|                                     | SO to OR                              |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>OE</sub>    | 5.0             | 3.5 | 9.5                                                       | 15.5 | 3.0                    | 17.5       | ns    |

|                                     | SO to Empty                           |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>OD5</sub>   | 5.0             | 7.0 | 19.0                                                      | 30.5 | 6.0                    | 35.5       | ns    |

|                                     | SI to New Data Out                    |                 |     |                                                           |      |                        |            |       |

| t <sub>PHL</sub>                    | Propagation Delay, t <sub>OD5</sub>   | 5.0             | 7.0 | 19.0                                                      | 29.5 | 6.0                    | 34.5       | ns    |

|                                     | SI to New Data Out                    |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Propagation Delay, t <sub>X1</sub>    | 5.0             | 3.5 | 10.0                                                      | 16.0 | 2.5                    | 18.0       | ns    |

|                                     | SI to HF                              |                 |     |                                                           |      |                        |            |       |

| t <sub>PLH</sub>                    | Fall-Through Time, t <sub>FTO</sub>   | 5.0             | 3.5 | 13.5                                                      | 21.0 | 1.5                    | 24.0       | ns    |

|                                     | SI to OR                              |                 |     |                                                           |      | 1                      |            |       |

## AC Electrical Characteristics (Continued)

|                  |                                     | V <sub>CC</sub> | T <sub>A</sub> = +25°C |                 |      | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |       |

|------------------|-------------------------------------|-----------------|------------------------|-----------------|------|-----------------------------------------------|------|-------|

| Symbol           | Parameter                           | (V)             |                        | $C_L = 50 \ pF$ |      | C <sub>L</sub> = 50 pF                        |      | Units |

|                  |                                     | (Note 5)        | Min                    | Тур             | Max  | Min                                           | Max  |       |

| t <sub>W</sub>   | HF Pulse Width, t <sub>X3</sub>     | 5.0             | 14.5                   | 20.5            | 30.5 | 14.5                                          | 36.5 | ns    |

| t <sub>W</sub>   | IR Pulse Width, t <sub>IP</sub>     | 5.0             | 16.5                   | 28.0            | 43.0 | 16.5                                          | 51.5 | ns    |

| t <sub>W</sub>   | HF Pulse Width, t <sub>3F</sub>     | 5.0             | 17.5                   | 30.0            | 46.5 | 17.5                                          | 56.0 | ns    |

| t <sub>PLH</sub> | Fall-Through Times, t <sub>FT</sub> | 5.0             | 6.0                    | 15.0            | 23.5 | 2.5                                           | 28.0 | ns    |

|                  | SO to IR                            |                 |                        |                 |      |                                               |      |       |

| t <sub>PZL</sub> | Output Enable                       | 5.0             | 2.0                    | 6.5             | 11.0 | 1.5                                           | 12.0 | ns    |

|                  | $\overline{OE}$ to $O_n$            |                 |                        |                 |      |                                               |      |       |

| t <sub>PLZ</sub> | Output Disable                      | 5.0             | 1.5                    | 5.0             | 8.5  | 1.5                                           | 9.5  | ns    |

|                  | $\overline{OE}$ to $O_n$            |                 |                        |                 |      |                                               |      |       |

| t <sub>PZH</sub> | Output Enable                       | 5.0             | 2.0                    | 7.0             | 12.0 | 1.5                                           | 13.0 | ns    |

|                  | ŌE to O <sub>n</sub>                |                 |                        |                 |      |                                               |      |       |

| t <sub>PHZ</sub> | Output Disable                      | 5.0             | 1.5                    | 7.0             | 12.0 | 1.5                                           | 13.0 | ns    |

|                  | ŌĒ to O <sub>n</sub>                |                 |                        |                 |      |                                               |      |       |

| f <sub>SI</sub>  | Maximum SI                          | 5.0             | 55                     | 85              |      | 45                                            |      | MHz   |

|                  | Clock Frequency                     |                 |                        |                 |      |                                               |      |       |

| f <sub>SO</sub>  | Maximum SO                          | 5.0             | 42                     | 60              |      | 35                                            |      | MHz   |

|                  | Clock Frequency                     |                 |                        |                 |      |                                               |      |       |

Note 5: Voltage Range 5.0 is 5.0V ± 0.5V

## **AC Operating Requirements**

|                    |                                   | V <sub>CC</sub> | <b>T</b> <sub>A</sub> = | +25°C | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |       |

|--------------------|-----------------------------------|-----------------|-------------------------|-------|-----------------------------------------------|-------|

| Symbol             | Parameter                         | (V)             | C <sub>L</sub> = 50 pF  |       | C <sub>L</sub> = 50 pF                        | Units |

|                    |                                   | (Note 6)        | Тур                     | Gua   | ranteed Minimum                               |       |

| t <sub>W</sub> (H) | SI Pulse Width, t <sub>SIH</sub>  | 5.0             | 3.5                     | 6.5   | 7.5                                           | ns    |

| t <sub>W</sub> (L) | SI Pulse Width, t <sub>SIL</sub>  | 5.0             | 6.0                     | 10.0  | 12.0                                          | ns    |

|                    |                                   |                 |                         |       |                                               |       |

| t <sub>S</sub>     | Setup Time, HIGH or               | 5.0             | 1.0                     | 3.5   | 4.5                                           | ns    |

|                    | LOW, D <sub>n</sub> to SI         |                 |                         |       |                                               |       |

| t <sub>H</sub>     | Hold Time, HIGH or                | 5.0             | 1.5                     | 3.5   | 4.5                                           | ns    |

|                    | LOW, D <sub>n</sub> to SI         |                 |                         |       |                                               |       |

| t <sub>W</sub>     | MR Pulse Width, t <sub>MRW</sub>  | 5.0             | 13.0                    | 20.0  | 24.5                                          | ns    |

| t <sub>rec</sub>   | Recovery Time, t <sub>MRSIH</sub> | 5.0             | 4.5                     | 7.5   | 8.5                                           | ns    |

|                    | MR to SI                          |                 |                         |       |                                               |       |

| t <sub>W</sub> (H) | SO Pulse Width, t <sub>SOH</sub>  | 5.0             | 7.5                     | 6.5   | 8.0                                           | ns    |

| t <sub>W</sub> (L) | SO Pulse Width, t <sub>SOL</sub>  | 5.0             | 9.0                     | 14.0  | 17.0                                          | ns    |

Note 6: Voltage Range 5.0 is  $5.0V \pm 0.5V$

## Capacitance

| C <sub>IN</sub> Input Capacitance     4.5     pF     V <sub>CC</sub> = OPEN       C <sub>PD</sub> Power Dissipation Capacitance     20.0     pF     V <sub>CC</sub> = 5.0V | Symbol          | Parameter                     | Тур  | Units | Conditions      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|------|-------|-----------------|

| $C_{PD}$ Power Dissipation Capacitance 20.0 pF $V_{CC} = 5.0V$                                                                                                             | C <sub>IN</sub> | Input Capacitance             | 4.5  | pF    | $V_{CC} = OPEN$ |

|                                                                                                                                                                            | C <sub>PD</sub> | Power Dissipation Capacitance | 20.0 | pF    | $V_{CC} = 5.0V$ |

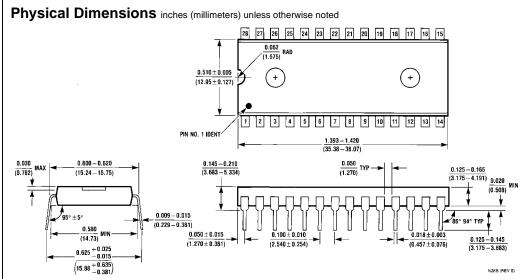

28-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600" Wide Package Number N28B

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.