Microphone Preamp Stage and National 3D Sound

## **Boomer**<sup>®</sup> Audio Power Amplifier Series LM4832 **Digitally Controlled Tone and Volume Circuit with Stereo** Audio Power Amplifier, Microphone Preamp Stage and National 3D Sound

## **General Description**

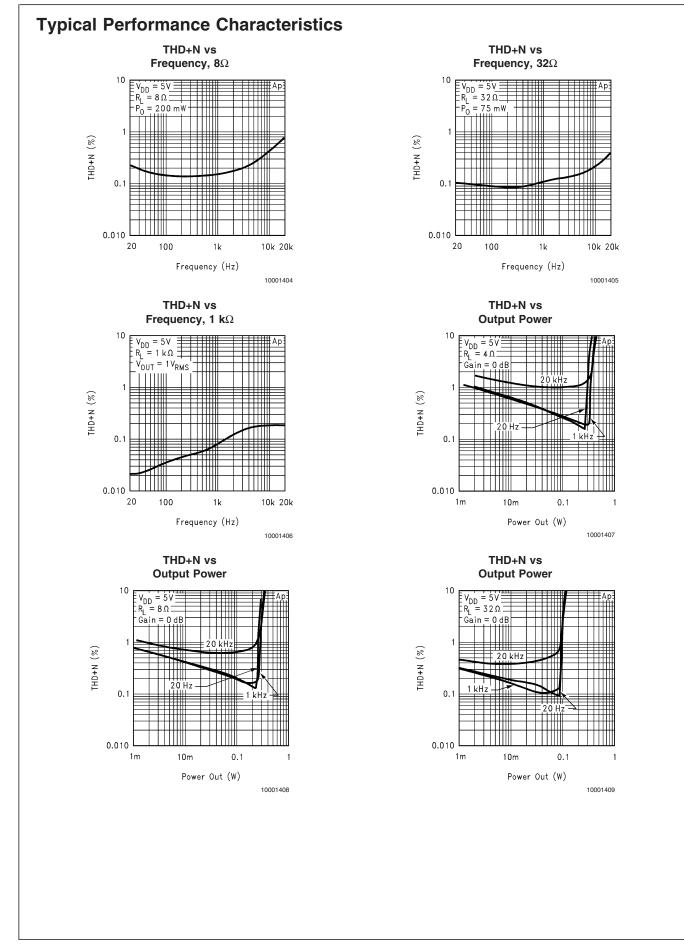

The LM4832 is a monolithic integrated circuit that provides volume and tone (bass and treble) controls as well as a stereo audio power amplifier capable of producing 250 mW (typ) into  $8\Omega$  or 90 mW (typ) into  $32\Omega$  with less than 1.0% THD. In addition, a two input microphone preamp stage, with volume control, capable of driving a 1 k $\Omega$  load is implemented on chip.

The LM4832 also features National's 3D Sound circuitry which can be externally adjusted via a simple RC network. For maximum system flexibility, the LM4832 has an externally controlled, low-power consumption shutdown mode, and an independent mute for power and microphone amplifiers .

Boomer<sup>®</sup> audio integrated circuits were designed specifically to provide high quality audio while requiring few external components. Since the LM4832 incorporates tone and volume controls, a stereo audio power amplifier and a microphone preamp stage, it is optimally suited to multimedia monitors and desktop computer applications.

## **Key Specifications**

Output Power at 10% into 8Ω 350mW (typ) Output Power at 10% into 32Ω 100mW (typ) THD+N at 75mW into 32Ω at 1kHz 0.5% (max) Microphone Input Referred Noise 7µV (typ) Supply Current 13mA (typ) Shutdown Current 4µA (typ)

#### Features

- Independent Left and Right Output Volume Controls

- Treble and Bass Control

- National 3D Sound

- I<sup>2</sup>C Compatible Interface

- Two Microphone Inputs with Selector

- Software Controlled Shutdown Function

## Applications

- Multimedia Monitors

- Portable and Desktop Computers

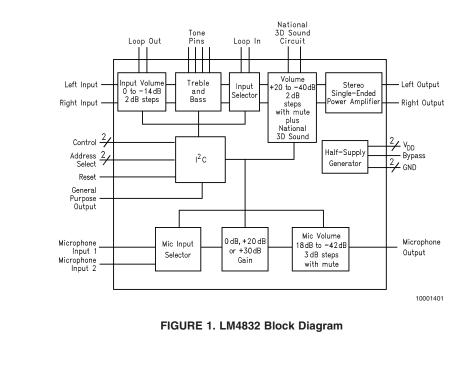

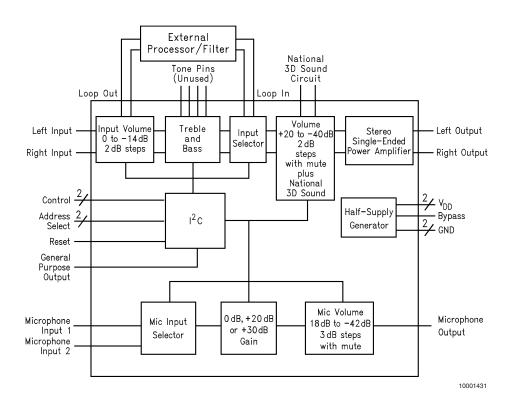

## **Block Diagram**

Boomer® is a registered trademark of National Semiconductor Corporation.

## Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage              | 6.0V                           |

|-----------------------------|--------------------------------|

| Storage Temperature         | –65°C to +150°C                |

| Input Voltage               | –0.3V to V <sub>DD</sub> +0.3V |

| Power Dissipation (Note 3)  | Internally limited             |

| ESD Susceptibility (Note 4) | 2000V                          |

| ESD Susceptibility (Note 5) | 250V                           |

| Junction Temperature        | 150°C                          |

| Soldering Information       |                                |

| Small Outline Package       |                                |

| Vapor Phase (60 sec.)       | 215°C                          |

| Infrared (15 sec.)          | 220°C                          |

See AN-450 "Surface Mounting and their Effects on Product Reliability" for other methods of soldering surface mount devices.

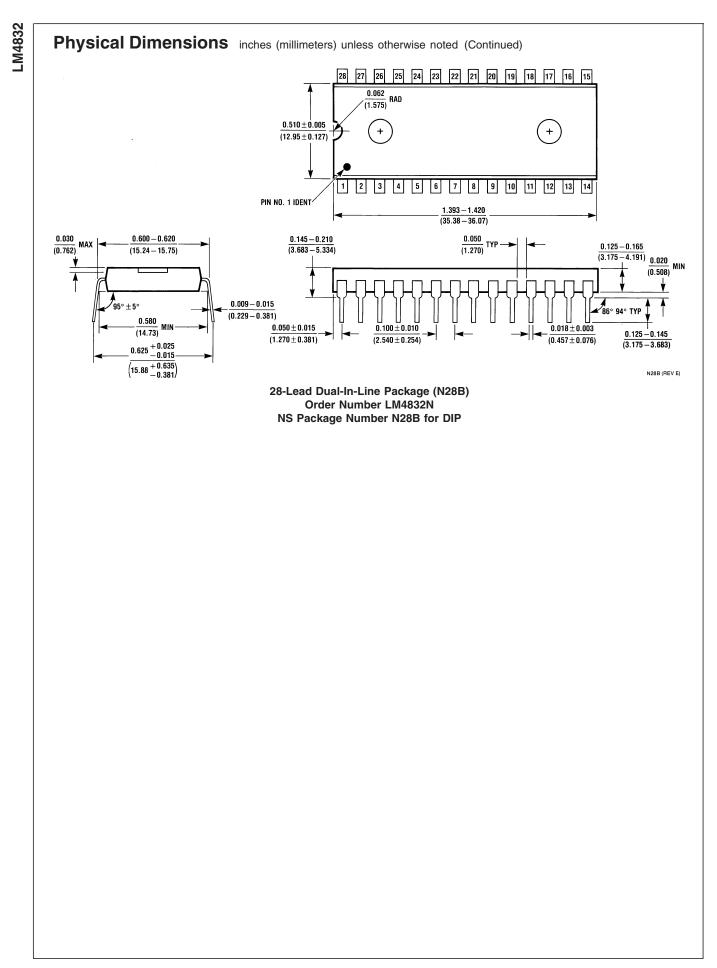

| $\theta_{JC}$ (typ)—N28B    | 21°C/W |

|-----------------------------|--------|

| θ <sub>JA</sub> (typ)—N28B  | 62°C/W |

| θ <sub>JC</sub> (typ)—M28B  | 15°C/W |

| θ <sub>JA</sub> (typ)—M28B  | 69°C/W |

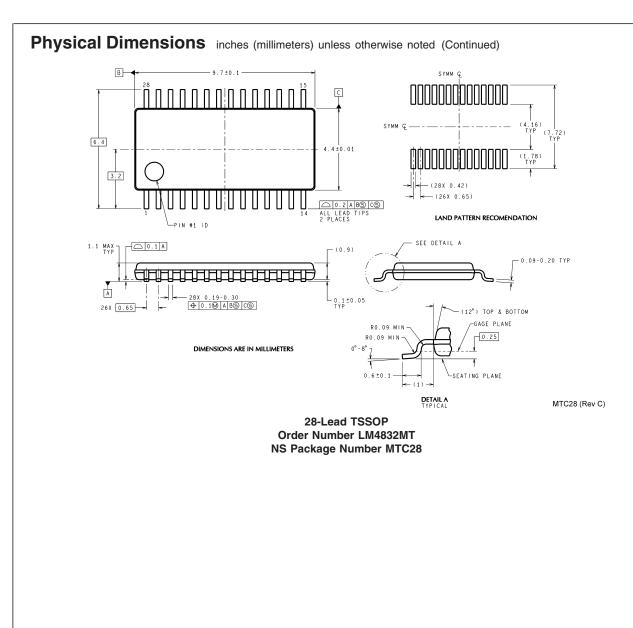

| $\theta_{JC}$ (typ)—MTC28   | 20°C/W |

| θ <sub>JA</sub> (typ)—MTC28 | 80°C/W |

## **Operating Ratings**

|                       |         | ••••••••••••••••••••••••••••••••••••••• |                                          |

|-----------------------|---------|-----------------------------------------|------------------------------------------|

| dering Information    |         | Temperature Depres                      |                                          |

| mall Outline Package  |         | Temperature Range                       |                                          |

| 0                     | 0.15° 0 | $T_{MIN} \le T_A \le T_{MAX}$           | $-40^{\circ}C \le T_{A} \le 85^{\circ}C$ |

| Vapor Phase (60 sec.) | 215°C   |                                         |                                          |

| Infrared (15 sec.)    | 220°C   | Supply Voltage                          | $4.5 \le V_{DD} \le 5.5V$                |

#### Electrical Characteristics for Entire IC (Notes 1, 2)

The following specifications apply for  $V_{\text{DD}}$  = 5V unless otherwise noted. Limits apply for  $T_{\text{A}}$  = 25°C.

|                 |                                   |                                                   | LM4      |          |         |

|-----------------|-----------------------------------|---------------------------------------------------|----------|----------|---------|

| Symbol          | Parameter                         | Conditions                                        | Typical  | Limit    | Units   |

| Symbol          | Falanielei                        | Conditions                                        | (Note 6) | (Note 7) | (Limits |

|                 |                                   |                                                   |          | (Note 8) |         |

| V <sub>DD</sub> | Supply Voltage                    | $V_{IN} = 0V, I_O = 0A$                           |          | 4.5      | V (min  |

|                 |                                   |                                                   |          | 5.5      | V (max  |

| I <sub>DD</sub> | Quiescent Power Supply Current    |                                                   | 13       | 21       | mA (ma  |

| I <sub>SD</sub> | Shutdown Current                  |                                                   | 2.5      | 9        | μA (max |

| INPUT ATTE      | NUATORS                           |                                                   |          |          |         |

| A <sub>R</sub>  | Attenuator Range                  | Attenuation at 0 dB Setting                       |          | 1        | dB (max |

|                 |                                   | Attenuation at -14 dB Setting                     |          | -15      | dB (mir |

| A <sub>S</sub>  | Step Size                         | 0 dB to -14 dB                                    | 2        |          | dB      |

|                 | Gain Step Size Error              |                                                   | 0.1      |          | dB (ma  |

| Ε <sub>T</sub>  | Channel to Channel Tracking Error |                                                   | 0.15     |          | dB (ma  |

| BASS CONT       | ROL                               |                                                   |          |          |         |

| A <sub>R</sub>  | Bass Control Range                | f = 100 Hz, V <sub>IN</sub> = 0.25V               | ±12      | -14      | dB (mir |

|                 |                                   |                                                   |          | 14       | dB (ma  |

| A <sub>S</sub>  | Bass Step Size                    |                                                   | 2        |          | dB      |

| E <sub>SE</sub> | Bass Step Size Error              |                                                   | 0.5      |          | dB (max |

| Ε <sub>T</sub>  | Bass Tracking Error               |                                                   | 0.15     |          | dB (ma  |

| TREBLE CO       | NTROL                             | ·                                                 |          |          |         |

| A <sub>R</sub>  | Treble Control Range              | f <sub>IN</sub> = 10 kHz, V <sub>IN</sub> = 0.25V | ±12      | -13      | dB (mir |

|                 |                                   |                                                   |          | 13       | dB (ma  |

| A <sub>S</sub>  | Treble Step Size                  |                                                   | 2        |          | dB      |

| E <sub>SE</sub> | Treble Step Size Error            |                                                   | 0.1      |          | dB (ma  |

| Ε <sub>T</sub>  | Treble Tracking Error             |                                                   | 0.15     |          | dB (ma  |

| OUTPUT AT       | TENUATORS                         | •                                                 | •        |          |         |

| A <sub>R</sub>  | Attenuator Range                  | Gain at +20 dB Setting                            |          | 21       | dB (max |

|                 |                                   | Attenuation at -40 dB Setting                     |          | -42      | dB (mir |

| A <sub>s</sub>  | Step Size                         | +20 dB to -40 dB                                  | 2        |          | dB      |

|                 | Step Size Error                   |                                                   | 0.1      |          | dB (ma  |

| E <sub>τ</sub>  | Channel to Channel Tracking Error | 1                                                 | 0.1      |          | dB (ma  |

|                 | -                                 | 1                                                 | 1        |          |         |

| V <sub>os</sub> | Output Offset Voltage             | V <sub>IN</sub> = 0V                              | 3        | 50       | mV (ma  |

|                          |                                                          |                                                                                                           | LM4                     |                               |                   |

|--------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------|-------------------|

| Symbol                   | Parameter                                                | Conditions                                                                                                | <b>Typical</b> (Note 6) | Limit<br>(Note 7)<br>(Note 8) | Units<br>(Limits) |

| Po                       | Output Power                                             | THD = 1.0% (max), f = 1 kHz, All controls at 0dB                                                          |                         |                               |                   |

|                          |                                                          | $R_{L} = 8\Omega$                                                                                         | 250                     |                               | mW (min           |

|                          |                                                          | $R_{L} = 32\Omega$                                                                                        | 95                      | 75                            | mW (min)          |

| THD+N                    | Total Harmonic Distortion+Noise                          | All Controls at 0 dB, THD = 10%, f = 1                                                                    |                         |                               |                   |

|                          |                                                          | kHz                                                                                                       |                         |                               |                   |

|                          |                                                          | $R_L = 8\Omega$                                                                                           | 350                     |                               | mW                |

|                          |                                                          | $P_{O} = 200 \text{ mW}, R_{L} = 8\Omega$                                                                 | 0.15                    |                               | %                 |

|                          |                                                          | $P_{O} = 75 \text{ mW}, R_{L} = 32\Omega$                                                                 | 0.11                    |                               | %                 |

|                          |                                                          | $V_{O} = 1$ Vrms, $R_{L} = 10\Omega$                                                                      | 0.08                    |                               | %                 |

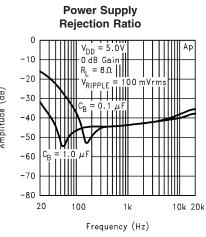

| PSRR                     | Power Supply Rejection Ratio                             | $C_B = 1 \ \mu F$ , f = 100 Hz, $V_{RIPPLE} = 100$<br>mVrms, All Controls at 0 dB Setting                 | 45                      |                               | dB                |

| A <sub>M</sub>           | Mute Attenuation                                         | $f = 1 \text{ kHz}, V_{IN} = 1 \text{ V}$                                                                 | -75                     |                               | dB                |

| X <sub>TALK</sub>        | Cross Talk                                               | $P_{O} = 200 \text{ mW}, R_{L} = 8\Omega,$<br>All controls at 0 dB setting,<br>f = 1 kHz<br>Left to Right | -85                     |                               | dB                |

|                          |                                                          | Right to Left                                                                                             | -72                     |                               | dB                |

| MICROPHON                | E PREAMP AND VOLUME CONTROL                              |                                                                                                           |                         |                               |                   |

| A <sub>V</sub>           | Preamp Gain                                              | 0 dB Gain                                                                                                 | 0                       | –1, 1                         | dB                |

|                          |                                                          | +20 dB Gain                                                                                               | 20                      | 19, 21                        | dB                |

|                          |                                                          | +30 dB Gain                                                                                               | 30                      | 29, 31                        | dB                |

| A <sub>R</sub>           | Attenuator Range                                         | Gain at +18 dB Setting                                                                                    |                         | 20                            | dB (max           |

|                          |                                                          | Attenuation at -42 dB Setting                                                                             |                         | -43                           | dB (min           |

| A <sub>S</sub>           | Step Size                                                | 0 dB to -42 dB                                                                                            | 3                       |                               | dB                |

|                          | Step Size Error                                          |                                                                                                           | 0.4                     |                               | dB (max           |

| V <sub>SWING</sub>       | Output Voltage Swing                                     | f = 1 kHz, THD < 1.0%, $R_L$ = 1 k $\Omega$                                                               | 1.7                     |                               | V <sub>rms</sub>  |

| E <sub>NO</sub>          | Input Referred Noise                                     | A-Weighted, Attenuator at 0 dB                                                                            | 7                       |                               | μV (min           |

| PSRR                     | Power Supply Rejection Ratio                             | f = 100 Hz, $V_{RIPPLE}$ = 100 mVrms,<br>C <sub>B</sub> = 1 µF                                            | 35                      |                               | dB                |

| A <sub>M</sub>           | Mute Attenuation                                         |                                                                                                           | -90                     |                               | dB                |

| X <sub>talk</sub>        | Cross Talk                                               | Power Amp $P_O = 200 \text{ mW}, \text{ f} = 1 \text{ kHz}$                                               | -90                     |                               | dB                |

| THD+N                    | Total Harmonic Distortion Plus Noise                     | All controls at 0 dB, f = 1 kHz, $V_0 = 1V$                                                               |                         |                               |                   |

|                          |                                                          | 0 dB Setting                                                                                              | 0.03                    |                               | %                 |

|                          |                                                          | +20 dB Gain                                                                                               | 0.03                    |                               | %                 |

|                          |                                                          | +30 dB Gain                                                                                               | 0.04                    |                               | %                 |

| I <sup>2</sup> C BUS TIM | -                                                        | 1                                                                                                         |                         |                               |                   |

| f <sub>MAX</sub>         | Maximum Bus Frequency                                    |                                                                                                           |                         | 400                           | kHz               |

| T <sub>START:HOLD</sub>  | Start Signal: Hold Time before                           |                                                                                                           |                         | 0.6                           | μs                |

|                          | Clock/Data Transitions                                   |                                                                                                           |                         |                               |                   |

| T <sub>D;SETUP</sub>     | Data Setup Time                                          |                                                                                                           |                         | 0.1                           | μs                |

| Т <sub>с;нідн</sub>      | Minimum High Clock Duration                              |                                                                                                           |                         | 0.6                           | μs                |

| T <sub>C;LOW</sub>       | Minimum Low Clock Duration                               |                                                                                                           |                         | 1.3                           | μs                |

| T <sub>STOP;SETUP</sub>  | Stop Signal: Setup Time before<br>Clock/Data Transitions |                                                                                                           |                         | 0.6                           | μs                |

|                          | UT AND OUTPUT                                            |                                                                                                           |                         |                               |                   |

3

## Electrical Characteristics for Entire IC (Notes 1, 2) (Continued)

The following specifications apply for  $V_{DD}$  = 5V unless otherwise noted. Limits apply for  $T_A$  = 25°C.

|                 |                                 |            | LM4                 |                               |                   |

|-----------------|---------------------------------|------------|---------------------|-------------------------------|-------------------|

| Symbol          | Parameter                       | Conditions | Typical<br>(Note 6) | Limit<br>(Note 7)<br>(Note 8) | Units<br>(Limits) |

| V <sub>IH</sub> | Input High Voltage              |            |                     | 3                             | V (min)           |

| I <sub>IN</sub> | Input Current                   |            | 0.15                |                               | μA                |

| Vo              | Output Voltage—SDA Acknowledge  |            |                     | 0.4                           | V (max)           |

| V <sub>OL</sub> | External Power Amp Disable Low  |            |                     | 0.4                           | V (max)           |

| V <sub>он</sub> | External Power Amp Disable High |            |                     | 4                             | V (min)           |

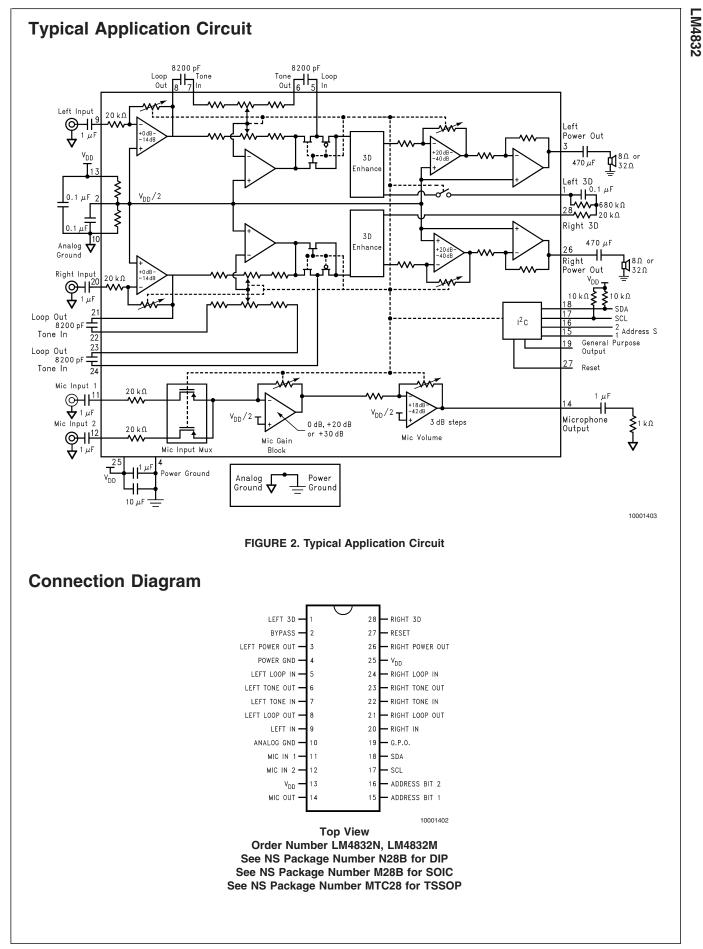

Note 1: All voltages are measured with respect to the ground pins, unless otherwise specified. All specifications are tested using the typical applications shown in Figure 1.

**Note 2:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

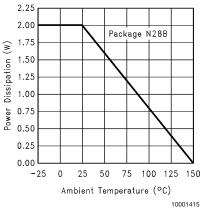

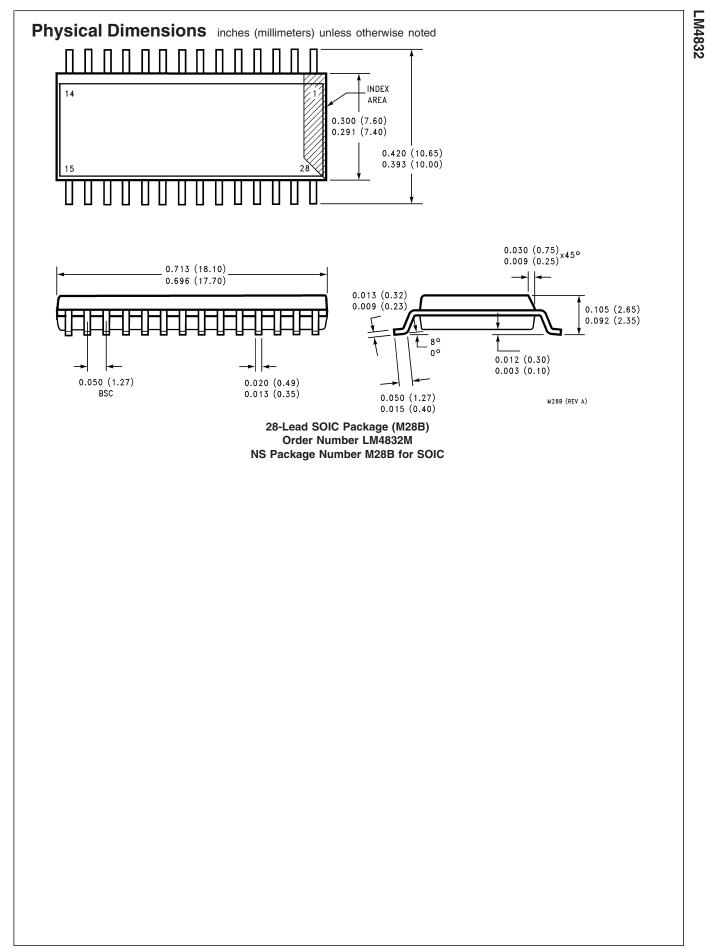

**Note 3:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$ . For the LM4832,  $T_{JMAX} = 150$ °C, and the typical junction-to-ambient thermal resistance, when board mounted, is 69°C/W assuming the M28B package.

Note 4: Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

Note 5: Machine Model, 220pF-240pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

# **Pin Descriptions**

| Pin Name                          | Description                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

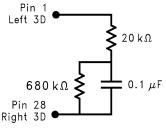

| LEFT 3D (1)                       | An external RC network is connected across these pins. This function                                                                                                                                                                                                                                                                          |  |  |  |  |

| RIGHT 3D (28)                     | provides left-right channel cross coupling and cancellation to create an                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                   | enhanced stereo channel separation effect.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| BYPASS (2)                        | A 0.1 $\mu$ F capacitor is placed between this pin and ground to provide an AC ground for the internal half-supply voltage reference. The capacitor at this pin affects "click-pop" and THD performance. Turn-on and turn-off times are also determined by this capacitor. Refer to the Application Information section for more information. |  |  |  |  |

| POWER AMP OUT LEFT (3) RIGHT (26) | These outputs are intended to drive $8\Omega$ speakers or $32\Omega$ headphones.<br>These outputs should be AC-coupled to the loads. Refer to the                                                                                                                                                                                             |  |  |  |  |

|                                   | Application Information section for more information.                                                                                                                                                                                                                                                                                         |  |  |  |  |

| POWER GND (4)                     | This pin provides the high current return for the power output stage MOSFETs and digital circuitry.                                                                                                                                                                                                                                           |  |  |  |  |

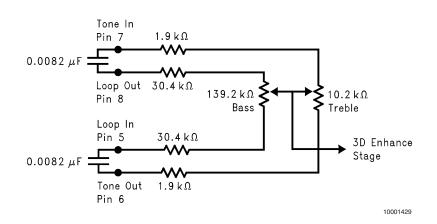

| LOOP OUT (8, 21) LOOP IN (5, 24)  | These pins allow an external signal processor access to the stereo signal Please see the Application Information section for more information.                                                                                                                                                                                                |  |  |  |  |

| TONE OUT                          | These pins are connected to the tone control op amp outputs and drive                                                                                                                                                                                                                                                                         |  |  |  |  |

| (6, 23)                           | the power amplifier inputs. Refer to the Application Information section for more information.                                                                                                                                                                                                                                                |  |  |  |  |

| TONE IN                           | These pins are connected to the inputs of the tone control op amps. A                                                                                                                                                                                                                                                                         |  |  |  |  |

| (7, 22)                           | capacitor between the Tone In and Tone Out pins sets the frequency response of the tone functions. Please refer to the Application Information section for more information.                                                                                                                                                                  |  |  |  |  |

| INPUTS                            | These pins are the stereo inputs for the LM4832. These pins should be                                                                                                                                                                                                                                                                         |  |  |  |  |

| (9, 20)                           | AC-coupled to the input signals.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ANALOG GND (10)                   | This pin is the AC analog ground for the line level AC signal inputs.                                                                                                                                                                                                                                                                         |  |  |  |  |

| MIC INPUTS (11, 12)               | These pins are the two independent selectable microphone inputs. These pins should be AC-coupled.                                                                                                                                                                                                                                             |  |  |  |  |

| MIC OUT (14)                      | This pin is the output for the microphone amplifier and should be AC-coupled to the load.                                                                                                                                                                                                                                                     |  |  |  |  |

| V <sub>DD</sub><br>(13, 25)       | These pins are for the 5V supply. These pins should be separately bypassed by 0.1 $\mu$ F, or higher, film capacitors. The 5V supply should be bypassed by a 10 $\mu$ F, or higher, tantalum or aluminum electrolytic capacitor.                                                                                                              |  |  |  |  |

| ADDRESS BITS (15, 16)             | These pins are used to determine the I <sup>2</sup> C address for the LM4832.                                                                                                                                                                                                                                                                 |  |  |  |  |

| CLOCK (17)                        | This pin is the input for the I <sup>2</sup> C clock signal.                                                                                                                                                                                                                                                                                  |  |  |  |  |

| DATA (18)                         | This pin is the input for the I <sup>2</sup> C data signal.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| GENERAL PURPOSE OUTPUT (19)       | This pin provides a general purpose TTL/CMOS output. Please refer to the Application Information section for more information.                                                                                                                                                                                                                |  |  |  |  |

| RESET (27)                        | This pin is a TTL/CMOS input which is used to reset the chip logic and states.                                                                                                                                                                                                                                                                |  |  |  |  |

#### Typical Performance Characteristics (Continued) **Power Amplifier** Crosstalk 0 1m $V_{DD} = 5V$ Ap -10 =1μF CR Output Noise Voltage ( $\mu$ V) = 200 m 🕅 -20 ്പ = 0 dB| Gain -30 100*µ* -40 Level (dB) -50 -60 10*µ* Right to Lef -70 -80 -90 -100 1μ 20 100 10k 20k 20 1k Frequency (Hz) 10001410 **Power Amplifier Attenuation** vs Frequency 30 0 20 dB 20 -10 10 dB 10 0 dB -20 0 Output Level (dB) 10 dB Amplitude (dB) -10 -30 20 dB -20 30 dB -40 -30 ΠU 40 dB -50 -40 $= 5V, R_{L}$ = 8 Ω+ -50 -60 מס' = 200 mW@ 20 dB dB Steps| \_\_\_\_\_ Amplif -60 10 dB Steps Mute -70 -70 -80 -80 20 10k 20k 20 100 1k Frequency (Hz) 10001412 **Power Dissipation** vs Output Power 700 2.25 2.00 600 1.75 Power Dissipation (mW) ٠ Power Dissipation (W) 500 1.50 400 1.25 \*\*\* 1.00 300 0.75 200 0.50 100 0.25 0 0.00 300 400 0 100 200 500 600 Power Output (mW) 10001414

Noise Floor  $\begin{array}{c}

1m \\

R_L = 8.\Omega \\

Gain = 0 \ dB \\

A - Weighted Filter \\

D0 \mu \\

\hline

\end{array}$

100

Frequency (Hz)

1k

**Power Amplifier**

10001413

10k 20k

10001411

Power Derating Curve

#### Typical Performance Characteristics (Continued) **Bass Response Treble Response** vs Frequency 20 20 $\dot{V}_{DD} = 5V$ $R_L = 8\Omega$ = 5 V Ap /DD $R_L = 8 \Omega$ 15 15 CTONE = 8200 pl CTONE 10 10 Output Level (dB) Output Level (dB) 5 5 0 0 -5 -5 -10 -10 -15 -15 -20 -20 20 100 10k 20k 20 1k Frequency (Hz) 10001422 **Bass and Treble Response Supply Current** vs Frequency vs Temperature 20 16 $V_{DD} = 5V$ $R_L = 8\Omega$ = 5 V Aι 15 14 C<sub>TONE</sub> = 8200 F 10 12 Supply Current (mA) Output Level (dB) 5 10 0 8 -5 6 -10 4 -15 2 0 -20 -40 -20 20 10k 20k 100 1k Frequency (Hz) 10001424

vs Frequency

= 8200 pF

100

0 20 40 60 80 100

Temperature (°C)

1k

Frequency (Hz)

Αp

10k 20k

10001423

10001425

## **Truth Tables**

#### SOFTWARE SPECIFICATION

| Chip Address |   |   |   |   |       |       |     |  |  |  |

|--------------|---|---|---|---|-------|-------|-----|--|--|--|

| MSB          |   |   |   |   |       |       | LSB |  |  |  |

| 1            | 0 | 0 | 0 | 0 | *E.C. | *E.C. | 0   |  |  |  |

#### \*E.C. = Externally Configuarable

|     | Data Bytes (Brief Description) |   |                  |                  |                  |                  |                  |                        |  |  |  |  |  |

|-----|--------------------------------|---|------------------|------------------|------------------|------------------|------------------|------------------------|--|--|--|--|--|

| MSB |                                |   |                  |                  |                  |                  | LSB              | Function               |  |  |  |  |  |

| 0   | 0                              | 0 | Х                | Х                | D2               | D1               | D0               | Input Volume Control   |  |  |  |  |  |

| 0   | 0                              | 1 | Х                | D3               | D2               | D1               | D0               | Bass Control           |  |  |  |  |  |

| 0   | 1                              | 0 | Х                | D3               | D2               | D1               | D0               | Treble Control         |  |  |  |  |  |

| 0   | 1                              | 1 | D4               | D3               | D2               | D1               | D0               | Right Output Vol./Mute |  |  |  |  |  |

| 1   | 0                              | 0 | D4               | D3               | D2               | D1               | D0               | Left Output Vol./Mute  |  |  |  |  |  |

| 1   | 0                              | 1 | Х                | $D_11$           | D <sub>1</sub> 0 | D <sub>o</sub> 1 | D <sub>o</sub> 0 | Mic Input and Gain     |  |  |  |  |  |

| 1   | 1                              | 0 | D4               | D3               | D2               | D1               | D0               | Microphone Volume      |  |  |  |  |  |

| 1   | 1                              | 1 | D <sub>4</sub> 0 | D <sub>3</sub> 0 | D <sub>2</sub> 0 | D <sub>1</sub> 0 | D <sub>0</sub> 0 | General Control        |  |  |  |  |  |

| MSB                          |            |   |                     |   |   |   | LSB | Attenuation (dB)     |

|------------------------------|------------|---|---------------------|---|---|---|-----|----------------------|

| 0                            | 0          | 0 | Х                   | Х | 0 | 0 | 0   | 0                    |

| 0                            | 0          | 0 | Х                   | Х | 0 | 0 | 1   | -2                   |

| 0                            | 0          | 0 | Х                   | Х | 0 | 1 | 0   | -4                   |

| 0                            | 0          | 0 | Х                   | Х | 0 | 1 | 1   | -6                   |

| 0                            | 0          | 0 | Х                   | Х | 1 | 0 | 0   | -8                   |

| 0                            | 0          | 0 | Х                   | Х | 1 | 0 | 1   | -10                  |

| 0                            | 0          | 0 | Х                   | Х | 1 | 1 | 0   | -12                  |

| 0                            | 0          | 0 | Х                   | Х | 1 | 1 | 1   | -14                  |

| Input Volume Control X X 0 0 |            |   |                     |   |   |   | 0   | Input Volume Control |

| Powe                         | r Up State |   | at 0 dB Attenuation |   |   |   |     |                      |

Input Volume Control

|        |          |   |   |   | Bass Col |   |     |                      |

|--------|----------|---|---|---|----------|---|-----|----------------------|

| MSB    |          |   |   |   |          |   | LSB | Level (dB)           |

| 0      | 0        | 1 | Х | 0 | 0        | 0 | 0   | -12                  |

| 0      | 0        | 1 | Х | 0 | 0        | 0 | 1   | -10                  |

| 0      | 0        | 1 | Х | 0 | 0        | 1 | 0   | -8                   |

| 0      | 0        | 1 | Х | 0 | 0        | 1 | 1   | -6                   |

| 0      | 0        | 1 | Х | 0 | 1        | 0 | 0   | -4                   |

| 0      | 0        | 1 | Х | 0 | 1        | 0 | 1   | -2                   |

| 0      | 0        | 1 | Х | 0 | 1        | 1 | 0   | 0                    |

| 0      | 0        | 1 | Х | 0 | 1        | 1 | 1   | 2                    |

| 0      | 0        | 1 | Х | 1 | 0        | 0 | 0   | 4                    |

| 0      | 0        | 1 | Х | 1 | 0        | 0 | 1   | 6                    |

| 0      | 0        | 1 | Х | 1 | 0        | 1 | 0   | 8                    |

| 0      | 0        | 1 | Х | 1 | 0        | 1 | 1   | 10                   |

| 0      | 0        | 1 | Х | 1 | 1        | 0 | 0   | 12                   |

| Bass ( | Control  |   | Х | 0 | 1        | 1 | 0   | Bass Control is Flat |

| Power  | Up State | е |   |   |          |   |     |                      |

Bass Control

## Truth Tables (Continued)

**Treble Control**

| MSB   |            |   |   |   |   |   | LSB | Level (dB)             |

|-------|------------|---|---|---|---|---|-----|------------------------|

| 0     | 1          | 0 | Х | 0 | 0 | 0 | 0   | -12                    |

| 0     | 1          | 0 | Х | 0 | 0 | 0 | 1   | -10                    |

| 0     | 1          | 0 | Х | 0 | 0 | 1 | 0   | -8                     |

| 0     | 1          | 0 | Х | 0 | 0 | 1 | 1   | -6                     |

| 0     | 1          | 0 | Х | 0 | 1 | 0 | 0   | -4                     |

| 0     | 1          | 0 | Х | 0 | 1 | 0 | 1   | -2                     |

| 0     | 1          | 0 | Х | 0 | 1 | 1 | 0   | 0                      |

| 0     | 1          | 0 | Х | 0 | 1 | 1 | 1   | 2                      |

| 0     | 1          | 0 | Х | 1 | 0 | 0 | 0   | 4                      |

| 0     | 1          | 0 | Х | 1 | 0 | 0 | 1   | 6                      |

| 0     | 1          | 0 | Х | 1 | 0 | 1 | 0   | 8                      |

| 0     | 1          | 0 | Х | 1 | 0 | 1 | 1   | 10                     |

| 0     | 1          | 0 | Х | 1 | 1 | 0 | 0   | 12                     |

| Trebl | e Control  |   | Х | 0 | 1 | 1 | 0   | Treble Control is Flat |

| Powe  | er Up Stat | е |   |   |   |   |     |                        |

#### Left Volume Control

| MSB    |           |        |   |   |   |   | LSB | Function              |

|--------|-----------|--------|---|---|---|---|-----|-----------------------|

| 1      | 0         | 0      | 0 | 0 | 0 | 0 | 0   | 20                    |

| 1      | 0         | 0      | 0 | 0 | 0 | 0 | 1   | 18                    |

| 1      | 0         | 0      |   |   |   |   |     |                       |

| 1      | 0         | 0      | 1 | 1 | 1 | 0 | 1   | -38                   |

| 1      | 0         | 0      | 1 | 1 | 1 | 1 | 0   | -40                   |

| 1      | 0         | 0      | 1 | 1 | 1 | 1 | 1   | Left Channel Mute     |

| Left V | olume Co  | ontrol | 1 | 1 | 1 | 1 | 1   | Left Channel is Muted |

| Powe   | r Up Stat | е      |   |   |   |   |     |                       |

#### **General Control**

| MSB  |            |    |   |   |   |   | LSB | Function              |

|------|------------|----|---|---|---|---|-----|-----------------------|

| 1    | 1          | 1  |   |   |   |   | 0   | Chip On               |

| 1    | 1          | 1  |   |   |   |   | 1   | Chip Shutdown         |

| 1    | 1          | 1  |   |   |   | 0 |     | G.P.O. Output Low     |

| 1    | 1          | 1  |   |   |   | 1 |     | G.P.O. Output High    |

| 1    | 1          | 1  |   |   | 0 |   |     | Stereo Enhance Off    |

| 1    | 1          | 1  |   |   | 1 |   |     | Stereo Enhance On     |

| 1    | 1          | 1  |   | 0 |   |   |     | Stereo Operation      |

| 1    | 1          | 1  |   | 1 |   |   |     | Mono Force On         |

| 1    | 1          | 1  | 0 |   |   |   |     | External Loop Disable |

| 1    | 1          | 1  | 1 |   |   |   |     | External Loop Enable  |

| Gene | ral Contro | ol | 0 | 0 | 0 | 0 | 0   |                       |

| Powe | r Up Stat  | е  |   |   |   |   |     |                       |

## Truth Tables (Continued)

|     |                     |   |   | Righ | t Volume | Control |     |                        |

|-----|---------------------|---|---|------|----------|---------|-----|------------------------|

| MSB |                     |   |   |      |          |         | LSB | Level (dB)             |

| 0   | 1                   | 1 | 0 | 0    | 0        | 0       | 0   | 20                     |

| 0   | 1                   | 1 | 0 | 0    | 0        | 0       | 1   | 18                     |

| 0   | 1                   | 1 |   |      |          |         |     |                        |

| 0   | 1                   | 1 | 1 | 1    | 1        | 0       | 0   | -38                    |

| 0   | 1                   | 1 | 1 | 1    | 1        | 1       | 0   | -40                    |

| 0   | 1                   | 1 | 1 | 1    | 1        | 1       | 1   | Right Channel Mute     |

| -   | Volume<br>r Up Stat |   | 1 | 1    | 1        | 1       | 1   | Right Channel Is Muted |

#### Microphone Input Selection and Gain

| MSB    |          |         |   |   |   |   | LSB | Function           |

|--------|----------|---------|---|---|---|---|-----|--------------------|

| 1      | 0        | 1       | Х |   |   | 0 | 0   | Mic Input 1        |

| 1      | 0        | 1       | Х |   |   | 0 | 1   | Mic Input 2        |

| 1      | 0        | 1       | Х |   |   | 1 | Х   | Mic Input 1 and 2  |

| 1      | 0        | 1       | Х | 0 | 0 |   |     | Mic Gain (+0 dB)   |

| 1      | 0        | 1       | Х | 0 | 1 |   |     | Mic Gain (+20 dB)  |

| 1      | 0        | 1       | Х | 1 | 0 |   |     | Mic Gain (+30 dB)  |

| Mic In | put Sel. | and     | Х | 1 | 0 | 0 | 0   | Mic 1 is selected  |

| Gain I | Power Up | o State |   |   |   |   |     | with a +30 dB gain |

#### **Microphone Volume Control**

| MSB   |            |        |   |   |   |   | LSB | Function         |

|-------|------------|--------|---|---|---|---|-----|------------------|

| 1     | 1          | 0      | 0 | 0 | 0 | 0 | 0   | 18               |

| 1     | 1          | 0      | 0 | 0 | 0 | 0 | 1   | 15               |

| 1     | 1          | 0      |   |   |   |   |     |                  |

| 1     | 1          | 0      | 1 | 0 | 1 | 0 | 0   | -42              |

| 1     | 1          | 0      | 1 | 0 | 1 | 0 | 1   | Microphone Muted |

| Mic V | olume Co   | ontrol | 1 | 0 | 1 | 0 | 1   | Microphone Muted |

| Powe  | er Up Stat | е      |   |   |   |   |     |                  |

## **Application Information**

#### GROUNDING

In order to achieve the best possible performance, certain grounding techniques should be followed. All input reference grounds should be tied with their respective source grounds and brought back to the power supply ground separately from the output load ground returns. These input grounds should also be tied in with the half-supply bypass ground. Bringing the ground returns for the output loads back to the supply separately will keep large signal currents from interfering with the stable AC input ground references.

#### LAYOUT

As stated in the Grounding section, placement of ground return lines is critical for maintaining the highest level of system performance. It is not only important to route the correct ground return lines together, but also important to be aware of where those ground return lines are routed in conjunction with each other. The output load ground returns should be physically located as far as reasonably possible from low signal level lines and their ground return lines. Critical signal lines are those relating to the microphone amplifier section, since these lines generally work at very low signal levels.

#### SUPPLY BYPASSING

As with all op amps and power op amps, the LM4832 requires the supplies to be bypassed to avoid oscillation. To avoid high frequency instabilities, a 0.1  $\mu F$  metallized-film or ceramic capacitor should be used to bypass the supplies as close to the chip as possible. For low frequency considerations, a 10  $\mu F$  or greater tantalum or electrolytic capacitor should be paralleled with the high frequency bypass capacitor.

If power supply bypass capacitors are not sufficiently large, the current in the power supply leads, which is a rectified version of the output current, may be fed back into internal circuitry. This internal feedback signal can cause high frequency distortion and oscillation.

If power supply lines to the chip are long, larger bypass capacitors could be required. Long power supply leads have inductance and resistance associated with them, that could prevent peak low frequency current demands from being met. The extra bypass capacitance will reduce the peak current requirements from the power supply lines.

#### **POWER-UP STATUS**

On power-up or after a hard reset, the LM4832 registers will be initialized with the default values listed in the truth tables. By default, the LM4832 power and microphone outputs are muted, the tone controls are all flat, National 3D Enhance is off, the chip is in stereo mode, and the microphone input 1 is selected with +30 dB of gain.

#### CLICK AND POP CIRCUITRY

The LM4832 contains circuitry to minimize turn-on transients or "click and pops". In this case, turn-on refers to either power supply turn-on or the device coming out of shutdown mode. When the deviceis turning on, the amplifiers are internally configured as unity gain buffers. An internal current source charges the bypass capacitor on the bypass pin. Both the inputs and outputs ideally track the voltage at the bypass pin. The device will remain in buffer mode until the bypass pin has reached its half supply voltage, 1/2  $\rm V_{DD}.$  As soon as the bypass node is stable, the device will become fully operational.

Although the bypass pin current source cannot be modified, the size of the bypass capacitor,  $C_B$ , can be changed to alter the device turn-on time and the amount of "click and pop". By increasing  $C_B$ , the amount of turn-on pop can be reduced. However, the trade-off for using a larger bypass capacitor is an increase in the turn-on time for the device. Reducing  $C_B$  will decrease turn-on time and increase "click and pop". If  $C_B$  is too small, the LM4832 can develop a low-frequency oscillation ("motorboat") when used at high gains.

There is a linear relationship between the size of  $C_B$  and the turn-on time. Some typical turn-on times for different values of  $C_B$  are:

| Cb      | T <sub>ON</sub> |

|---------|-----------------|

| 0.01 µF | 20 ms           |

| 0.1 µF  | 200 ms          |

| 0.22 μF | 420 ms          |

In order to eliminate "click and pop", all capacitors must be discharged before turn-on. Rapid on/off switching of the device or shutdown function may cause the "click and pop" circuitry to not operate fully, resulting in increased "click and pop" noise. The output coupling cap, C<sub>O</sub>, is of particular concern. This capacitor discharges through an internal 20 k $\Omega$  resistor. Depending on the size of C<sub>O</sub>, the time constant can be quite large. To reduce transients, an external 1 k $\Omega$ -5 k $\Omega$  resistor can be placed in parallel with the internal 20 k $\Omega$  resistor. The tradeoff for using this resistor is an increase in quiescent current.

#### COUPLING CAPACITORS

Because the LM4832 is a single supply circuit, all audio signals must be capacitor coupled to the chip to remove the 2.5  $V_{DC}$  bias. All audio inputs have 20 k $\Omega$  input impedances, so the AC-coupling capacitor will create a high-pass filter with

$$f_{-3dB} = 1/(2\pi^{*}20 \text{ k}\Omega^{*}C_{IN})$$

The amplifier outputs also need to be AC-coupled to the loads. The high-pass filter is comprised of the output load and the coupling capacitor, where the filter cutoff is at

$$f_{-3dB} = 1/(2\pi^*R_{LOAD}^*C_{OUT}).$$

#### POWER AMPLIFIER

The power amplifiers in the LM4832 are designed to drive  $8\Omega$  or  $32\Omega$  loads at 200 mW (continuous) and 75 mW (continuous), respectively, with 1% THD+N. As shown in the Typical Performance Characteristics, the power amplifiers typically drive  $4\Omega$  loads at 350 mW, but with a slight increase in high-frequency THD. As discussed above, these outputs should be AC-coupled to the output load.

#### **MICROPHONE AMPLIFIER**

The microphone preamplifier is intended to amplify low-level signals for signal conditioning. The microphone inputs can be directly connected to microphone networks. The microphone amplifier has enough output capability to drive a 1 k $\Omega$  load. All microphone inputs and outputs must be AC-coupled.

#### I<sup>2</sup>C INTERFACE

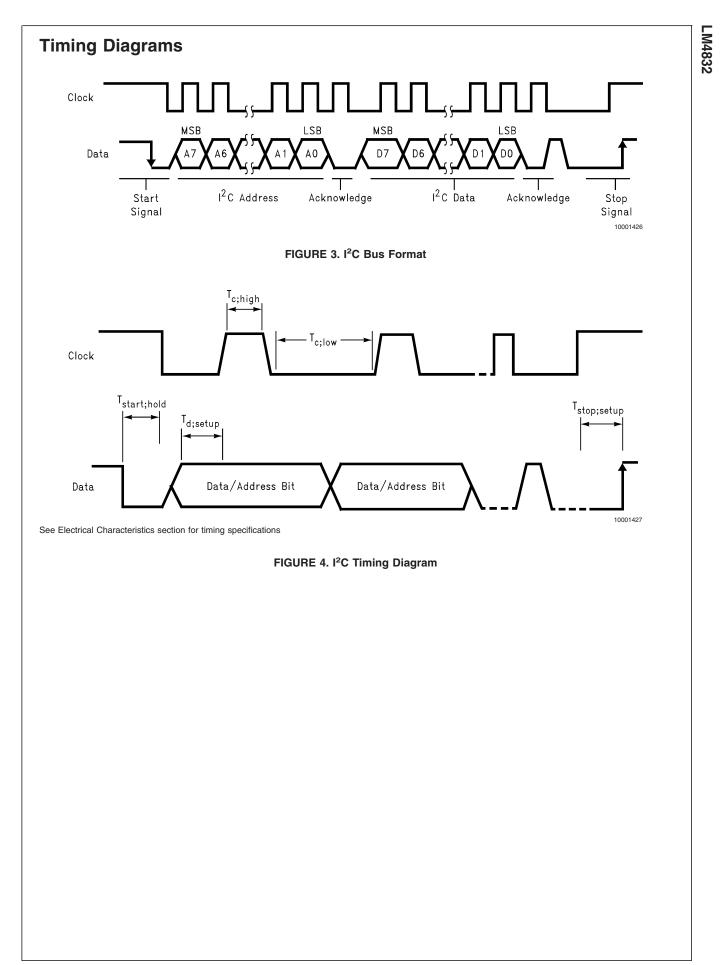

The LM4832 uses a serial bus, which conforms to the I<sup>2</sup>C protocol, to control the chip's functions with two wires: clock and data. The clock line is uni-directional. The data line is bi-directional(open-collector) with a pullup resistor (typically 10 k $\Omega$ ). The maximum clock frequency specified by the I<sup>2</sup>C standard is 400 kHz. In this discussion, the master is the controlling microcontroller and the slave is the LM4832.

The I<sup>2</sup>C address for the LM4832 is determined using the Address Bit 1 and Address Bit 2 TTL/CMOS inputs on the chip. The LM4832's four possible I<sup>2</sup>C chip addresses are of the form  $10000X_2X_10$  (binary), where the  $X_2$  and  $X_1$ bits are determined by the voltage levels at the Address Bit 2 and Address Bit 1 pins, respectively. If the I<sup>2</sup>C interface is used to address a number of chips in a system and the LM4832's chip address can be changed to avoid address conflicts.

The timing diagram for the  $l^2C$  is shown in *Figure 2*. The data is latched in on the stable high level of the clock and the data line should be held high when not in use. The timing diagram is broken up into six major sections:

The "start" signal is generated by lowering the data signal while the clock signal is high. The start signal will alert all devices attached to the  $I^2C$  bus to check the incoming address against their own chip address.

The 8-bit chip address is sent next, most significant bit first. Each address bit must be stable while the clock level is high.

After the last bit of the address is sent, the master checks for the LM4832's acknowledge. The master releases the data line high (through a pullup resistor). Then the master sends a clock pulse. If the LM4832 has received the address correctly, then it holds the data line low during the clock pulse. If the data line is not low, then the master should send a "stop" signal (discussed later) and abort the transfer.

The 8 bits of data are sent next, most significant bit first. Each data bit should be valid while the clock level is stable high.

After the data byte is sent, the master must generate another acknowledge to see if the LM4832 received the data.

If the master has more data bytes to send to the LM4832, then the master can repeat the previous two steps until all data bytes have been sent.

The "stop" signal ends the transfer. To signal "stop", the data signal goes high while the clock signal is high.

#### **3D AUDIO ENHANCEMENT**

The LM4832 has a 3D audio enhancement effect that helps improve the apparent stereo channel separation when, because of cabinet or equipment limitations, the left and right speakers are closer to each other than optimal.

An external RC network, shown in *Figure 3*, is required to enable the effect. The amount of the effect is set by the 20

$k\Omega$  resistor. A 0.1  $\mu F$  capacitor is used to reduce the effect at frequencies below 80 Hz. Decreasing the resistor size will make the 3D effect more pronounced and decreasing the capacitor size will raise the cutoff frequency for the effect.

The 680 k $\Omega$  resistor across the 0.1  $\mu\text{F}$  capacitor reduces switching noise by discharging the capacitor when the effect is not in use.

FIGURE 5. 3D Effect Components

#### TONE CONTROL RESPONSE

Bass and treble tone controls are included in the LM4832. The tone controls use two external capacitors for each stereo channel. Each has a corner frequency determined by the value of C2 and C3 (see *Figure 4*) and internal resistors in the feedback loop of the internal tone amplifier.

Typically, C2 = C3 and for 100 Hz and 10 kHz corner frequencies, C2 = C3 =  $0.0082 \,\mu$ F. Altering the ratio between C2 and C3, changes the midrange gain. For example, if C2 = 2(C3), then the frequency response will be flat at 20 Hz and 20 kHz, but will have a 6 dB peak at 1 kHz.

With C = C2 = C3, the treble turn-over frequency is nominally

$$f_{TT} = 1/(2\pi C(14 \text{ k}\Omega))$$

and the bass turn-over frequency is nominally

$f_{BT} = 1/(2\pi C(30.4 \text{ k}\Omega)),$

when maximum boost is chosen. The inflection points (the frequencies where the boost or cut is within 3 dB of the final value) are, for treble and bass respectively,

$f_{TI} = 1/(2\pi C(1.9 \text{ k}\Omega))$  $f_{BI} = 1/(2\pi C(169.6 \text{ k}\Omega))$

Increasing the values of C2 and C3 decreases the turnover and inflection frequencies: i.e., the Tone Control Response Curves shown in **Typical Performance Section** will shift left when C2 and C3 are increased and shift right when C2 and C3 are decreased. With C2 = C3 = 0.0082  $\mu$ F, 2 dB steps are achieved at 100 Hz and 10 kHz. Changing C2 and C3 to 0.01  $\mu$ F shifts the 2 dB step frequency to 72 Hz and 8.3 kHz.If the tone control capacitors' size is decreased these frequencies will increase.With C2 = C3 = 0.0068  $\mu$ F the 2 dB steps take place at 130 Hz and 11.2 kHz.

FIGURE 6. Tone Control Diagram

#### **GENERAL PURPOSE OUTPUT PIN**

The General Purpose Output pin is intended to be used as a control signal for other devices, such as an external power amplifier. This pin is controlled through the  $I^2C$  interface and is not related to any other functions within the LM4832. Refer to the Truth Tables section for the proper  $I^2C$  data bits to utilize this function.

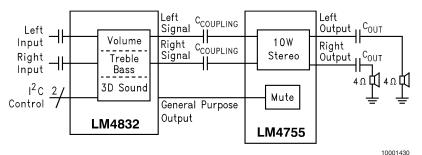

*Figure 7* shows an example of using the General Purpose Output to interface with an external power amp. In this case, the external power amp is the LM4755 stereo 10 watt per

channel (rms) power amplifier with mute. AC-coupling capacitors must be used to remove the DC bias present between the LM4832 outputs and the external power amplifier inputs.

Prior to placing any of the preamp circuitry in shutdown, the General Purpose Output should be used to disable the external power amplifier. This will prevent any shutdown transients in the preamp circuitry from being amplified by the external power amplifier.

10W/ch System with I<sup>2</sup>C Controlled Tone,Volume and 3D Sound

#### FIGURE 7.

#### LOOP IN/OUT PINS

The Loop In and Loop Out pins are used when an application requires a special function to be performed on the audio signal. As shown in *Figure 7*, the audio signal is taken from the Loop Out pin and sent to an external signal processor. After the signal is processed externally, it is fed back into the Loop In pin.

An example of where this functionality would be used is computer speakers. The external loop could be used to provide bass boost to counteract the speaker's natural or baffle-induced rolloff. Since the Loop In pin goes directly to the input of a CMOS amplifier, the input impedance is very high. The Loop Out pin is driven by the input attenuation amplifier, which is capable of driving impedances as low as 1 k $\Omega$ .

LM4832

FIGURE 8.

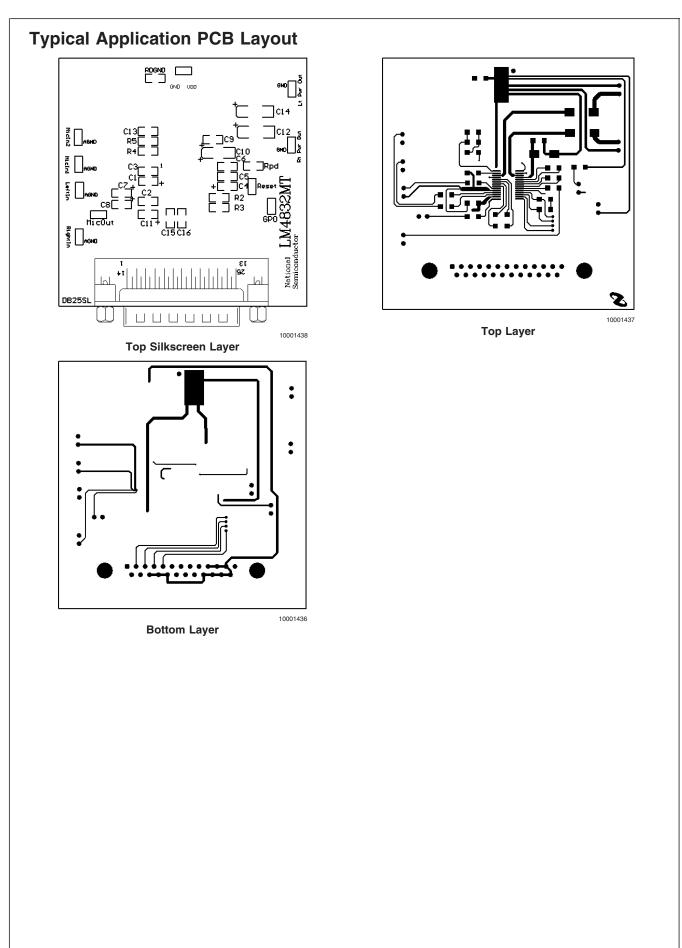

LM4832 SAMPLE LAYOUT

| LAYOUT PARTS LIST       |                              |          |  |  |  |  |

|-------------------------|------------------------------|----------|--|--|--|--|

| Name                    | Туре                         | Quantity |  |  |  |  |

| Capacitors:             |                              |          |  |  |  |  |

| C1                      | 1µF, Tantalum, 16V, 10%      | 1        |  |  |  |  |

| C2                      | 0.1µF, Tantalum, 16V, 10%    | 1        |  |  |  |  |

| C3                      | 0.1µF, Tantalum, 16V, 10%    | 1        |  |  |  |  |

| C4                      | 1µF, Tantalum, 16V, 10%      | 1        |  |  |  |  |

| C5                      | 8200pF, Ceramic, 50V, 10%    | 1        |  |  |  |  |

| C6                      | 8200pF, Ceramic, 50V, 10%    | 1        |  |  |  |  |

| C7                      | 1µF, Tantalum, 16V, 10%      | 1        |  |  |  |  |

| C8                      | 1µF, Tantalum, 16V, 10%      | 1        |  |  |  |  |

| C9                      | 1µF, Tantalum, 16V, 10%      | 1        |  |  |  |  |

| C10                     | 10µF, Tantalum, 16V, 10%     | 1        |  |  |  |  |

| C11                     | 1µF, Tantalum, 16V, 10%      | 1        |  |  |  |  |

| C12                     | 470µF, Size D; or 300µF, 10V | 1        |  |  |  |  |

| C13                     | 0.1µF, Tantalum, 50V, 10%    | 1        |  |  |  |  |

| C14                     | 470µF, Size D; 300µF, 10V    | 1        |  |  |  |  |

| C15                     | 8200pF, Ceramic, 50V, 10%    | 1        |  |  |  |  |

| C16                     | 8200pF, Ceramic, 50V, 10%    | 1        |  |  |  |  |

| Resistors:              | ·                            | · ·      |  |  |  |  |

| RPD                     | 1kΩ, 1/8W                    | 1        |  |  |  |  |

| RDGND                   | 100Ω, 1/8W                   | 1        |  |  |  |  |

| R2                      | 10kΩ, 1/8W                   | 1        |  |  |  |  |

| R3                      | 10kΩ, 1/8W                   | 1        |  |  |  |  |

| R4                      | 20kΩ, 1/8W                   | 1        |  |  |  |  |

| R5                      | 680kΩ, 1/8W                  | 1        |  |  |  |  |

| Connectors:             |                              |          |  |  |  |  |

| HDR 2X1                 | 100mil                       | 9        |  |  |  |  |

| DB25SL connector - male |                              | 1        |  |  |  |  |

#### LAYOUT DESCRIPTION

The layout given in the following pages is meant to be connected to a PC by a parallel port (printer) cable. The board is controlled by software for a Windows PC. The parallel cable must be the standard type used for hooking up a printer to a PC: one end is a male DB-25 connector and the other end is a female DB-25 connector.

This layout is set up to allow the use of the internal tonecontrol circuitry or the external loop.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.