# LMV710/LMV711/LMV715 Low Power, RRIO Operational Amplifiers with High Output Current Drive and Shutdown Option

# **General Description**

The LMV710, LMV711 and LMV715 are BiCMOS operational amplifiers with a CMOS input stage. These devices have greater than RR input common mode voltage range, rail-to-rail output and high output current drive. They offer a bandwidth of 5MHz and a slew rate of 5V/µs.

On the LMV711/LMV715, a separate shutdown pin can be used to disable the device and reduces the supply current to 0.2µA (typical). They also feature a turn on time of less than 10µs. It is an ideal solution for power sensitive applications, such as cellular phone, pager, palm computer, etc. In addition, once the LMV715 is in shutdown the output will be "Tri-stated".

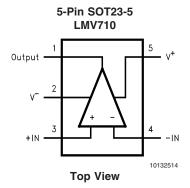

The LMV710 is offered in the space saving SOT23-5 Tiny package. The LMV711 and LMV715 are offered in the space saving SOT23-6 Tiny package.

The LMV710/711/715 are designed to meet the demands of low power, low cost, and small size required by cellular phones and similar battery powered portable electronics.

# **Features**

(For 5 Supply, Typical Unless Otherwise Noted).

■ Low offset voltage 3mV, max■ Gain-bandwidth product 5MHz, typ

■ Slew rate 5V/µs, typ

■ Space saving packages SOT23-5 and SOT23-6 ■ Turn on time from shutdown <10µs

Industrial temperature range

Supply current in shutdown mode

0.2µA, typ

■ Guaranteed 2.7V and 5V Performance

■ Unity gain stable

■ Rail-to-rail input and output

■ Capable of driving 600Ω load

# **Applications**

- Wireless phones

- GSM/TDMA/CDMA power amp control

- AGC, RF power detector

- Temperature compensation

- Wireless LAN

- Bluetooth

- HomeRF

# **Typical Application**

# RSENSE O.2 RSENSE VOUT RSENSE RSENSE

$V_{OUT} = \frac{R_{SENSE} \cdot R_3}{R_1} \cdot I_{Charge} = 1 \Omega \cdot I_{Charge}$

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2)

Machine Model 100V 2000V Human Body Model Differential Input Voltage ± Supply Voltage Voltage at Input/Output Pin  $(V^+) + 0.4V$  $(V^{-}) - 0.4V$ Supply Voltage (V+ - V -) 5.5V Output Short Circuit to V+ (Note 3)

Output Short Circuit to V-(Note 4) Current at Input Pin ± 10mA

Mounting Temp.

Infrared or Convection (20 sec) 235°C Storage Temperature Range -65°C to 150°C Junction Temperature $(T_{JMAX})$ 150°C (Note 5)

# **Operating Ratings** (Note 1)

Supply Voltage 2.7V to 5.0V Temperature Range -40°C to 85°C

Thermal Resistance  $(\theta_{JA})$

MF05A Package, 5-Pin SOT23 265 °C/W MF06A package, 6-Pin SOT23 265 °C/W

# 2.7V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ .  $V^+ = 2.7V$ ,  $V^- = 0V$ ,  $V_{CM} = 1.35V$  and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol              | Parameter                       | Condition                           | Тур      | Limits   | Units |

|---------------------|---------------------------------|-------------------------------------|----------|----------|-------|

|                     |                                 |                                     | (Note 6) | (Note 7) |       |

| V <sub>os</sub>     | Input Offset Voltage            | $V_{CM} = 0.85V \& V_{CM} = 1.85V$  | 0.4      | 3        | mV    |

|                     |                                 |                                     |          | 3.2      | max   |

| $I_B$               | Input Bias Current              |                                     | 4        |          | pA    |

| CMRR                | Common Mode Rejection Ratio     | $0 \le V_{CM} \le 2.7V$             | 75       | 50       | dB    |

|                     |                                 |                                     |          | 45       | min   |

| PSRR                | Power Supply Rejection Ratio    | $2.7V \le V^+ \le 5V,$              | 110      | 70       | dB    |

|                     |                                 | $V_{CM} = 0.85V$                    |          | 68       | min   |

|                     |                                 | $2.7V \le V^+ \le 5V,$              | 95       | 70       | dB    |

|                     |                                 | $V_{CM} = 1.85V$                    |          | 68       | min   |

| $V_{CM}$            | Input Common-Mode Voltage Range | For CMRR ≥ 50dB                     | -0.3     | -0.2     | V     |

|                     |                                 |                                     | 3        | 2.9      | v     |

| I <sub>SC</sub>     | Output Short Circuit Current    | Sourcing                            | 28       | 15       | mA    |

|                     |                                 | V <sub>O</sub> =0V                  |          | 12       | min   |

|                     |                                 | Sinking                             | 40       | 25       | mA    |

|                     |                                 | $V_O = 2.7V$                        |          | 22       | min   |

| Vo                  | Output Swing                    | $R_L = 10k\Omega$ to 1.35V          | 2.68     | 2.62     | V     |

| Vo                  |                                 |                                     |          | 2.60     | min   |

|                     |                                 |                                     | 0.01     | 0.12     | V     |

|                     |                                 |                                     |          | 0.15     | max   |

|                     |                                 | $R_L = 600\Omega$ to 1.35V          | 2.55     | 2.52     | V     |

|                     |                                 |                                     |          | 2.50     | min   |

|                     |                                 |                                     | 0.05     | 0.23     | V     |

|                     |                                 |                                     |          | 0.30     | max   |

| $V_O$ (SD)          | Output Voltage Level in         |                                     | 50       | 200      | mV    |

|                     | Shutdown Mode (LMV711 only)     |                                     |          |          |       |

| I <sub>O</sub> (SD) | Output Leakage Current in       |                                     | 1        |          | pА    |

|                     | Shutdown Mode (LMV715 Only)     |                                     |          |          |       |

| C <sub>O</sub> (SD) | Output Capacitance in           |                                     | 32       |          | pF    |

|                     | Shutdown Mode (LMV715 Only)     |                                     |          |          |       |

| $I_S$               | Supply Current                  | ON Mode                             | 1.22     | 1.7      | mA    |

|                     |                                 |                                     |          | 1.9      | max   |

|                     |                                 | Shutdown Mode, V <sub>SD</sub> = 0V | 0.002    | 10       | μΑ    |

# 2.7V Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J$  = 25°C.  $V^+$  = 2.7V,  $V^-$  = 0V,  $V_{CM}$  = 1.35V and  $R_L$  > 1M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol          | Parameter                    | Condition                        | Typ        | Limits     | Units     |  |

|-----------------|------------------------------|----------------------------------|------------|------------|-----------|--|

|                 |                              | -                                | (Note 6)   | (Note 7)   |           |  |

| $A_V$           | Large Signal Voltage         | Sourcing                         | 115        | 80         | dB        |  |

|                 |                              | $R_L = 10k\Omega$                |            | 76         | min       |  |

|                 |                              | $V_{O} = 1.35V \text{ to } 2.3V$ |            |            |           |  |

|                 |                              | Sinking                          | 113        | 80         | dB        |  |

|                 |                              | $R_L = 10k\Omega$                |            | 76         | min       |  |

|                 |                              | $V_{\rm O} = 0.4 V$ to 1.35 V    |            |            |           |  |

|                 |                              | Sourcing                         | 110        | 80         | dB        |  |

|                 |                              | $R_L = 600\Omega$                |            | 76         | min       |  |

|                 |                              | $V_{\rm O} = 1.35 V$ to 2.2V     |            |            |           |  |

|                 |                              | Sinking                          | 100        | 80         | dB        |  |

|                 |                              | $R_L = 600\Omega$                |            | 76         | min       |  |

|                 |                              | $V_{\rm O} = 0.5 V$ to 1.35 V    |            |            |           |  |

| SR              | Slew Rate                    | (Note 8)                         | 5          |            | V/µs      |  |

| GBWP            | Gain-Bandwidth Product       |                                  | 5          |            | MHz       |  |

| φ <sub>m</sub>  | Phase Margin                 |                                  | 60         |            | Deg       |  |

| T <sub>ON</sub> | Turn-on Time from Shutdown   |                                  | <10        |            | μs        |  |

| V <sub>SD</sub> | Shutdown Pin Voltage Range   | On Mode                          | 1.5 to 2.7 | 2.4 to 2.7 | V         |  |

|                 |                              | Shutdown Mode                    | 0 to 1     | 0 to 0.8   | V         |  |

| e <sub>n</sub>  | Input-Referred Voltage Noise | f = 1kHz                         | 20         |            | <u>nV</u> |  |

| e <sub>n</sub>  | Input-Referred Voltage Noise | f = 1kHz                         | 20         |            | _ 1       |  |

# 3.2V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ .  $V^+ = 3.2V$ ,  $V^- = 0V$ ,  $V_{CM} = 1.6V$ . **Boldface** limits apply at the temperature extremes.

| Symbol | Parameter    | Conditions             | Тур      | Limit    | Units |

|--------|--------------|------------------------|----------|----------|-------|

|        |              |                        | (Note 6) | (Note 7) |       |

| Vo     | Output Swing | I <sub>O</sub> = 6.5mA | 3.0      | 2.95     | V     |

|        |              |                        |          | 2.92     | min   |

|        |              |                        | 0.01     | 0.18     | V     |

|        |              |                        |          | 0.25     | max   |

# **5V Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ .  $V^+ = 5V$ ,  $V_- = 0V$ ,  $V_{CM} = 2.5V$ , and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol          | Parameter                       | Condition                          | Тур      | Limits   | Units |

|-----------------|---------------------------------|------------------------------------|----------|----------|-------|

|                 |                                 |                                    | (Note 6) | (Note 7) |       |

| Vos             | Input Offset Voltage            | $V_{CM} = 0.85V \& V_{CM} = 1.85V$ | 0.4      | 3        | mV    |

|                 |                                 |                                    |          | 3.2      | max   |

| I <sub>B</sub>  | Input Bias Current              |                                    | 4        |          | pA    |

| CMRR            | Common Mode Rejection Ratio     | $0V \le V_{CM} \le 5V$             | 70       | 50       | dB    |

|                 |                                 |                                    |          | 48       | min   |

| PSRR            | Power Supply Rejection Ratio    | $2.7V \le V^+ \le 5V,$             | 110      | 70       | dB    |

|                 |                                 | $V_{CM} = 0.85V$                   |          | 68       | min   |

|                 |                                 | $2.7V \le V^+ \le 5V,$             | 95       | 70       | dB    |

|                 |                                 | V <sub>CM</sub> = 1.85V            |          | 68       | min   |

| V <sub>CM</sub> | Input Common-Mode Voltage Range | For CMRR ≥ 50dB                    | -0.3     | -0.2     | V     |

|                 |                                 |                                    | 5.3      | 5.2      | V     |

# 5V Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ .  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = 2.5V$ , and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol              | Parameter                                                | Condition                                   | Typ<br>(Note 6) | Limits<br>(Note 7) | Units             |

|---------------------|----------------------------------------------------------|---------------------------------------------|-----------------|--------------------|-------------------|

| I <sub>sc</sub>     | Output Short Circuit Current                             | Sourcing                                    | 35              | 25                 | mA                |

| '50                 | Carpat Grieft Griedit Garrent                            | $V_O = 0V$                                  |                 | 21                 | min               |

|                     |                                                          | Sinking                                     | 40              | 25                 | mA                |

|                     |                                                          | $V_{O} = 5V$                                |                 | 21                 | min               |

| Vo                  | Output Swing                                             | $R_L = 10k\Omega$ to 2.5V                   | 4.98            | 4.92               | V                 |

|                     |                                                          |                                             |                 | 4.90               | min               |

|                     |                                                          |                                             | 0.01            | 0.12               | V                 |

|                     |                                                          |                                             |                 | 0.15               | max               |

|                     |                                                          | $R_L = 600\Omega$ to 2.5V                   | 4.85            | 4.82               | V                 |

|                     |                                                          |                                             |                 | 4.80               | min               |

|                     |                                                          |                                             | 0.05            | 0.23               | V                 |

|                     |                                                          |                                             |                 | 0.3                | max               |

| V <sub>O</sub> (SD) | Output Voltage Level in<br>Shutdown Mode (LMV711 only)   |                                             | 50              | 200                | mV                |

| I <sub>O</sub> (SD) | Output Leakage Current in<br>Shutdown Mode (LMV715 Only) |                                             | 1               |                    | pA                |

| C <sub>O</sub> (SD) | Output Capacitance in shutdown Mode (LMV715 Only)        |                                             | 32              |                    | pF                |

| I <sub>s</sub>      | Supply Current                                           | On Mode                                     | 1.17            | 1.7                | mA                |

| 3                   |                                                          |                                             |                 | 1.9                | max               |

|                     |                                                          | Shutdown Mode                               | 0.2             | 10                 | μΑ                |

| A <sub>V</sub>      | Large Signal Voltage Gain                                | Sourcing                                    | 123             | 80                 | dB                |

|                     |                                                          | $R_L = 10k\Omega$                           |                 | 76                 | min               |

|                     |                                                          | $V_{O} = 2.5V \text{ to } 4.6V$             |                 |                    |                   |

|                     |                                                          | Sinking                                     | 120             | 80                 | dB                |

|                     |                                                          | $R_L = 10k\Omega$                           |                 | 76                 | min               |

|                     |                                                          | $V_{\rm O} = 0.4 \text{V to } 2.5 \text{V}$ |                 |                    |                   |

|                     |                                                          | Sourcing                                    | 110             | 80                 | dB                |

|                     |                                                          | $R_L = 600\Omega$                           |                 | 76                 | min               |

|                     |                                                          | V <sub>O</sub> = 2.5V to 4.5V               |                 |                    |                   |

|                     |                                                          | Sinking                                     | 118             | 80                 | dB                |

|                     |                                                          | $R_{L} = 600\Omega$                         |                 | 76                 | min               |

|                     | Olavi Data                                               | $V_{\rm O} = 0.5 \text{V to } 2.5 \text{V}$ | -               |                    | 1//               |

| SR                  | Slew Rate                                                | (Note 8)                                    | 5               |                    | V/µs              |

| GBWP                | Gain-Bandwidth Product                                   |                                             | 5               |                    | MHz               |

| ф <sub>т</sub>      | Phase Margin                                             |                                             | 60              |                    | Deg               |

| T <sub>ON</sub>     | Turn-on Time from Shutdown                               |                                             | <10             | 0.4                | μs                |

| $V_{SD}$            | Shutdown Pin Voltage Range                               | ON Mode                                     | 2 to 5          | 2.4 to 5           | V                 |

|                     |                                                          | Shutdown Mode                               | 0 to 1.5        | 0 to 0.8           | n\/               |

| e <sub>n</sub>      | Input-Referred Voltage Noise                             | f = 1kHz                                    | 20              |                    | <u>nV</u><br>1⁄Hz |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

- Note 2: Human body model, 1.5 k $\Omega$  in series with 100pF. Machine model,  $0\Omega$  in series with 100pF.

- Note 3: Shorting circuit output to V<sup>+</sup> will adversely affect reliability.

- Note 4: Shorting circuit output to  $V^-$  will adversely affect reliability.

- Note 5: The maximum power dissipation is a function of  $T_{J(max)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(max)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board.

- Note 6: Typical values represent the most likely parametric norm.

- Note 7: All limits are guaranteed by testing or statistical analysis.

- $\textbf{Note 8:} \ \ \text{Number specified is the slower of the positive and negative slew rates}.$

# **Typical Performance Characteristics** Unless otherwise specified, $V_S = +5V$ , single supply, $T_A = 25^{\circ}C$ .

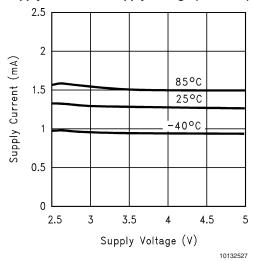

### Supply Current vs. Supply Voltage (On Mode)

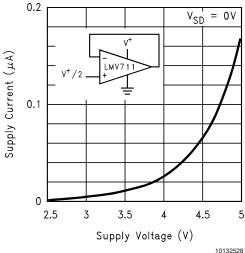

# LMV711 and LMV715 Supply Current vs. Supply Voltage (Shutdown Mode)

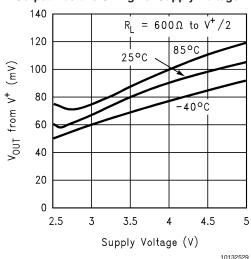

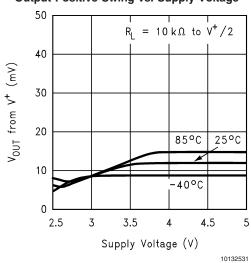

# **Output Positive Swing vs. Supply Voltage**

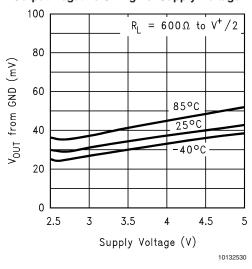

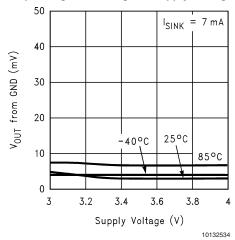

# **Output Negative Swing vs. Supply Voltage**

# Output Positive Swing vs. Supply Voltage

# **Output Negative Swing vs. Supply Voltage**

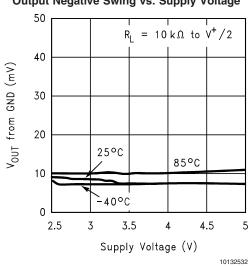

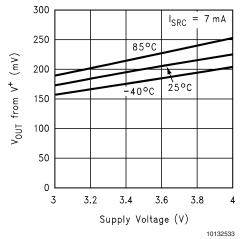

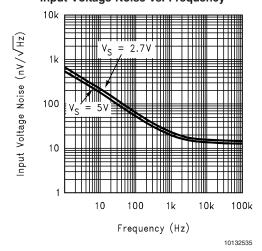

# Typical Performance Characteristics Unless otherwise specified, V<sub>S</sub> = +5V, single supply,

$T_A = 25$ °C. (Continued)

### **Output Positive Swing vs. Supply Voltage**

# Input Voltage Noise vs. Frequency

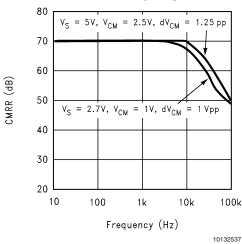

# CMRR vs. Frequency

### **Output Negative Swing vs. Supply Voltage**

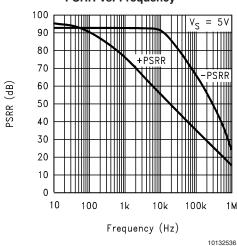

# PSRR vs. Frequency

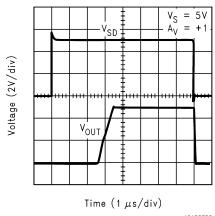

### LMV711/LMV715 Turn On Characteristics

# Typical Performance Characteristics Unless otherwise specified, V<sub>S</sub> = +5V, single supply,

$T_A = 25$ °C. (Continued)

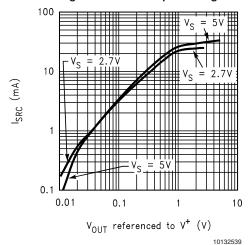

### Sourcing Current vs. Output Voltage

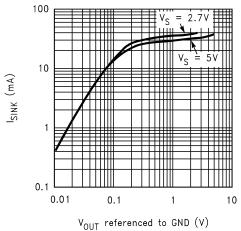

# Sinking Current vs. Output Voltage

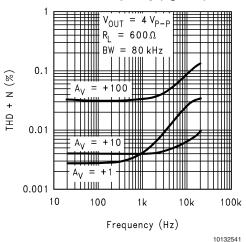

# THD+N vs. Frequency $(V_S = 5V)$

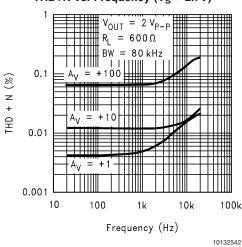

# THD+N vs. Frequency (V<sub>S</sub> = 2.7V)

10132540

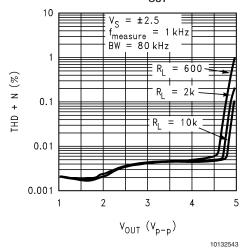

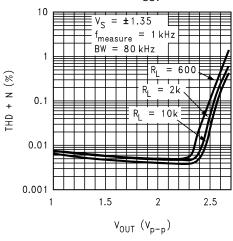

# THD+N vs. V<sub>OUT</sub>

# THD+N vs. $V_{\rm OUT}$

# Typical Performance Characteristics Unless otherwise specified, $V_S = +5V$ , single supply,

$T_A = 25$ °C. (Continued)

10132507

# Typical Performance Characteristics Unless otherwise specified, V<sub>S</sub> = +5V, single supply,

$T_A = 25$ °C. (Continued)

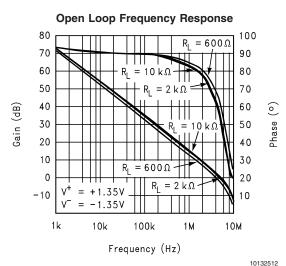

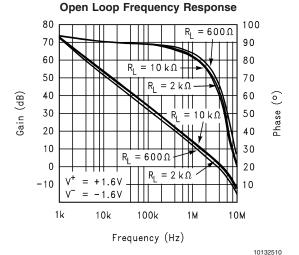

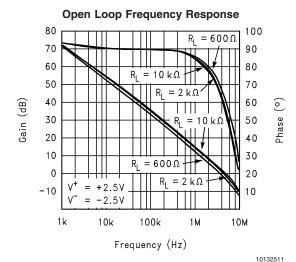

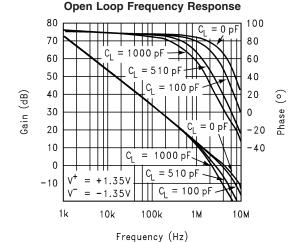

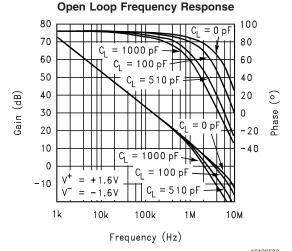

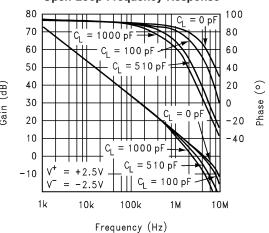

**Open Loop Frequency Response**

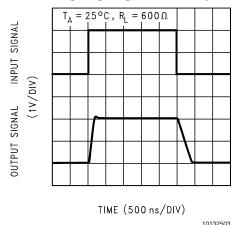

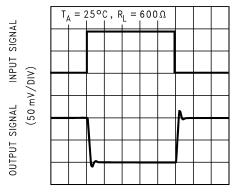

Non-Inverting Large Signal Pulse Response

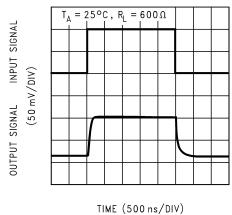

Non-Inverting Small Signal Pulse Response

# **Typical Performance Characteristics** Unless otherwise specified, $V_S = +5V$ , single supply, $T_A = 25^{\circ}C$ . (Continued)

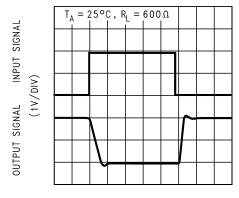

### **Inverting Large Signal Pulse Response**

TIME (500 ns/DIV)

10132504

10132549

10

### **Inverting Small Signal Pulse Response**

TIME (500 ns/DIV)

# **Application Note**

### 1.0 SUPPLY BYPASSING

The application circuits in this datasheet do not show the power supply connections and the associated bypass capacitors for simplification. When the circuits are built, it is always required to have bypass capacitors. Ceramic disc capacitors (0.1 $\mu$ F) or solid tantalum (1 $\mu$ F) with short leads, and located close to the IC are usually necessary to prevent interstage coupling through the power supply internal impedance. Inadequate bypassing will manifest itself by a low frequency oscillation or by high frequency instabilities. Sometimes, a 10 $\mu$ F (or larger) capacitor is used to absorb low frequency variations and a smaller 0.1 $\mu$ F disc is paralleled across it to prevent any high frequency feedback through the power supply lines.

### 2.0 SHUTDOWN MODE

The LMV711 and LMV715 have a shutdown pin. To conserve battery life in portable applications, they can be disabled when the shutdown pin voltage is pulled low. For LMV711 during shutdown mode, the output stays at about 50mV from the lower rail, and the current drawn from the power supply is 0.2μA (typical). This makes the LMV711 an ideal solution for power sensitive applications. For the LMV715 during shutdown mode, the output will be "Tri-stated".

The shutdown pin should never be left unconnected. In applications where shutdown operation is not needed and the LMV711 or LMV715 is used, the shutdown pin should be connected to V<sup>+</sup>. Leaving the shutdown pin floating will result in an undefined operation mode and the device may oscillate between shutdown and active modes.

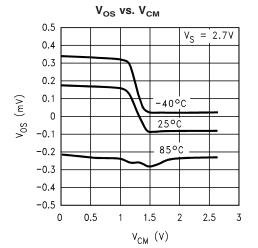

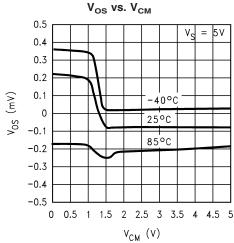

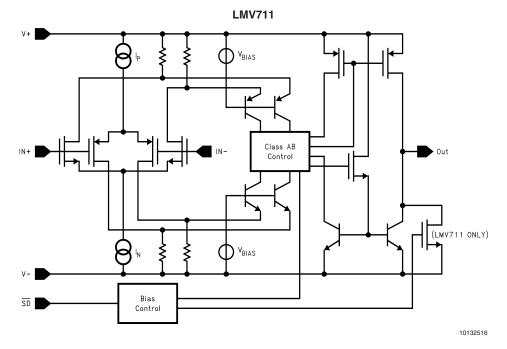

# 3.0 RAIL-TO-RAIL INPUT

The rail-to-rail input is achieved by using paralleled PMOS and NMOS differential input stages. (See Simplified Schematics in this datasheet). When the common mode input voltage changes from ground to the positive rail, the input stage goes through three modes. First, the NMOS pair is cutoff and the PMOS pair is active. At around 1.4V, both PMOS and NMOS pairs operate, and finally the PMOS pair is cutoff and NMOS pair is active. Since both input stages have their own offset voltage ( $\rm V_{OS}$ ), the offset of the amplifier becomes a function of the common-mode input voltage. See curves for  $\rm V_{OS}$  vs.  $\rm V_{CM}$  in curve section.

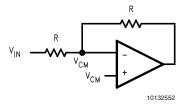

As shown in the curve, the  $V_{OS}$  has a crossover point at 1.4V above  $V^-$ . Proper design must be done in both DC and AC coupled applications to avoid problems. For large input signals that include the  $V_{OS}$  crossover point in their dynamic range, it will cause distortion in the output signal. One way to avoid such distortion is to keep the signal away from the crossover point. For example, in a unity gain buffer configuration and with  $V_S = 5V$ , a 3V peak-to-peak signal center at 2.5V will contain input-crossover distortion. To avoid this, the input signal should be centered at 3.5V instead. Another way to avoid large signal distortion is to use a gain of -1 circuit which avoids any voltage excursions at the input terminals of the amplifier. See *Figure 1*. In this circuit, the common mode DC voltage ( $V_{CM}$ ) can be set at a level away from the  $V_{OS}$  crossover point.

FIGURE 1.

When the input is a small signal and this small signal falls inside the  $\rm V_{OS}$  transition range, the gain, CMRR and some other parameters will be degraded. To resolve this problem, the small signal should be placed such that it avoids the  $\rm V_{OS}$  crossover point.

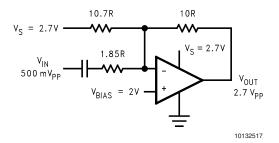

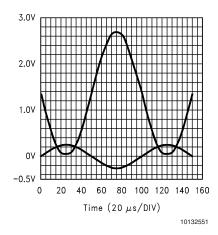

To achieve maximum output swing, the output should be biased at mid-supply. This is normally done by biasing the input at mid-supply. But with supply voltage range from 2V to 3.4V, the input of the op amp should not be biased at mid-supply because of the transition of the  $V_{\rm OS}$ . Figure 2 shows an example of how to get away from the  $V_{\rm OS}$  crossover point and maintain a maximum swing with a 2.7V supply. Figure 3 shows the waveforms of  $V_{\rm IN}$  and  $V_{\rm OUT}$ .

FIGURE 2.

FIGURE 3.

The inputs can be driven 300mV beyond the supply rails without causing phase reversal at the output. However, the inputs should not be allowed to exceed the maximum ratings.

# **Application Note** (Continued)

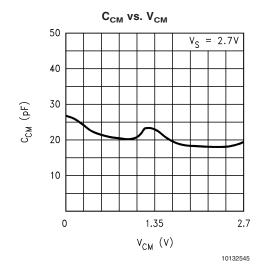

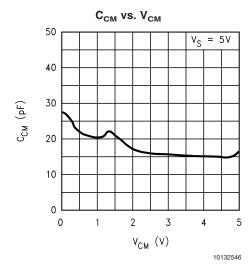

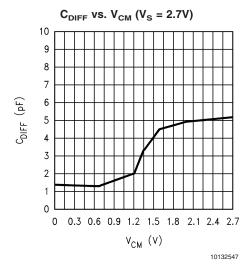

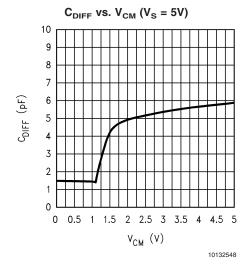

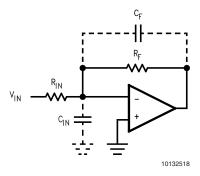

### 4.0 COMPENSATION OF INPUT CAPACITANCE

In the application (*Figure 4*) where a large feedback resistor is used, the feedback resistor can react with the input capacitance of the op amp and introduce an additional pole to the close loop frequency response.

FIGURE 4. Cancelling the Effect of Input Capacitance

This pole occurs at frequency  $f_p$ , where

$$f_P = \frac{1}{2\pi (R_{IN}||R_F)C_{IN}}$$

Any stray capacitance due to external circuit board layout, any source capacitance from transducer or photodiode connected to the summing node will also be added to the input capacitance. If  $\rm f_p$  is less than or close to the unity-gain bandwidth (5MHz) of the op amp, the phase margin of the loop is reduced and can cause the system to be unstable.

To avoid this problem, make sure that  $f_p$  occurs at least 2 octaves beyond the expected –3dB frequency corner of the close loop frequency response. If not, a feedback capacitor  $C_F$  can be placed in parallel with  $R_F$  such that

$$\frac{1}{2\pi R_F C_F} = \frac{1}{2\pi (R_{IN}||R_F)(C_F + C_{IN})}$$

The paralleled  $R_{\text{F}}$  and  $C_{\text{F}}$  introduce a zero, which cancels the effect from the pole.

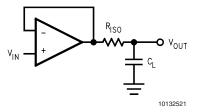

### **5.0 CAPACITIVE LOAD TOLERANCE**

The LMV710, LMV711 and LMV715 can directly drive 200pF in unity-gain without oscillation. The unity-gain follower is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers. The combination of the amplifier's output impedance and the capacitive load induces phase lag. This results in either an underdamped pulse response or oscillation. To drive a heavier capacitive load, circuit in *Figure 5* can be used.

FIGURE 5. Indirectly Driving A Capacitive Load using Resistive Isolation

In Figure 5, the isolation resistor  $R_{\rm ISO}$  and the load capacitor  $C_{\rm L}$  form a pole to increase stability by adding more phase margin to the overall system. The desired performance depends on the value of  $R_{\rm ISO}$ . The bigger the  $R_{\rm ISO}$  resistor value, the more stable  $V_{\rm OUT}$  will be. But the DC accuracy is not great when the  $R_{\rm ISO}$  gets bigger. If there were a load resistor in Figure 5, the output would be voltage divided by  $R_{\rm ISO}$  and the load resistor.

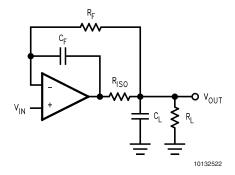

The circuit in Figure 6 is an improvement to the one in Figure 5 because it provides DC accuracy as well as AC stability. In this circuit,  $R_{\rm F}$  provides the DC accuracy by using feed-forward techniques to connect  $V_{\rm IN}$  to  $R_{\rm L}.$   $C_{\rm F}$  and  $R_{\rm ISO}$  serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop. Increased capacitive drive is possible by increasing the value of  $C_{\rm F}$ . This in turn will slow down the pulse response.

FIGURE 6. Indirectly Driving A Capacitive A Load with DC Accuracy

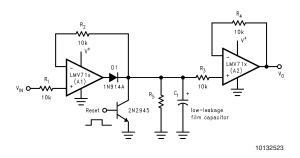

# 6.0 APPLICATION CIRCUITS PEAK DETECTOR

Peak detectors are used in many applications, such as test equipment, measurement instrumentation, ultrasonic alarm systems, etc. *Figure 7* shows the schematic diagram of a peak detector using LMV710 or LMV711 or LMV715. This peak detector basically consists of a clipper, a parallel RC network, and a voltage follower.

# **Application Note** (Continued)

FIGURE 7. Peak Detector

The capacitor  $C_1$  is first discharged by applying a positive pulse to the reset transistor. When a positive voltage  $V_{IN}$  is applied to the input, the input voltage is higher than the voltage across  $C_1$ . The output of the op amp goes high and forward biases the diode  $D_1$ . The capacitor  $C_1$  is charged to  $V_{IN}$ . When the input becomes less than the current capacitor voltage, the output of the op amp A1 goes low and the diode  $D_1$  is reverse biased. This isolates the  $C_1$  and leaves it with the charge equivalent to the peak of the input voltage. The follower prevents unintentional discharging of  $C_1$  by loading from the following circuit.

$\rm R_5$  and  $\rm C_1$  are properly selected so that the capacitor is charged rapidly to  $\rm V_{IN}.$  During the holding period, the capacitor slowly discharge through  $\rm C_1,$  via leakage of the capacitor and the reverse-biased diode, or op amp bias currents. In any cases the discharging time constant is much larger than the charge time constant. And the capacitor can hold its voltage long enough to minimize the output ripple.

Resistors  $\rm R_2$  and  $\rm R_3$  limit the current into the inverting input of A1 and the non-inverting input of A2 when power is disconnected from the circuit. The discharging current from  $\rm C_1$  during power off may damage the input circuitry of the op amps.

The peak detector can be reset by applying a positive pulse to the reset transistor. The charge on the capacitor is dumped into ground, and the detector is ready for another cycle.

The maximum input voltage to this detector should be less than  $(V^+ - V_D)$ , where  $V_D$  is the forward voltage drop of the diode. Otherwise, the input voltage should be scaled down before applying to the circuit.

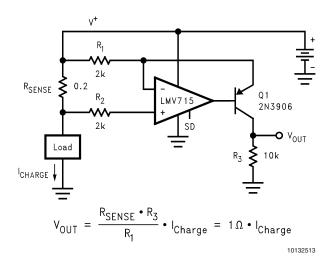

### HIGH SIDE CURRENT SENSING

The high side current sensing circuit (Figure 8) is commonly used in a battery charger to monitor charging current to prevent over-charging. A sense resistor  $R_{sense}$  is connected to the battery directly. This system requires an op amp with rail-to-rail input. The LMV710/711/715 are ideal for this application because its common mode input range can go beyond the positive rail.

FIGURE 8. High Side Current Sensing

# Application Note (Continued)

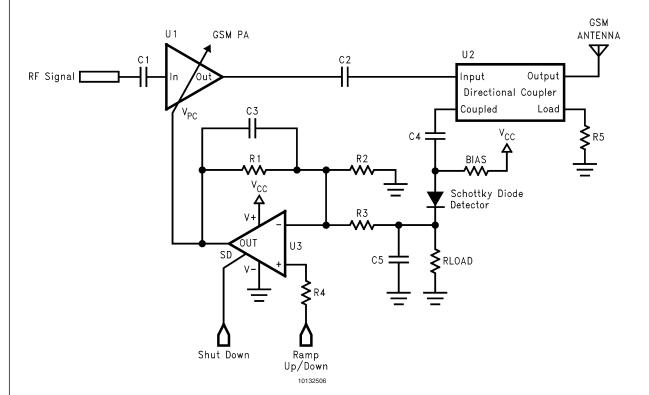

FIGURE 9. Typical of GSM P.A. Control Loop

### **GSM POWER AMPLIFIER CONTROL LOOP**

There are four critical sections in the GSM Power Amplifier Control Loop. The class-C  $\rm R_F$  power amplifier provides amplification of the  $\rm R_F$  signal. A directional coupler couples small amount of  $\rm R_F$  energy from the output of the  $\rm R_F$  P. A. to an envelope detector diode. The detector diode senses the signal level and rectifies it to a DC level to indicate the signal strength at the antenna. An op-amp is used as an error amplifier to process the diode voltage and ramping voltage. This loop control the power amplifier gain via the op-amp and forces the detector diode voltage and ramping voltage to be equal. Power control is accomplished by changing the ramping voltage.

The LMV710, LMV711 and LMV715 are well suited as an error amplifier in this application. The LMV711 and LMV715 have an extra shutdown pin to switch the op-amp to shutdown mode. In shutdown mode, the LMV711 and LMV715 consume very low current. The LMV711 provides a ground voltage to the power amplifier control pin  $V_{\rm PC}$ . Therefore, the power amplifier can be turned off to save battery life. The LMV715 output will be "tri-stated" when in shutdown.

# **Simplified Schematic**

# **Connection Diagrams**

# **Ordering Information**

| Package      | Temperature Range<br>Industrial<br>-40°C to +85°C | Packaging Marking | Transport Media        | NSC<br>Drawing |  |

|--------------|---------------------------------------------------|-------------------|------------------------|----------------|--|

| 5-Pin SOT23  | LMV710M5                                          | A48A              | 1k Units Tape and Reel | MF05A          |  |

| 5-111 30123  | LMV710M5X                                         | A40A              | 3k Units Tape and Reel | IVII USA       |  |

|              | LMV711M6                                          | A47A              | 1k Units Tape and Reel |                |  |

| 6-Pin SOT23  | LMV711M6X                                         | A4/A              | 3k Units Tape and Reel | MF06A          |  |

| 6-2111 30123 | LMV715MF                                          | A75A              | 1k Units Tape and Reel | IVIFUOA        |  |

|              | LMV715MFX                                         | A/SA              | 3k Units Tape and Reel |                |  |

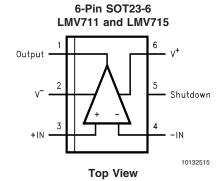

# **SOT-23 Tape and Reel Specification**

# **Tape Format**

| Tape Section | # Cavities | Cavity Status | Cover Tape Status |

|--------------|------------|---------------|-------------------|

| Leader       | 0 (min)    | Empty         | Sealed            |

| (Start End)  | 75 (min)   | Empty         | Sealed            |

| Carrier      | 3000       | Filled        | Sealed            |

|              | 1000       | Filled        | Sealed            |

| Trailer      | 125 (min)  | Empty         | Sealed            |

| (Hub End)    | 0 (min)    | Empty         | Sealed            |

# **Tape Dimensions**

10132555

| TAPE | DIM   | DIM Ao | DIM   | DIM Bo | DIM              | DIM             | DIM P1 | DIM             | DIM           |

|------|-------|--------|-------|--------|------------------|-----------------|--------|-----------------|---------------|

| SIZE | Α     |        | В     |        | F                | Ko              |        | Т               | W             |

| 8 mm | .130  | .124   | .130  | .126   | .138 ± .002      | .055 ± .004     | .157   | .008 ± .004     | .315 ± .012   |

|      | (3.3) | (3.15) | (3.3) | (3.2)  | $(3.5 \pm 0.05)$ | $(1.4 \pm 0.1)$ | (4)    | $(0.2 \pm 0.1)$ | $(8 \pm 0.3)$ |

Note: UNLESS OTHERWISE SPECIFIED

- 1. CUMULATIVE PITCH TOLERANCE FOR FEEDING HOLES AND CAVITIES (CHIP POCKETS) NOT TO EXCEED .008 IN / 0.2mm OVER 10 PITCH SPAN.

- 2. THRU HOLE INSIDE CAVITY IS CENTERED WITHIN CAVITY.

- 3. SMALLEST ALLOWABLE TAPE BENDING RADIUS: 1.181 IN/

- 4. DIMENSIONS WITH  $\Delta$  ARE CRITICAL. DIMENSIONS TO BE ABSOLUTELY INSPECTED.

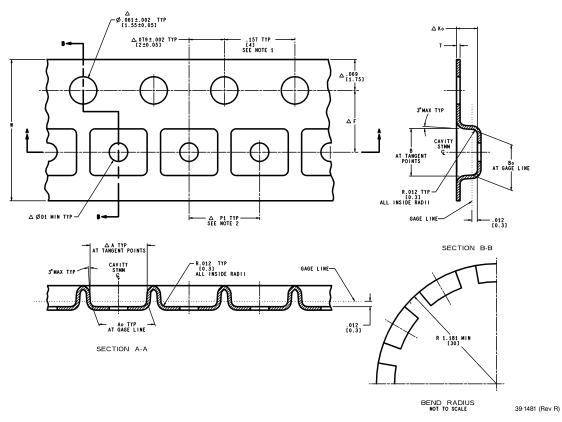

# **Reel Dimensions**

39-1922 (Rev H)

10132554

| TAPE<br>SIZE | DIM A   | DIM B | DIM C           | DIM D  | DIM N | DIM W1          | DIM W2 | DIM W3<br>(LSL-USL) |

|--------------|---------|-------|-----------------|--------|-------|-----------------|--------|---------------------|

| 8 mm         | 7.00    | .059  | .512 + .020/008 | .795   | 2.165 | .331 + .059/000 | .567   | .311429             |

|              | (177.8) | (1.5) | (13 +0.5/-0.2)  | (20.2) | (55)  | (8.4 + 1.5/0)   | (14.4) | (7.9 - 10.9)        |

Note: UNLESS OTHERWISE SPECIFIED

- 1. MATERIAL:

- POLYSTYRENE/PVC (WITH ANTISTATIC COATING).

- OR POLYSTYRENE/PVC, ANTISTATIC

- OR POLYSTYRENE/PVC, CONDUCTIVE.

- 2. CONTROLLING DIMENSION IS MILLIMETER, DIMENSIONS IN INCHES ROUNDED.

- 3. SURFACE RESISTIVITY:  $10^{10}$  OHM/SQ MAXIMUM.

- 4. ALL OUTPUT REELS SHALL BE UNIFORM IN SHADE.

- 5. PACKING OF REELS IN CONTAINERS MUST ENSURE NO DAMAGE TO THE REEL.

- 6. SURFACE FINISH OF THE FLANGES SHALL BE SMOOTH, MATTE FINISH PREFERRED.

- 7. ALL EDGES, ESPECIALLY THE TAPE ENTRY EDGES, MUST BE FREE OF BURRS.

- 8. THE REEL SHOULD NOT WARP IN THE STORAGE TEMPERATURE OF  $67\,^{\circ}\mathrm{C}$  MAXIMUM.

- 9. GLASS TRANSITION TEMPERATURE  $(T_g)$  OF THE PLASTIC REEL SHALL BE LOWER THAN  $-20\,^{\circ}\mathrm{C}.$

- 10. ALL GATING FROM THE MOLD MUST BE PROPERLY REMOVED.

- 11. NO FLASHES ARE TO BE PRESENT ALONG THE PARTING LINES.

- 12. ALLOWABLE RADIUS FOR CORNERS AND EDGES IS .012 INCHES/0.3 MILLIMETERS MINIMUM.

- 13. SINK MARKS THAT WILL CAUSE A CHANGE TO THE SPECIFIED DIMENSIONS OR SHAPE OF THE REELS ARE NOT ALLOWED.

- 14. MOLDED REELS SHALL BE FREE OF COSMETIC DEFECTS SUCH AS VOIDS. FLASHING, EXCESSIVE FLOW MARKS, ETC.

- 15. THERE MUST BE NO MISMATCH BETWEEN MATING PARTS.

- 16. MOLDED REELS SHALL BE ANTISTATIC COATED OR BLENDED.

- 17. THE SOT23-5L AND SOT23-6L PACKAGE USE THE 7-INCH REEL.

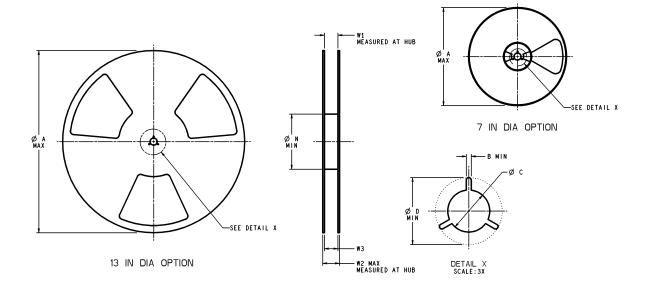

# **Physical Dimensions** inches (millimeters) unless otherwise noted .115±.003 -.075 [1.91] В .112±.006 [2.84±0.15] LAND PATTERN RECOMMENDATION R.004 MIN TYP R.004 MIN TYP [0.1] .0060\*:0015 [0.152\*0:038] Ç \_\_\_\_\_.004 [0.1]C (.025) [0.635] .014-.022 [0.36-0.55] TYP CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS MF05A (Rev B) SOT23-5 NS Package Number MF05A - .115±.003 - [2.92±0.07] В .112±.006 [2.84±0.15] .063±.003 [1.6±0.07] RECOMMENDED LAND PATTERN R.004 MIN TYP R.004 MIN TYP .0060<sup>+</sup>:0015 [0.152<sup>+0.038</sup>] △ .004 [0.1] C 6X .01701.0025 [ 0.43210.053 ] ( 0.08 [ 0.21@ | C AS | BS (.025 TYP) .014-.022 TYP [0.36-0.55] CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS MF06A (Rev B) SOT23-6 NS Package Number MF06A

# **Notes**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor

Asia Pacific Customer

Support Center

Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560