# CLC115QML Quad, Closed-Loop Monolithic Buffer

### **General Description**

The CLC115 is a high performance, closed-loop quad buffer designed for high density applications requiring a low-cost-per-channel solution to buffering high-frequency signals. The CLC115's high performance includes a  $700 \text{MH}_Z$  small signal bandwidth  $(0.5 \text{V}_{PP})$  and a  $2700 \text{V}/\mu \text{s}$  slew rate while requiring only 11mA quiescent current per channel. Signal fidelity is maintained with low harmonic distortion (-62dBc 2nd and 3rd harmonics at  $20 \text{MH}_Z$ ), and channel separation (60dB crosstalk at  $10 \text{MH}_Z$ ).

Featuring a unique closed-loop design, the CLC115 offers true unity-gain stability and very low output impedance plus a 60mA per channel output drive capability. The CLC115 is ideally suited for buffering video signals with its 0.08%/0.04° differential gain and phase performance at 3.58MHz. Applications such as analog multiplexing and high-speed A/D converters will benefit from the CLC115's high signal fidelity.

The CLC115 offers a low-cost-per-channel solution to high-speed buffering with four high-performance, closed-loop buffers integrated in one 14-pin package.

Constructed using an advanced, complementary bipolar process and Comlinear's proven current feedback architectures.

#### **Features**

- Closed-loop quad buffer

- 700MH<sub>Z</sub> small-signal bandwidth

- 2700V/µs slew rate

- 0.08%/0.04° differential gain/phase

- 60dB channel isolation (10MH<sub>7</sub>)

- -62dBc 2nd and 3rd harmonics at 20MH<sub>2</sub>

- 60mA current output per channel

### **Applications**

- Multi-channel video distribution

- Video switching buffers

- High-speed analog multplexing

- Channelized EW

- High-density buffering

- Instrumentation amps

- Active filters

### **Ordering Information**

| NS PART NUMBER | SMD PART NUMBER | NS PACKAGE NUMBER | PACKAGE DISCRIPTION |

|----------------|-----------------|-------------------|---------------------|

| CLC115AJ-QML   |                 | J14A              | 14LD CERDIP         |

# **Absolute Maximum Ratings** (Note 1)

Supply Voltage  $\pm 7 V_{DC}$ Output Current  $\pm 96 mA$

Thermal Resistance (Note 2)

Thermal Resistance (Note 2)  $\theta_{JA} \qquad \qquad 75^{\circ}\text{C/W}$   $\theta_{JC} \qquad \qquad 28^{\circ}\text{C/W}$  Junction Temperature  $\qquad \qquad +175^{\circ}\text{C}$  Operating Temperature  $\qquad \qquad -55^{\circ}\text{C} \leq \text{T}_{A} \leq +125^{\circ}\text{C}$  Storage Temperature  $\qquad \qquad -65^{\circ}\text{C} \leq \text{T}_{A} \leq +150^{\circ}\text{C}$  Lead Temperature (Soldering 10 seconds)  $\qquad \qquad +300^{\circ}\text{C}$

## **Recommended Operating Conditions**

Supply Voltage  $\pm 5 V_{DC}$ Ambient Temperature Range  $-55^{\circ}C$  to  $+125^{\circ}C$

# **Quality Conformance Inspection**

MIL-STD-883, Method 5005 - Group A

| Subgroup | Description         | Temp ( C) |

|----------|---------------------|-----------|

| 1        | Static tests at     | +25       |

| 2        | Static tests at     | +125      |

| 3        | Static tests at     | -55       |

| 4        | Dynamic tests at    | +25       |

| 5        | Dynamic tests at    | +125      |

| 6        | Dynamic tests at    | -55       |

| 7        | Functional tests at | +25       |

| 8A       | Functional tests at | +125      |

| 8B       | Functional tests at | -55       |

| 9        | Switching tests at  | +25       |

| 10       | Switching tests at  | +125      |

| 11       | Switching tests at  | -55       |

### **CLC115 Electrical Characteristics**

#### **DC Parameters**

(The following conditions apply, unless otherwise specified.)  $R_{LOAD} = 100W$ ,  $V_{CC} = \pm 5V$ ,  $-55^{\circ}C < T_{A} < =125^{\circ}C$

|                 |                              |            |       |      |      |      | SUB-    |

|-----------------|------------------------------|------------|-------|------|------|------|---------|

| SYMBOL          | PARAMETER                    | CONDITIONS | NOTES | MIN  | MAX  | UNIT | GROUPS  |

|                 | Input Bias Current           |            |       | -20  | 20   | μΑ   | 1, 2    |

| I <sub>BN</sub> | Non-inverting                |            |       | -35  | 35   | μΑ   | 3       |

| V <sub>os</sub> | Output Offset Voltage        |            |       | -9.0 | 9.0  | mV   | 1, 2    |

|                 |                              |            |       | -17  | 17   | mV   | 3       |

| I <sub>CC</sub> | Supply Current               |            |       |      | 61.0 | mA   | 1, 2, 3 |

| PSRR            | Power Supply Rejection Ratio |            |       | 48   |      | dB   | 1       |

|                 |                              |            |       | 46   |      | dB   | 2       |

|                 |                              |            |       | 44   |      | dB   | 3       |

#### **CLC115 Electrical Characteristics**

#### **AC Parameters**

(The following conditions apply, unless otherwise specified.)  $R_{LOAD} = 100W$ ,  $V_{CC} = \pm 5V$ ,  $-55^{\circ}C < T_{A} < =125^{\circ}C$

| SYMBOL          | PARAMETER                           | CONDITIONS                            | NOTES | MIN  | MAX  | UNIT            | SUB-<br>GROUPS |

|-----------------|-------------------------------------|---------------------------------------|-------|------|------|-----------------|----------------|

|                 | T ATAMETER                          | CONDITIONS                            | HOTEG |      | 1.15 | dB              | 4, 5           |

| GFPH            | Gain Flatness Peaking               | 30 to 200MH <sub>Z</sub>              |       |      | 1.4  | dB              | 6              |

| GFR             | Gain Flatness Rolloff               | 30 to 200MH <sub>Z</sub>              |       | -0.5 |      | dB              | 4, 5, 6        |

| HD <sub>2</sub> | 2 <sub>ND</sub> Harmonic Distortion | 2V <sub>PP</sub> at 20MH <sub>Z</sub> |       |      | -47  | dB <sub>C</sub> | 4, 5           |

|                 |                                     |                                       |       |      | -45  | dB <sub>C</sub> | 6              |

| HD <sub>3</sub> | 3 <sub>RD</sub> Harmonic Distortion | 2V <sub>PP</sub> at 20MH <sub>Z</sub> |       |      | -53  | dB <sub>C</sub> | 4, 6           |

|                 |                                     |                                       |       |      | -50  | dB <sub>C</sub> | 5              |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limit s. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions

Note 2: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower.

# **Revision History Section**

| Date<br>Released | Revision  | Section                         | Originator | Changes                         |

|------------------|-----------|---------------------------------|------------|---------------------------------|

| Heleasea         | TICVISION | occion                          | Originator | Onlanges                        |

| 7/01/05          | Α         | New Data Sheet, Initial Release | R. Malone  | New Data Sheet, Initial Release |

www.national.com 4

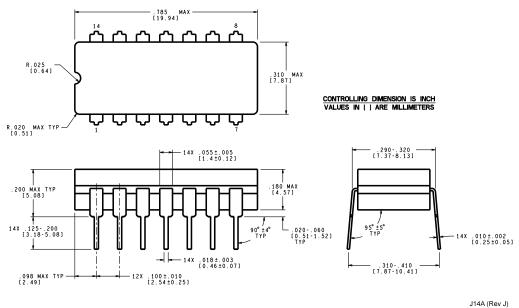

# Physical Dimensions inches (millimeters) unless otherwise noted

Ceramic Dual-In-Line Package (J) NS Package Number J14A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560