# National Semiconductor

# **CLC430 General Purpose 100MHz Op Amp with Disable**

# **General Description**

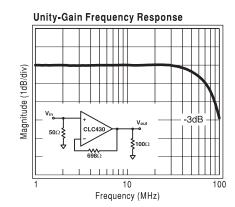

The CLC430 is a low-cost, wideband monolithic amplifier for general purpose applications. The CLC430 utilizes National's patented current feedback circuit topology to provide an op amp with a slew rate of  $2000\text{V}/\mu\text{s}$ , 100MHz unity-gain bandwidth and fast output disable function. Like all current feedback op amps, the CLC430 allows the frequency response to be optimized (or adjusted) by the selection of the feedback resistor. For demanding video applications, the 0.1dB bandwidth to 20MHz and differential gain/phase of 0.03%/0.05° make the CLC430 the preferred component for broadcast quality NTSC and PAL video systems.

The large voltage swing  $(28V_{pp})$ , continuous output current (85mA) and slew rate  $(2000\text{V}/\mu\text{s})$  provide high-fidelity signal conditioning for applications such as CCDs, transmission lines and low impedance circuits. Even driving loads of  $100\Omega$ , the CLC430 provides very low 2nd and 3rd harmonic distortion at 1MHz (-76/-82dBc).

Video distribution, multimedia and general purpose applications will benefit from the CLC430's wide bandwidth and disable feature. Power is reduced and the output becomes a high impedance when disabled. The wide gain range of the CLC430 makes this general purpose op amp an improved solution for circuits such as active filters, differential-to-single-ended drivers, DAC transimpedance amplifiers and MOSFET drivers.

#### **Features**

- 0.1dB gain flatness to 20MHz  $(A_v=+2)$

- 100MHz bandwidth  $(A_v=+1)$

- 2000V/us slew rate

- 0.03%/0.05° differential gain/phase

- ±5V, ±15V or single supplies

- 100ns disable to high-impedance output

- Wide gain range

- Low cost

# **Applications**

- Video distribution

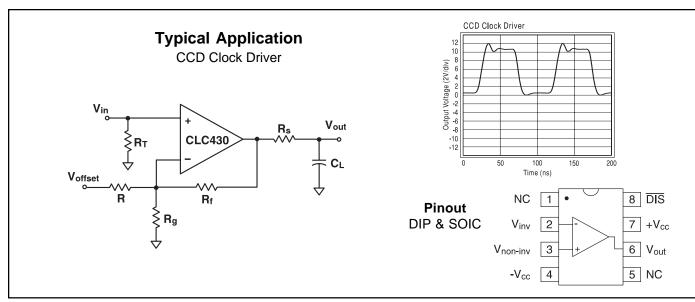

- CCD clock driver

- Multimedia systems

- DAC output buffers

- Imaging systems

# CLC430 Electrical Characteristics ( $V_{cc} = \pm 15V$ ; $A_v = +2V/V$ ; $R_f = 604\Omega$ ; $R_L = 100\Omega$ ; unless noted)

| PARAMETERS                                                                                                                                                                                         | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>cc</sub>                             | TYP                                                           | TYP MIN/MAX RATINGS                                  |                                                             | UNITS                                                          | NOTES                                                             |             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|-------------|

| Ambient Temperature                                                                                                                                                                                | CLC430                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                             | 25°C                                                          | 25°C                                                 | 0 to 70°C                                                   | -40 to 85°C                                                    |                                                                   |             |

| FREQUENCY DOMAIN RESI<br>unity-gain bandwidth<br>small-signal bandwidth<br>0.1dB bandwidth<br>large-signal bandwidth                                                                               | $\begin{aligned} &\text{PONSE} \\ &V_{\text{out}} < 1.0 V_{\text{pp}} \\ &V_{\text{out}} = 10 V_{\text{pp}} \end{aligned}$                                                                                                                            | ±15<br>±15<br>±5<br>±15<br>±5               | 100<br>75<br>55<br>20<br>16<br>30                             | 50<br>35<br>7                                        | 45<br>20                                                    | 42<br>19                                                       | MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz                     |             |

| gain flatness peaking rolloff linear phase deviation differential gain differential phase                                                                                                          | $\begin{array}{l} \text{V}_{\text{out}} < 1.0 \text{V}_{\text{pp}} \\ \text{DC to } 10 \text{MHz} \\ \text{DC to } 20 \text{MHz} \\ \text{DC to } 20 \text{MHz} \\ \text{4.43MHz}, \text{ R}_{\text{L}} = 150 \Omega \\ \end{array}$ |                                             | 0.0<br>0.1<br>0.5<br>0.03<br>0.03<br>0.05<br>0.09             | 0.1<br>0.7<br>1.8<br>0.05<br>0.05<br>0.09<br>0.19    | 0.2<br>1.0<br>2.0<br>0.06                                   | 0.2<br>1.2<br>2.1<br>0.06                                      | dB<br>dB<br>%<br>%                                                |             |

| rise and fall time settling time to 0.05% overshoot slew rate                                                                                                                                      | 2V step<br>10V step<br>2V step<br>2V step<br>20V step                                                                                                                                                                                                                                                                                                                                                                                                    |                                             | 5<br>10<br>35<br>5<br>2000                                    | 7<br>14<br>50<br>15<br>1500                          | 7<br>14<br>55<br>15<br>1450                                 | 7<br>14<br>55<br>15<br>1450                                    | ns<br>ns<br>ns<br>%<br>V/µs                                       |             |

| DISTORTION AND NOISE RE<br>2 <sup>nd</sup> harmonic distortion<br>3 <sup>rd</sup> harmonic distortion<br>input voltage noise<br>non-inverting input current noise<br>inverting input current noise | $1V_{pp}$ , 1MHz, $R_L$ =500<br>$1V_{pp}$ , 1MHz, $R_L$ =500<br>>1MHz<br>>>1MHz                                                                                                                                                                                                                                                                                                                                                                          |                                             | -89<br>-92<br>3.0<br>3.2<br>15                                | 3.5<br>6.0<br>18                                     | 3.7<br>6.3<br>20                                            | 3.8<br>6.8<br>21                                               | dBc<br>dBc<br>nV/√Hz<br>pA/√Hz<br>pA/√Hz                          |             |

| input offset voltage average drift input bias current input bias current average drift power-supply rejection ratio common-mode rejection ratio supply current disabled                            | non-inverting average drift inverting DC DC $R_L = \infty$ $R_L = \infty$                                                                                                                                                                                                                                                                                                                                                                                | ±15<br>±15,±5<br>±15,±5<br>±15,±5<br>±15,±5 | 1.0<br>25<br>3<br>10<br>3<br>10<br>62<br>62<br>11, 8.5<br>1.5 | 7.5<br><br>14<br><br>14<br><br>56<br>54<br>12<br>2.0 | 9.0<br>50<br>16<br>100<br>15<br>60<br>54<br>53<br>13<br>2.2 | 10.0<br>50<br>20<br>100<br>17<br>90<br>53<br>52<br>14.5<br>2.4 | mV<br>μV/ C<br>μA<br>nA/°C<br>μA<br>nA/°C<br>dB<br>dB<br>mA<br>mA | A<br>A<br>A |

| SWITCHING PERFORMANC turn on time turn off time off isolation high input voltage low input voltage                                                                                                 | (Note 2)<br>10MHz<br>V <sub>IH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                     | ±15<br>±5<br>±15<br>±5                      | 200<br>100<br>59<br>11.8<br>1.8<br>10.8                       | 300<br>200<br>56<br>12.5<br>2.5<br>10.5<br>0.6       | 320<br>200<br>56<br>12.7<br>2.7<br>10.0<br>0.1              | 340<br>200<br>56                                               | ns<br>ns<br>dB<br>>>                                              |             |

| MISCELLANEOUS PERFOR Non-inverting input resistance Non-inverting input capacitan input voltage range                                                                                              | e<br>nce<br>common mode<br>common mode                                                                                                                                                                                                                                                                                                                                                                                                                   | ±15<br>±5                                   | 8.0<br>0.5<br>±12.5<br>±2.5                                   | 3.0<br>1.0<br>±12.3<br>±2.3                          | 2.5<br>1.0<br>±12.1<br>±2.2                                 | 1.7<br>1.0<br>±11.8<br>±1.9                                    | MΩ<br>pF<br>V                                                     |             |

| output voltage range output current                                                                                                                                                                | $R_L = \infty$<br>$R_L = \infty$                                                                                                                                                                                                                                                                                                                                                                                                                         | ±15<br>±5                                   | ±14<br>±4.0<br>±85                                            | ±13.7<br>±3.9<br>±60                                 | ±13.7<br>±3.8<br>±50                                        | ±13.6<br>±3.7<br>±45                                           | V<br>V<br>mA                                                      |             |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# Absolute Maximum Ratings

supply voltage  $\pm 16.5 \text{V}$ short circuit current  $\pm 10.5 \text{V}$ common-mode input voltage  $\pm \text{V}_{cc}$ maximum junction temperature  $\pm 150 ^{\circ}\text{C}$ storage temperature  $\pm 150 ^{\circ}\text{C}$ lead temperature (soldering 10 sec)  $\pm 300 ^{\circ}\text{C}$ ESD rating (human body model)  $\pm 4000 ^{\circ}\text{V}$

## **Notes**

A)J-level: spec is 100% tested at +25°C.

1) Output is short circuit protected to ground, however maximum reliability is obtained if output current does not exceed 125mA.

2) To>50dB attenuation @ 10MHz.

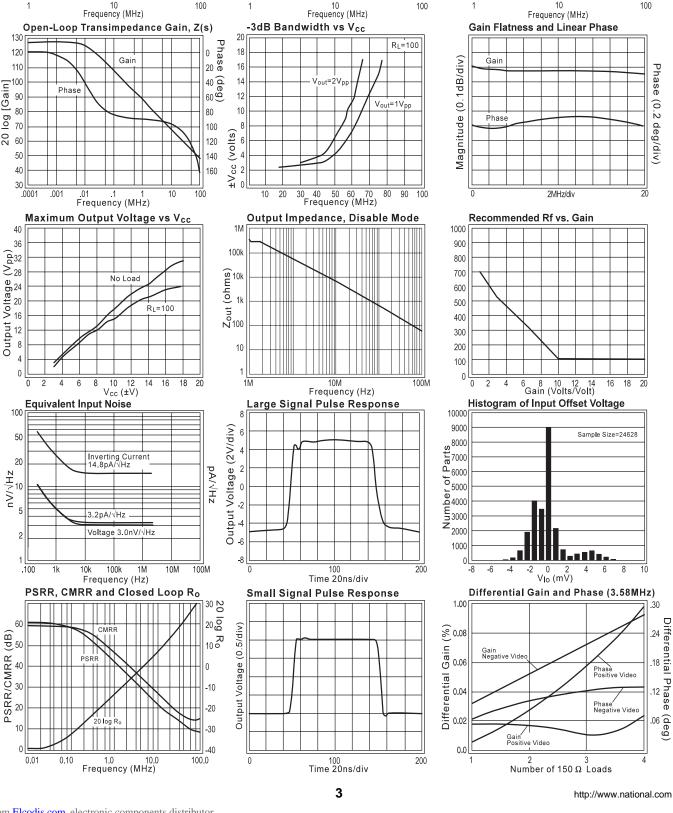

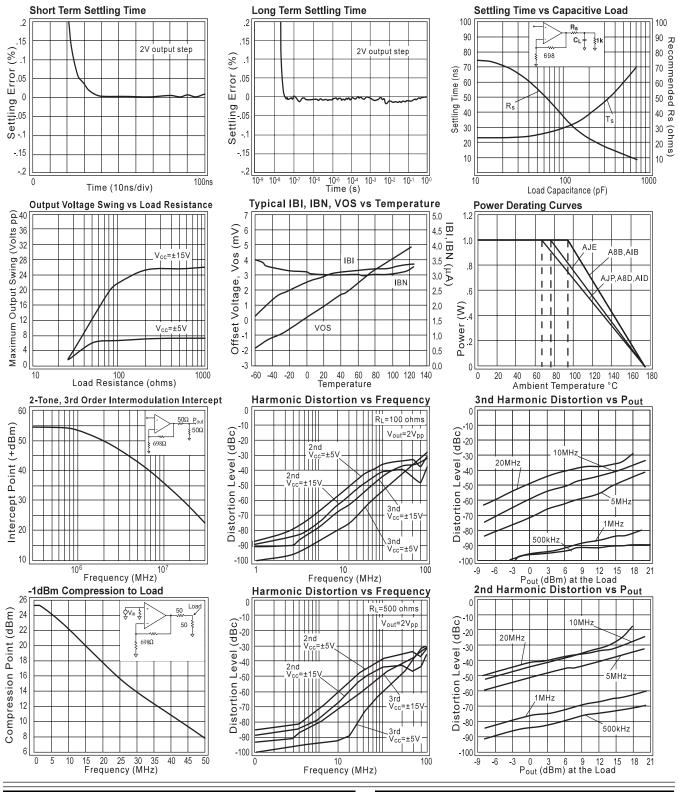

#### CLC430 Typical Performance ( $V_{cc} = \pm 15V$ ; $A_V = +2V/V$ ; $R_f = 604\Omega$ ; $R_L = 100\Omega$ ; unless noted) Non-Inverting Frequency Response **Inverting Frequency Response** Frequency Response vs Load Phase (deg) R<sub>f</sub>=698 Gain Gain Magnitude (1dB/div) Magnitude (1dB/div) RL=50= (deg) RL=10 Magnitude (1dB/ Phase Phase Phase 0 -90 -135 180 10 Frequency (MHz) 100 10 Frequency (MHz) 10 100 Frequency (MHz) -3dB Bandwidth vs Vcc Open-Loop Transimpedance Gain, Z(s) Gain Flatness and Linear Phase Phase ( R<sub>L</sub>=100 120 18 Gain Ġair Magnitude (0.1dB/div) 110 16 Phase log [Gain] 40 (deg) 60 (deg) 14 Phase 12 (0.2 80 10 100 deg/div) ±V<sub>CC</sub> (volts) 20 60 120 50 140 40 30 .01 .1 1 Frequency (MHz) 30 40 50 60 70 Frequency (MHz) .001 100 2MHz/div 20 .0001 Output Impedance, Disable Mode Maximum Output Voltage vs Vcc Recommended Rf vs. Gain 1000 40 36 900 100k Output Voltage (Vpp) 800 Zout (ohms) 700 No Load 500 R<sub>L</sub>=100 400 300 10 200 100 10 12 V<sub>cc</sub> (±V) 14 16 6 8 10 12 14 Gain (Volts/Volt) Frequency (Hz) Equivalent Input Noise Histogram of Input Offset Voltage Large Signal Pulse Response 100 10000 9000 Output Voltage (2V/div) Sample Size=24628 50 Parts 7000 6000 Inverting Current 14.8pA/√Hz 20 5<sub>5000</sub> 0 N 2000 -2 .2pA/√Hz Voltage 3.0nV/√Hz -6 1000

# $\textbf{CLC430 Typical Performance} \ \ (\textit{V}_{\text{CC}} = \pm 15 \textit{V}; \ \, \textit{A}_{\textit{V}} = +2 \textit{V/V}; \ \, \textit{R}_{\textit{f}} = 604 \Omega \ \, ; \ \, \textit{R}_{\textit{L}} = 100 \Omega \ \, ; \ \, \textit{unless noted})$

| Ordering Information   |                                   |                                         |  |

|------------------------|-----------------------------------|-----------------------------------------|--|

| Model                  | Temperature Range                 | Description                             |  |

| CLC430AJP              | -40°C to +85°C                    | 8-pin PDIP                              |  |

| CLC430AJE<br>CLC430A8B | -40°C to +85°C<br>-55°C to +125°C | 8-pin SOIC<br>8-pin CERDIP, MIL-STD-883 |  |

DESC SMD number: 5962-92030.

| Package Thermal Resistance |               |               |  |

|----------------------------|---------------|---------------|--|

| Package                    | $\theta_{JC}$ | $\theta_{JA}$ |  |

| AJP                        | 60°C/W        | 115°C/W       |  |

| AJE                        | 55°C/W        | 135°C/W       |  |

| A8B                        | 30°C/W        | 120°C/W       |  |

| Reliability Information |    |

|-------------------------|----|

| Transistor count        | 38 |

#### **General Design Considerations**

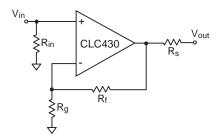

The CLC430 is a general purpose current-feedback amplifier for use in a variety of small- and large-signal applications. Use the feedback resistor to fine tune the gain flatness and -3dB bandwidth for any gain setting. Comlinear provides information for the performance at a gain of +2 for small and large signal bandwidths. The plots show feedback resistor values for selected gains.

#### Gain

Use the following equations to set the CLC430's non-inverting or inverting gain:

Non-Inverting Gain =

$$1 + \frac{R_f}{R_g}$$

Inverting Gain =  $-\frac{R_f}{R_g}$

Choose the resistor values for non-inverting or inverting gain by the following steps.

Fig. 0 Component Identification

- 1) Select the recommended feedback resistor  $R_f$  (refer to plot in the plot section entitled  $R_f$  vs Gain).

- Choose the value of R<sub>g</sub> to set gain.

- 3) Select R<sub>s</sub> to set the circuit output impedance.

- 4) Select R<sub>in</sub> for input impedance and input bias.

## **High Gains**

Current feedback closed-loop bandwidth is independent of gain-bandwidth-product for small gain changes. For larger gain changes the optimum feedback register  $R_f$  is derived by the following:

$$R_f = 724\Omega - 60\Omega \cdot (A_v)$$

As gain is increased, the feedback resistor allows bandwidth to be held constant over a wide gain range. For a more complete explanation refer to application note OA-25 Stability Analysis of Current-Feedback Amplifiers.

Resistors have varying parasitics that affect circuit performance in high-speed design. For best results, use leaded metal-film resistors or surface mount resistors. A SPICE model for the CLC430 is available to simulate overall circuit performance.

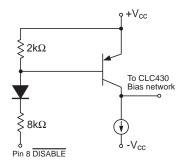

#### **Enable / Disable Function**

The CLC430 amplifier features an enable/disable function that changes the output and inverting input from low to high impedance. The pin 8 enable/disable logic levels are as

follows:

| $V_{cc}$ | ±15V   | ±5V   |

|----------|--------|-------|

| Enable   | >12.7V | >2.7V |

| Disable  | <10.0V | <0.8V |

The amplifier is enabled with pin 8 left open due to the  $2k\Omega$  pull-up resistor, shown in Fig. 1.

Fig. 1 Pin 8 Equivalent Disable Circuit

Open-collector or CMOS interfaces are recommended to drive pin 8. The turn-on and off time depends on the speed of the digital interface.

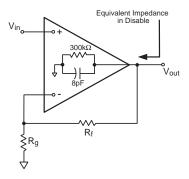

The equivalent output impedance when disabled is shown in Fig. 2. With  $R_g$  connected to ground, the sum of  $R_f$  and  $R_g$  dominates and reduces the disabled output impedance. To raise the output impedance in the disabled state, connect the CLC430 as a unity-gain voltage follower by removing  $R_g$ . Current-feedback op-amps need the recommended  $R_f$  in a unity-gain follower circuit. For high density circuit layouts consider using the dual CLC431 (with disable) or the dual CLC432 (without disable).

Fig. 2 Equivalent Disabled Output Impedance

## 2<sup>nd</sup> and 3<sup>rd</sup> Harmonic Distortion

To meet low distortion requirements, recognize the effect of the feedback resistor. Increasing the feedback resistor will decrease the loop gain and increase distortion. Decreasing the load impedance increases 3<sup>rd</sup> harmonic distortion more than 2<sup>nd</sup>.

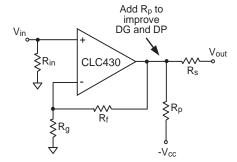

#### **Differential Gain and Differential Phase**

The CLC430 has low DG and DP errors for video applications. Add an external pulldown resistor to the CLC430's output to improve DG and DP as seen in Fig.3. A  $604\Omega\,R_P$  will improve DG and DP to 0.01% and 0.02°.

Fig. 3 Improved DG and DP Video Amplifier

## **Printed Circuit Layout**

To get the best amplifier performance careful placement of the amplifier, components and printed circuit traces must be observed. Place the  $0.1\mu F$  ceramic decoupling capacitors less than 0.1" (3mm) from the power supply pins. Place the  $6.8\mu F$  tantalum capacitors less than 0.75" (20mm) from the power supply pins. Shorten traces between the inverting pin and components to less than 0.25" (6mm). Clear ground plane 0.1" (3mm) away from pads and traces that connect to the inverting, non-inverting and output pins. Do not place ground or power plane beneath the op-amp package. Comlinear provides literature and evaluation boards 730013 DIP or 730027 SOIC illustrating the recommended op-amp layout.

### **Applications Circuits**

### **Level Shifting**

The circuit shown in Fig. 4 implements level shifting by AC coupling the input signal and summing a DC voltage. The resistor  $R_{in}$  and the capacitor C set the high-pass break frequency. The amplifier closed-loop bandwidth is fixed by the selection of  $R_{f}$ . The DC and AC gains for circuit of Fig. 4 are different. The AC gain is set by the ratio of  $R_{f}$  and  $R_{g}$ . And the DC gain is set by the parallel combination of  $R_{g}$  and  $R_{g}$ .

$$V_{out} = V_{in_{ac}} \left( 1 + \left( \frac{R_f}{R_g || R_2} \right) \right) - V_{in_{DC}} \left( \frac{R_f}{R_2} \right)$$

$$V_{in_{DC}} \stackrel{\bullet}{\sim} \frac{1}{R_2} \stackrel{\bullet}{\sim} \frac{1}{R_f} \stackrel{\bullet}{\sim} \frac{1}{R_$$

Fig. 4 Level Shifting Circuit

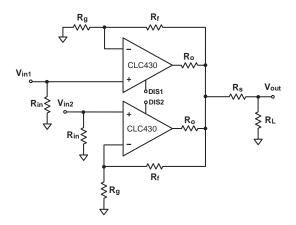

#### Multiplexing

Multiple signal switching is easily handled with the disable function of the CLC430. Board trace capacitance at the output pin will affect the frequency response and switching transients. To lessen the effects of output capacitance place a resistor ( $R_0$ ) within the feedback loop to isolate the

outputs as shown in Fig. 5. To match the mux output impedance to a transmission line, add a resistor ( $R_s$ ) in series with the output.

Fig. 5 Output Connection

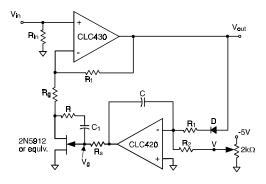

#### **Automatic Gain Control**

Current-feedback amplifiers can implement very fast automatic-gain control circuits. The circuit shown in Fig. 6 shows an AGC circuit using the CLC430, a half-wave rectifier, an integrator and a FET. The CLC430 current-feedback amplifier maintains constant bandwidth and linear phase over AGC's gain range. This circuit effectively controls the output level for continuous signals.

Fig. 6 AGC Circuit

The bandwidth of the CLC430 AGC is limited by  $\rm R_{\rm f}$  , the feedback resistor. The FET gate voltage is limited to a range of:

$$-2.5 < V_g < -1$$

R of  $750\Omega$  and C1 of  $1.0\mu F$  gives a useful  $R_{ds}$  range of approximately 150 to 2K ohms. Scaling the integrator gain or adding attenuation before the diode D accommodates large signal swings. Determine the overall gain by:

$$1 + \frac{R_f}{R_a + R_{ds}}$$

The integrator sets the loop time constant.

This page intentionally left blank.

#### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### **Life Support Policy**

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# National Semiconductor Corporation

1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

# National Semiconductor Hong Kong Ltd.

2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600

Fax: (852) 2736-9960

### National Semiconductor Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.