# CLC406 Wideband, Low Power Monolithic Op Amp

## **General Description**

The CLC406 is a wideband monolithic operational amplifier designed for low-gain applications where power and cost are of primary concern. Operating from  $\pm5V$  supplies, the CLC406 consumes only 50mW of power yet maintains a 160MHz small signal bandwidth and a 1500V/ $\mu s$  slew rate. Benefitting from National's current feedback architecture, the CLC406 offers a gain range of  $\pm1$  to  $\pm10$  while providing stable, oscillation free operation without external compensation, even at unity gain.

With its exceptional differential gain and phase, typically 0.02% and 0.02° at 3.58MHz, the CLC406 is designed to meet the performance and cost requirements of high volume composite video applications. The CLC406's large signal bandwidth, high slew rate and high drive capability are features well suited for RGB video applications.

Providing a 12ns settling time to 0.05% (1/2 LSB in 10-bit systems) and -68/-75 dBc 2nd/3rd harmonic distortion (2V $_{pp}$  at 10MHz,  $R_{L}\!=\!1k\Omega)$ , the CLC406 is an excellent choice as a buffer or driver for high speed A/D and D/A converter systems.

Commercial remote sensing applications and battery powered radio transceivers requiring a high performance, low power amplifier will find the CLC406 to be an attractive, cost-effective solution.

Constructed using an advanced, complementary bipolar process and National's proven current feedback architectures, the CLC406 is available in several versions to meet a variety of requirements.

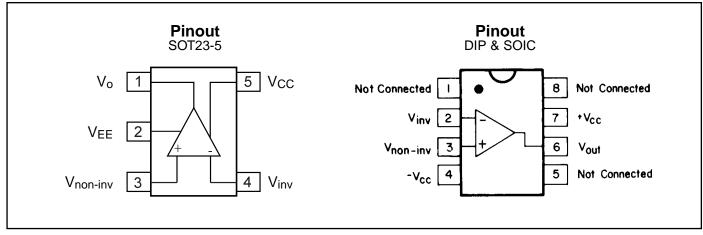

CLC406AJP -40°C to +85°C 8-pin plastic DIP CLC406AJE -40°C to +85°C 8-pin plastic SOIC CLC406AJM5 -40°C to +85°C 5-pin SOT

### **Features**

- 160MHz small signal bandwidth

- 50mW power (±5Vsupplies)

- 0.02%/0.02° differential gain/phase

- 12ns settling to 0.05%

- 1500V/us slew rate

- 2.2ns rise and fall time (2V<sub>pp</sub>)

- 70mA output current

## **Applications**

- Video distribution amp

- HDTV amplifier

- Flash A/D driver

- D/A transimpedance buffer

- Pulse amplifier

- Photodiode amp

- LAN amplifier

# CLC406 Electrical Characteristics (A $_{v}$ = +6, V $_{cc}$ = ±5V, R $_{L}$ = 100 $\Omega$ , R $_{f}$ = 500 $\Omega$ ; unless specified)

| PARAMETERS                                                                                                                                                           | CONDITIONS                                                                                                                                                                                                                        | TYP                                              | MAX & MIN RATINGS                                              |                                                         | UNITS                                                        | SYMBOL                                                                                                                                                          |                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Ambient Temperature                                                                                                                                                  | CLC406AJ                                                                                                                                                                                                                          | +25°C                                            | −40°C                                                          | +25℃                                                    | + 85°C                                                       |                                                                                                                                                                 |                                                                  |

| FREQUENCY DOMAIN  - 3db bandwidth  gain flatness                                                                                                                     | $\begin{array}{c} \textbf{PERFORMANCE} \\ V_{out} < 2V_{pp} \\ V_{out} < 5V_{pp} \\ V_{out} < 2V_{pp} \\ DC to 25MHz \end{array}$                                                                                                 | 160<br>130                                       | >110<br>>95                                                    | >110<br>>95                                             | >90<br>>80                                                   | MHz<br>MHz                                                                                                                                                      | SSBW<br>LSBW                                                     |

| peaking peaking rolloff linear phase deviation differential gain differential phase                                                                                  | DC to $25 \text{MHz}$<br>> 25 MHz<br>DC to $50 \text{MHz}$<br>DC to $75 \text{MHz}$<br>(A <sub>V</sub> = +2) $150 \Omega \log d$ , $3.58 \text{MHz}$<br>4.43 MHz<br>(A <sub>V</sub> = +2) $150 \Omega \log d$ , $3.58 \text{MHz}$ | 0<br>0<br>0<br>0.2<br>0.02<br>0.02<br>0.02       | <0.2<br><0.5<br><0.6<br><0.8<br><0.04<br><0.04<br><0.04        | <0.2<br><0.5<br><0.6<br><0.8<br><0.04<br><0.04<br><0.04 | <0.2<br><0.5<br><1.0<br><1.2<br><0.04<br><0.04<br><0.08      | dB<br>dB<br>dB<br>%                                                                                                                                             | GFPL<br>GFPH<br>GFR<br>LPD<br>DG1<br>DG2<br>DP1                  |

| •                                                                                                                                                                    | 4.43MHz                                                                                                                                                                                                                           | 0.025                                            | < 0.05                                                         | < 0.05                                                  | <0.10                                                        | 0                                                                                                                                                               | DP2                                                              |

| rise and fall time settling time to 0.05% overshoot slew rate                                                                                                        | 2V step<br>4V step<br>2Vstep<br>2V step                                                                                                                                                                                           | 2.2<br>3.0<br>12<br>8<br>1500                    | <3.0<br><3.6<br><18'<br><15<br>>1200                           | <3.0<br><3.6<br><18<br><15<br>>1200                     | <3.9<br><5.0<br><20<br><15<br>>1000                          | ns<br>ns<br>ns<br>%<br>V/μs                                                                                                                                     | TRS<br>TRL<br>TS<br>OS<br>SR                                     |

| 2nd harmonic distortion  3rd harmonic distortion                                                                                                                     | SE RESPONSE $2V_{pp},20MHz,R_L = 100\Omega$ $2V_{pp},10MHz,R_L = 1k\Omega$ $2V_{pp},20MHz,R_L = 100\Omega$ $2V_{pp},10MHz,R_L = 1k\Omega$                                                                                         | -46<br>-68<br>-50<br>-75                         | <-42<br><-62<br><-46<br><-70                                   | <-42<br><-62<br><-46<br><-70                            | <-38<br><-60<br><-42<br><-65                                 | dBc<br>dBc<br>dBc<br>dBc<br>dBc                                                                                                                                 | HD2<br>HD2L<br>HD3<br>HD3L                                       |

| equivalent input noise<br>non-inverting voltag<br>inverting current<br>non-inverting currei<br>total noise floor<br>total integrated nois                            | >1MHz<br>nt >1MHz<br>>1MHz                                                                                                                                                                                                        | 2.7<br>11.0<br>2.1<br>-157<br>31                 | 3.4<br>13.9<br>2.6<br><-156<br><38                             | 3.4<br>13.9<br>2.6<br><-156<br><38                      | 3.8<br>15.5<br>3.0<br>-155<br><42                            | $\begin{array}{c} \text{nV/}\sqrt{\text{Hz}} \\ \text{pA/}\sqrt{\text{Hz}} \\ \text{pA/}\sqrt{\text{Hz}} \\ \text{dBm}_{\text{1Hz}} \\ \mu\text{V} \end{array}$ | VN<br>ICN<br>NCN<br>SNF<br>INV                                   |

| STATIC, DC PERFORMANCE  *input offset voltage     average temperature coefficient  *input bias current                                                               |                                                                                                                                                                                                                                   | 2<br>30<br>5<br>30<br>3<br>20<br>50<br>50<br>5.0 | <10<br><60<br><24<br><125<br><23<br><100<br>>46<br>>45<br><7.0 | <6<br>-12<br>-15<br>-15<br>-46<br>>45<br><6.7           | <12<br><60<br><12<br><50<br><20<br><50<br>>44<br>>43<br><6.7 | mV<br>μV/°C<br>μΑ<br>nA/°C<br>μA<br>nA/°C<br>dB<br>dB<br>mA                                                                                                     | VIO<br>DVIO<br>IBN<br>DIBN<br>IBI<br>DIBI<br>PSRR<br>CMRR<br>ICC |

| MISCELLANEOUS PERI<br>non-inverting input resist<br>non-inverting input capac<br>output impedance<br>output voltage range<br>common mode input ran<br>output current | ance citance $DC$ $R_1 = 100\Omega$                                                                                                                                                                                               | 1000<br>1.0<br>0.2<br>+3.1, -2.7<br>± 2.2<br>70  | >300<br><2.0<br><0.6<br>+1.6, -2.5<br>± 1.4<br>30              | >500<br><2.0<br><0.3<br>±2.7<br>±2.0<br>50              | >500<br><2.0<br><0.2<br>±2.7<br>± 2.0<br>50                  | kΩ<br>pF<br>Ω<br>V<br>V<br>mA                                                                                                                                   | RIN<br>CIN<br>RO<br>VO<br>CMIR<br>IO                             |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# **Absolute Maximum Ratings**

# Miscellaneous Ratings

| V <sub>cc</sub>                                | ±7V               |

|------------------------------------------------|-------------------|

| lout output is short circuit protected to      |                   |

| ground, but maximum reliability will be        |                   |

| maintained if I <sub>out</sub> does not exceed | 70mA              |

| common mode input voltage                      | $\pm V_{cc}$      |

| differential input voltage                     | 10Ŭ               |

| junction temperature                           | + 150°C           |

| operating temperature range                    |                   |

| ĀJ:                                            | – 40°C to + 85°C  |

| storage temperature range                      | - 65°C to + 150°C |

| Lead solder duration (+ 300°C)                 | 10 sec            |

| EDS rating (human body model)                  | 2000V             |

| Reliability Ir | nformation |

|----------------|------------|

|----------------|------------|

Transistor count 34

recommended gain range:  $\pm 1$  to  $\pm 10$

NOTES:

AJ 100% tested at + 25°C,

# Package Thermal Resistance

| Package | $\theta_{JC}$ | $\theta_{JA}$ |

|---------|---------------|---------------|

| AJP     | 70°C/W        | 125°C/W       |

| AJE     | 65°C/W        | 145°C/W       |

| AJM5    | 130°C/W       | 150°C/W       |

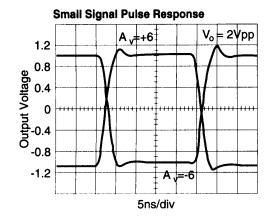

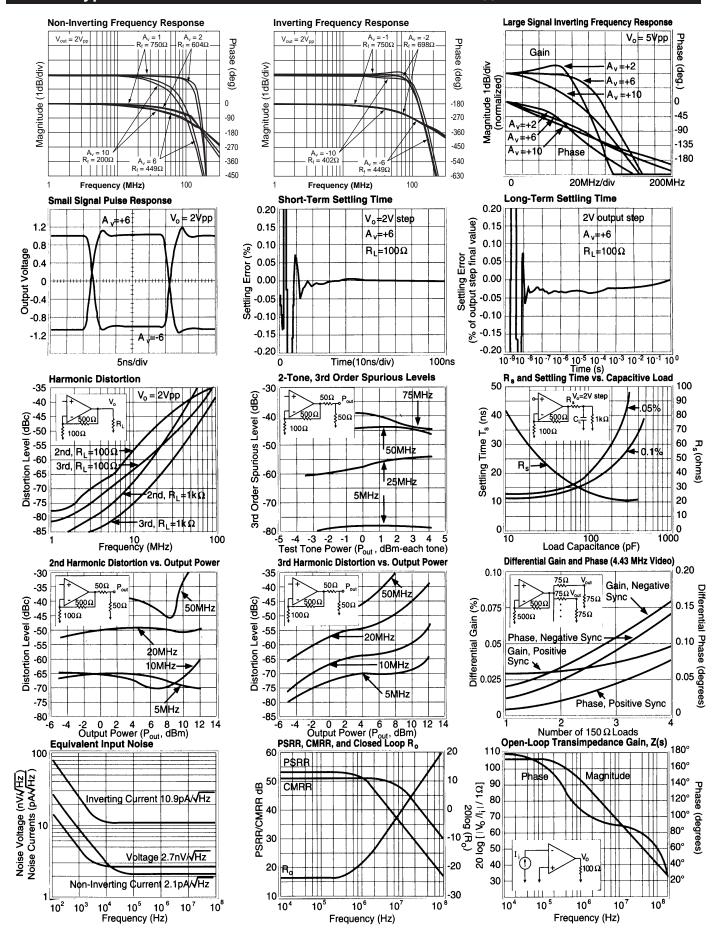

# CLC406 Typical Performance Characteristics ( $T_A = 25^{\circ}$ , $A_V = +6$ , $V_{CC} = \pm 5V$ , $R_L = 100\Omega$ , $R_f = 500\Omega$ )

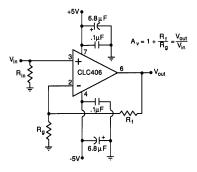

## **Feedback Resistor**

The CLC406 achieves its exceptional AC performance while requiring very low quiescent power by using the current feedback topology and an internal slew rate enhancement circuit. The loop gain and frequency response for a current feedback op amp is predominantly set by the feedback resistor value. The CLC406 is optimized for a gain of +6 to use a  $500\Omega$  feedback resistor (for maximally flat response at a gain of +2, use  $\mathbf{R_f} = \mathbf{1}\mathbf{k}\Omega$ ). Using lower values can lead to excessive ringing in the pulse response while a higher value will limit the bandwidth. Application Note OA-13 provides a more detailed discussion of choosing a feedback resistor. A plot within the CLC415 data sheet entitled "Recommended Rf vs. Gain" is also applicable to the CLC406. The values of R<sub>f</sub> found on this plot will optimize the performance of the CLC406 over its  $\pm 1$  to  $\pm 10$  gain range. The CLC406, like all current feedback op amps, can be operated at higher than recommended gains with an expected reduction in bandwidth.

#### **Slew Rate and Harmonic Distortion**

The current feedback topology yields an inherently high slew rate amplifier. For this reason the CLC406 shows little difference in bandwidth between  $2V_{pp}$  and  $5V_{pp}$ outputs. The dominant slew rate limiting mechanism is the unity gain buffer used internally from the non-inverting to the inverting inputs. Using a slew enhancement circuit to sense the onset of slew limiting, the buffer stage momentarily increases the quiescent current to handle high slew requirements. Slew rates will decrease when operating the CLC406 at lower non-inverting gains due to the increasing signal swing through the buffer stage which is necessary to maintain a fixed desired output swing. Conversely, slew rates are generally higher and relatively insensitive to gain setting for inverting gain operation. An additional discussion of slew rates can be found in the CLC404 data sheet.

As the output signal swing is increased, the slew enhancement circuit found in the buffer stage acts to suppress harmonic distortions. This is one reason the CLC406 does not exhibit a simple relationship between output power and distortion. For example, the 2-tone, 3rd order spurious plot shows the spurious level to remain nearly constant over test tone power. For this reason the CLC406 does not exhibit an intercept type performance where the relative spurious levels change at twice the rate of the test tone power.

#### **Differential Gain and Phase**

Differential gain and phase performance specifications are common to composite video distribution applications. These specifications refer to the change in small signal gain and phase of the color subcarrier frequency (4.43MHz for PAL composite video ) as the amplifier output is swept over a range of DC voltages. For this test only, the CLC406 is specified at a gain of  $\pm 2$  while connected to one or more doubly terminated 75 $\Omega$  loads. Application Note OA-

08 provides an additional discussion of differential gain and phase measurements.

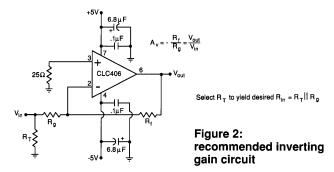

#### Non-inverting Source Impedance

For best operation, the DC source impedance looking out of the non-inverting input should be less than  $3k\Omega$  but greater than  $20\Omega$ . Parasitic self oscillations may occur in the input transistors if the DC source impedance is out of this range. This impedance also acts as the gain for the non-inverting input bias and noise currents and therefore can become troublesome for high values of DC source impedance. The inverting configuration of Figure 2 shows a  $25\Omega$  resistor to ground on the non-inverting input which insures stability but does not provide bias current cancellation. The input bias currents are unrelated for a current feedback amplifier which eliminates the need for source impedance matching to achieve bias current cancellation.

#### DC Accuracy and Noise

Figure 3 shows an example of the output offset voltage computation. The calculation is developed using typical bias current and offset voltage specifications at 25°C, a gain (Av) of +6 and a non-inverting source impedance  $(R_{\rm s})$  of  $25\Omega.$

Figure 3: Output Offset Voltage Calculation Output Offset Voltage  $V_o = (\pm I_{bn}R_{in} \pm V_{io})(1 + R_f/R_g) \pm I_{bi}R_f$   $V_o = (\pm 5\mu A(25\Omega) \pm 2mV)(6) \pm 3\mu A(500\Omega) = \pm 14.25mV$

Improved output offset voltage is possible using the composite circuits shown in Application Note OA-07.

The total output spot noise is computed in a similar fashion to the output offset voltage. Using the input spot noise voltage and the two input spot noise currents, the total output spot noise is developed through the same gain equations for each term but combined as the square root of the sum of squared contributing elements. Application Note OA-12 provides a more detailed discussion of noise calculations for current feedback amplifiers.

## **Printed Circuit Layout**

As with any high speed component, a careful attention to the board layout is necessary for optimum performance. Of particular importance is the careful control of parasitic capacitances on the output pin. As the output impedance plot shows, the closed loop output for the CLC406 eventually becomes inductive as the loop gain rolls off with increasing frequency. Direct capacitive loading on the output pin can quickly lead to peaking in the frequency response, overshoot in the pulse response, ringing or even sustained oscillations. The "Suggested Series R<sub>s</sub> vs. C" plot should be used as a starting point when a capacitive load must be driven.

Evaluation boards (CLC730013 – DIP, CLC730027 – SOIC, and CLC730068 – SOT) for the CLC406 are available. Further layout suggestions can be found in Application Note OA-15.

This page intentionally left blank.

## **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at 1-800-272-9959 or fax 1-800-737-7018.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **National Semiconductor** Corporation

1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### **National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

#### **National Semiconductor** Hong Kong Ltd.

2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600

Fax: (852) 2736-9960

Japan Ltd. Tel: 81-043-299-2309

**National Semiconductor**

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications