# CLC451 Single Supply, Low-Power, High Output, Programmable Buffer

# **General Description**

The CLC451 is a low cost, high speed (85MHz) buffer that features user-programmable gains of +2, +1, and -1V/V. It has a new output stage that delivers high output drive current (100mA), but consumes minimal quiescent supply current (1.5mA) from a single 5V supply. Its current feedback architecture, fabricated in an advanced complementary bipolar process, maintains consistent performance over a programmable range of gains and wide signal levels, and has a linear-phase response up to one half of the -3dB frequency. The CLC451's internal feedback network provides an excellent gain accuracy of 0.3%

The CLC451 offers superior dynamic performance with a 85MHz small-signal bandwidth,  $260V/\mu s$  slew rate and 6.5ns rise/fall times ( $2V_{step}$ ). The combination of the small SOT23-5 package, low quiescent power, high output current drive, and high-speed performance make the CLC451 well suited for many battery-powered personal communication/computing systems.

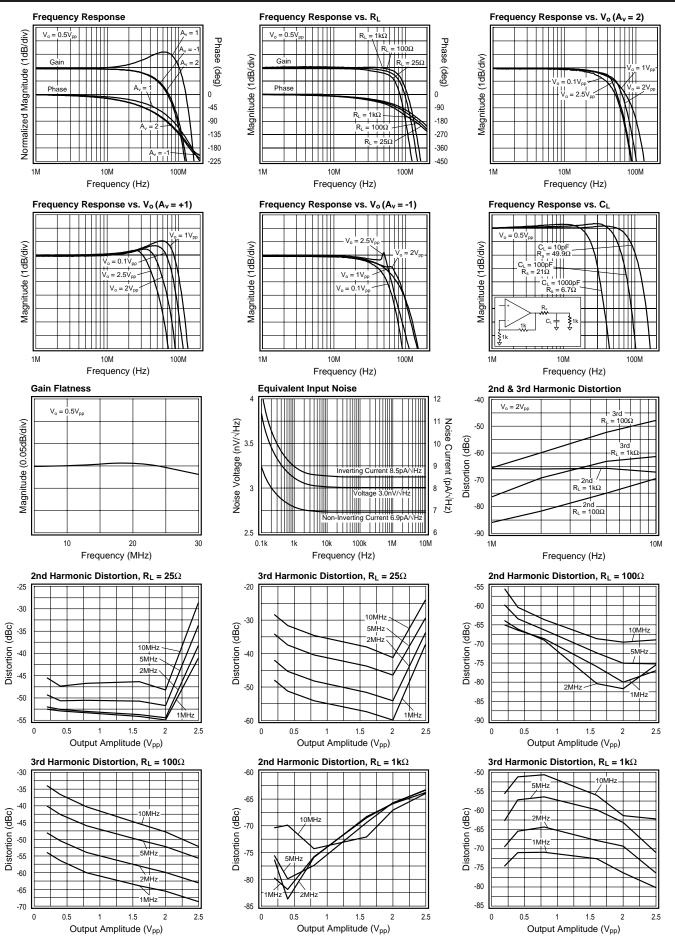

The ability to drive low-impedance, highly capacitive loads, makes the CLC451 ideal for single ended cable applications. It also drives low impedance loads with minimum distortion. The CLC451 will drive a 100 $\Omega$  load with only -78/-65dBc second/third harmonic distortion (A $_{\rm V}$  = +2, V $_{\rm out}$  = 2V $_{\rm pp}$ , f = 1MHz). With a 25 $\Omega$  load, and the same conditions, it produces only -55/-60dBc second/third harmonic distortion. It is also optimized for driving high currents into single-ended transformers and coils.

When driving the input of high-resolution A/D converters, the CLC451 provides excellent -66/-75dBc second/third harmonic distortion (A<sub>V</sub> = +2, V<sub>out</sub> = 2V<sub>pp</sub>, f = 1MHz, R<sub>L</sub> = 1k $\Omega$ ) and fast settling time.

#### **Features**

- 100mA output current

- 1.5mA supply current

- 85MHz bandwidth  $(A_v = +2)$

- -66/-75dBc HD2/HD3 (1MHz)

- 25ns settling to 0.05%

- 260V/µs slew rate

- Stable for capacitive loads up to 1000pF

- Single 5V to ±5V supplies

- Available in Tiny SOT23-5 package

# **Applications**

- Coaxial cable driver

- Twisted pair driver

- Transformer/Coil Driver

- High capacitive load driver

- Video line driver

- Portable/battery-powered applications

- A/D driver

#### +5V Electrical Characteristics ( $A_v = +2$ , $R_L = 100\Omega$ , $V_s = +5V^1$ , $V_{cm} = V_{EE} + (V_s/2)$ , $R_L$ tied to $V_{cm}$ , unless specified) **PARAMETERS** CONDITIONS **TYP** MIN/MAX RATINGS **NOTES** UNITS CLC451AJ +25°C +25°C 0 to 70°C -40 to 85°C Ambient Temperature FREQUENCY DOMAIN RESPONSE -3dB bandwidth $V_0 = 0.5V_{pp}$ 85 60 55 55 MHz $V_0 = 2.0 V_{pp}^{PP}$ 70 50 45 MHz 55 $V_{o} = 0.5V_{pp}$ <200MHz, $V_{o} = 0.5V_{pp}$ -0.1dB bandwidth 20 15 13 13 MHz gain peaking 0 0.5 0.9 1.0 dB $<30MHz, V_0 = 0.5V_{pp}$ gain rolloff 0.2 0.5 0.7 0.7 dB $<30MHz, V_0 = 0.5V_{pp}$ linear phase deviation 0.1 0.4 0.5 0.5 deg TIME DOMAIN RESPONSE rise and fall time 2V step 6.5 9.0 9.7 10.5 ns settling time to 0.05% 1V step 25 ns 13 15 18 18 overshoot 2V step % slew rate 2V step 260 180 165 150 V/µs DISTORTION AND NOISE RESPONSE $2V_{pp}$ , 1MHz $2V_{pp}$ , 1MHz; $R_L = 1k\Omega$ $2V_{pp}$ , 5MHz 2<sup>nd</sup> harmonic distortion -78 -72 -70 -70 dBc -66 -60 -58 -58 dBc -52 -60 -52 dBc -54 $2V_{pp}$ , 1MHz $2V_{pp}$ , 1MHz; $R_L = 1k\Omega$ $2V_{pp}$ , 5MHz3rd harmonic distortion -65 -59 -59 dBc -61 -75 -69 -67 -67 dBc -46 dBc -52 -48 -46 equivalent input noise nV/√Hz voltage (e<sub>ni</sub>) >1MHz 3.0 3.7 4 4 >1MHz 10 10 pA/√Hz non-inverting current (ibn) 6.9 9 inverting current (ibi) pA/√Hz >1MHz 8.5 11 12 12 STATIC DC PERFORMANCE input offset voltage 8 30 37 37 m۷ Α μV/°C average drift 80 input bias current (non-inverting) 3 14 17 18 Α μΑ average drift 25 nA/°C ±2.0 gain accuracy ±0.3 ±1.5 ±2.0 % Α internal resistors (R<sub>f</sub>, R<sub>a</sub>) 1000 ±20% ±26% ±30% Ω DC 44 dB power supply rejection ratio 49 46 44 DC 46 46 common-mode rejection ratio 51 48 dB supply current 1.7 1.8 1.8 Α $R_L = \infty$ 1.5 mΑ **MISCELLANEOUS PERFORMANCE**

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

0.5

1.5

4.2

8.0

4.0

1.0

4.1

0.9

100

400

0.37

2.3

4.1

0.9

3.9

1.1

4.0

1.0

80

600

0.33

2.3

4.0

1.0

3.8

1.2

4.0

1.0

65

600

# **Notes**

$R_1 = 100\Omega$

$R_L^- = 100\Omega$

$R_L^- = \infty$

$R_L = \infty$

DC

A) J-level: spec is 100% tested at +25° C.

input resistance (non-inverting)

input voltage range, High

input voltage range, Low

output voltage range, High

output voltage range, Low

output voltage range, High

output voltage range, Low

output resistance, closed loop

input capacitance (non-inverting)

- B) The short circuit current can exceed the maximum safe output current.

- 1)  $V_s = V_{CC} V_{EE}$

output current

| Reliability | Information |

|-------------|-------------|

| nt          |             |

Transistor Count

MTBF (based on limited test data)

# Absolute Maximum Ratings

0.33

2.3

4.0

1.0

3.8

1.2

3.9

1.1

40

600

$\begin{array}{c} M\Omega \\ pF \end{array}$

٧

٧

٧

V

٧

٧

mΑ

$m\Omega$

В

supply voltage ( $V_{CC} - V_{EE}$ ) +14V output current (see note C) 140mA common-mode input voltage  $V_{EE}$  to  $V_{CC}$  maximum junction temperature +150°C storage temperature range -65°C to +150°C lead temperature (soldering 10 sec) +300°C ESD rating (human body model) 500V

49

31Mhr

| PARAMETERS                                            | CONDITIONS                                                                     | TYP        | GUAR  | ANTEED MI | N/MAX       | UNITS       | NOTES |

|-------------------------------------------------------|--------------------------------------------------------------------------------|------------|-------|-----------|-------------|-------------|-------|

| Ambient Temperature                                   | CLC451AJ                                                                       | +25°C      | +25°C | 0 to 70°C | -40 to 85°C |             |       |

| FREQUENCY DOMAIN RESPONS                              | SE                                                                             |            |       |           |             |             |       |

| -3dB bandwidth                                        | $V_0 = 1.0 V_{DD}$                                                             | 100        | 80    | 68        | 65          | MHz         |       |

|                                                       | $V_0 = 4.0 V_{00}$                                                             | 55         | 45    | 42        | 40          | MHz         |       |

| -0.1dB bandwidth                                      | $V_0 = 1.0 V_{pp}$                                                             | 20         | 15    | 13        | 13          | MHz         |       |

| gain peaking                                          | $<200MHz, V_0 = 1.0V_{pp}$                                                     | 0          | 0.5   | 0.9       | 1.0         | dB          |       |

| gain rolloff                                          | $<30MHz, V_0 = 1.0V_{pp}$                                                      | 0.2        | 0.7   | 0.8       | 0.8         | dΒ          |       |

| linear phase deviation                                | $<30MHz, V_0 = 1.0V_{pp}$                                                      | 0.1        | 0.3   | 0.4       | 0.4         | deg         |       |

| differential gain                                     | NTSC, $R_L=150\Omega$                                                          | 0.3        | _     | _         | _           | %           |       |

| differential phase                                    | NTSC, $R_L=150\Omega$                                                          | 0.3        | _     | _         | _           | deg         |       |

| TIME DOMAIN RESPONSE                                  |                                                                                |            |       |           |             |             |       |

| rise and fall time                                    | 2V step                                                                        | 5.0        | 6.5   | 7.0       | 7.7         | ns          |       |

| settling time to 0.05%                                | 2V step                                                                        | 20         | _     | _         |             | ns          |       |

| overshoot                                             | 2V step                                                                        | 10         | 13    | 15        | 15          | %           |       |

| slew rate                                             | 2V step                                                                        | 350        | 260   | 240       | 220         | V/μs        |       |

| DISTORTION AND NOISE RESPO                            |                                                                                |            |       |           |             |             |       |

| 2 <sup>nd</sup> harmonic distortion                   | 2V <sub>pp</sub> , 1MHz                                                        | -72        | -66   | -64       | -64         | dBc         |       |

|                                                       | $2V_{pp}$ , 1MHz; $R_L = 1k\Omega$                                             | -69        | -63   | -61       | -61         | dBc         |       |

| ord I I I I                                           | $2V_{pp}$ , 1MHz; R <sub>L</sub> = 1kΩ<br>$2V_{pp}$ , 5MHz<br>$2V_{pp}$ , 1MHz | -66        | -60   | -58       | -58         | dBc         |       |

| 3 <sup>rd</sup> harmonic distortion                   | 2V <sub>pp</sub> , 1MHz                                                        | -65        | -61   | -59       | -59         | dBc         |       |

|                                                       | $2V_{pp}^{\prime\prime}$ , 1MHz; $R_L = 1k\Omega$                              | -73<br>-73 | -67   | -65<br>40 | -65<br>46   | dBc         |       |

| equivalent input noise                                | 2V <sub>pp</sub> , 5MHz                                                        | -52        | -48   | -46       | -46         | dBc         |       |

| voltage (e <sub>ni</sub> )                            | >1MHz                                                                          | 3.0        | 3.7   | 4         | 4           | nV/√Hz      |       |

| non-inverting current (i <sub>bn</sub> )              | >1MHz                                                                          | 6.9        | 9     | 10        | 10          | pA/√Hz      |       |

| inverting current (i <sub>bi</sub> )                  | >1MHz                                                                          | 8.5        | 11    | 12        | 12          | pA/√Hz      |       |

|                                                       | 7 1101112                                                                      | 0.0        |       |           |             | p, ( 11.12  |       |

| STATIC DC PERFORMANCE                                 |                                                                                | _          | 20    | 25        | 25          | m\/         |       |

| output offset voltage<br>average drift                |                                                                                | 3<br>80    | 30    | 35        | 35<br>-     | mV<br>μV/°C |       |

| input bias current (non-inverting)                    |                                                                                | 1          | 12    | 19        | 19          | μΑ          |       |

| average drift                                         |                                                                                | 40         | _     | _         | _           | nA/°C       |       |

| gain accuracy                                         |                                                                                | ±0.3       | ±1.5  | ±2.0      | ±2.0        | 1,, v O     |       |

| internal resistors (R <sub>f</sub> , R <sub>g</sub> ) |                                                                                | 1000       | ±20%  | ±26%      | ±30%        | Ω           |       |

| power supply rejection ratio                          | DC                                                                             | 48         | 45    | 43        | 43          | dB          |       |

| common-mode rejection ratio                           | DC                                                                             | 53         | 50    | 48        | 48          | dB          |       |

| supply current                                        | R <sub>L</sub> = ∞                                                             | 1.6        | 1.9   | 2.0       | 2.0         | mA          |       |

| MISCELLANEOUS PERFORMAN                               |                                                                                |            |       |           |             |             |       |

| input resistance (non-inverting)                      | <del>-</del>                                                                   | 0.7        | 0.50  | 0.45      | 0.45        | MΩ          |       |

| input capacitance (non-inverting)                     |                                                                                | 1.2        | 1.8   | 1.8       | 1.8         | pF          |       |

| common-mode input range                               |                                                                                | ±4.2       | ±4.1  | ±4.1      | ±4.0        | V           |       |

| output voltage range                                  | $R_{I} = 100\Omega$                                                            | ±3.8       | ±3.6  | ±3.6      | ±3.5        | v           |       |

| output voltage range                                  | $R_1 = \infty$                                                                 | ±4.0       | ±3.8  | ±3.8      | ±3.7        | v           |       |

| output current                                        | L                                                                              | 130        | 100   | 80        | 50          | mA          | В     |

| output resistance, closed loop                        | DC                                                                             | 400        | 600   | 600       | 600         | mΩ          |       |

| •    |      |

|------|------|

| N. I | 0+00 |

|      |      |

B) The short circuit current can exceed the maximum safe output current.

| Package mermai Resistance |                 |               |  |

|---------------------------|-----------------|---------------|--|

| Package                   | θ <sub>JC</sub> | $\theta_{JA}$ |  |

| Plastic (AJP)             | 105°C/W         | 155°C/W       |  |

| Surface Mount (AJE)       | 95°C/W          | 175°C/W       |  |

| Surface Mount (AJM5)      | 140°C/W         | 210°C/W       |  |

| Dice (ALC)                | 25°C/W          | _             |  |

| Ordering Information                              |                                                                      |                                               |  |

|---------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|--|

| Model                                             | Temperature Range                                                    | Description                                   |  |

| CLC451AJP<br>CLC451AJE<br>CLC451AJM5<br>CLC451ALC | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C | 8-pin PDIP<br>8-pin SOIC<br>5-pin SOT<br>dice |  |

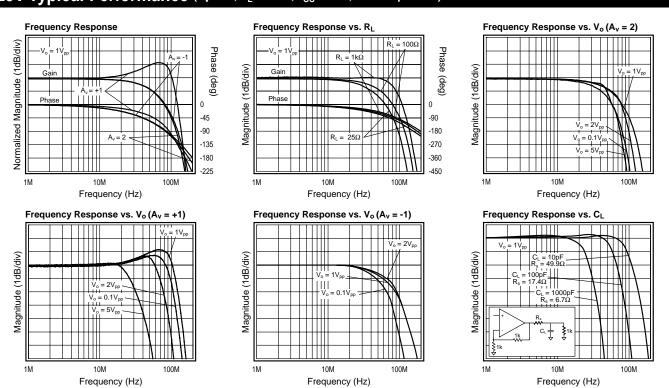

# +5V Typical Performance (A<sub>v</sub> = +2, R<sub>L</sub> = $100\Omega$ , V<sub>s</sub> = +5V<sup>1</sup>, V<sub>cm</sub> = V<sub>EE</sub> + (V<sub>s</sub>/2), R<sub>L</sub> tied to V<sub>cm</sub>, unless specified)

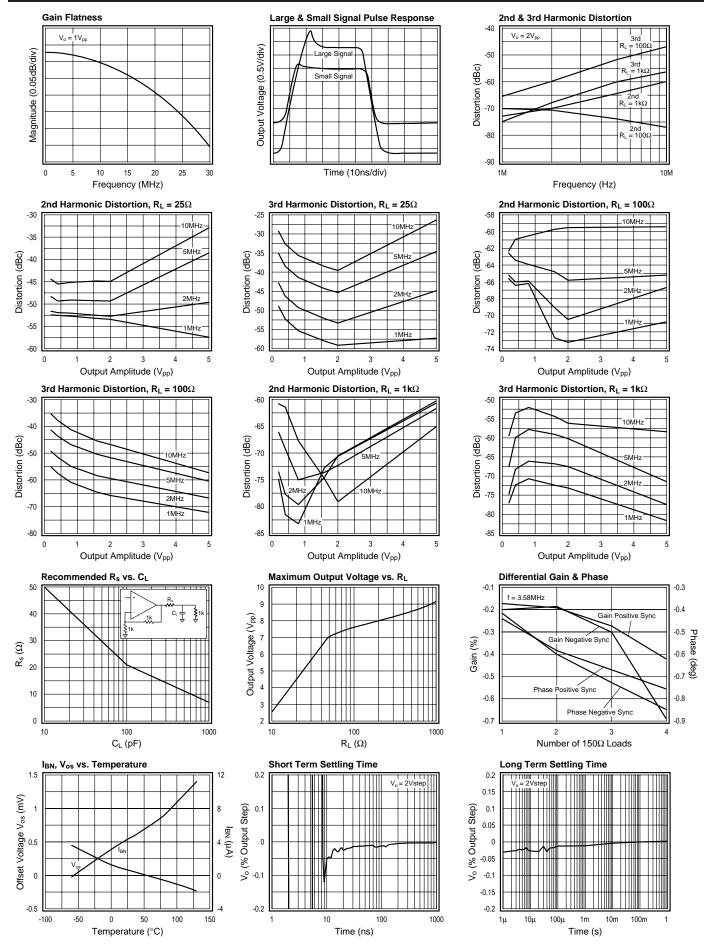

# +5V Typical Performance ( $A_v = +2$ , $R_L = 100\Omega$ , $V_s = +5V^1$ , $V_{cm} = V_{EE} + (V_s/2)$ , $R_L$ tied to $V_{cm}$ , unless specified)

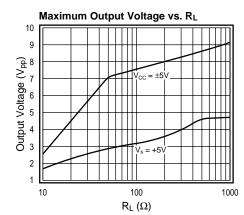

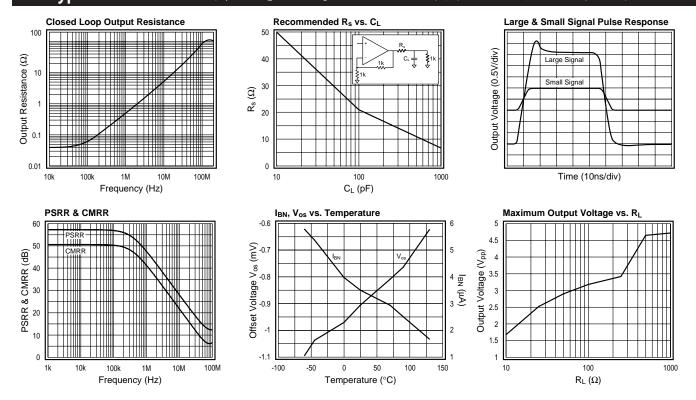

# $\pm 5V$ Typical Performance (A<sub>v</sub> = +2, R<sub>L</sub> = 100 $\Omega$ , V<sub>CC</sub> = $\pm$ 5V, unless specified)

# $\pm 5V$ Typical Performance (A<sub>v</sub> = +2, R<sub>L</sub> = 100 $\Omega$ , V<sub>CC</sub> = $\pm$ 5V, unless specified)

# **CLC451 Operation**

The CLC451 is a current feedback buffer built in an advanced complementary bipolar process. The CLC451 operates from a single 5V supply or dual ±5V supplies. Operating from a single 5V supply, the CLC451 has the following features:

- Gains of +1, -1, and 2V/V are achievable without external resistors

- Provides 100mA of output current while consuming only 7.5mW of power

- Offers low -66/-75dBc 2nd and 3rd harmonic distortion

- Provides BW > 60MHz and 1MHz distortion < -55dBc at V<sub>o</sub> = 2V<sub>pp</sub>

The CLC451 performance is further enhanced in ±5V supply applications as indicated in the ±5V Electrical Characteristics table and ±5V Typical Performance plots.

If gains other than +1, -1, or +2V/V are required, then the CLC450 can be used. The CLC450 is a current feedback amplifier with near identical performance and allows for external feedback and gain setting resistors.

### **Current Feedback Amplifiers**

Some of the key features of current feedback technology are:

- Independence of AC bandwidth and voltage gain

- Inherently stable at unity gain

- Adjustable frequency response with feedback resistor

- High slew rate

- Fast settling

Current feedback operation can be described using a simple equation. The voltage gain for a non-inverting or inverting current feedback amplifier is approximated by Equation 1.

$$\frac{V_o}{V_{in}} = \frac{A_v}{1 + \frac{R_f}{Z(i\omega)}}$$

Equation 1

where:

- A<sub>v</sub> is the closed loop DC voltage gain

- R<sub>f</sub> is the feedback resistor

- Z(jω) is the CLC451's open loop transimpedance gain

- $\frac{Z(j\omega)}{R_f}$  is the loop gain

The denominator of Equation 1 is approximately equal to 1 at low frequencies. Near the -3dB corner frequency, the interaction between  $R_f$  and  $Z(j\omega)$  dominates the circuit performance. The value of the feedback resistor has a large affect on the circuits performance. Increasing  $R_f$  has the following affects:

- Decreases loop gain

- Decreases bandwidth

- Reduces gain peaking

- Lowers pulse response overshoot

- Affects frequency response phase linearity

# **CLC451 Design Information**

#### **Closed Loop Gain Selection**

The CLC451 is a current feedback op amp with  $R_f = R_g = 1 k\Omega$  on chip (in the package). Select from three closed loop gains without using any external gain or feedback resistors. Implement gains of +2, +1, and -1V/V by connecting pins 2 and 3 as described in the chart below.

| Gain    | Input Connections    |                  |  |

|---------|----------------------|------------------|--|

| $A_{V}$ | Non-Inverting (pin3) | Inverting (pin2) |  |

| -1V/V   | ground               | input signal     |  |

| +1V/V   | input signal         | NC (open)        |  |

| +2V/V   | input signal         | ground           |  |

The gain accuracy of the CLC451 is excellent and stable over temperature change. The internal gain setting resistors,  $R_{\rm f}$  and  $R_{\rm g}$  are diffused silicon resistors with a process variation of  $\pm$  20% and a temperature coefficient of  $\sim$  2000ppm/°C. Although their absolute values change with processing and temperature, their ratio  $(R_{\rm f}/R_{\rm g})$  remains constant. If an external resistor is used in series with  $R_{\rm g}$ , gain accuracy over temperature will suffer.

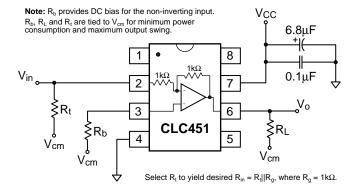

### Single Supply Operation $(V_{CC} = +5V, V_{EE} = GND)$

The specifications given in the **+5V Electrical Characteristics** table for single supply operation are measured with a common mode voltage ( $V_{cm}$ ) of 2.5V.  $V_{cm}$  is the voltage around which the inputs are applied and the output voltages are specified.

Operating from a single +5V supply, the Common Mode Input Range (CMIR) of the CLC451 is typically +0.8V to +4.2V. The typical output range with  $R_L$ =100 $\Omega$  is +1.0V to +4.0V.

For single supply DC coupled operation, keep input signal levels above 0.8V DC. For input signals that drop below 0.8V DC, AC coupling and level shifting the signal are recommended. The non-inverting and inverting configurations for both input conditions are illustrated in the following 2 sections.

#### **DC Coupled Single Supply Operation**

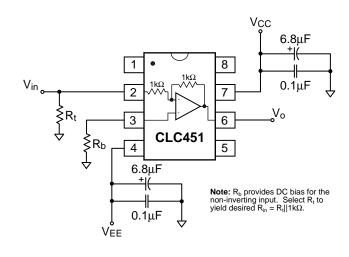

Figures 1, 2, and 3 on the following page, show the recommended configurations for input signals that remain above 0.8V DC.

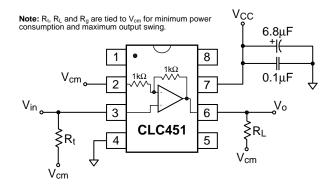

Figure 1: DC Coupled,  $A_v = -1V/V$  Configuration

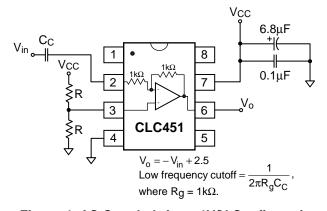

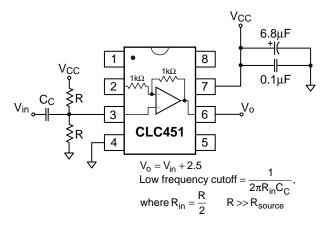

Figure 2: DC Coupled,  $A_v = +1V/V$  Configuration

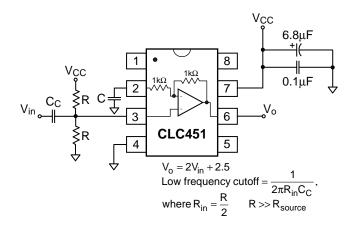

Figure 3: DC Coupled,  $A_v = +2V/V$  Configuration

# **AC Coupled Single Supply Operation**

Figures 4, 5, and 6 show possible non-inverting and inverting configurations for input signals that go below 0.8V DC.

Figure 4: AC Coupled,  $A_v = -1V/V$  Configuration

The input is AC coupled to prevent the need for level shifting the input signal at the source. The resistive voltage divider biases the non-inverting input to  $V_{CC} \div 2 = 2.5V$  (For  $V_{CC} = +5V$ ).

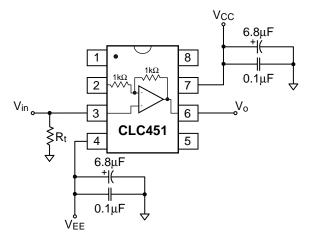

Figure 5: AC Coupled,  $A_v = +1V/V$  Configuration

Figure 6: AC Coupled,  $A_v = +2V/V$  Configuration

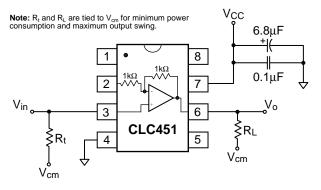

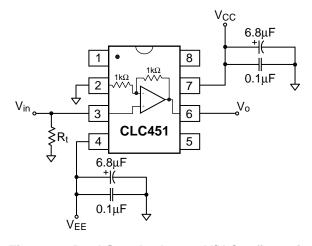

### **Dual Supply Operation**

The CLC451 operates on dual supplies as well as single supplies. The non-inverting and inverting configurations are shown in Figures 7, 8 and 9.

Figure 7: Dual Supply,  $A_v = -1V/V$  Configuration

Figure 8: Dual Supply,  $A_v = +1V/V$  Configuration

Figure 9: Dual Supply,  $A_v = +2V/V$  Configuration

# Bandwidth vs. Output Amplitude

The bandwidth of the CLC451 is at a maximum for output voltages near 1V<sub>DD</sub>. The bandwidth decreases for smaller and larger output amplitudes. Refer to the Frequency Response vs. Vo plots.

### **Load Termination**

The CLC451 can source and sink near equal amounts of current. For optimum performance, the load should be tied to V<sub>cm</sub>.

### **Driving Cables and Capacitive Loads**

When driving cables, double termination is used to prevent reflections. For capacitive load applications, a small series resistor at the output of the CLC451 will improve stability and settling performance. The Frequency Response vs. C<sub>L</sub> and Recommended R<sub>s</sub> vs. C<sub>1</sub> plots, in the typical performance section, give the recommended series resistance value for optimum flatness at various capacitive loads.

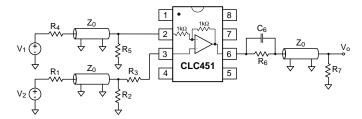

#### Transmission Line Matching

One method for matching the characteristic impedance (Z<sub>0</sub>) of a transmission line or cable is to place the appropriate resistor at the input or output of the amplifier.

Figure 10 shows typical inverting and non-inverting circuit configurations for matching transmission lines.

Non-inverting gain applications:

- Connect pin 2 as indicated in the table in the Closed Loop Gain Selection section.

- Make  $R_1$ ,  $R_2$ ,  $R_6$ , and  $R_7$  equal to  $Z_0$ .

- Use R<sub>3</sub> to isolate the amplifier from reactive loading caused by the transmission line, or by parasitics.

Inverting gain applications:

- Connect R<sub>3</sub> directly to ground.

- Make the resistors R<sub>4</sub>, R<sub>6</sub>, and R<sub>7</sub> equal to Z<sub>0</sub>.

- Make  $R_5$  II  $R_q = Z_o$ .

The input and output matching resistors attenuate the signal by a factor of 2, therefore additional gain is needed. Use C<sub>6</sub> to match the output transmission line over a greater frequency range. C<sub>6</sub> compensates for the increase of the amplifier's output impedance with frequency.

Figure 10: Transmission Line Matching

#### **Power Dissipation**

Follow these steps to determine the power consumption of the CLC451:

- 1. Calculate the quiescent (no-load) power:

- $P_{amp} = I_{CC} (V_{CC} V_{EE})$ 2. Calculate the RMS power at the output stage:  $P_o = (V_{CC} - V_{load}) (I_{load})$ , where  $V_{load}$  and  $I_{load}$ are the RMS voltage and current across the external load.

- 3. Calculate the total RMS power:

$$P_t = P_{amp} + P_o$$

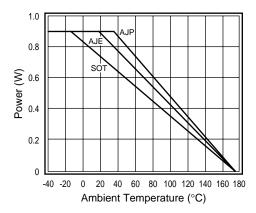

The maximum power that the DIP, SOIC, and SOT packages can dissipate at a given temperature is illustrated in Figure 11. The power derating curve for any CLC451 package can be derived by utilizing the following equation:

where

$$\frac{(175^{\circ} - T_{amb})}{\theta_{JA}}$$

$T_{amb}$  = Ambient temperature (°C)

$\theta_{\text{JA}}$  = Thermal resistance, from junction to ambient, for a given package (°C/W)

Figure 11: Power Derating Curve

# **Layout Considerations**

A proper printed circuit layout is essential for achieving high frequency performance. Comlinear provides evaluation boards for the CLC451 (CLC730013-DIP, CLC730027-SOIC, CLC730068-SOT) and suggests their use as a guide for high frequency layout and as an aid for device testing and characterization.

General layout and supply bypassing play major roles in high frequency performance. Follow the steps below as a basis for high frequency layout:

- Include 6.8µF tantalum and 0.1µF ceramic capacitors on both supplies.

- Place the 6.8µF capacitors within 0.75 inches of the power pins.

- Place the 0.1µF capacitors less than 0.1 inches from the power pins.

- Remove the ground plane under and around the part, especially near the input and output pins to reduce parasitic capacitance.

- Minimize all trace lengths to reduce series inductances.

- Use flush-mount printed circuit board pins for prototyping, never use high profile DIP sockets.

#### **Evaluation Board Information**

Data sheets are available for the CLC730013/ CLC730027 and CLC730068 evaluation boards. The evaluation board data sheets provide:

- Evaluation board schematics

- Evaluation board layouts

- General information about the boards

The CLC730013/CLC730027 data sheet also contains tables of recommended components to evaluate several of Comlinear's high speed amplifiers. This table for the CLC451 is illustrated below. Refer to the evaluation board data sheet for schematics and further information.

### Components Needed to Evaluate the CLC451 on the Evaluation Board:

■  $R_{in}$ ,  $R_{out}$  - Typically 50 $\Omega$  (Refer to the *Basic* Operation section of the evaluation board data sheet for details)

- R<sub>t</sub> Optional resistor for inverting gain configurations (Select R<sub>t</sub> to yield desired input impedance  $= R_q || R_t$

- C<sub>1</sub>, C<sub>2</sub> 0.1μF ceramic capacitors

- $C_3$ ,  $C_4$  6.8µF tantalum capacitors

Components not used:

- C<sub>5</sub>, C<sub>6</sub>, C<sub>7</sub>, C<sub>8</sub> R<sub>1</sub> thru R<sub>8</sub>

The evaluation boards are designed to accommodate dual supplies. The boards can be modified to provide single supply operation. For best performance; 1) do not connect the unused supply, 2) ground the unused supply pin.

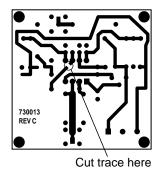

### **Special Evaluation Board** Considerations for the CLC451

To optimize off-isolation of the CLC451, cut the R<sub>f</sub> trace on both the CLC730013 and the CLC730027 evaluation boards. This cut minimizes capacitive feedthrough between the input and the output. Figure 12 shows where to cut both evaluation boards for improved off-isolation.

Cut trace here

Figure 12: Evaluation Board Changes

#### **SPICE Models**

SPICE models provide a means to evaluate amplifier designs. Free SPICE models are available for Comlinear's monolithic amplifiers that:

- Support Berkeley SPICE 2G and its many derivatives

- Reproduce typical DC, AC, Transient, and Noise performance

- Support room temperature simulations

The readme file that accompanies the diskette lists released models, and provides a list of modeled parameters. The application note OA-18, Simulation SPICE Models for Comlinear's Op Amps, contains schematics and a reproduction of the readme file.

# **Application Circuits**

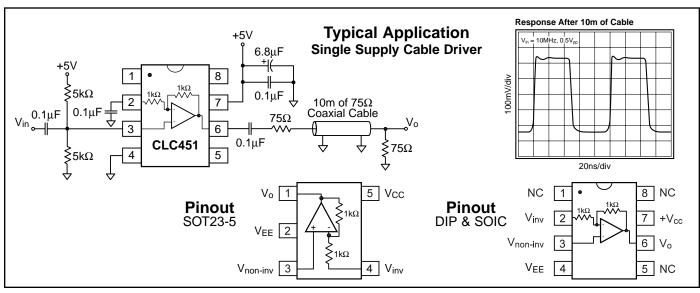

#### Single Supply Cable Driver

The typical application shown on the front page shows the CLC451 driving 10m of  $75\Omega$  coaxial cable. The CLC451 is set for a gain of +2V/V to compensate for the divide-by-two voltage drop at V<sub>o</sub>.

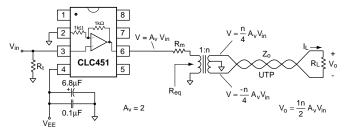

#### **Twisted Pair Driver**

The high output current and low distortion, of the CLC451, make it well suited for driving transformers. Figure 13 illustrates a typical twisted pair driver utilizing the CLC451 and a transformer. The transformer provides the signal and its inversion for the twisted pair.

Figure 13: Twisted Pair Driver

To match the line's characteristic impedance (Z<sub>o</sub>) set:

$$\blacksquare R_L = Z_0$$

$$\blacksquare R_m = R_{eq}$$

Where  $R_{eq}$  is the transformed value of the load impedance,  $(R_L),$  and is approximated by:

$$R_{eq} = \frac{R_L}{n^2}$$

Select the transformer so that it loads the line with a value close to  $Z_0$ , over the desired frequency range. The output impedance,  $R_0$ , of the CLC451 varies with frequency and can also affect the return loss. The return loss, shown below, takes into account an ideal transformer and the value of  $R_0$ .

Return Loss(dB)

$$\approx -20log_{10} \left| n^2 \cdot \frac{R_o}{Z_o} \right|$$

The load current  $(I_L)$  and voltage  $(V_0)$  are related to the CLC451's maximum output voltage and current by:

$$|V_0| \le n \cdot V_{max}$$

$|I_L| \le \frac{I_{max}}{n}$

From the above current relationship, it is obvious that an amplifier with high output drive capability is required.

### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at 1-800-272-9959 or fax 1-800-737-7018.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **National Semiconductor** Corporation

1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

# **National Semiconductor**

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

#### **National Semiconductor** Hong Kong Ltd.

2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui. Kowloon Hong Kong Tel: (852) 2737-1600

Fax: (852) 2736-9960

#### **National Semiconductor** Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications