# ANALOG DEVICES

# LCD Panel Power, V<sub>COM</sub>, and Gate Modulation

# ADD8754

#### **FEATURES**

| Step-up switching regulator with 2 A power switch |

|---------------------------------------------------|

| 650 kHz or 1.2 MHz switching frequency            |

| Output adjustable to 20 V                         |

| 350 mA logic voltage regulator                    |

| Selectable output voltages: 2.5 V, 2.85 V, 3.3 V  |

| V <sub>COM</sub> amplifier with 300 mA drive      |

| Gate pulse modulation circuitry                   |

| Independently adjustable delay and falling slope  |

| General                                           |

| 3 V to 5.5 V input                                |

| Undervoltage lockout                              |

| Thermal shutdown                                  |

| 24-lead, Pb-free LFCSP package                    |

APPLICATIONS TFT LCD panels for monitors, TVs, and notebooks

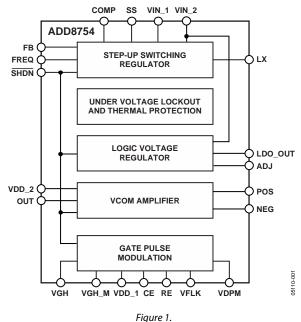

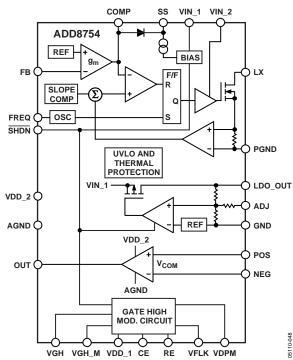

### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The ADD8754 is optimized for use in TFT LCD applications, requiring only external charge pump components to provide all the requirements for panel power,  $V_{COM}$ , and gate modulation. Included in a single chip are a high frequency step-up dc-to-dc switching regulator, logic voltage regulator,  $V_{COM}$  amplifier, and gate pulse modulation circuitry.

The step-up dc-to-dc converter provides up to 20 V output and includes a 2 A internal switch. Either a 650 kHz or 1.2 MHz stepup switching regulator frequency can be chosen, allowing easy filtering and low noise operation. It achieves 93% efficiency and features soft start to limit the inrush current at startup.

The internal voltage regulator operates with an input voltage range of 3 V to 5.5 V and delivers a load current of up to

350 mA. Three selectable output voltages are available: 2.5 V, 2.85 V, and 3.3 V.

The proprietary  $V_{\rm COM}$  amplifier can deliver a peak output current of 300 mA and is specifically designed to drive TFT panel loads.

The gate pulse modulator allows shaping of the TFT gate high voltage to improve image quality. The integrated switches provide the ability to independently control the delay and slope for the gate drive voltage.

The ADD8754 is offered in a 24-lead, Pb-free LFCSP package and is specified over the industrial temperature range of -40 to  $+85^{\circ}$ C.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2005 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Specifications                              | 3 |

|---------------------------------------------|---|

| Step-Up Switching Regulator Specifications  | 3 |

| LDO Regulator Specifications                | 4 |

| V <sub>COM</sub> Amplifier Specifications   | 5 |

| Gate Pulse Modulator Specifications         | 6 |

| General Specifications                      | 6 |

| Absolute Maximum Ratings                    | 7 |

| ESD Caution                                 | 7 |

| Pin Configuration and Function Descriptions | 8 |

| Typical Performance Characteristics         | 9 |

| Theory of Operation1                        | 2 |

### **REVISION HISTORY**

4/05—Revision 0: Initial Version

|    | Current-Mode, Step-Up Switching Regulator Operation | 12 |

|----|-----------------------------------------------------|----|

|    | V <sub>COM</sub> Amplifier                          | 16 |

|    | Gate Pulse Modulator Circuit                        | 16 |

|    | Power-Up Sequence                                   | 17 |

|    | Shutdown                                            | 17 |

|    | UVLO                                                | 17 |

|    | Power Dissipation                                   | 18 |

|    | Layout Guidelines                                   | 19 |

| Ту | pical Application Circuits                          | 20 |

| Oı | utline Dimensions                                   | 25 |

|    | Ordering Guide                                      | 25 |

### **SPECIFICATIONS**

### STEP-UP SWITCHING REGULATOR SPECIFICATIONS

$VIN_1 = VIN_2 = \overline{SHDN} = 5 V$ ,  $V_{OUT}^1 = VDD_1 = VDD_2 = 14 V$ ,  $T_A = 25^{\circ}C$ , FREQ = GND, unless otherwise noted.

### Table 1.

| Parameter            | Symbol               | Conditions                                                                                | Min   | Тур   | Max   | Unit  |

|----------------------|----------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| SUPPLY               |                      |                                                                                           |       |       |       |       |

| Input Voltage Range  | VIN                  |                                                                                           | 3.0   |       | 5.5   | V     |

| OUTPUT <sup>1</sup>  |                      |                                                                                           |       |       |       |       |

| Output Voltage Range | Vout <sup>1</sup>    |                                                                                           |       |       | 20    | V     |

| Load Regulation      |                      | $10 \text{ mA} \le I_{\text{LOAD}} \le 150 \text{ mA}, V_{\text{OUT}}^{1} = 10 \text{ V}$ |       | 200   |       | μV/mA |

| Line Regulation      |                      | $I_{LOAD} = 350 \text{ mA}, 4.5 \text{ V} \le \text{VIN}_1 \le 5.5 \text{ V}$             |       |       |       | mV    |

| Load Regulation      |                      | $10 \text{ mA} \le I_{\text{LOAD}} \le 150 \text{ mA}, V_{\text{OUT}}^{1} = 10 \text{ V}$ |       | 200   |       | μV/mA |

| Line Regulation      |                      | $I_{LOAD} = 150 \text{ mA}, 3.0 \text{ V} \le \text{VIN}_1 \le 5.5 \text{ V}$             |       |       |       | mV    |

| Overall Regulation   |                      | Line, load, temperature (–40°C $\leq$ T <sub>A</sub> $\leq$ +85°C)                        | -3    |       | +3    | %     |

| REFERENCE            |                      |                                                                                           |       |       |       |       |

| Feedback Voltage     | VFB                  |                                                                                           | 1.200 | 1.211 | 1.220 | V     |

| ERROR AMPLIFIER      |                      |                                                                                           |       |       |       |       |

| Transconductance     | GMEA                 |                                                                                           |       | 100   |       | μA/V  |

| Gain                 | Av                   |                                                                                           |       | 1000  |       | V/V   |

| Input Bias Current   | IB                   |                                                                                           |       | 225   |       | nA    |

| SWITCH               |                      |                                                                                           |       |       |       |       |

| On Resistance        | R <sub>DS (ON)</sub> |                                                                                           |       | 170   |       | mΩ    |

| Leakage Current      | ILKG                 | $V_{LX} = 14 \text{ V}, \overline{\text{SHDN}} = \text{GND}$                              |       | 0.5   |       | μΑ    |

| Peak Current Limit   | Icl                  |                                                                                           |       | 2.6   |       | А     |

| OSCILLATOR           |                      |                                                                                           |       |       |       |       |

| Oscillator Frequency | Fosc                 | FREQ = GND                                                                                |       | 650   |       | kHz   |

|                      |                      | FREQ = VIN_1                                                                              |       | 1.2   |       | MHz   |

| Maximum Duty Cycle   | D <sub>MAX</sub>     | VFB = 1 V                                                                                 |       | 90    | 95    | %     |

| SOFT START           |                      |                                                                                           |       |       |       |       |

| Peak Current         |                      | SS = GND                                                                                  |       | 2.5   |       | μA    |

<sup>1</sup> Refer to the Figure 23.

### LDO REGULATOR SPECIFICATIONS

VIN\_1 = VIN\_2 =  $\overline{SHDN}$  = 5 V, ADJ = LDO\_OUT,<sup>1</sup> CLDO = 2.2  $\mu$ F, T<sub>A</sub> = 25°C, unless otherwise noted.

Table 2.

| Parameter           | Symbol            | Conditions                                                                                       | Min  | Тур  | Max | Unit |

|---------------------|-------------------|--------------------------------------------------------------------------------------------------|------|------|-----|------|

| INPUT               |                   |                                                                                                  |      |      |     |      |

| Input Voltage Range | VIN <sup>2</sup>  | $ADJ = LDO_OUT^1$                                                                                | 3.0  |      | 5.5 | V    |

|                     |                   | $ADJ = OPEN^3$                                                                                   | 3.35 |      | 5.5 | V    |

|                     |                   | $ADJ = GND^4$                                                                                    | 3.8  |      | 5.5 | V    |

| OUTPUT              |                   |                                                                                                  |      |      |     |      |

| Output Voltage      | LDO_OUT           | I <sub>LDO</sub> = 1 mA, ADJ = GND                                                               |      | 3.31 |     | v    |

|                     |                   | $I_{LDO} = 350 \text{ mA}, \text{ADJ} = \text{GND}$                                              |      | 3.29 |     | v    |

|                     |                   | $I_{LDO} = 1 \text{ mA}, \text{ADJ} = \text{OPEN}$                                               |      | 2.86 |     | V    |

|                     |                   | $I_{LDO} = 350 \text{ mA}, \text{ADJ} = \text{OPEN}$                                             |      | 2.84 |     | V    |

|                     |                   | $I_{LDO} = 1 \text{ mA}, \text{ADJ} = \text{LDO}_\text{OUT}$                                     |      | 2.51 |     | V    |

|                     |                   | I <sub>LDO</sub> = 350 mA, ADJ = LDO_OUT                                                         |      | 2.49 |     | V    |

| Voltage Accuracy    |                   | $I_{LDO} = 1 \text{ mA to } 350 \text{ mA}, -40^{\circ}\text{C} \le T_A \le +85^{\circ}\text{C}$ | -3   |      | +3  | %    |

| Line Regulation     |                   | $I_{LDO} = 1 \text{ mA}$                                                                         |      | 3    |     | mV/V |

| Load Regulation     |                   | I <sub>LDO</sub> = 1 mA to 350 mA                                                                |      | 20   |     | mV   |

| Dropout Voltage     | VDROP             | $LDO_OUT = 98\%$ of $LDO_OUT(NOM)$ , $I_{LDO} = 350$ mA                                          |      | 300  | 500 | mV   |

| Current Limit       | I <sub>LDPK</sub> |                                                                                                  |      | 350  |     | mA   |

<sup>1</sup> Sets LDO\_OUT(NOM) to 2.5 V.

<sup>2</sup> VIN = VIN\_1 = VIN\_2. <sup>3</sup> Sets LDO\_OUT(NOM) to 2.85 V. <sup>4</sup> Sets LDO\_OUT(NOM) to 3.3 V.

### **V**<sub>COM</sub> AMPLIFIER SPECIFICATIONS

$VIN_1 = VIN_2 = \overline{SHDN} = 5 V$ ,  $VDD_2 = 14 V$ , POS = 4.0 V, NEG = OUT,  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                       | Symbol          | Conditions                                                                   | Min | Тур         | Max       | Unit |

|---------------------------------|-----------------|------------------------------------------------------------------------------|-----|-------------|-----------|------|

| INPUT CHARACTERISTICS           |                 |                                                                              |     |             |           |      |

| Offset Voltage                  | Vos             |                                                                              |     | 19          |           | mV   |

| Noninverting Input Bias Current | IB              |                                                                              |     | 50          | 300       | nA   |

| Input Voltage Range             |                 |                                                                              | 2   |             | VDD_2 - 3 | v    |

| Common-Mode Rejection Ratio     | CMRR            | $V_{CM} = 2 V \text{ to } (VDD_2 - 3) V$                                     |     | 60          |           | dB   |

| OUTPUT CHARACTERISTICS          |                 |                                                                              |     |             |           |      |

| Output Voltage Swing            | Vон             | l <sub>out</sub> (source) = 50 mA                                            |     | VDD_2 - 0.5 |           | V    |

|                                 | V <sub>OL</sub> | I <sub>OUT</sub> (sink) = 50 mA                                              |     | 50          |           | mV   |

| Output Current <sup>1</sup>     | Іоит            |                                                                              |     | ±300        |           | mA   |

| POWER SUPPLY                    |                 |                                                                              |     |             |           |      |

| Supply Voltage                  | VDD_2           |                                                                              | 8   |             | 18        | v    |

| Power Supply Rejection Ratio    | PSRR            | 7.5 V ≤ VDD_2 ≤ 18.5 V                                                       | 65  | 70          |           | dB   |

| Supply Current                  | Isy             | No load, POS = VDD_2 /2                                                      |     | 2           |           | mA   |

| DYNAMIC PERFORMANCE             |                 |                                                                              |     |             |           |      |

| Slew Rate <sup>2</sup>          | SR              | $R_L = 10 \text{ k}\Omega$ , $C_L = 10 \text{ pF}$                           |     | 105         |           | V/µs |

| Gain Bandwidth                  | GBW             | $-3 \text{ dB}, \text{R}_L = 10 \text{ k}\Omega, \text{C}_L = 10 \text{ pF}$ |     | 1.95        |           | MHz  |

<sup>1</sup> Not short-circuit protected.

<sup>2</sup> Slew rate is the average of the rising and the falling slew rates.

### GATE PULSE MODULATOR SPECIFICATIONS

$VIN_1 = VIN_2 = \overline{SHDN} = 5 V$ , VGH = 20 V,  $VDD_1 = 14 V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 4.

| Parameter                            | Symbol             | Condition                                             | Min | Тур  | Max | Unit |

|--------------------------------------|--------------------|-------------------------------------------------------|-----|------|-----|------|

| INPUT CHARACTERISTICS                |                    |                                                       |     |      |     |      |

| VGH Voltage                          | VGH                |                                                       | 7   |      | 30  | V    |

| VGH Input Current                    | lvgн               | VFLK = GND, VDPM = LDO_OUT                            |     | 95   |     | μΑ   |

| VDD_1 Voltage                        |                    |                                                       | 7   |      | VGH | V    |

| VDD_1 Input Current                  | IVDD_1             | VFLK = VDPM = LDO_OUT                                 |     | 0.02 |     | μΑ   |

| CONTROL INPUT CHARACTERISTICS        |                    |                                                       |     |      |     |      |

| VFLK Voltage Low                     | VLOWFLK            |                                                       |     |      | 0.8 | V    |

| VFLK Voltage High                    | VHIGHFLK           |                                                       | 2.2 |      |     | V    |

| VFLK Input Current                   | IFLK               | $0.9 \le VFLK \le LDO_OUT$                            | -1  |      | +1  | μA   |

| VDPM Voltage Low                     | VLOWDPM            |                                                       |     |      | 0.8 | V    |

| VDPM Voltage High                    | VHIGHDPM           |                                                       | 2.2 |      |     | V    |

| VDPM Input Current                   | IVDPM              | $0.9 \le VDPM \le LDO_OUT$                            | -1  |      | +1  | μΑ   |

| SWITCHING CHARACTERISTICS            |                    |                                                       |     |      |     |      |

| VGH to VGH_M On Resistance           | R <sub>VGH</sub>   | VDPM = VFLK = LDO_OUT                                 |     | 60   |     | Ω    |

| VGH_M Discharge Current <sup>1</sup> | I <sub>VGH_M</sub> | VFLK < 0.8 V, RE = 33 k $\Omega$                      |     | 8.0  |     | mA   |

| DELAY CHARACTERISTICS                |                    |                                                       |     |      |     |      |

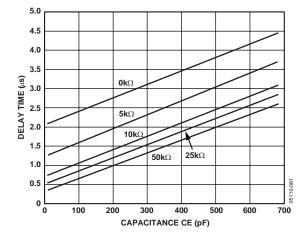

| Delay Time <sup>2</sup>              | T <sub>DELAY</sub> | $CE = 470 \text{ pF}, \text{RE} = 33 \text{ k}\Omega$ |     | 1.88 |     | μs   |

<sup>1</sup> Discharge current = 302.5/(RE + 5000).

<sup>2</sup> Delay time = CE  $\times$  4200.

### **GENERAL SPECIFICATIONS**

VIN\_1 = VIN\_2 =  $\overline{SHDN}$  = 5 V, T<sub>A</sub> = 25°C, unless otherwise noted.

### Table 5.

| Parameter                                                                | Symbol           | Conditions                            | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------|------------------|---------------------------------------|-----|-----|-----|------|

| SHUTDOWN                                                                 |                  |                                       |     |     |     |      |

| Input Voltage Low                                                        | VIL              |                                       |     |     | 0.8 | V    |

| Input Voltage High                                                       | VIH              |                                       | 2.2 |     |     | V    |

| Shutdown Pin Input Current                                               |                  | $GND \le \overline{SHDN} \le 5.5 V$   | -1  |     | +1  | μA   |

| Total Ground Current                                                     |                  | $\overline{\text{SHDN}} = \text{GND}$ |     | 2.0 |     | μA   |

| Total V <sub>IN</sub> Current (I <sub>VIN_1</sub> + I <sub>VIN_2</sub> ) |                  | SHDN = GND                            | -1  |     | +1  | μΑ   |

| UNDERVOLTAGE LOCKOUT                                                     |                  |                                       |     |     |     |      |

| UVLO Rising Threshold                                                    | VUVLOR           | VIN_1 rising                          |     | 2.8 |     | V    |

| UVLO Falling Threshold                                                   | VUVLOF           | VIN_1 falling                         |     | 2.6 |     | V    |

| QUIESCENT CURRENT                                                        |                  |                                       |     |     |     |      |

| Step-Up Regulator in Nonswitching State                                  | lq               |                                       |     | 300 | 500 | μΑ   |

| Step-Up Regulator in Switching State                                     | l <sub>QSW</sub> |                                       |     | 2   | 3   | mA   |

### ABSOLUTE MAXIMUM RATINGS

$T_A$ = 25°C, unless otherwise noted.

#### Table 6.

| Tuble 0:                                                                                                 |                 | -                             |

|----------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|

| Parameter                                                                                                | Symbol          | Rating                        |

| RE, CE, FB, SHDN, VIN_2, FREQ,<br>COMP, SS, VIN_1, LDO_OUT,<br>ADJ, VDPM, VFLK to GND,<br>PGND, and AGND |                 | –0.5 V to +6.5 V              |

| OUT, NEG and POS to GND,<br>PGND, and AGND                                                               |                 | –0.5 V to +16 V               |

| LX to GND, PGND, and AGND                                                                                |                 | –0.5 V to +22 V               |

| VDD_2 and OUT to GND, PGND,<br>and AGND                                                                  |                 | –0.5 V to +18.5<br>V          |

| Voltage Between GND and<br>AGND, GND and PGND, and<br>AGND and PGND                                      |                 | ±0.5 V                        |

| VDD_1, VGH, and VGH_M to<br>GND, PGND, and AGND                                                          |                 | –0.5 V to +32 V               |

| Differential Voltage Between<br>POS and NEG                                                              |                 | ±5 V                          |

| Package Power Dissipation                                                                                | PD              | $(T_J max - T_A)/\theta_{JA}$ |

| Thermal Resistance                                                                                       | θ <sub>JA</sub> | 38°C/W                        |

| Maximum Junction Temperature                                                                             | T₁max           | 125°C                         |

| Operating Temperature Range                                                                              | TA              | -40°C to +85°C                |

| Storage Temperature Range                                                                                | Ts              | –65°C to +150°C               |

| Reflow Peak Temperature<br>(20 sec to 40 sec)                                                            |                 | 250°C                         |

|                                                                                                          |                 |                               |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

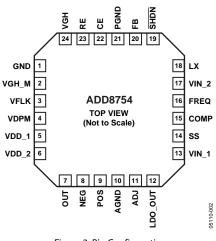

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

#### Table 7. Pin Function Descriptions

| Pin | Mnemonic | Description                                                                                                                                                                                     |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND      | Ground.                                                                                                                                                                                         |

| 2   | VGH_M    | Gate Pulse Modulator Output. This pin supplies the gate drive signal.                                                                                                                           |

| 3   | VFLK     | Gate Pulse Modulator Control Input.                                                                                                                                                             |

| 4   | VDPM     | Gate Pulse Modulator Enable. VGH_M is enabled when the voltage on this pin is more than 2.2 V. VGH_M goes to GND when this pin is connected to GND.                                             |

| 5   | VDD_1    | Gate Pulse Modulator Low Voltage Input.                                                                                                                                                         |

| 6   | VDD_2    | V <sub>COM</sub> Amplifier Supply.                                                                                                                                                              |

| 7   | OUT      | V <sub>COM</sub> Amplifier Output.                                                                                                                                                              |

| 8   | NEG      | Inverting Input of V <sub>COM</sub> Amplifier.                                                                                                                                                  |

| 9   | POS      | Noninverting Input of V <sub>COM</sub> Amplifier.                                                                                                                                               |

| 10  | AGND     | Analog Ground.                                                                                                                                                                                  |

| 11  | ADJ      | LDO Output Voltage Select. Refer to Table 13 for details.                                                                                                                                       |

| 12  | LDO_OUT  | LDO Output.                                                                                                                                                                                     |

| 13  | VIN_1    | Supply Input. This pin supplies power to the LDO and step-up switching regulator. Typically connected to VIN_2.                                                                                 |

| 14  | SS       | Soft Start. A capacitor must be connected between GND and this pin to set the soft start time.                                                                                                  |

| 15  | СОМР     | Compensation for the Step-Up Converter. A capacitor and resistor are connected in series between GND and this pin for stable operation.                                                         |

| 16  | FREQ     | Frequency Select. Set the switching frequency with a logic level. The step-up switching regulator operates at 650 kHz when this pin is connected to GND and at 1.2 MHz when connected to VIN_1. |

| 17  | VIN_2    | Step-Up Switching Regulator Power Supply. This pin supplies power to the driver for the switch. Typically connected to VIN_1.                                                                   |

| 18  | LX       | Step-Up Switching Regulator Switch Node.                                                                                                                                                        |

| 19  | SHDN     | Device Shutdown Pin. This pin allows users to shut the device off when connected to GND. The normal operating mode is to pull this pin to VIN_1.                                                |

| 20  | FB       | Feedback Voltage Sense to Set the Output Voltage of the Step-Up Switching Regulator.                                                                                                            |

| 21  | PGND     | Step-Up Switching Regulator Power Ground.                                                                                                                                                       |

| 22  | CE       | GPM Time Delay. A capacitor must be connected between GND and this pin to set the delay time.                                                                                                   |

| 23  | RE       | GPM Negative Ramp Rate. A resistor must be connected between GND and this pin to set the negative ramp rate.                                                                                    |

| 24  | VGH      | Gate Pulse Modulator High Voltage Input.                                                                                                                                                        |

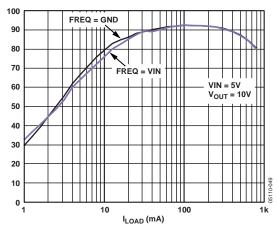

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 3. Efficiency vs. Load Current (mA)

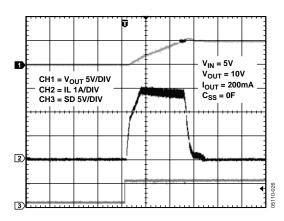

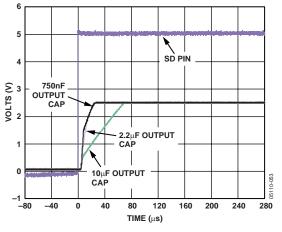

Figure 4. Start-Up Response from Shutdown,  $C_{SS} = 0 F$

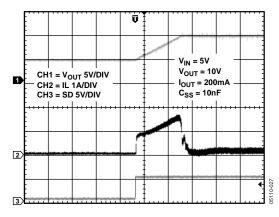

Figure 5. Start-Up Response from Shutdown, C<sub>SS</sub> = 10 F

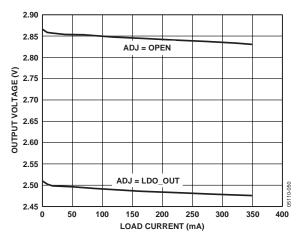

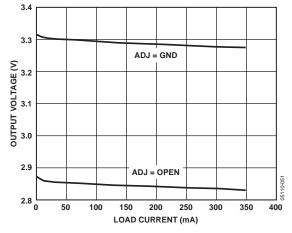

Figure 6. LDO Output Voltage vs. Load Current, VIN = 3.3 V

*Figure 7. LDO Output Voltage vs. Load Current, VIN = 5 V*

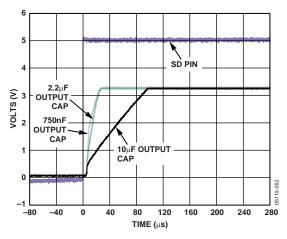

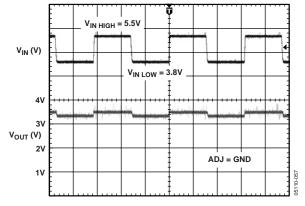

Figure 8. LDO Power-Up Response from Shutdown

Rev. 0 | Page 9 of 28

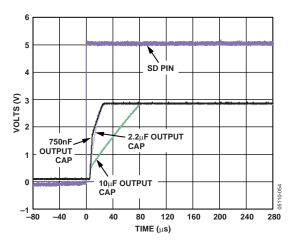

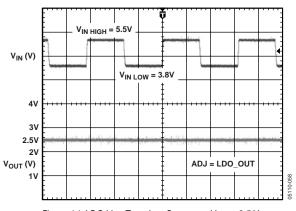

Figure 9. LDO Power-Up Response from Shutdown

Figure 10. LDO Power-Up Response from Shutdown

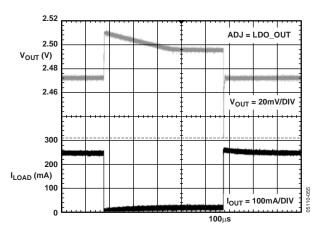

Figure 11. LDO Load Transient Response,  $V_{OUT} = 2.5 V$

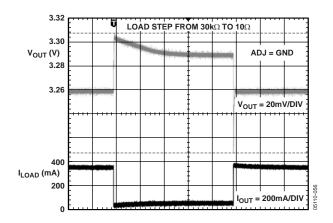

Figure 12. LDO Load Transient Response, Vout = 3.3 V

Figure 13. LDO Line Transient Response, Vout = 3.3 V

Figure 14. LDO Line Transient Response,  $V_{OUT} = 2.5 V$

Rev. 0 | Page 10 of 28

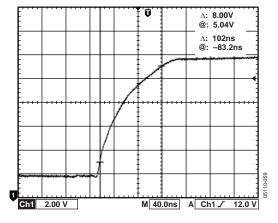

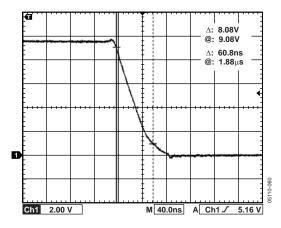

Figure 15.  $V_{COM}$  Rising Slew Rate,  $VDD_2 = 14 V$

Figure 17. GPM Delay Time vs. CE Capacitance

Figure 16. V<sub>COM</sub> Falling Slew Rate, VDD\_2 = 14 V

### **THEORY OF OPERATION**

Figure 18. Detailed Functional Block Diagram

# CURRENT-MODE, STEP-UP SWITCHING REGULATOR OPERATION

The ADD8754 uses current mode to regulate the output voltage. This current-mode regulation system allows fast transient response while maintaining a stable output voltage. By selecting the proper resistor-capacitor network from COMP to GND, the regulator response can be optimized for a wide range of input voltages, output voltages, and load conditions.

### **Frequency Selection**

The ADD8754's frequency is user-selectable to operate either at 650 kHz to optimize the regulator for high efficiency or at 1.2 MHz for small external components. Connect FREQ to VIN\_2 for 1.2 MHz operation, or connect FREQ to GND for 650 kHz operation.

### Soft Start Capacitor

The voltage at SS ramps up slowly by charging the soft start capacitor ( $C_{SS}$ ) with an internal 2.5  $\mu$ A current source. Table 8 lists the values for the soft start period based on maximum output current and maximum switching frequency.

The soft start capacitor limits the rate of voltage rise on the COMP pin, which in turn limits the peak switch current at startup. Table 8 shows a typical soft start period,  $t_{SS}$ , at the maximum output current,  $I_{OUT\_MAX}$ , for several conditions.

A 20 nF soft start capacitor results in negligible input-current overshoot at startup, making it suitable for most applications. However, if an unusually large output capacitor is used, a longer soft start period is required to prevent large input inrush current.

| Table 8. Typical Soft Start P | Period |

|-------------------------------|--------|

|-------------------------------|--------|

| V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | C <sub>ουτ</sub> (μF) | C <sub>ss</sub> (nF) | t <sub>ss</sub> (ms) |

|---------------------|----------------------|-----------------------|----------------------|----------------------|

| 3.3                 | 9                    | 10                    | 20                   | 2.5                  |

| 3.3                 | 9                    | 10                    | 100                  | 8.2                  |

| 3.3                 | 12                   | 10                    | 20                   | 3.5                  |

| 3.3                 | 12                   | 10                    | 100                  | 15                   |

| 5                   | 9                    | 10                    | 20                   | 0.4                  |

| 5                   | 9                    | 10                    | 100                  | 1.5                  |

| 5                   | 12                   | 10                    | 20                   | 0.62                 |

| 5                   | 12                   | 10                    | 100                  | 2                    |

### **On/Off Control**

The SHDN input turns the ADD8754 on or off. When the stepup dc-to-dc converter is turned off, there is a dc path from the input to the output through the inductor and output diode. This causes the output voltage to remain slightly below the input voltage by the forward voltage of the diode, preventing the output voltage from dropping to zero when the regulator is shut down. See Figure 25 for the typical application circuit to disconnect the output voltage from the input voltage at shutdown.

### Setting the Output Voltage

The ADD8754 features an adjustable output voltage range of  $(V_{IN} + 2 V)$  to 20 V. The output voltage is set by the resistive voltage divider from the output voltage  $(V_{OUT})$  to the 1.21 V feedback input at FB. Use the following formula to determine the output voltage:

$$V_{OUT} = 1.21 \text{ V} \times (1 + R1/R2) \tag{1}$$

Use an R2 resistance of 10 k $\Omega$  or less to prevent output voltage errors due to the 10 nA FB input bias current. Choose R1 based on the following formula:

$$R1 = R2 \times \left(\frac{V_{OUT} - 1.21 V}{1.21 V}\right)$$

For example,  $R1 = 75.8 \text{ k}\Omega$

with

$$V_{OUT} = 10$$

V and  $R2 = 10$  k $\Omega$  (2)

#### Inductor Selection

The inductor is an integral part of the step-up converter. It stores energy during the switch-on time and transfers that energy to the output through the output diode during the switch-off time. Use inductance in the range of 1  $\mu$ H to 22  $\mu$ H. In general, lower inductance values have higher saturation current and lower series resistance for a given physical size. However, lower inductance results in higher peak current, which can lead to reduced efficiency and greater input and/or output ripple and noise. Peak-to-peak inductor ripple current at close to 30% of the maximum dc input current typically yields an optimal compromise.

For determining the inductor ripple current, the input  $(V_{\rm IN})$  and output  $(V_{\rm OUT})$  voltages determine the switch duty cycle (D) by the following equation:

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}} \tag{3}$$

Using the duty cycle and switching frequency,  $f_{SW}$ , determine the on time by using the following equation:

$$t_{\rm ON} = \frac{D}{f_{\rm SW}} \tag{4}$$

The inductor ripple current ( $\Delta I_L$ ) in steady state is

$$\Delta I_L = \frac{V_{IN} \times t_{ON}}{L} \tag{5}$$

Solving for the inductance value, *L*,

$$L = \frac{V_{IN} \times t_{ON}}{\Delta I_L} \tag{6}$$

Make sure that the peak inductor current (the maximum input current plus half of the inductor ripple current) is less than the rated saturation current of the inductor. In addition, ensure that the maximum rated rms current of the inductor is greater than the maximum dc input current to the regulator.

For duty cycles greater than 50% that occur with input voltages greater than half the output voltage, slope compensation is required to maintain stability of the current-mode regulator. For stable current-mode operation, ensure that the selected inductance is equal to or greater than L<sub>MIN</sub>:

$$L > L_{MIN} = \frac{V_{OUT} - V_{IN}}{1.8 \, \text{A} \times f_{SW}} \tag{7}$$

| Vendor            | Part          | L (µH) | Max DC Current | Max DCR (mΩ) | Height (mm) |

|-------------------|---------------|--------|----------------|--------------|-------------|

| Sumida            | CMD4D11-2R2MC | 2.2    | 0.95           | 116          | 1.2         |

| www.sumida.com    | CMD4D11-4R7MC | 4.7    | 0.75           | 216          | 1.2         |

|                   | CDRH4D28-100  | 10     | 1.00           | 128          | 3.0         |

|                   | CDRH5D18-220  | 22     | 0.80           | 290          | 2.0         |

|                   | CR43-4R7      | 4.7    | 1.15           | 109          | 3.5         |

|                   | CR43-100      | 10     | 1.04           | 182          | 3.5         |

| Coilcraft         | DS1608-472    | 4.7    | 1.40           | 60           | 2.9         |

| www.coilcraft.com | DS1608-103    | 10     | 1.00           | 75           | 2.9         |

| Toko              | D52LC-4R7M    | 4.7    | 1.14           | 87           | 2.0         |

| www.tokoam.com    | D52LC-100M    | 10     | 0.76           | 150          | 2.0         |

### Table 9. Inductor Manufacturers

#### Choosing the Input and Output Capacitors

The ADD8754 requires input and output bypass capacitors to supply transient currents while maintaining a constant input and output voltage. Use a low effective series resistance (ESR) 10  $\mu$ F or greater input capacitor to prevent noise at the ADD8754 input. Place the capacitors between VIN\_1, VIN\_2, and GND and as close as possible to the ADD8754. Ceramic capacitors are preferred because of their low ESR characteristics. Alternatively, use a high value, medium ESR capacitor in parallel with a 0.1  $\mu$ F low ESR capacitor as close as possible to the ADD8754.

The output capacitor maintains the output voltage and supplies current to the load while the ADD8754 switch is on. The value and characteristics of the output capacitor greatly affect the output voltage ripple and stability of the regulator. Use a low ESR output capacitor; ceramic dielectric capacitors are preferred.

For very low ESR capacitors such as ceramic capacitors, the ripple current due to the capacitance is calculated as follows. Because the capacitor discharges during the on time,  $t_{ON}$ , the charge removed from the capacitor,  $Q_{C}$ , is the load current multiplied by the on time. Therefore, the output voltage ripple ( $\Delta V_{OUT}$ ) is

$$\Delta V_{OUT} = \frac{Q_C}{C_{OUT}} = \frac{I_L \times t_{ON}}{C_{OUT}}$$

(8)

where:

$C_{OUT}$  is the output capacitance.

$I_L$  is the average inductor current.

$$t_{\rm ON} = \frac{D}{f_{\rm SW}} \tag{9}$$

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}} \tag{10}$$

Choose the output capacitor based on the following equation:

$$C_{OUT} \ge \frac{I_L \times (V_{OUT} - V_{IN})}{f_{SW} \times V_{OUT} \times \Delta V_{OUT}}$$

(11)

#### Table 10. Capacitor Manufacturers

| Vendor      | Web Address        |

|-------------|--------------------|

| AVX         | www.avxcorp.com    |

| Murata      | www.murata.com     |

| Sanyo       | www.sanyovideo.com |

| Taiyo Yuden | www.t-yuden.com    |

#### **Diode Selection**

The output diode conducts the inductor current to the output capacitor and load while the switch is off. For high efficiency, minimize the forward voltage drop of the diode. Schottky diodes are recommended. However, for high voltage, high temperature applications, where the Schottky diode reverse leakage current becomes significant and can degrade efficiency, use an ultrafast junction diode.

The diode must be rated to handle the average output load current. Many diode manufacturers derate the current capability of the diode as a function of the duty cycle. Verify that the output diode is rated to handle the average output load current with the minimum duty cycle. The minimum duty cycle of the ADD8754 is

$$D_{MIN} = \frac{V_{OUT} - V_{IN} MAX}{V_{OUT}}$$

(12)

where  $V_{IN\_MAX}$  is the maximum input voltage.

For example,  $D_{MIN} = 0.45$  when  $V_{OUT} = 10$  V and  $V_{IN\_MAX} = 5.5$  V

#### Table 11. Schottky Diode Manufacturers

| Vendor                      | Web Address         |

|-----------------------------|---------------------|

| ON Semiconductor            | www.onsemi.com      |

| Diodes, Inc.                | www.diodes.com      |

| Central Semiconductor Corp. | www.centralsemi.com |

| Sanyo                       | www.sanyovideo.com  |

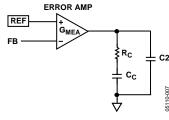

#### **Loop Compensation**

Use of external components to compensate the regulator loop allows optimization of the loop dynamics for a given application. A step-up converter produces an undesirable right-half plane zero in the regulation feedback loop. This requires compensating the regulator such that the crossover frequency occurs well below the frequency of the right-half plane zero. The right-half plane zero is determined by the following equation:

$$F_Z(RHP) = \left(\frac{V_{IN}}{V_{OUT}}\right)^2 \times \frac{R_{LOAD}}{2\pi \times L}$$

(13)

where:

$F_Z(RHP)$  is the right-half plane zero.

$R_{LOAD}$  is the equivalent load resistance, or the output voltage divided by the load current.

To stabilize the regulator, make sure that the regulator crossover frequency is less than or equal to one-fifth of the right-half plane zero and less than or equal to one-fifteenth of the switching frequency.

The regulator loop gain is

$$A_{VL} = \frac{V_{FB}}{V_{OUT}} \times \frac{V_{IN}}{V_{OUT}} \times G_{MEA} \times \left| Z_{COMP} \right| \times G_{CS} \times \left| Z_{OUT} \right|$$

(14)

where:

$A_{VL}$  is the loop gain.

$V_{FB}$  is the feedback regulation voltage, 1.210 V.

$V_{OUT}$  is the regulated output voltage.

$V_{IN}$  is the input voltage.

$G_{MEA}$  is the error amplifier transconductance gain.

$Z_{\ensuremath{\textit{COMP}}}$  is the impedance of the series RC network from COMP to GND.

$G_{CS}$  is the current sense transconductance gain (the inductor current divided by the voltage at COMP), which is internally set by the ADD8754.

Z<sub>OUT</sub> is the impedance of the load and output capacitor.

To determine the crossover frequency, it is important to note that at that frequency the compensation impedance ( $Z_{COMP}$ ) is dominated by the resistor and the output impedance ( $Z_{OUT}$ ) is dominated by the impedance of the output capacitor. Therefore, when solving for the crossover frequency, (by definition of the crossover frequency) the equation is simplified to

$$\left|A_{VL}\right| = \frac{V_{FB}}{V_{OUT}} \times \frac{V_{IN}}{V_{OUT}} \times G_{MEA} \times R_C \times G_{CS} \times \frac{1}{2\pi \times f_C \times C_{OUT}} = 1 \quad (15)$$

where:

$f_c$  is the crossover frequency.  $R_c$  is the compensation resistor.

Solving for R<sub>C</sub>,

m 11 40 D

$$R_{C} = \frac{2\pi \times f_{C} \times C_{OUT} \times V_{OUT} \times V_{OUT}}{V_{FB} \times V_{IN} \times G_{MEA} \times G_{CS}}$$

(16)

1 .....

For  $V_{FB} = 1.21$  V,  $G_{MEA} = 100 \ \mu$ s, and  $G_{CS} = 2$  sec,

$$R_{C} = \frac{2.55 \times 10^{4} \times f_{C} \times C_{OUT} \times V_{OUT} \times V_{OUT}}{V_{IN}}$$

(17)

Once the compensation resistor is known, set the zero formed by the compensation capacitor and resistor to one-fourth of the crossover frequency, or

$$C_C = \frac{2}{\pi \times f_C \times R_C} \tag{18}$$

where  $C_c$  is the compensation capacitor.

Figure 19. Compensation Components

The capacitor C2 is chosen to cancel the zero introduced by output capacitance ESR.

Solving for C2,

$$C2 = \frac{ESR \times C_{OUT}}{R_C}$$

(19)

For low ESR output capacitance, such as with a ceramic capacitor, C2 is optional. For optimal transient performance, the R<sub>c</sub> and C<sub>c</sub> might need to be adjusted by observing the load transient response of the ADD8754. For most applications, the compensation resistor should be in the range of 30 k $\Omega$  to 400 k $\Omega$ , and the compensation capacitor should be in the range of 100 pF to 1.2 nF. Table 12 shows external component values for several applications.

....

| Table 12. | Recommen | ded Externa | I Compone | nts for Vari | ous Input/C | Jutput Volta | age Conditio | ons |

|-----------|----------|-------------|-----------|--------------|-------------|--------------|--------------|-----|

|           |          |             |           |              |             |              |              |     |

| V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | <b>f</b> sw | L (µH) | C <sub>ουτ</sub> (μF) | C <sub>IN</sub> (μF) | R <sub>1</sub> (kΩ) | R₂ (kΩ) | R <sub>c</sub> (kΩ) | C <sub>c</sub> (pF) | I <sub>OUT_MAX</sub> (mA) |

|---------------------|----------------------|-------------|--------|-----------------------|----------------------|---------------------|---------|---------------------|---------------------|---------------------------|

| 5                   | 9                    | 650 kHz     | 10     | 10                    | 10                   | 63.4                | 10      | 84.5                | 390                 | 450                       |

| 5                   | 9                    | 1.2 MHz     | 4.7    | 10                    | 10                   | 63.4                | 10      | 178                 | 100                 | 450                       |

| 5                   | 12                   | 650 kHz     | 10     | 10                    | 10                   | 88.7                | 10      | 140                 | 220                 | 350                       |

| 5                   | 12                   | 1.2 MHz     | 4.7    | 10                    | 10                   | 88.7                | 10      | 300                 | 100                 | 350                       |

| 3.3                 | 9                    | 650 kHz     | 10     | 10                    | 10                   | 63.4                | 10      | 71.5                | 820                 | 350                       |

| 3.3                 | 9                    | 1.2 MHz     | 4.7    | 10                    | 10                   | 63.4                | 10      | 150                 | 180                 | 350                       |

| 3.3                 | 12                   | 650 kHz     | 10     | 10                    | 10                   | 88.7                | 10      | 130                 | 420                 | 250                       |

| 3.3                 | 12                   | 1.2 MHz     | 4.7    | 10                    | 10                   | 88.7                | 10      | 280                 | 100                 | 250                       |

### **V**<sub>COM</sub> AMPLIFIER

The output of the  $V_{\rm COM}$  amplifier is designed to control the voltage on the  $V_{\rm COM}$  plane of the LCD display. The  $V_{\rm COM}$  amplifier is designed to source and sink the capacitive pulse current and ensure stable operation with high load capacitance.

#### Input Overvoltage Protection

Whenever the input exceeds the supply voltage, attention must be paid to the input overvoltage characteristics. When an overvoltage occurs, the amplifier can be damaged, depending on the voltage level and the magnitude of the fault current. When the input voltage exceeds the supply voltage by more than 0.6 V, the internal pin junctions allow current to flow from the input to the supplies. This input current is not inherently damaging to the device, provided it is 5 mA or less.

#### **Short-Circuit Output Conditions**

The  $V_{\rm COM}$  amplifier does not have internal short-circuit protection circuitry. As a precaution, do not short the output directly to the positive power supply or to the ground.

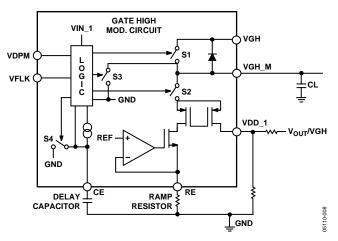

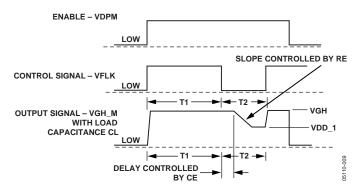

### GATE PULSE MODULATOR CIRCUIT

The gate pulse modulator is used for LCD applications in which shaping of the gate high voltage signal improves image quality. A charge pump is used to generate the on voltage, VGH. A lower gate voltage level, VDD\_1, is desired during the last portion of the gate's on time and is provided by VOUT. The integrated gate pulse modulator circuit provides control over the slope and delay of the transition between these two TFT on-voltage levels.

The gate pulse modulator circuit has four input pins (VGH, VDD\_1, VDPM, and VFLK) and one output pin (VGH\_M). VFLK is a digital control signal, usually provided by the timing controller, whose high or low level determines which of the two input voltages, VGH or VDD\_1, is passed through to VGH\_M. The gate high modulator circuit becomes active when the voltage on pin VDPM exceeds the turn-on threshold value of 2.2 V.

When the control voltage VFLK switches from logic low to logic high during normal operation with VDPM at logic high (see Figure 21), the output voltage VGH\_M transitions from VDD\_1 to VGH. When the control voltage VFK switches from logic high to logic low, the output voltage VGH\_M transitions from VGH to VDD\_1 after a time delay determined by the size of a capacitor from the CE pin to the GND and a slew rate determined by the size of resistor from the RE pin to the GND. The delay capacitance in farad is calculated using the following equation:

$CE = (Delay Time) \times 0.000238$

The RE in ohms is calculated using the following equation:

$$RE = \frac{302}{\left(Slew \ Rate \times Load \ Capacitance\right)} - 5000$$

When the voltage on the VDPM pin is less than the turn-on threshold value, the CE pin is internally connected to GND to discharge the delay capacitor.

Figure 20. Gate Pulse Modulator Functional Block Diagram

Figure 21. Gate Pulse Modulator Timing Diagram

### **POWER-UP SEQUENCE**

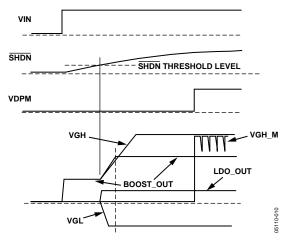

Most LCD panels require that when VIN is applied, LDO\_OUT, VGL, BOOST\_OUT, VGH, and VGH\_M are established sequentially, as indicated in Figure 22. ADD8754 provides this sequence with appropriate capacitors for the VGL and VGH charge pumps.

Figure 22. Power-Up Sequence Timing Diagram

#### LDO Regulator

The ADD8754 low dropout (LDO) regulator has three preset output voltage settings. As shown in Table 13, by tying the ADJ pin low, a 3.3 V nominal output is selected. By tying ADJ to the output voltage, a 2.5 V nominal output is selected. By leaving ADJ as an open circuit, a nominal voltage of 2.85 V is selected.

| LDO Output Voltage | ADJ Pin       |

|--------------------|---------------|

| 2.5 V              | LDO_OUT       |

| 2.85 V             | No connection |

| 3.3 V              | GND           |

#### LDO Input Capacitor Selection

For the input voltage of the ADD8754 LDO regulator (VIN\_1), a local bypass capacitor is recommended. The input capacitor provides bypassing for the internal amplifier used in the voltage regulation loop. Use at least a 1  $\mu$ F low ESR capacitor. Larger input capacitance and lower ESR provide better supply noise rejection. Multilayer ceramic chip (MLCC) capacitors provide the best combination of low ESR and small size.

#### LDO Output Capacitor Selection

The output capacitor improves the regulator response to sudden load changes. The output capacitor helps determine the performance of any LDO. The ADD8754 LDO requires at least a 2.2  $\mu$ F capacitor. Transient response is a function of output capacitance, in that larger values of output capacitance decrease peak deviations, providing improved transient response for large load current changes.

Choose the capacitors by comparing their lead inductance, ESR, and dissipation factor. Output capacitance affects stability, and a larger cap provides a greater phase margin for the ADD8754 LDO. MLCC capacitors provide the best combination of low ESR and small size.

Note that the capacitance of some capacitor types show wide variations over temperature. A good quality dielectric X7R or better capacitor is recommended.

### SHUTDOWN

Applying a TTL high signal to the shutdown pin (tying it to the VIN\_1) turns on all outputs. Pulling SHDN down to 0.4 V or below (tying it to GND) turns off all outputs. In shutdown mode, quiescent current is reduced to a typical value of 300  $\mu$ A.

### UVLO

An undervoltage lockout (UVLO) circuit is included with a built in hysteresis. ADD8754 turns on when VIN\_1 rises above 2.8 V and shuts down when VIN\_1 falls below 2.6 V.

### **POWER DISSIPATION**

The ADD8754's maximum power dissipation depends on the thermal resistance from the IC die to the ambient environment and the ambient temperature. The thermal resistance depends on the IC package, PC board copper area, other thermal mass, and airflow. The ADD8754, with the exposed backside pad soldered to a 2-layer PC board with nine 12 mil-diameter thermal vias, can dissipate about 1.5 W into 65°C still air before the die exceeds 125°C. More PC board copper, cooler ambient air, and more airflow increase the dissipation capability, whereas less copper or warmer air decreases the IC's dissipation capability. The major contributors to the power dissipation are the LDO regulator and the  $V_{COM}$  amplifier.

#### Step-Up Converter

The largest portions of power dissipation in the step-up converter are the internal MOSFET, the inductor, and the output diode. For a 90% efficiency step-up converter, about 3% to 5% of the power is lost in the internal MOSFET, about 3% to 4% in the inductor, and about 1% in the output diode. The rest of the 1% to 3% is distributed among the input and output capacitors and the PC board traces. For an input power of about 3 W, the power lost in the internal MOSFET is about 90 mW to 150 mW.

#### LDO

The power dissipated in the LDO depends on the output current, the output voltage, and the supply voltage:

$PD_{LDO} = (VIN_1 - LDO_OUT) \times I_{LDO_OUT}$

#### V<sub>COM</sub> Amplifier

The power dissipated in the  $V_{\text{COM}}$  amplifier depends on the output current, the output voltage, and the supply voltage:

$PD_{SOURCE} = I_{OUT} (source) \times (VDD_2 - V_{OUT})$

$PD_{SINK} = I_{OUT} (sink) \times V_{OUT}$

where:

$I_{OUT}$  (*source*) is the output current sourced by the  $V_{\rm COM}$  amplifier.

$I_{OUT}\,(sink)$  is the output current that the  $V_{\rm COM}$  amplifier sinks to AGND.

In a typical case where the supply voltage is 12 V and the output voltage is 6 V with an output source current of 20 mA, the power dissipated is 120 mW.

#### **Thermal Overload Protection**

Thermal overload protection prevents excessive power dissipation from overheating the ADD8754. When the junction temperature exceeds  $T_J = 145^{\circ}$ C, a thermal sensor immediately activates the fault protection, which shuts down the device, allowing the IC to cool. The device self-starts once the die temperature falls below  $T_J = 105^{\circ}$ C.

Thermal overload protection protects the controller in the event of fault conditions. For continuous operation, do not exceed the absolute maximum junction temperature rating of  $T_I = 125^{\circ}C$ .

### LAYOUT GUIDELINES

When designing a high frequency, switching, regulated power supply, layout is very important. Using a good layout can solve many problems associated with these types of supplies. Some of the main problems are loss of regulation at high output current and/or large input-to-output voltage differentials, excessive noise on the output and switch waveforms, and instability. Using the following guidelines can help minimize these problems.

Make all power (high current) traces as short, direct, and thick as possible. It is good practice on a standard PCB board to make the traces an absolute minimum of 15 mil (0.381 mm) per Ampere. The inductor, output capacitors, and output diode should be as close to each other as possible. This helps reduce the EMI radiated by the power traces that is due to the high switching currents through them. This also reduces lead inductance and resistance, which in turn reduce noise spikes, ringing, and resistive losses that produce voltage errors.

The grounds of the IC, input capacitors, output capacitors, and output diode (if applicable), should be connected close together, directly to a ground plane. It is also a good idea to have a ground plane on both sides of the printed circuit board (PCB). This reduces noise by reducing ground-loop errors and absorbing more of the EMI radiated by the inductor.

For multilayer boards of more than two layers, a ground plane can be used to separate the power plane (power traces and components) and the signal plane (feedback, compensation, and components) for improved performance. On multilayer boards, the use of vias is required to connect traces and different planes. If a trace needs to conduct a significant amount of current from one plane to the other, it is good practice to use one standard via per 200 mA of current. Arrange the components so that the switching current loops curl in the same direction.

Due to the how switching regulators operate, there are two power states: one state when the switch is on, and one when the switch is off. During each state, there is a current loop made by the power components currently conducting. Place the power components so that the current loop is conducting in the same direction during each of the two states. This prevents magnetic field reversal caused by the traces between the two half cycles and reduces radiated EMI.

#### Layout Procedure

To achieve high efficiency, good regulation, and stability, a good PCB layout is required. It is recommended that the reference board layout be followed as closely as possible because it is already optimized for high efficiency and low noise.

Use the following general guidelines when designing PCBs:

- 1. Keep CIN close to the IN and GND leads of the ADD8754.

- 2. Keep the high current path from CIN (through L1) to the SW and PGND leads as short as possible.

- 3. Keep the high current path from CIN (through L1), D1, and COUT as short as possible.

- 4. Keep high current traces as short and wide as possible.

- 5. Keep nodes connected to SW away from sensitive traces such as FB or COMP to prevent coupling of the traces. If these traces need to be run near each other, place a ground trace between the two as a shield.

- 6. Place the feedback resistors as close as possible to the FB pin to prevent noise pickup.

- 7. Place the compensation components as close as possible to the COMP pin.

- 8. Avoid routing noise-sensitive traces near the high current traces and components.

- 9. Use a thermal pad size that is the same as the dimension of the exposed pad on the bottom of the package.

#### **Heat Sinking**

When using a surface-mount power IC or external power switches, the PCB can often be used as the heat sink. This is done by simply using the copper area of the PCB to transfer heat from the device.

## **TYPICAL APPLICATION CIRCUITS**

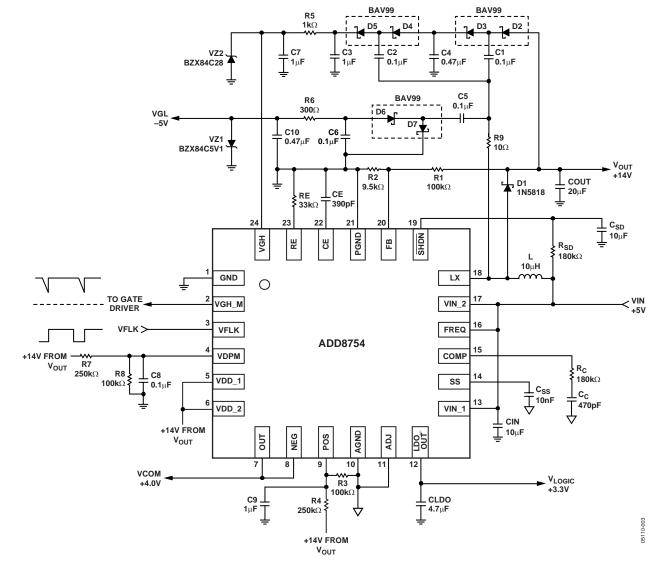

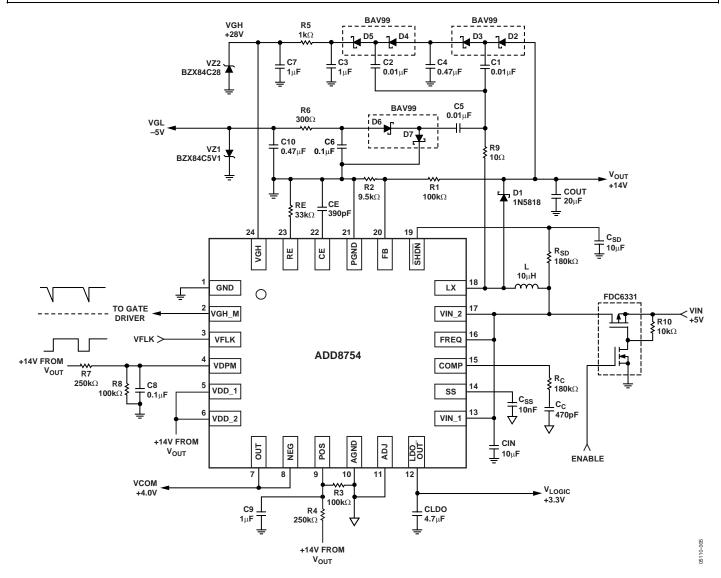

Figure 23. 1.2 MHz Application Circuit for TFT LCD Panel with Charge Pumps for VGH and VGL

Rev. 0 | Page 20 of 28

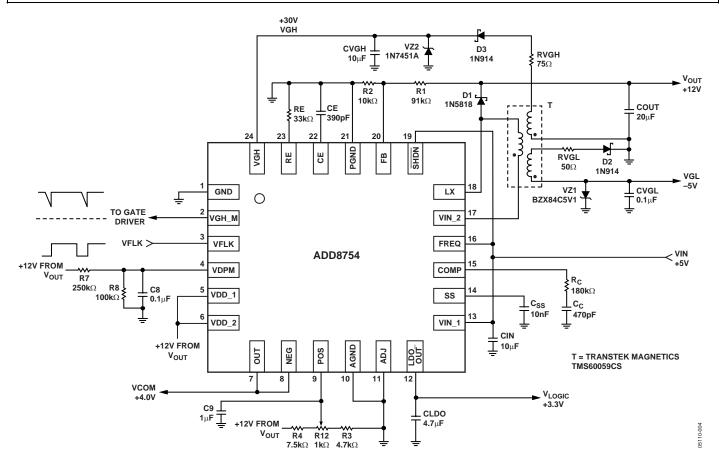

Figure 24. 1.2 MHz Application Circuit for TFT LCD Display with Transformer for VGH and VGL

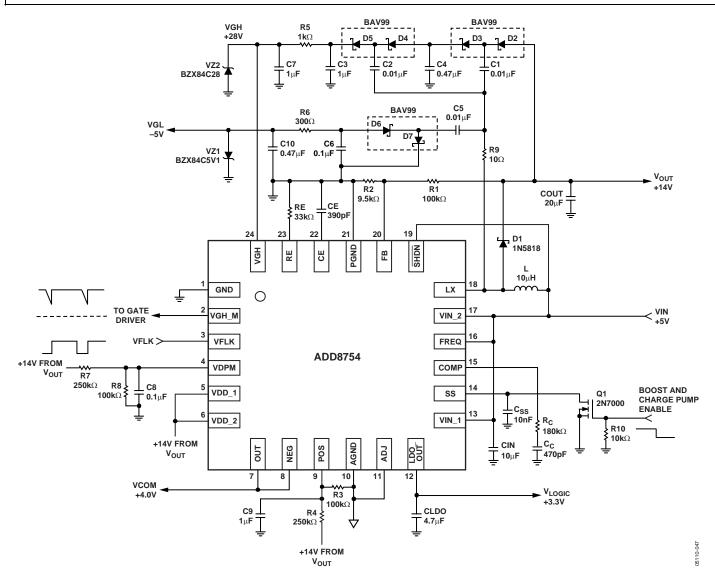

Figure 25. 1.2 MHz Application Circuit for TFT LCD Display with Charge Pumps with Input Power Disconnect Switch

Figure 26. 1.2 MHz Application Circuit for TFT LCD Display with LDO\_ALWAYS\_ON

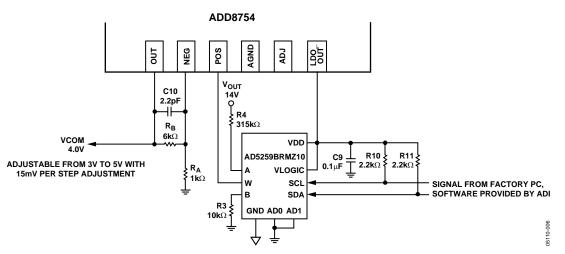

Figure 27. ADD8754 with Programmable V<sub>COM</sub>

The  $V_{COM}$  calibration for flicker reduction is one of the essential steps in the panel manufacturing process. In a typical panel production environment, such a process can take additional time to complete and, therefore, impacts production throughput. One additional concern is that a potentiometer typically used only for calibration offers limited resolution. The resistance can drift over time and can be noticeable after a few years of operation. The production throughput, image quality, and panel reliability concerns can all be solved by using a digital potentiometer. As shown in Figure 27, AD5259, a low cost 256-step digital potentiometer with nonvolatile memory, can calibrate the ADD8754  $V_{COM}$  voltage precisely, reliably, and time efficiently.

In the worst case, where the temperature, aging effect, and resistance tolerance of the AD5259 are all accounted for, the circuit in Figure 27 makes the  $V_{COM}$  voltage adjustable from 3.0 V to 5.0 V with 15 mV per step adjustment. A micro-

controller or I<sup>2</sup>C programmer can be used to provide the control signal for the AD5259, but ADI provides programming software that simplifies the calibration process. The software can be installed in the factory computer, and two tester probes can be connected to the computer's parallel port to implement the  $V_{COM}$  programming.

The  $V_{\mbox{\scriptsize COM}}$  voltage can be calculated as

$$V_{COM} = \frac{\frac{D}{256} \times R_{AB} + R_3}{R_4 + R_{AB} + R_3} \times 7 \times V_{OUT}$$

where:

D is the decimal code of the AD5259 programmable resistance between the W-to-B terminals.  $R_{AB}$  is the AD5259 nominal resistance.

## **OUTLINE DIMENSIONS**

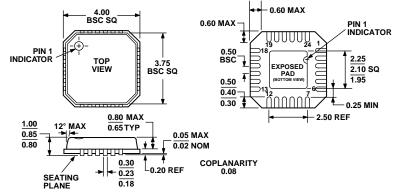

COMPLIANT TO JEDEC STANDARDS MO-220-VGGD-2

Figure 28. 24-Lead Lead Frame Chip Scale Package [LFCSP\_VQ] 4 × 4 mm Body, Very Thin Quad (CP-24-1) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                          | Temperature Range | Package Description | Package Option | Quantity |

|--------------------------------|-------------------|---------------------|----------------|----------|

| ADD8754ACPZ-Reel <sup>1</sup>  | -40°C to +85°C    | 24-Lead LFCSP_VQ    | CP-24-1        | 5,000    |

| ADD8754ACPZ-Reel7 <sup>1</sup> | -40°C to +85°C    | 24-Lead LFCSP_VQ    | CP-24-1        | 1,500    |

$^{1}$  Z = Pb-free part.

## NOTES

## NOTES

## NOTES

©2005 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D05110-0-4/05(0)

Rev. 0 | Page 28 of 28

www.analog.com

Downloaded from Elcodis.com electronic components distributor