# ICs for Communications

ISDN Echocancellation Circuit for Terminal Applications IEC-Q TE

PSB 21911 Version 5.2

PSF 21911 Version 5.2

Data Sheet 11.97

| PSB 21911<br>Revision Hi | istory:        | Original Version: 11.97   |

|--------------------------|----------------|---------------------------|

| Previous Re              | leases:        | None                      |

| Page                     | Subjects (chan | nges since last revision) |

|                          |                |                           |

|                          |                |                           |

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide: see our webpage at http://www.siemens.de/Semiconductor/address/address.htm.

Edition 11.97

Published by Siemens AG, HL TS, Balanstraße 73, 81541 München

© Siemens AG 28,11.97.

O Siemens AG 28.11.97

All Rights Reserved.

### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table of C | Contents                                      | age |

|------------|-----------------------------------------------|-----|

| 1          | Overview                                      |     |

| 1.1        | Features                                      | 9   |

| 1.2        | Logic Symbol µP Mode                          | .10 |

| 1.3        | Logic Symbol Stand-Alone Mode                 | .11 |

| 1.4        | Pin Configuration                             | .12 |

| 1.5        | Pin Definitions and Functions                 |     |

| 1.6        | Microprocessor Bus Interface (Overview)       | .21 |

| 1.7        | System Integration                            |     |

| 1.7.1      | ISDN PC Adapter Card                          |     |

| 1.7.2      | ISDN Stand-Alone Terminal with POTS Interface | .23 |

| 1.7.3      | ISDN Feature Phone                            |     |

| 1.7.4      | ISDN-Modem PC Card                            | .25 |

| 2          | Functional Description                        | .26 |

| 2.1        | Operating Modes                               |     |

| 2.2        | Device Architecture                           |     |

| 2.3        | IOM-2 Interface                               |     |

| 2.3.1      | IOM-2 Frame Structure                         |     |

| 2.3.2      | IOM-2 Command / Indication Channels           |     |

| 2.3.3      | IOM-2 Monitor Channel                         |     |

| 2.3.4      | Activation/Deactivation of IOM-2 Clocks       |     |

| 2.3.5      | Superframe Marker                             |     |

| 2.3.6      | iOM-2 Output Driver Selection                 |     |

| 2.4        | Microprocessor Interface                      |     |

| 2.4.1      | Microprocessor Clock Output                   |     |

| 2.4.2      | Watchdog Timer                                |     |

| 2.5        | U-Transceiver                                 |     |

| 2.5.1      | U-Frame Structure                             | .42 |

| 2.5.2      | EOC-Processor and MON-0                       | .51 |

| 2.5.3      | Maintenance (MON-1)                           | .54 |

| 2.5.4      | Overhead Bits (MON-2)                         |     |

| 2.5.5      | Local Functions (MON-8)                       | .59 |

| 2.5.6      | State Machine Notation Rules                  | .62 |

| 2.5.7      | State Machine                                 | .63 |

| 2.5.8      | C/I Codes                                     | .74 |

| 2.5.9      | Layer 1 Loop-Backs                            | .76 |

| 2.5.10     | Analog Line Port                              | .78 |

| 2.6        | Access to IOM-2 Channels                      | .81 |

| 2.6.1      | B-Channel Access                              | .82 |

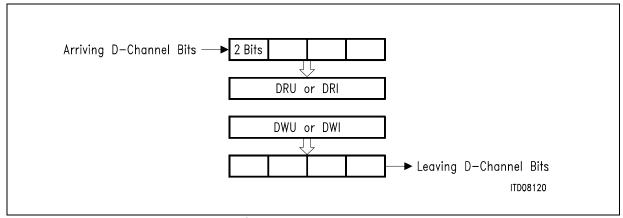

| 2.6.2      | D-Channel Access                              | .82 |

| 2.6.3      | C/I Channel Access                            | .83 |

| 2.6.4      | Monitor Channel Access                        | .84 |

| 2.7        | S/G Bit and BAC Bit in TE Mode                | .89 |

| 2.7.1<br>2.8                                             | Applications with ELIC on the Linecard (PBX)90                                                                                                                                                                                      |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.6                                                      | Reset                                                                                                                                                                                                                               |

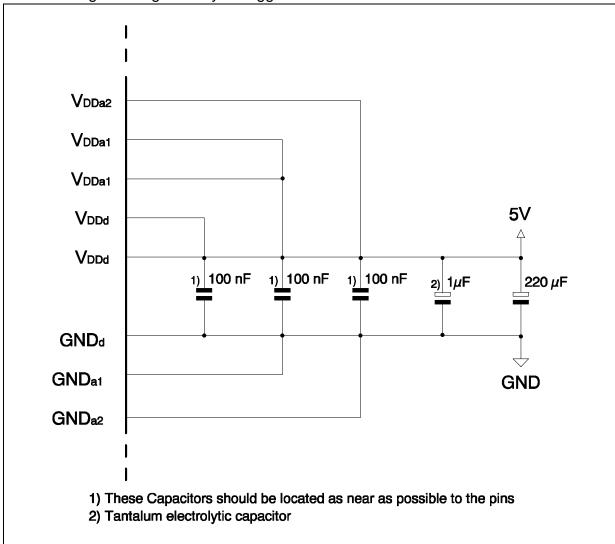

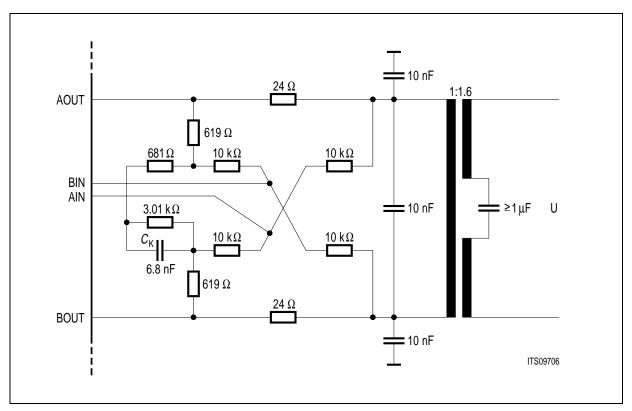

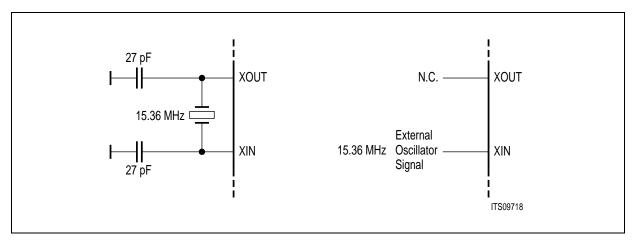

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3 | Operational Description97C/I Channel Programming97Monitor Channel Programming98Layer 1 Activation/Deactivation100External Circuitry109Power Supply Blocking Recommendation109U-Interface110Oscillator Circuit111                    |

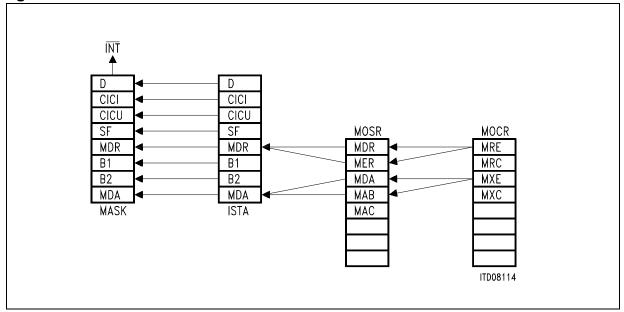

| <b>4</b><br>4.1<br>4.1.1<br>4.2                          | Register Description112Interrupt Structure114Monitor-Channel Interrupt Logic115Registers116                                                                                                                                         |

| 5<br>5.1<br>5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3 | Electrical Characteristics130Absolute Maximum Ratings130Power Consumption132DC Characteristics133AC Characteristics136Parallel Microprocessor Interface Timing136Serial Microprocessor Interface Timing140IOM-2 Interface Timing142 |

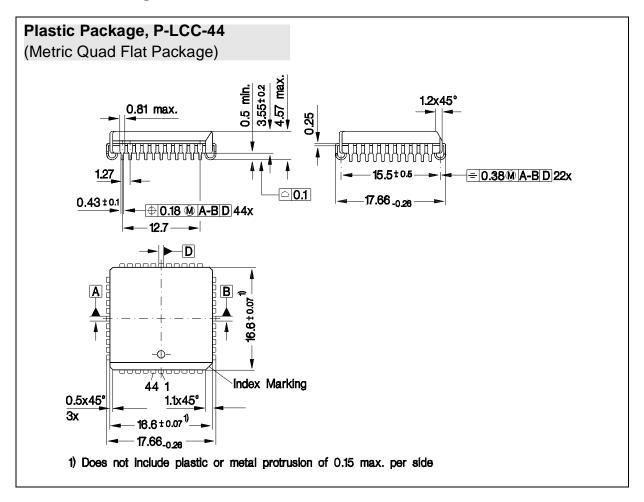

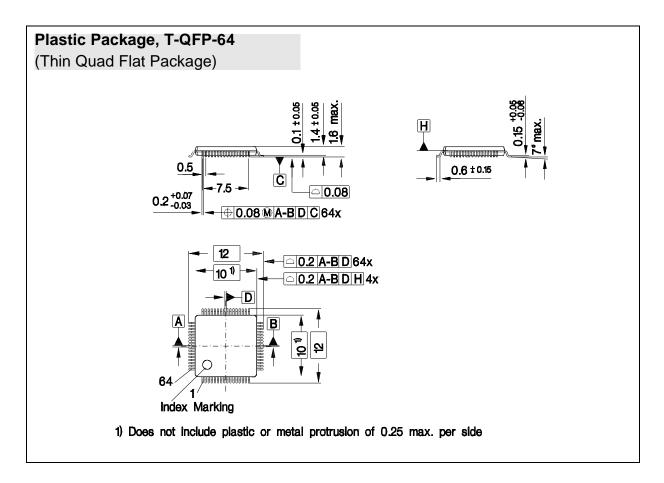

| 6                                                        | Package Outlines                                                                                                                                                                                                                    |

| 7                                                        | External Component Sourcing                                                                                                                                                                                                         |

| 8                                                        | <b>Glossary</b>                                                                                                                                                                                                                     |

| Appendix<br>App A<br>App B<br>App C                      | Jitter on IOM-2                                                                                                                                                                                                                     |

| Index                                                    |                                                                                                                                                                                                                                     |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4 $\mu$ C, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

$MUSAC^{^{\intercal}}\text{-}A,\ FALC^{^{\intercal}}\text{-}54,\ IWE}^{^{\intercal}},\ SARE^{^{\intercal}},\ UTPT^{^{\intercal}},\ ASM^{^{\intercal}},\ ASP^{^{\intercal}},\ DigiTape^{^{\intercal}}\ are\ trademarks\ of\ Siemens\ AG.$

Purchase of Siemens I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. Copyright Philips 1983.

| List of Fig | ures                                                         | Page |

|-------------|--------------------------------------------------------------|------|

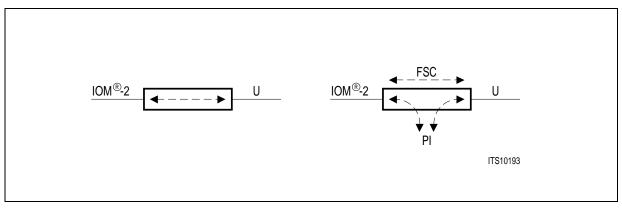

| Figure 1:   | Stand-Alone Mode (left) and µP Mode (right)                  | 8    |

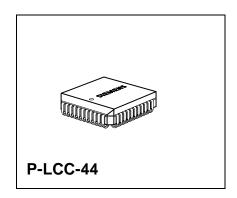

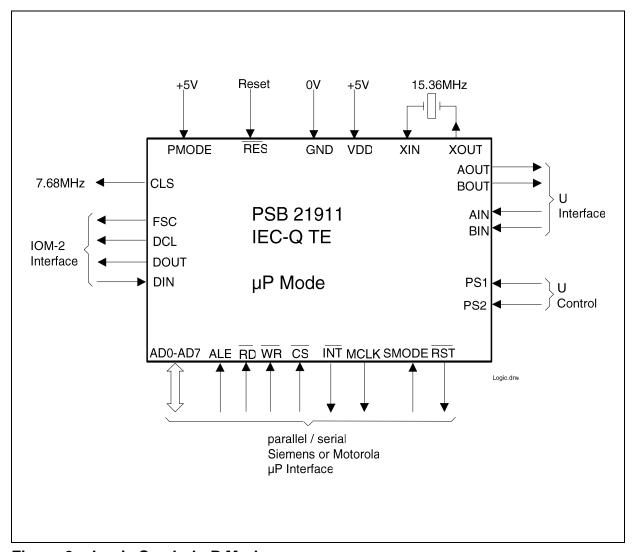

| Figure 2:   | Logic Symbol µP Mode                                         |      |

| Figure 3:   | Logic Symbol Stand-Alone Mode                                | 11   |

| Figure 4:   | Pin Configuration P-LCC-44 and T-QFP-64 Package (top view)   | 12   |

| Figure 5:   | ISDN PC Adapter Card                                         | 22   |

| Figure 6:   | ISDN Stand-Alone Terminal with POTS Interface                |      |

| Figure 7:   | ISDN Feature Phone                                           | 24   |

| Figure 8:   | ISDN-Modem PC Card                                           |      |

| Figure 9:   | IEC-Q TE Device Architecture (μP Mode)                       | 28   |

| Figure 10:  | IEC-Q TE Device Architecture (Stand-Alone Mode)              | 29   |

| Figure 11:  | IOM-2 Clocks and Data Lines                                  | 30   |

| Figure 12:  | Basic Channel Structure of IOM-2                             | 31   |

| Figure 13:  | Definition of the IOM-2 Frame in TE Mode                     | 32   |

| Figure 14:  | Definition of the IOM-2 Frame in NT Mode                     | 33   |

| Figure 15:  | Deactivation of the IOM-2 Clocks                             | 37   |

| Figure 16:  | U-Transceiver Block Diagram                                  | 41   |

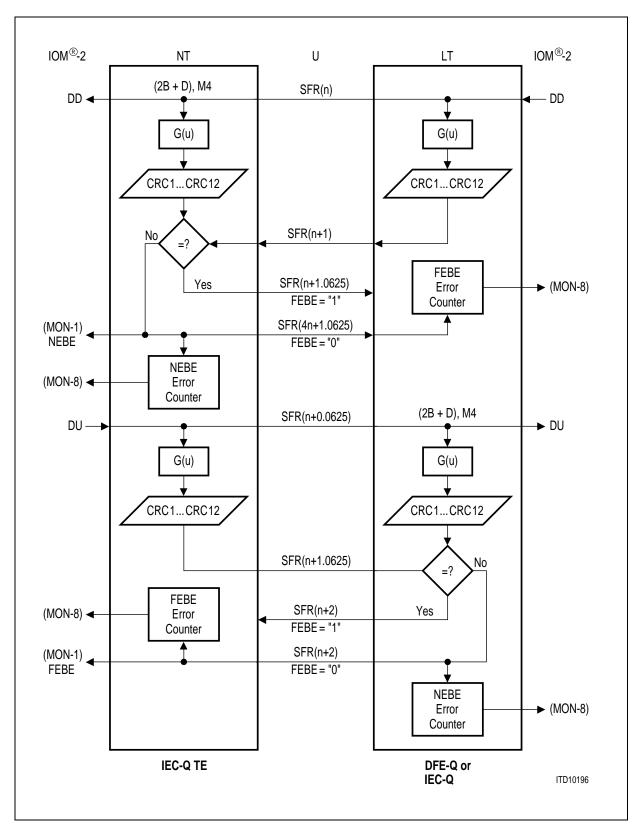

| •           | CRC-Process                                                  |      |

| Figure 18:  | Block Error Counter Test                                     | 48   |

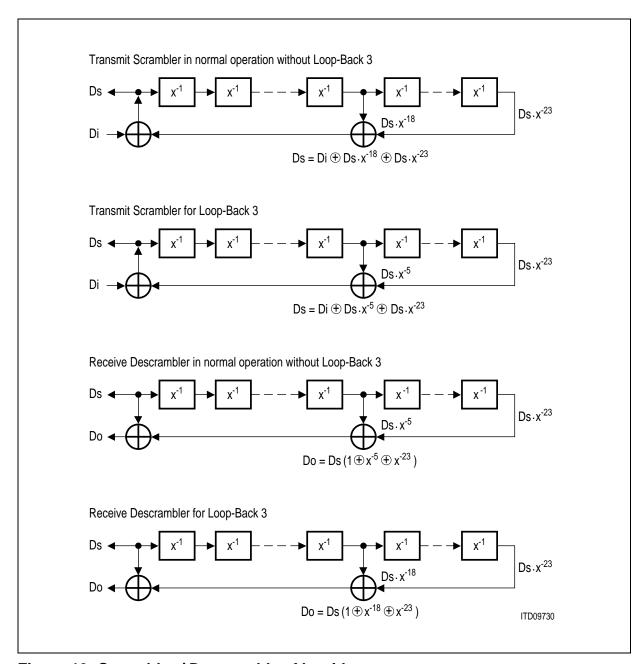

| •           | Scrambler / Descrambler Algorithms                           |      |

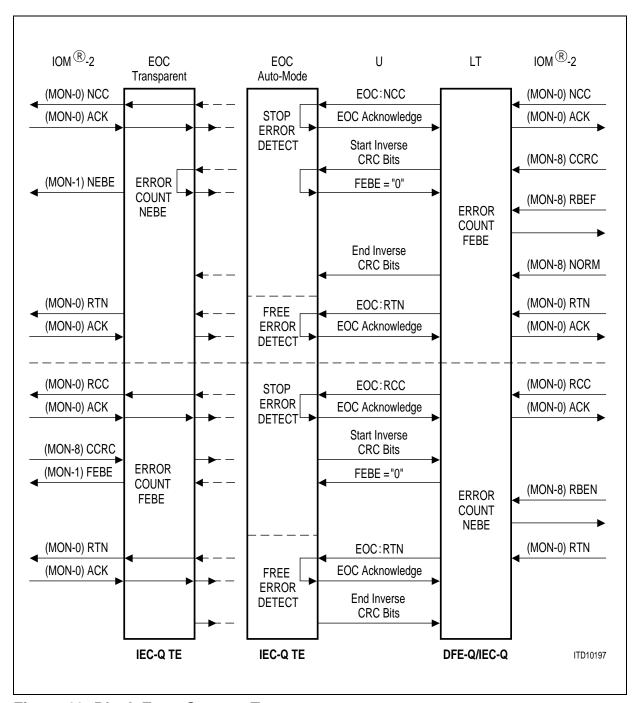

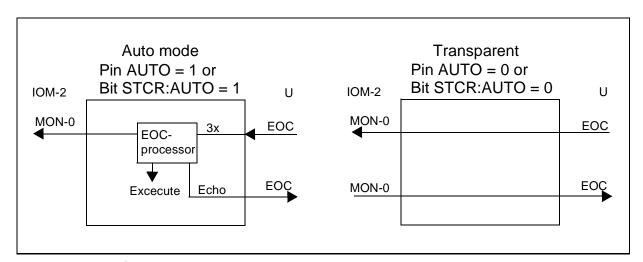

| Figure 20:  | EOC-Processor: Auto Mode, Transparent Mode                   | 51   |

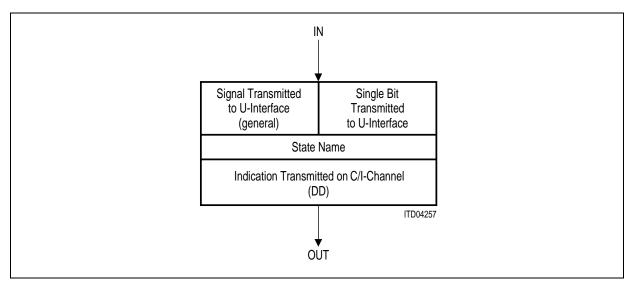

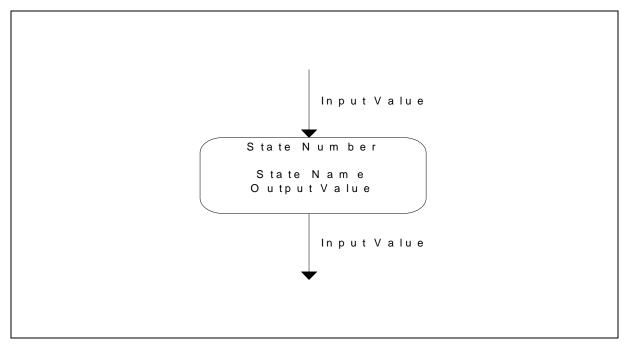

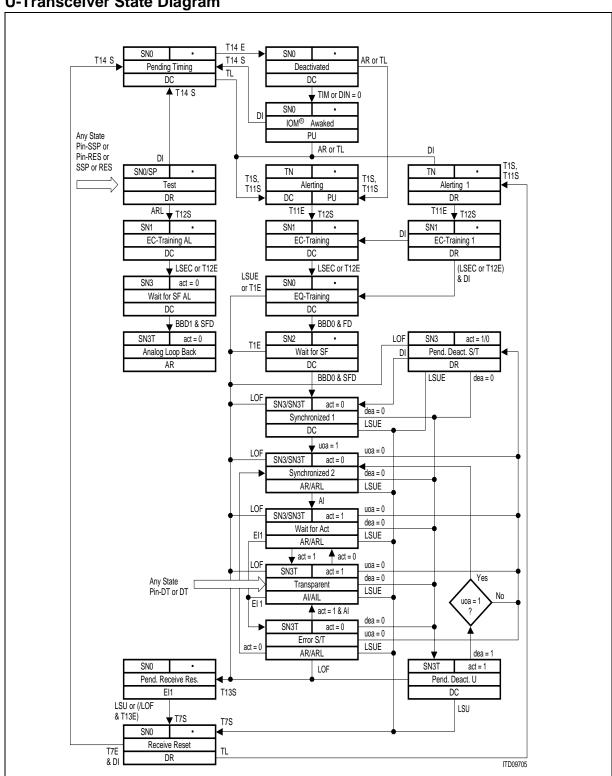

| Figure 21:  | State Diagram Notation U-Transceiver                         | 62   |

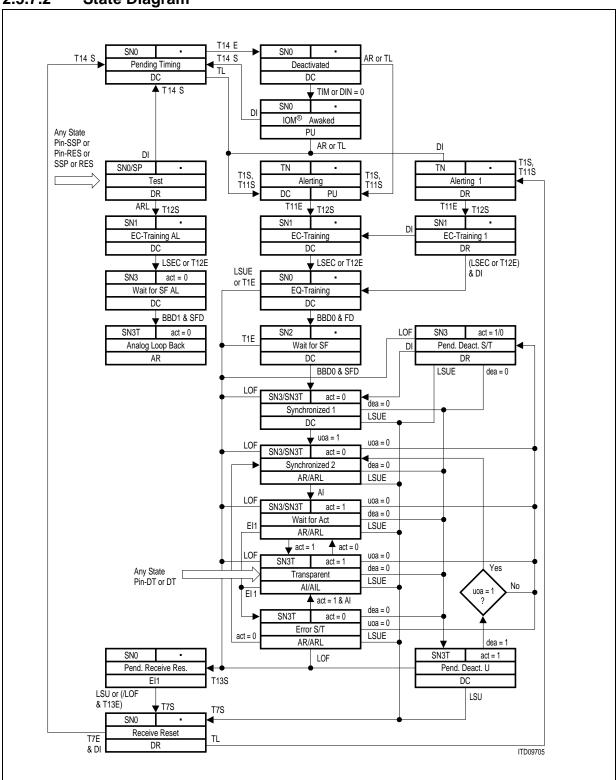

| Figure 22:  | State Transition Diagram                                     | 64   |

| Figure 23:  | Test Loop-Backs Supported by the IEC-Q TE                    | 76   |

| •           | DAC-Output for a Single Pulse                                |      |

|             | Pulse Mask for a Single Positive Pulse                       |      |

|             | Access to IOM-2 Channels (µP mode)                           |      |

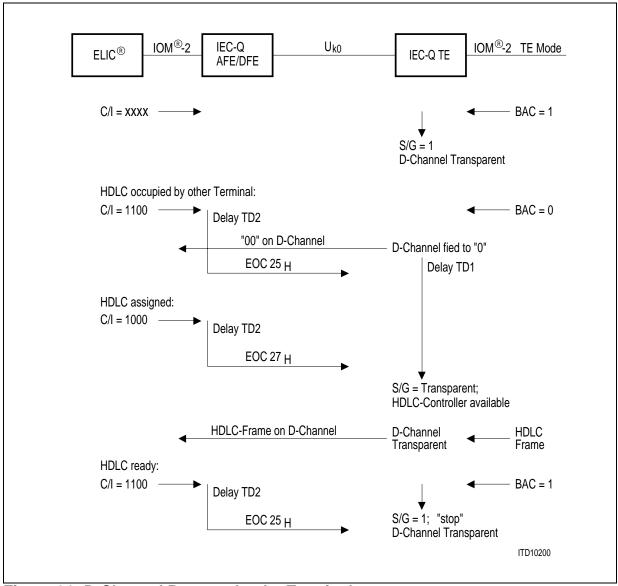

| Figure 27:  | Procedure for the D-Channel Processing                       | 83   |

| •           | C/I Channel Access                                           |      |

|             | Monitor Channel Access Directions                            |      |

| •           | Monitor Channel Protocol                                     |      |

| _           | D-Channel Request by the Terminal                            |      |

| •           | Reset Sources                                                |      |

| -           | Sampling of Interrupts                                       |      |

| •           | Example: C/I-Channel Use (all data values hexadecimal)       |      |

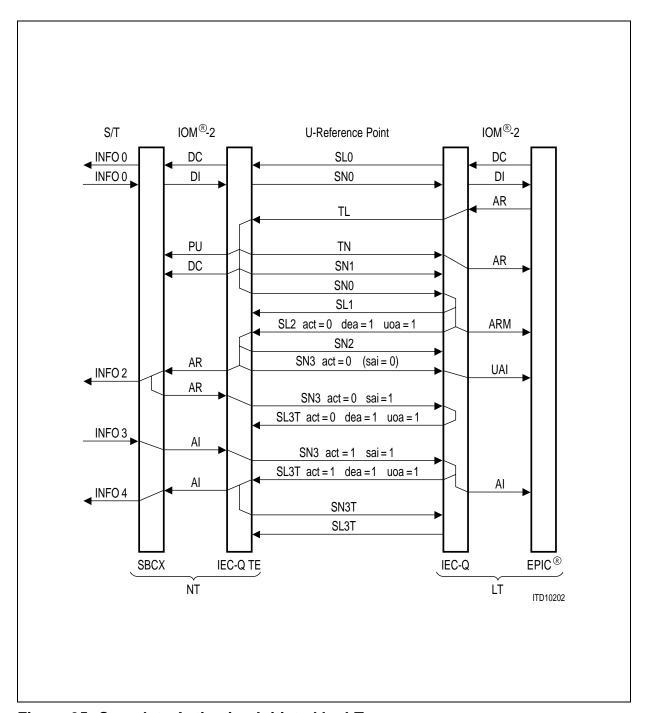

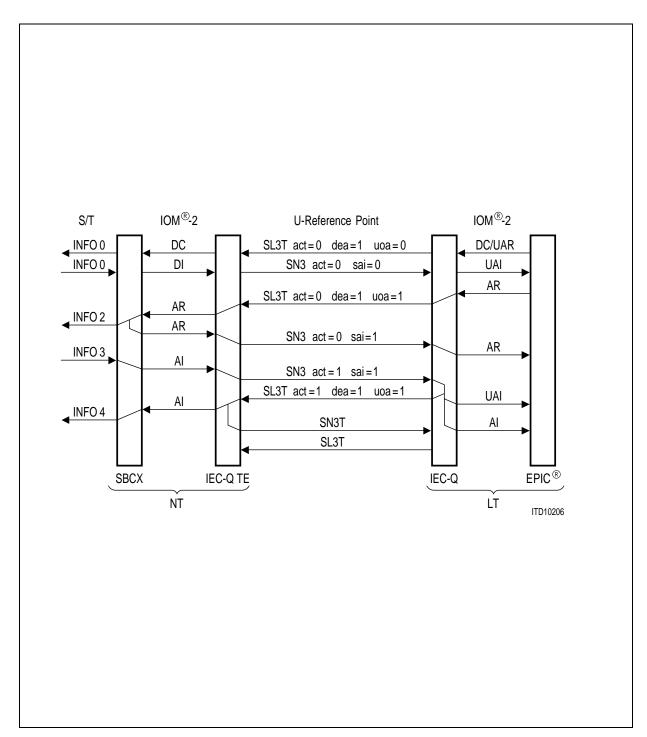

| •           | Complete Activation Initiated by LT                          |      |

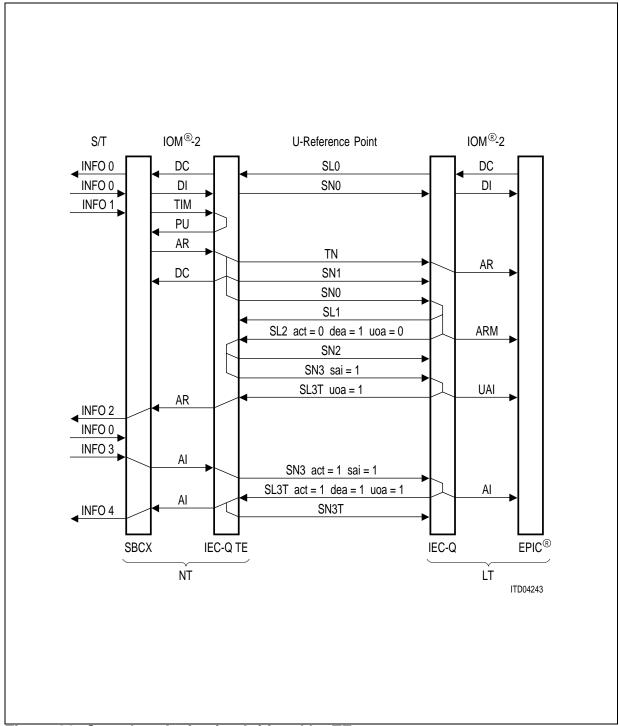

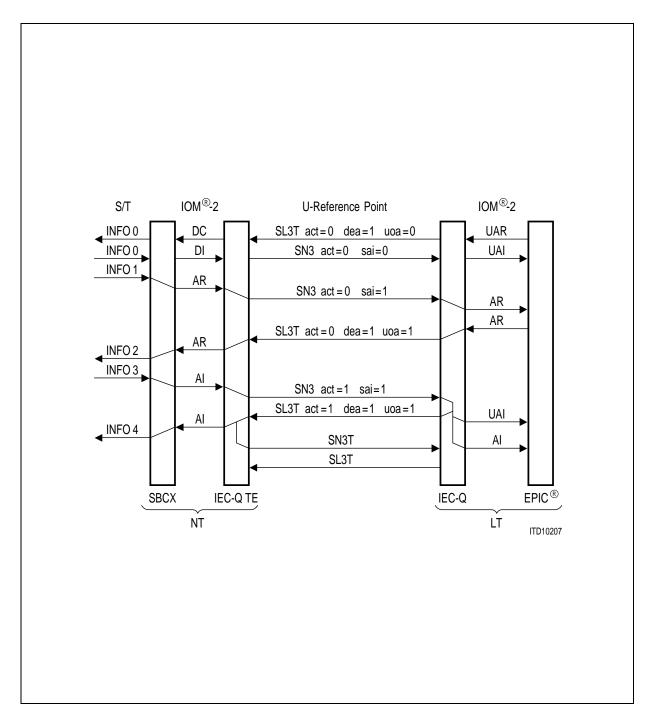

| _           | Complete Activation Initiated by TE                          |      |

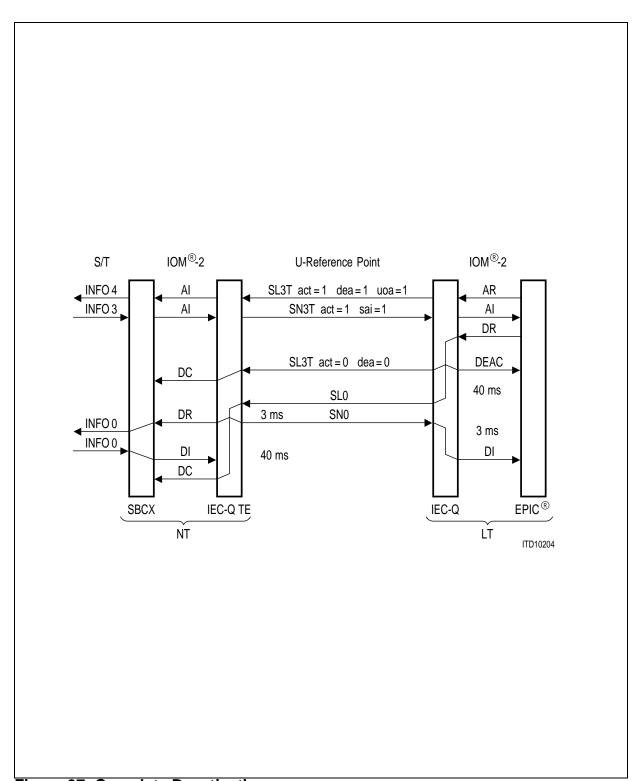

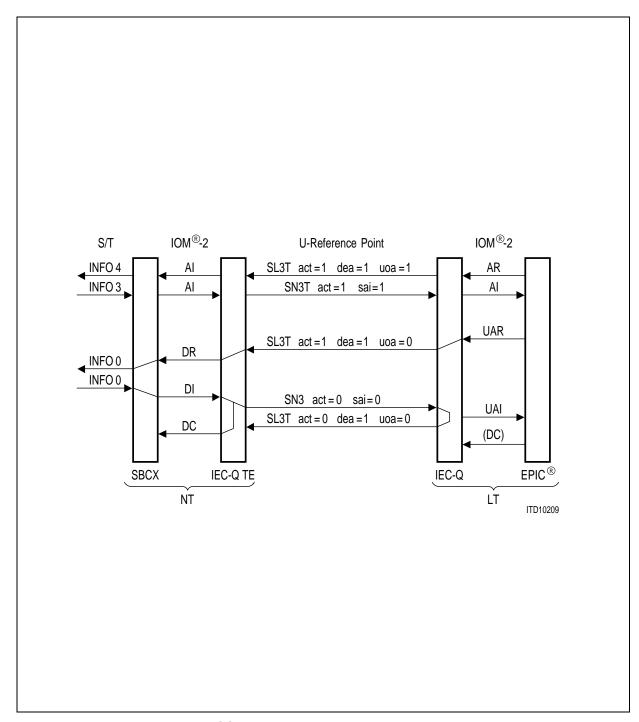

| _           | Complete Deactivation                                        |      |

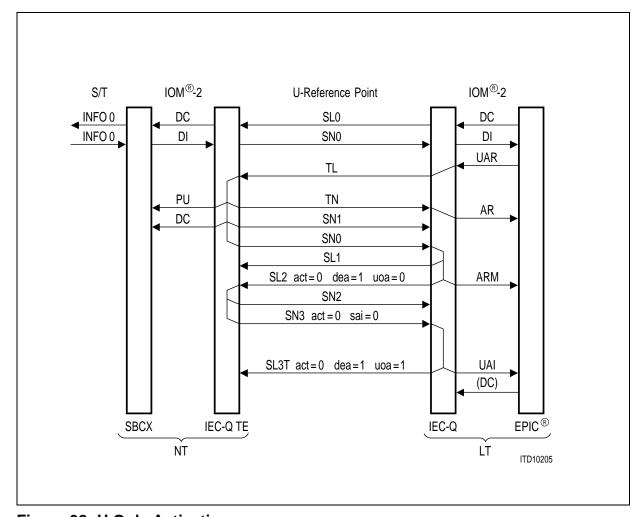

| _           | U Only Activation                                            |      |

| _           | LT Initiated Activation with U-Interface Active              |      |

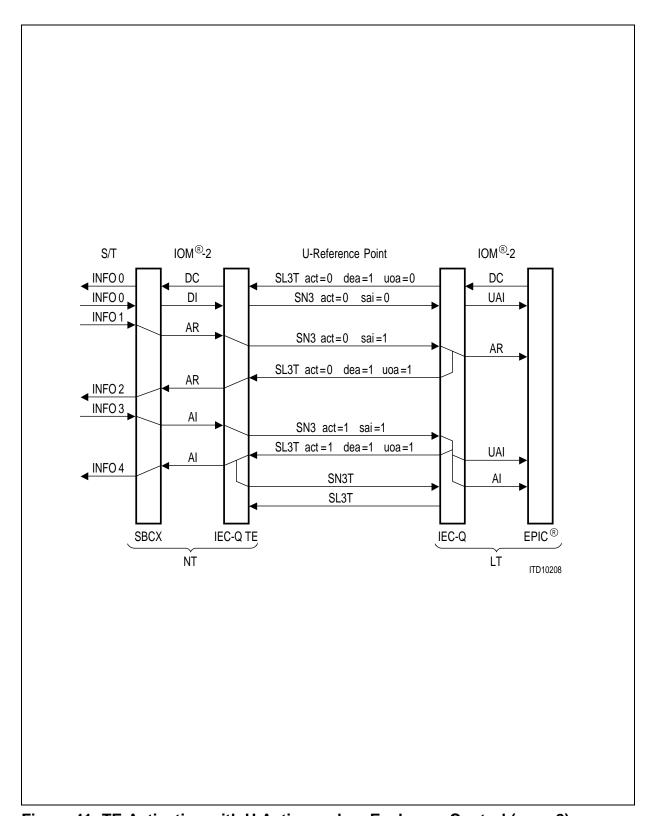

| •           | TE-Activation with U Active and Exchange Control (case 1)    |      |

| _           | TE-Activation with U Active and no Exchange Control (case 2) |      |

| Figure 42:  | Deactivation of S/T Only                                     | 108  |

| Figure 43: | Power Supply Blocking                                    | 109 |

|------------|----------------------------------------------------------|-----|

| Figure 44: | U-Interface Hybrid Circuit                               | 110 |

| Figure 45: | Crystal Oscillator or External Clock Source              | 111 |

| Figure 46: | Interrupt Structure                                      | 114 |

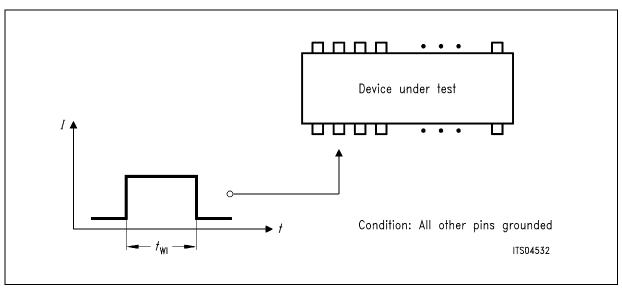

| Figure 47: | Test Condition for Maximum Input Current                 | 131 |

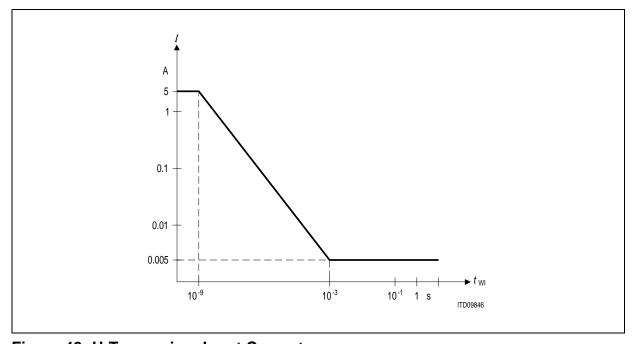

| Figure 48: | U-Transceiver Input Current                              | 131 |

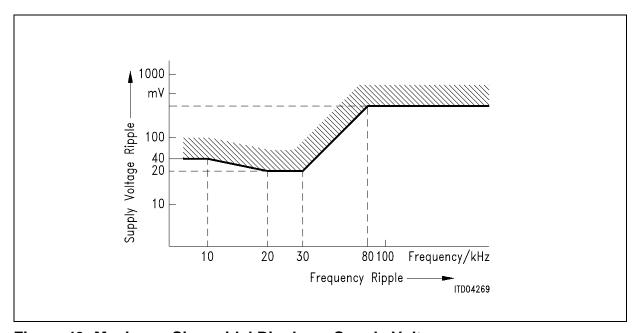

| Figure 49: | Maximum Sinusoidal Ripple on Supply Voltage              | 135 |

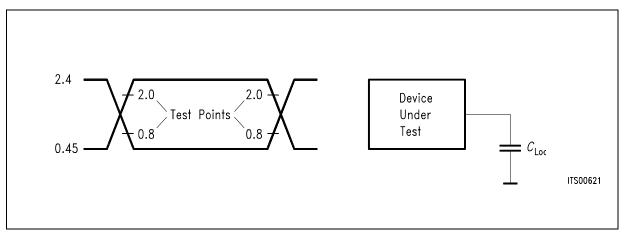

| Figure 50: | Input/Output Waveform for AC Tests                       | 136 |

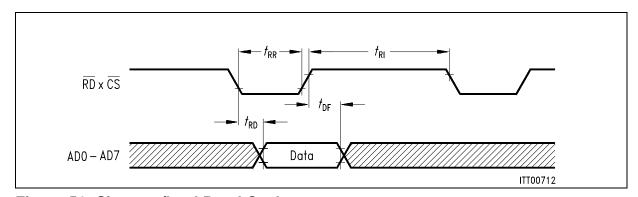

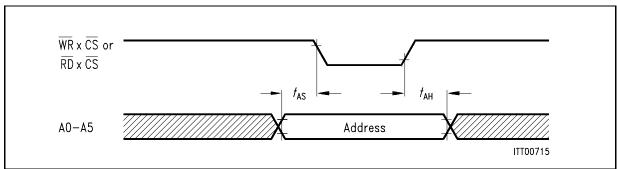

| Figure 51: | Siemens/Intel Read Cycle                                 | 136 |

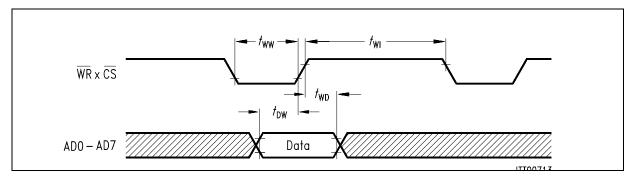

| Figure 52: | Siemens/Intel Write Cycle                                | 137 |

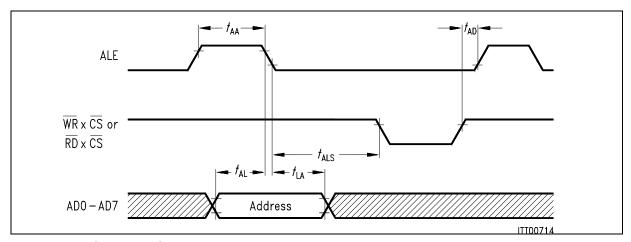

| Figure 53: | Siemens/Intel Multiplexed Address Timing                 | 137 |

| Figure 54: | Siemens/Intel Non-Multiplexed Address Timing             | 137 |

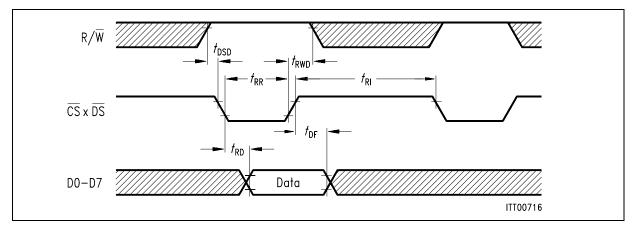

| Figure 55: | Motorola Read Timing                                     | 138 |

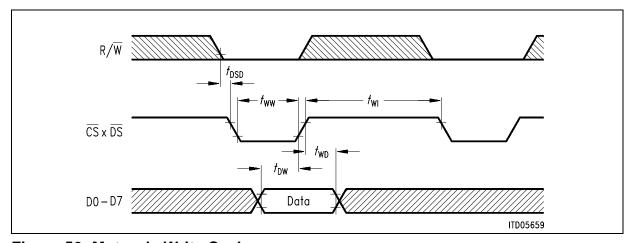

| Figure 56: | Motorola Write Cycle                                     | 138 |

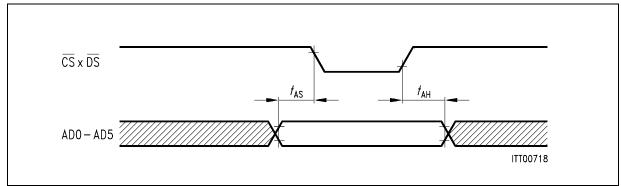

| Figure 57: | Motorola Non-Multiplexed Address Timing                  | 138 |

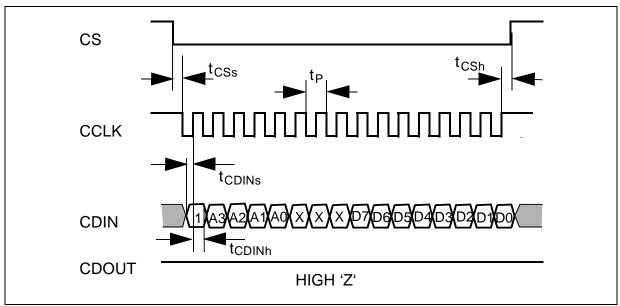

| Figure 58: | Serial µP Interface Mode Write                           | 140 |

| Figure 59: | Serial µP Interface Mode Read                            | 140 |

| Figure 60: | IOM-2 Timing in NT Mode                                  | 142 |

| Figure 61: | Dynamic Characteristics of Power Controller Write Access | 144 |

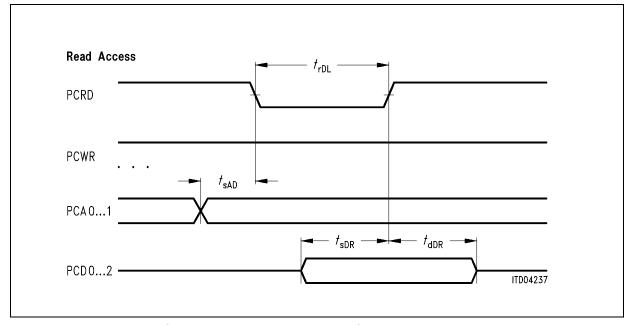

| Figure 62: | Dynamic Characteristics of Power Controller Read Access  | 144 |

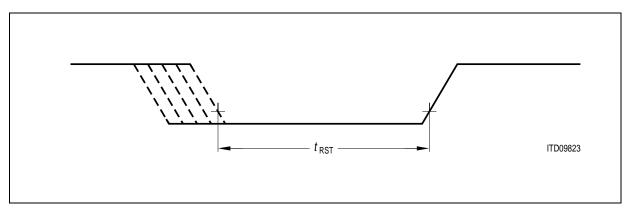

| Figure 63: | Reset Signal                                             | 146 |

| Figure 64: | S/G Bit State Machine Notation                           | 155 |

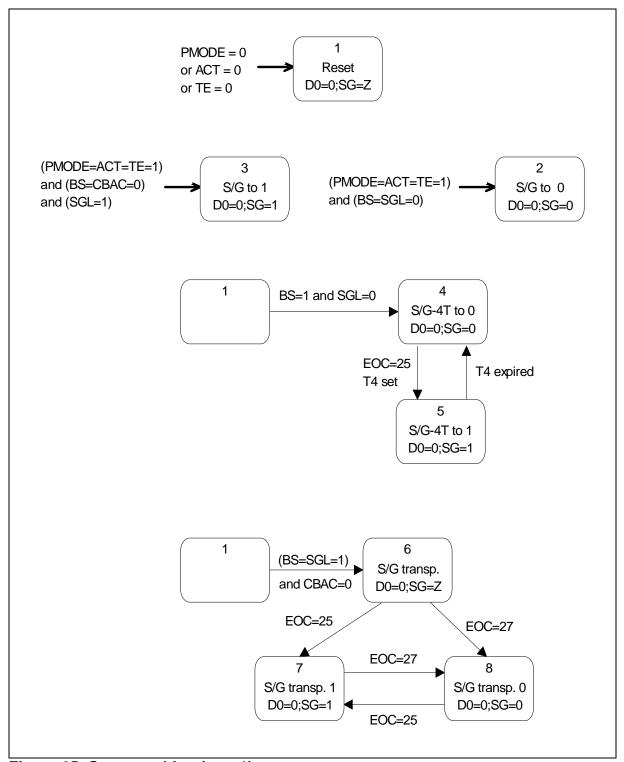

| Figure 65: | State machine (part 1)                                   | 156 |

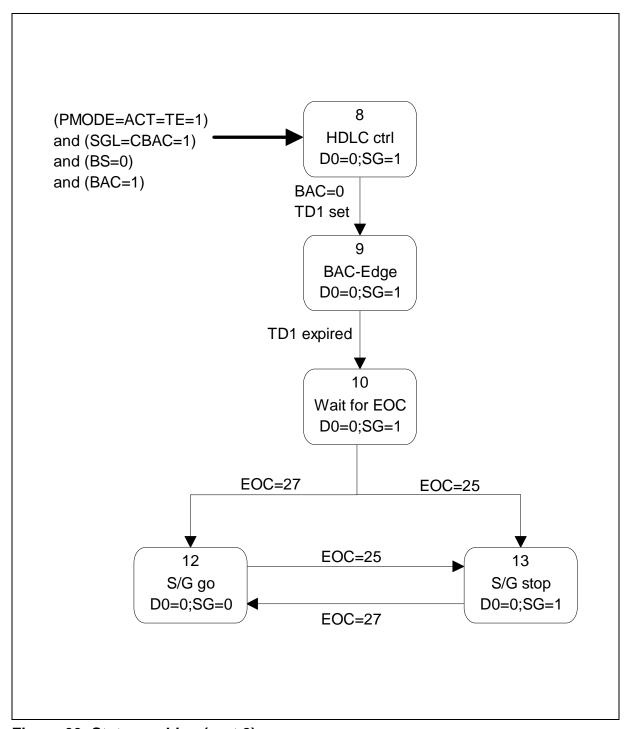

| Figure 66: | State machine (part 2)                                   | 157 |

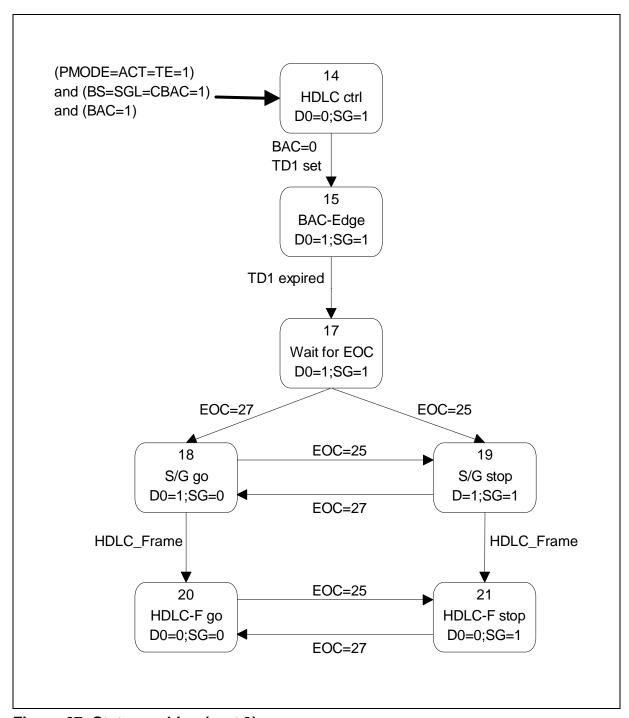

| Figure 67: | State machine (part 3)                                   | 158 |

| Figure 68: | U-Transceiver State Diagram                              | 161 |

|            |                                                          |     |

11.97

# **SIEMENS**

| List of Ta | bles                                                  | Page |

|------------|-------------------------------------------------------|------|

| Table 1:   | Microprocessor Bus Interface                          |      |

| Table 2:   | Modes of Operation (µP and Stand-Alone Mode)          |      |

| Table 3:   | Test Modes                                            |      |

| Table 4:   | DOUT Driver Modes                                     |      |

| Table 5:   | Microprocessor Interface Modes                        | 39   |

| Table 6:   | U-Frame Structure                                     |      |

| Table 7:   | EOC-Codes                                             |      |

| Table 8:   | Executed EOC Commands in Auto Mode                    |      |

| Table 9:   | Mon-1 S/Q-Channel Commands and Indications            | 54   |

| Table 10:  | Mon-1 M-Bit Commands                                  |      |

| Table 11:  | MON-2 Structure                                       |      |

| Table 12:  | Control of Overhead Bits                              |      |

| Table 13:  | Mon-8 Local Function Commands                         | 59   |

| Table 14:  | Timers                                                |      |

| Table 15:  | U-Transceiver C/I Codes                               |      |

| Table 16:  | B1/B2-Channel Data Registers                          |      |

| Table 17:  | D-channel data registers                              |      |

| Table 18:  | S/G Processing Mode                                   |      |

| Table 19:  | Control Structure of the S/G Bit and of the D-Channel |      |

| Table 20:  | Reset                                                 |      |

| Table 21:  | MON-8 and C/I-Commands                                |      |

| Table 22:  | U-Interface Signals                                   |      |

| Table 23:  | Register Address Map                                  |      |

| Table 24:  | Register Summary                                      |      |

| Table 25:  | Timing Characteristics (serial µP interface mode)     | 141  |

| Table 26:  | IOM-2 in NT Mode                                      |      |

| Table 27:  | Power Controller Interface Dynamic Characteristics    | 145  |

| Table 28:  | Reset Timing                                          |      |

| Table 29:  | U-Transformer Information                             | 149  |

| Table 30:  | Crystal Information                                   | 151  |

| Table 31:  | State Machine Input Signals                           | 159  |

| Table 32:  | State Machine Output Signals                          | 159  |

| Table 33:  | U-Transceiver C/I Codes                               | 162  |

Overview

#### 1 Overview

The PSB 21911, IEC-Q TE Version 5.2, is a specific derivative of the PEB 2091, IEC-Q for terminal and small PBX applications. It features all necessary functions required for NTs and terminal applications like PC add-on cards and terminal adapters.

In stand-alone mode the PSB 21911 IEC-Q TE Version 5.2 can be used fully pin compatible to IEC-Q V4.4 and former versions. In  $\mu P$  mode it offers a parallel or serial microprocessor interface.

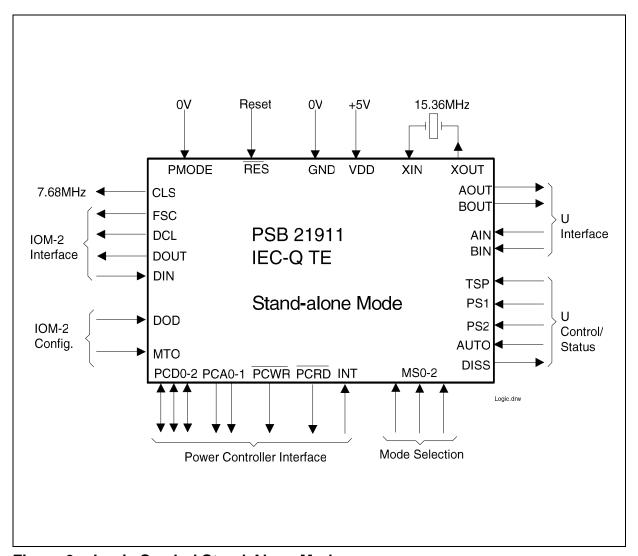

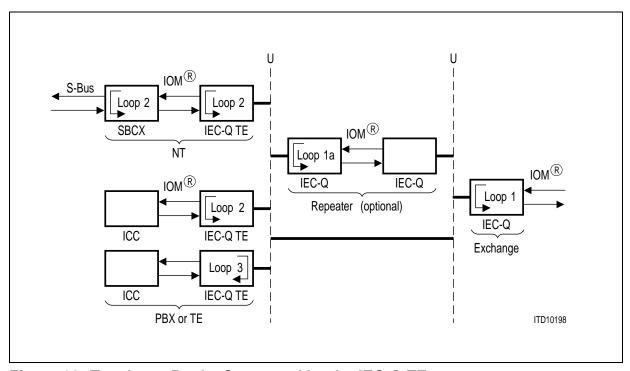

The <u>Processor Interface</u> (PI) of the IEC-Q TE V 5.2 establishes the access of a microprocessor between U-interface and IOM-2. It's main function is illustrated in **figure 1**.

Figure 1 Stand-Alone Mode (left) and µP Mode (right)

In  $\mu P$  mode B channels, D channel, C/I codes and Monitor commands can either be passed between the U-transceiver and IOM-2 directly, or they can be looped through the  $\mu P$  via the PI. Any selection of "passed" or "looped" channels can be programmed via a control register.

The  $\mu$ P-interface mode is enabled by setting the pin PMODE to "1". This pin was not to be connected in older versions of the IEC-Q. Its internal pull down resistor selects the stand-alone mode, if the pin is left open.

In stand-alone mode the IEC-Q TE is controlled exclusively via the IOM-2 interface and mode selection pins.

# ISDN Echocancellation Circuit for Terminal Applications IEC-Q TE

**PSB 21911**

Version 5.2 CMOS

### 1.1 Features

- ISDN U-transceiver with IOM-2 and optional microprocessor interface

- Compatible to NT modes and TE mode of PEB 2091 IEC-Q V5.1

- · Perfectly suited for terminal and TA applications

- U-interface (2B1Q) conform to ANSI T1.601, ETSI ETR 080 and CNET ST/LAA/ELR/DNP/822:

- Meets all transmission requirements on all ANSI, ETSI and CNET loops with margin

- Conform to British Telecom's RC7355E

- Compliant with ETSI 10ms micro interruptions

- IOM-2 interface for connection of e.g. ISAC-S, SICOFI-2/4TE, ARCOFI, ITAC, HSCX-TE, ISAR, IPAC, 3PAC

- Pin compatible to version 4.4 in the P-LCC-44 package

### In µP mode:

- Parallel or serial microprocessor interface and watchdog

- µP access to B-channels, D-channel and intercommunication channels

- µP access to IOM-2 Monitor-channels and C/I-channels

- Adjustable microcontroller clock source between 0.96MHz and 7.68MHz

- Selection between Bit clock (BCL) and Data clock (DCL)

- Supports synchronization of basestations in cordless applications (e.g. RITL)

- Supports D-channel arbitration with ELIC linecard (e.g. PBX)

#### In all modes:

- Single 5 Volt power supply

- Low power CMOS technology with power down mode

# Logic Symbol µP Mode

# 1.2 Logic Symbol µP Mode

Figure 2 Logic Symbol µP Mode

# **Logic Symbol Stand-Alone Mode**

# 1.3 Logic Symbol Stand-Alone Mode

Figure 3 Logic Symbol Stand-Alone Mode

### **Pin Configuration**

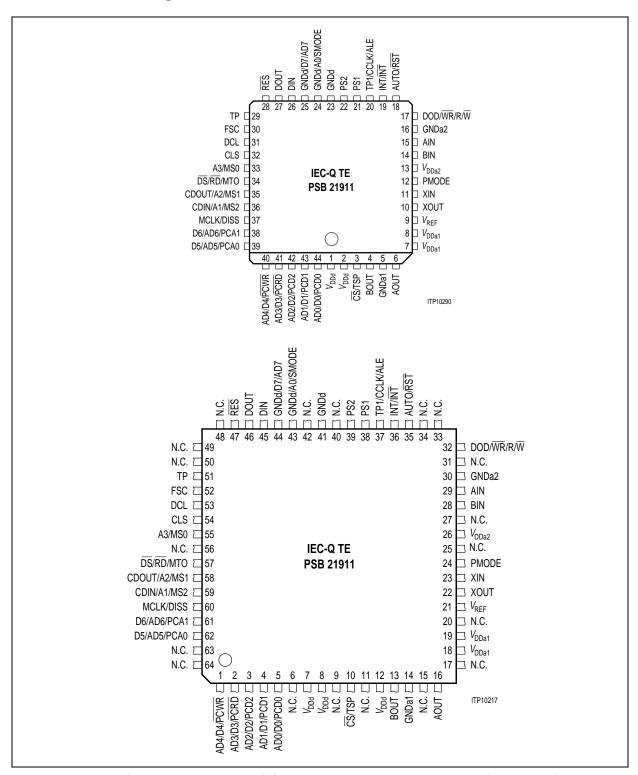

### 1.4 Pin Configuration

Figure 4 Pin Configuration P-LCC-44 and T-QFP-64 Package (top view)

### **Pin Definitions and Functions**

### 1.5 Pin Definitions and Functions

The following tables group the pins according to their functions. They include pin name, pin number, type and a brief description of the function.

| Pin No.  |         | Symbol          |            | I/O | Function |

|----------|---------|-----------------|------------|-----|----------|

| P-LCC-44 | T-QFP64 | Stand-<br>alone | μP<br>mode |     |          |

# **Power Supply Pins**

| 1, 2 | 7, 8, 12 | $V_{DDd}$  | $V_{DDd}$  | I | 5 V ± 5% digital supply voltage                                                   |

|------|----------|------------|------------|---|-----------------------------------------------------------------------------------|

| 5    | 14       | GNDa1      | GNDa1      | I | 0 V analog                                                                        |

| 7, 8 | 18, 19   | $V_{DDa1}$ | $V_{DDa1}$ | I | 5 V ± 5% analog supply voltage                                                    |

| 9    | 21       | $V_{REF}$  | $V_{REF}$  | 0 | $V_{REF}$ pin to buffer internally generated voltage with capacitor 100 nF vs GND |

| 13   | 26       | $V_{DDa2}$ | $V_{DDa2}$ | I | 5 V ± 5% analog supply voltage                                                    |

| 16   | 30       | GNDa2      | GNDa2      | I | 0 V analog                                                                        |

| 23   | 41       | GNDd       | GNDd       | I | 0 V digital                                                                       |

### **Mode Selection Pins**

| 3  | 10 | TSP  |     | I | Single Pulse Test Mode                                                                                                                    |

|----|----|------|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |      |     |   | For activation refer to table 3 on page 27. When active, alternating 2.5 V pulses are issued in 1.5 ms intervals. Tie to GND if not used. |

|    |    |      | CS  | I | Chip Select                                                                                                                               |

|    |    |      |     |   | (Multiplexed, demultiplexed and serial modes): Low active.                                                                                |

| 18 | 35 | AUTO |     | I | Auto EOC Mode                                                                                                                             |

|    |    |      |     |   | Selection between auto- and transparent mode for EOC channel processing. (Automode = (1))                                                 |

|    |    |      | RST | 0 | Reset output                                                                                                                              |

|    |    |      |     |   | (Multiplexed, demultiplexed and serial modes): Low active.                                                                                |

# **Pin Definitions and Functions**

| Pin No.  |         | Symbol |          | I/O | Function                                                                                        |  |

|----------|---------|--------|----------|-----|-------------------------------------------------------------------------------------------------|--|

| P-LCC-44 | T-QFP64 | Stand- | μΡ       |     |                                                                                                 |  |

|          |         | alone  | mode     |     |                                                                                                 |  |

| 24       | 43      | GNDd   |          | I   | GNDd                                                                                            |  |

|          |         |        |          |     | Must be connected to GNDd in standalone mode.                                                   |  |

|          |         |        | A0       | I   | Address Bus Pin                                                                                 |  |

|          |         |        |          |     | (Demultiplexed mode)                                                                            |  |

|          |         |        | SMODE    | I   | <b>Serial Mode Pin:</b> SMODE = 1 selects serial mode, SMODE = 0 enables the multiplexed mode.  |  |

| 25       | 44      | GNDd   |          | 1   | GNDd                                                                                            |  |

|          |         |        |          |     | Must be connected to GNDd in standalone mode.                                                   |  |

|          |         |        | D7       | I/O | Data Bus Pin                                                                                    |  |

|          |         |        |          |     | (Demultiplexed modes)                                                                           |  |

|          |         |        | AD7      | I/O | Address Data Bus Pin                                                                            |  |

|          |         |        |          |     | (Multiplexed mode)                                                                              |  |

|          |         |        | not used | I   | (Serial mode) tie to GND.                                                                       |  |

| 33       | 55      | MS0    |          | I   | Mode Selection 0                                                                                |  |

|          |         |        |          |     | refer to table 2 on page 26.                                                                    |  |

|          |         |        | not used | I   | (Multiplexed mode) tie to GND.                                                                  |  |

|          |         |        | A3       | 1   | Address Bus Pin                                                                                 |  |

|          |         |        |          |     | (Demultiplexed modes).                                                                          |  |

|          |         |        | not used |     | (Serial mode) tie to GND.                                                                       |  |

| 35       | 58      | MS1    |          | I   | Mode Selection 1                                                                                |  |

|          |         |        |          |     | refer to table 2 on page 26.                                                                    |  |

|          |         |        | not used | I   | (Multiplexed mode) tie to GND.                                                                  |  |

|          |         |        | A2       | I   | Address Bus Pin                                                                                 |  |

|          |         |        |          |     | (Demultiplexed modes).                                                                          |  |

|          |         |        | CDOUT    | О   | Controller Data Out CCLK determines the data rate. CDOUT is "high Z" if no data is transmitted. |  |

# **Pin Definitions and Functions**

| Pin No.  | Pin No. Symbol |                 | I/O        | Function |                                                                        |

|----------|----------------|-----------------|------------|----------|------------------------------------------------------------------------|

| P-LCC-44 | T-QFP64        | Stand-<br>alone | μP<br>mode |          |                                                                        |

| 36       | 59             | MS2             |            | I        | Mode Selection 2                                                       |

|          |                |                 |            |          | refer to table 2 on page 26.                                           |

|          |                |                 | not used   | 1        | (Multiplexed mode) tie to GND.                                         |

|          |                |                 | A1         | 1        | Address Bus Pin                                                        |

|          |                |                 |            |          | (Demultiplexed modes).                                                 |

|          |                |                 | CDIN       | 1        | Controller Data In (Serial mode) CCLK determines the data rate.        |

| 28       | 47             | RES             | RES        | I        | Reset                                                                  |

|          |                |                 |            |          | Low active, must be (0) at least for 10 ns.                            |

|          |                |                 |            |          | Refer also to table 3 on page 27 for test modes invoked with this pin. |

### **Power Controller Interface Pins**

| 44 | 5 | PCD0 |         | I/O  | Data Bus 0 of Power Controller |

|----|---|------|---------|------|--------------------------------|

|    |   |      |         | (PU) | Interface                      |

|    |   |      |         |      | internal pull-up.              |

|    |   |      | AD0     | I/O  | Address/Data Bus Pin           |

|    |   |      |         |      | (Multiplexed mode)             |

|    |   |      | D0      | I/O  | Data Bus Pin                   |

|    |   |      |         |      | (Demultiplexed modes)          |

|    |   |      | notused | I    | (Serial mode) tie to GND.      |

| 43 | 4 | PCD1 |         | I/O  | Data Bus 1 of Power Controller |

|    |   |      |         | (PU) | Interface                      |

|    |   |      |         |      | Internal pull-up.              |

|    |   |      | AD1     | I/O  | Address/Data Bus Pin           |

|    |   |      |         |      | (Multiplexed mode)             |

|    |   |      | D1      | I/O  | Data Bus Pin                   |

|    |   |      |         |      | (Demultiplexed modes)          |

|    |   |      | notused | I    | (Serial mode) tie to GND.      |

# **Pin Definitions and Functions**

| Pin No.  |         | Symbol |         | I/O  | Function                                             |

|----------|---------|--------|---------|------|------------------------------------------------------|

| P-LCC-44 | T-QFP64 | Stand- | μΡ      |      |                                                      |

|          |         | alone  | mode    |      |                                                      |

| 42       | 3       | PCD2   |         | I/O  | Data Bus 2 of Power Controller                       |

|          |         |        |         | (PU) | Interface                                            |

|          |         |        |         |      | Internal pull-up.                                    |

|          |         |        | AD2     | I/O  | Address/Data Bus Pin                                 |

|          |         |        |         |      | (Multiplexed mode)                                   |

|          |         |        | D2      | I/O  | Data Bus Pin                                         |

|          |         |        |         |      | (Demultiplexed modes)                                |

|          |         |        | notused | I    | (Serial mode) tie to GND.                            |

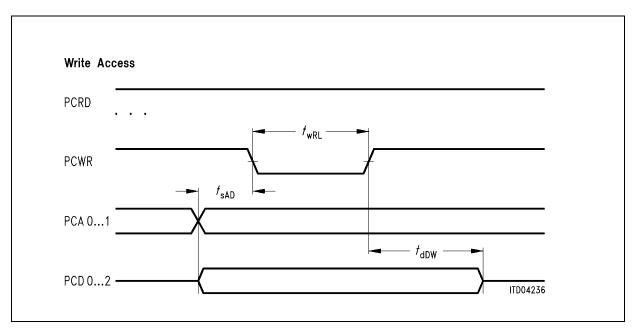

| 39       | 62      | PCA0   |         | 0    | Address bus 0 of Power Controller Interface.         |

|          |         |        | D5      | I/O  | Data Bus Pin                                         |

|          |         |        |         |      | (Demultiplexed modes)                                |

|          |         |        | AD5     | I/O  | Address Data Bus Pin                                 |

|          |         |        |         |      | (Multiplexed mode)                                   |

|          |         |        | notused | 1    | (Serial mode) tie to GND.                            |

| 38       | 61      | PCA1   |         | 0    | Address bus 1 of Power Controller Interface          |

|          |         |        | D6      | I/O  | Data Bus Pin                                         |

|          |         |        |         |      | (Demultiplexed modes)                                |

|          |         |        | AD6     | I/O  | Address Data Bus Pin                                 |

|          |         |        |         |      | (Multiplexed mode)                                   |

|          |         |        | notused | I    | (Serial mode) tie to GND.                            |

| 41       | 2       | PCRD   |         | 0    | <b>Power Controller Bus Read Request</b> Low active. |

|          |         |        | D3      | I/O  | Data Bus Pin                                         |

|          |         |        |         |      | (Demultiplexed modes)                                |

|          |         |        | AD3     | I/O  | Address/Data Bus Pin                                 |

|          |         |        |         |      | (Multiplexed mode)                                   |

|          |         |        | notused | 1    | (Serial mode) tie to GND.                            |

# **Pin Definitions and Functions**

| Pin No.  |         | Symbol          |            | I/O | Function                                                                                                                                                                       |

|----------|---------|-----------------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-44 | T-QFP64 | Stand-<br>alone | μP<br>mode |     |                                                                                                                                                                                |

| 40       | 1       | PCWR            |            | 0   | Power Controller Bus Write Request Low active.                                                                                                                                 |

|          |         |                 | D4         | I/O | Data Bus Pin                                                                                                                                                                   |

|          |         |                 |            |     | (Demultiplexed modes)                                                                                                                                                          |

|          |         |                 | AD4        | I/O | Address/Data Bus Pin                                                                                                                                                           |

|          |         |                 |            |     | (Multiplexed mode)                                                                                                                                                             |

|          |         |                 | notused    | I   | (Serial mode) tie to GND.                                                                                                                                                      |

| 19       | 36      | INT             |            | I   | Interrupt                                                                                                                                                                      |

|          |         |                 |            |     | Change-sensitive. After a change of level has been detected the C/I code "INT" will be issued on IOM. Tie to GND if not used.                                                  |

|          |         |                 | ĪNT        | 0   | Interrupt Line                                                                                                                                                                 |

|          |         |                 |            |     | (Multiplexed, demultiplexed and serial modes): Low active.                                                                                                                     |

| 37       | 60      | DISS            |            | 0   | Disable Power Supply                                                                                                                                                           |

|          |         |                 |            |     | This pin is set to '1' after receipt of MON-0 LBBD in EOC auto-mode.                                                                                                           |

|          |         |                 | MCLK       | 0   | Microprocessor Clock Output<br>(Multiplexed, demultiplexed and serial<br>modes): provided with four<br>programmable clock rates: 7.68 MHz,<br>3.84 MHz, 1.92 MHz and 0.96 MHz. |

| 21       | 38      | PS1             | PS1        | I   | Power Status 1 (primary).                                                                                                                                                      |

|          |         |                 |            |     | '1' indicates primary power supply ok. The pin level is identical to the overhead bit 'PS1' value.                                                                             |

| 22       | 39      | PS2             | PS2        | I   | Power Status 2 (secondary)                                                                                                                                                     |

|          |         |                 |            |     | '1' indicates secondary power supply ok. The pin level is identical to the overhead bit 'PS2' value.                                                                           |

# **Pin Definitions and Functions**

| Pin No.  | . Symbol |                 | I/O        | Function |  |

|----------|----------|-----------------|------------|----------|--|

| P-LCC-44 | T-QFP64  | Stand-<br>alone | μP<br>mode |          |  |

|          |          | 410110          | iiioac     |          |  |

# **Miscellaneous Function Pins**

| 10 | 22 | XOUT | XOUT     | 0    | Crystal OUT                                                                                                                                                                                      |

|----|----|------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |      |          |      | To connect 15.36-MHz crystal.<br>Leave open if not used.                                                                                                                                         |

| 11 | 23 | XIN  | XIN      | I    | Crystal IN                                                                                                                                                                                       |

|    |    |      |          |      | To connect 15.36-MHz crystal or external 15.36-MHz clock.                                                                                                                                        |

| 17 | 32 | DOD  |          | I    | DOUT Open Drain                                                                                                                                                                                  |

|    |    |      |          |      | Select open drain with DOD = (1) (external pull-up resistor required) and tristate with DOD = (0). See also table 4 on page 27.                                                                  |

|    |    |      | WR       | I    | Write (Siemens/Intel multiplexed and demultiplexed modes): indicates a write operation, active low.                                                                                              |

|    |    |      | R/W      | I    | Read/Write (Motorola demultiplexed mode): indicates a read (high) or write (low) operation.                                                                                                      |

|    |    |      | not used | I    | (Serial mode) tie to GND.                                                                                                                                                                        |

| 29 | 51 | TP   | TP       | I    | Test Pin                                                                                                                                                                                         |

|    |    |      |          | (PD) | Not available to user. Do not connect. Internal pull-down resistor.                                                                                                                              |

| 20 | 37 | TP1  |          | I    | Test Pin 1                                                                                                                                                                                       |

|    |    |      |          | (PD) | Not available to user. Do not connect. Internal pull-down resistor.                                                                                                                              |

|    |    |      | ALE      | I    | Address Latch Enable (Multiplexed mode): In the Siemens/ Intel µP interface modes a high indicates an address on the AD03 pins which is latched with the falling edge of ALE (see also page 39). |

# **Pin Definitions and Functions**

| Pin No.  |                                                                                 | Symbol          |            | I/O  | Function                                                                                                                              |

|----------|---------------------------------------------------------------------------------|-----------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-44 | T-QFP64                                                                         | Stand-<br>alone | μP<br>mode |      |                                                                                                                                       |

|          |                                                                                 |                 | ALE        | I    | Address Latch Enable (Demultiplexed mode): ALE tied to GND selects the Siemens/Intel type. ALE tied to VDD selects the Motorola type. |

|          |                                                                                 |                 | CCLK       | I    | Controller Data Clock<br>(Serial mode): Shifts data from (1) and<br>to (0) the device.                                                |

| 32       | 54                                                                              | CLS             | CLS        | 0    | Clock Signal                                                                                                                          |

|          |                                                                                 |                 |            |      | A 7.68MHz clock, synchronous to the U-interface, is provided on this pin.                                                             |

| 12       | 24                                                                              | PMOD            | PMODE      | I    | Processor Interface Enable                                                                                                            |

|          |                                                                                 | E               |            | (PD) | Setting PMODE to "1" enables the Processor Interface. Tie to GND or do not connect to select stand-alone mode. Internal pull down.    |

| 34       | 57                                                                              | MTO             |            | I    | Monitor Procedure Time-Out                                                                                                            |

|          |                                                                                 |                 |            | (PD) | Disables the internal 6 ms Monitor time-out when set to (1). Internal pull-down resistor.                                             |

|          |                                                                                 |                 | RD         | I    | Read (Siemens/Intel multiplexed and demultiplexed modes): indicates a read operation, active low.                                     |

|          |                                                                                 |                 | DS         | I    | Data Strobe (Motorola demultiplexed mode): indicates a data transfer, active low.                                                     |

|          |                                                                                 |                 | not used   | I    | (Serial mode) tie to GND.                                                                                                             |

|          | 6, 9, 11,<br>15, 20, 25,<br>27, 31, 33,<br>34, 40, 48,<br>49, 50, 51,<br>63, 64 | not<br>used     | not used   |      | Leave open for future compatibility.                                                                                                  |

# **Pin Definitions and Functions**

| Pin No. Symbol |         | I/O             | Function   |  |  |

|----------------|---------|-----------------|------------|--|--|

| P-LCC-44       | T-QFP64 | Stand-<br>alone | μP<br>mode |  |  |

# IOM<sup>®</sup>-2 Pins

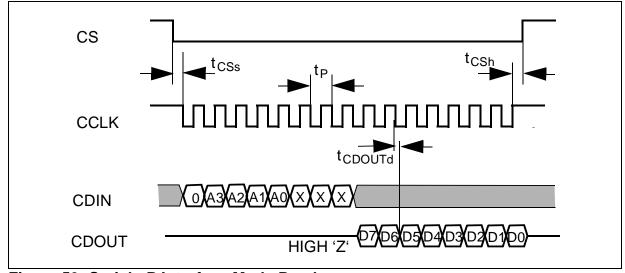

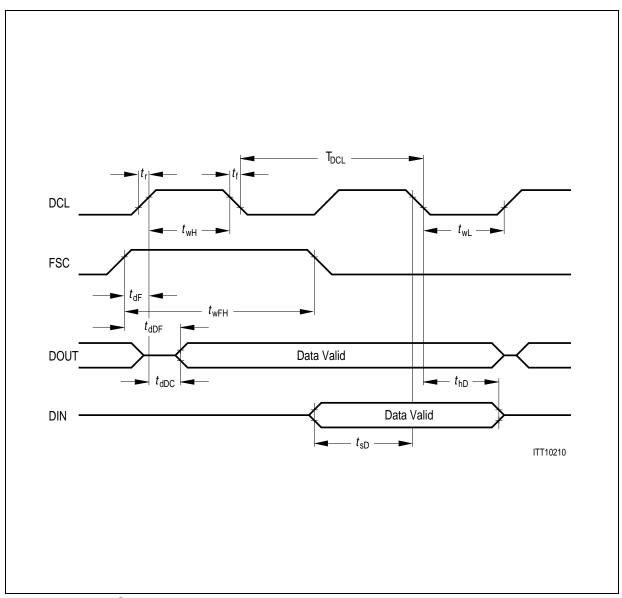

| 31 | 53 | DCL  | DCL  | 0 | Data Clock                                                                                                                                                                       |

|----|----|------|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |      |      |   | Data clock output 512 or 1536 kHz (table 2 on page 26). In µP mode this pin can be programmed to deliver a bit clock (256 or 768 kHz).                                           |

| 30 | 52 | FSC  | FSC  | 0 | Frame Synchronization Clock                                                                                                                                                      |

|    |    |      |      |   | The start of the B1-channel in time-slot 0 is marked. FSC = (1) for one DCL-period indicates a superframe marker. FSC = (1) for at least two DCL-periods marks a standard frame. |

| 26 | 45 | DIN  | DIN  | I | Data In                                                                                                                                                                          |

|    |    |      |      |   | Input of IOM-2 data synchronous to DCL-clock (Data upstream direction).                                                                                                          |

| 27 | 46 | DOUT | DOUT | 0 | Data Out                                                                                                                                                                         |

|    |    |      |      |   | Output of IOM-2 data synchronous to DCL-clock. Open drain or tristate depending on bit/pin DOD (Data Downstream direction).                                                      |

# **U-Interface Pins**

| 15 | 29 | AIN  | AIN  | I | Differential U-Interface Input Connect to hybrid.  |

|----|----|------|------|---|----------------------------------------------------|

| 14 | 28 | BIN  | BIN  | I | Differential U-Interface Input Connect to hybrid.  |

| 6  | 16 | AOUT | AOUT | 0 | Differential U-Interface Output Connect to hybrid. |

| 4  | 13 | BOUT | BOUT | 0 | Differential U-Interface Output Connect to hybrid. |

PU: internal pull-up resistor

PD: internal pull-down resistor

# **Microprocessor Bus Interface (Overview)**

# 1.6 Microprocessor Bus Interface (Overview)

The table below gives an overview of the different microprocessor bus modes.

Table 1

Microprocessor Bus Interface

| Pin n       | umber       | Stand-alone mode | Symbol in processor mode         |                                    |                           |         |  |

|-------------|-------------|------------------|----------------------------------|------------------------------------|---------------------------|---------|--|

| P-LCC<br>44 | T-QFP<br>64 |                  | Siemens/<br>Intel<br>multiplexed | Siemens/<br>Intel<br>demultiplexed | Motorola<br>demultiplexed | Serial  |  |

| 12          | 24          | PMODE = 0        |                                  | PMO                                | DE = 1                    |         |  |

| 45          | 5           | PCD0             | AD0                              | D0                                 | D0                        | n.c.    |  |

| 43          | 4           | PCD1             | AD1                              | D1                                 | D1                        | n.c.    |  |

| 42          | 3           | PCD2             | AD2                              | D2                                 | D2                        | n.c.    |  |

| 41          | 2           | PCRD             | AD3                              | D3                                 | D3                        | n.c.    |  |

| 40          | 1           | PCWR             | AD4                              | D4                                 | D4                        | n.c.    |  |

| 39          | 62          | PCA0             | AD5                              | D5                                 | D5                        | n.c.    |  |

| 38          | 61          | PCA1             | AD6                              | D6                                 | D6                        | n.c.    |  |

| 25          | 44          | GNDd             | AD7                              | D7                                 | D7                        | n.c.    |  |

| 19          | 36          | INT              | ĪNT                              | INT                                | ĪNT                       | ĪNT     |  |

| 24          | 43          | GNDd             | SMODE=0                          | A0                                 | A0                        | SMODE=1 |  |

| 36          | 59          | MS2              | n.c.                             | A1                                 | A1                        | CDIN    |  |

| 35          | 58          | MS1              | n.c.                             | A2                                 | A2                        | CDOUT   |  |

| 33          | 55          | MS0              | n.c.                             | A3                                 | A3                        | n.c.    |  |

| 20          | 37          | TP1              | ALE                              | ALE=0                              | ALE=1                     | CCLK    |  |

| 34          | 57          | MTO              | RD                               | RD                                 | DS                        | n.c.    |  |

| 17          | 32          | DOD              | WR                               | WR                                 | R/W                       | n.c.    |  |

| 3           | 10          | TSP              | CS                               | CS                                 | CS                        | CS      |  |

| 37          | 60          | DISS             | MCLK                             |                                    |                           |         |  |

| 18          | 35          | AUTO             | RST                              |                                    |                           |         |  |

System Integration

### 1.7 System Integration

Due to the IOM-2 interface the IEC-Q TE can be combined with a variety of other devices to fit in numerous applications. This chapter only shows some typical applications of the IEC-Q TE.

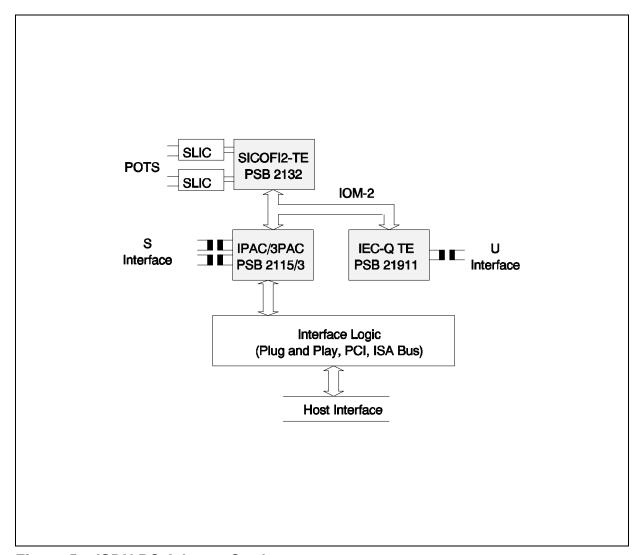

### 1.7.1 ISDN PC Adapter Card

An ISDN adapter card which supports the U-interface may be realized using the IEC-Q TE together with the PSB 2113 3PAC (**figure 5**). The 3PAC provides a D-channel and two B-channel HDLC controllers. Optionally, a PSB 2132 SICOFI2-TE can be connected to provide two POTS interfaces. If an S-interface is required, the PSB 2115 IPAC can be used instead of the 3PAC.

Figure 5 ISDN PC Adapter Card

System Integration

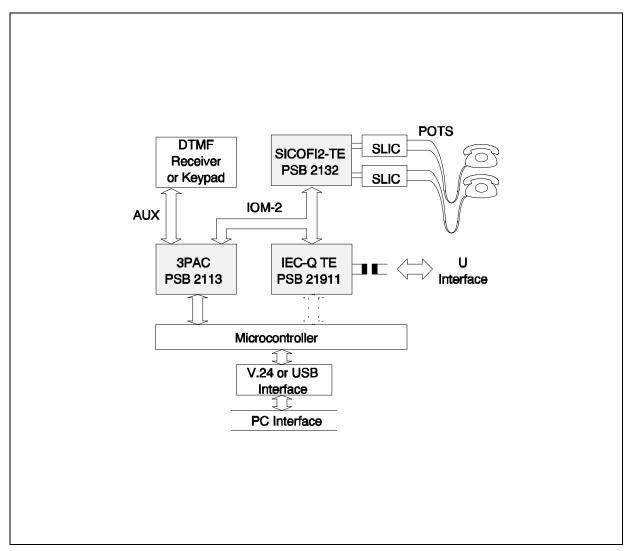

### 1.7.2 ISDN Stand-Alone Terminal with POTS Interface

The IEC-Q TE can be integrated in a microcontroller based stand-alone terminal (figure 6) that is connected to the communications interface of a PC. The PSB 2132 SICOFI-TE enables connection of analog terminals (e.g. telephones or fax) to its dual channel POTS interface.

Figure 6 ISDN Stand-Alone Terminal with POTS Interface

**System Integration**

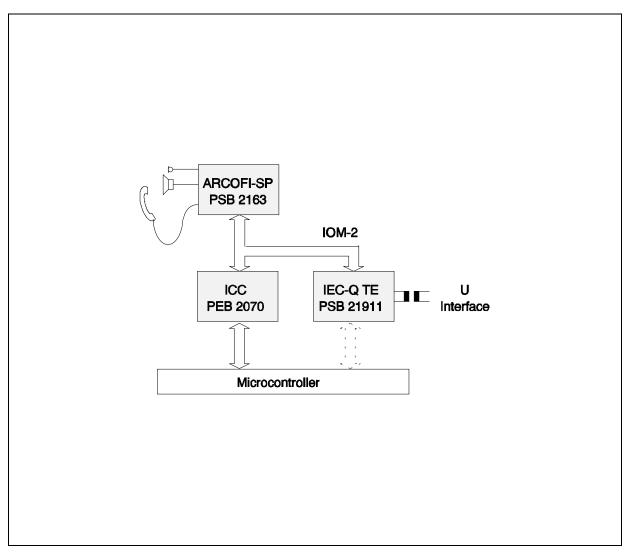

### 1.7.3 ISDN Feature Phone

An ISDN feature phone with U-interface can be built using the IEC-Q TE together with the ARCOFI-SP and the ICC.

Figure 7 ISDN Feature Phone

**System Integration**

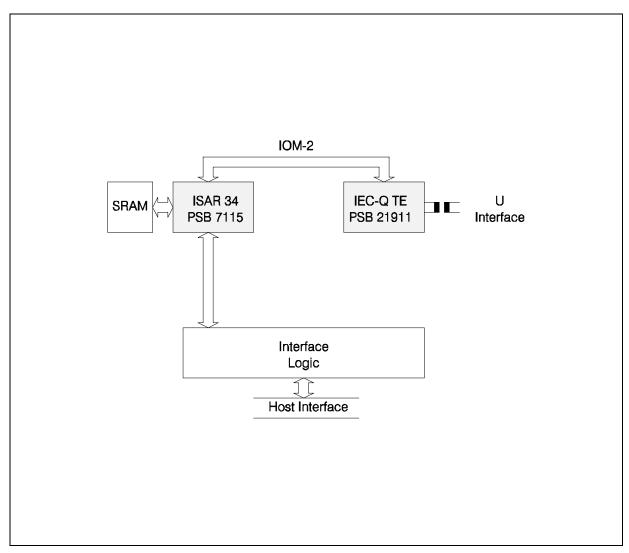

### 1.7.4 ISDN-Modem PC Card

The combination of the IEC-Q TE and a PSB 7115 ISAR 34 allows to build an ISDN-modem PC card .

Figure 8 ISDN-Modem PC Card

Operating Modes

#### 2 **Functional Description**

#### 2.1 Operating Modes

The default configuration after power-on or external reset depends on the state of the PMODE pin. The cases µP mode and stand-alone mode have to be distinguished:

### $\mu P \mod (PMODE = VDD)$

In μP mode a microprocessor interface gives access to the IOM-2 channel registers as well as configuration registers. The operating mode is selected via bits STCR:MS0-MS2 according to table 2. The STCR register is described on page 119.

Test modes Send Single Pulses, Quiet Mode or Data Through are invoked via the corresponding C/I channel command (page 75) or via bits STCR:TM1-2 (table 3).

### Stand-alone mode (PMODE = GND)

In stand-alone mode the operating mode is selected via pin strapping according to table 2. It is possible to change the mode of a device during operation (e.g. for test purposes) if the mode change is followed by a reset.

The test modes Send Single Pulses (SSP), Quiet Mode (QM) and Data Through (DT) are invoked via the corresponding C/I channel command (page 75) or via pins RES and TSP (table 3).

|          | Mode Se        | election       |                | Output<br>Synchr |                    |                                          |

|----------|----------------|----------------|----------------|------------------|--------------------|------------------------------------------|

| Mode     | Bit/Pin<br>MS2 | Bit/Pin<br>MS1 | Bit/Pin<br>MS0 | DCL<br>OUT       | CLS<br>OUT         | Super-<br>frame-<br>marker <sup>1)</sup> |

| NT       | 0              | 0              | 0              | 512              | 7680 <sup>2)</sup> | no                                       |

| NT       | 1              | 0              | 0              | 512              | 7680 <sup>2)</sup> | yes                                      |

| NT-Auto  | 0              | 0              | 1              | 512              | 7680 <sup>2)</sup> | no                                       |

| TE       | 0              | 1              | 0              | 1536             | 7680 <sup>2)</sup> | no                                       |

| TE       | 1              | 1              | 0              | 1536             | 7680 <sup>2)</sup> | yes                                      |

| reserved | others         | •              | •              |                  |                    |                                          |

Modes of Operation (uP and Stand-Alone Mode) Table 2

- **Notes:** 1) 1 DCL-period high-phase of FSC at superframe position

- 2 DCL-periods high-phase of FSC at normal position

- 2) CLS-clock signal not available while device is in power-down

**Operating Modes**

Table 3 Test Modes

| Test-Mode                        | Bit TM1/<br>Pin RES | Bit TM2/<br>Pin TSP |

|----------------------------------|---------------------|---------------------|

| Master-Reset <sup>1)</sup>       | 0                   | 0                   |

| Send Single-Pulses <sup>2)</sup> | 1                   | 1                   |

| Data-Through <sup>3)</sup>       | 0                   | 1                   |

| Normal                           | 1                   | 0                   |

<sup>1)</sup> Used for Quiet Mode and Return Loss measurements

Table 4 DOUT Driver Modes

| Mode                        | Pin    | Pin<br>TSP <sup>2)</sup> | Pin /<br>Bit<br>DOD | Pin DOUT Output Driver |                          |                           |  |

|-----------------------------|--------|--------------------------|---------------------|------------------------|--------------------------|---------------------------|--|

|                             | RES 1) |                          |                     | Value                  | DOUT in active time slot | DOUT in passive time slot |  |

| Pin-Reset                   | 0      | 0                        | х                   | 0                      | low                      | int. pull-up              |  |

|                             |        |                          |                     | 1                      | int. pull-up             |                           |  |

| Normal                      | 1      | 0                        | 0                   | 0                      | low                      | high Z                    |  |

| (Tristate)                  |        |                          |                     | 1                      | high                     |                           |  |

| Normal                      | 1      | 0                        | 1                   | 0                      | low                      | floating                  |  |

| (Open Drain <sup>3)</sup> ) |        |                          |                     | 1                      | floating                 |                           |  |

<sup>1)</sup> In stand-alone mode and µP mode

<sup>2)</sup> Used for Pulse Mask measurements

<sup>3)</sup> Used for Insertion Loss, Power Spectral Density and Total Power measurements

$<sup>^{2)}\,</sup>$  Only in stand-alone mode. In  $\mu P$  mode the output driver of pin DOUT is selected via bit DOD in the ADF2 register

<sup>3)</sup> External pull-up resistors required (typ.1 k $\Omega$ )

**Device Architecture**

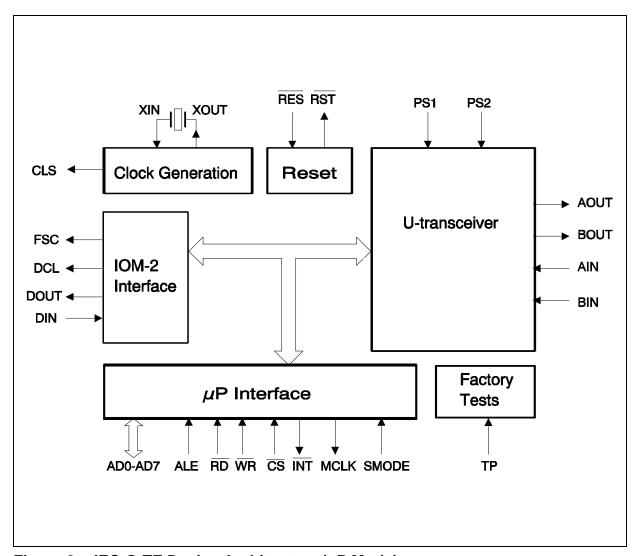

### 2.2 Device Architecture

Factory Test Unit

In µP mode the following interfaces and functional blocks are used:

IOM-2 interface see pp. 30

Microprocessor interface pp. 39, 81, 112

U-transceiver pp. 40

Clock Generation pp. 111

Reset pp. 30

pp. 39, 81, 112

pp. 40

pp. 111

pp. 93

Figure 9 IEC-Q TE Device Architecture (µP Mode)

### **Device Architecture**

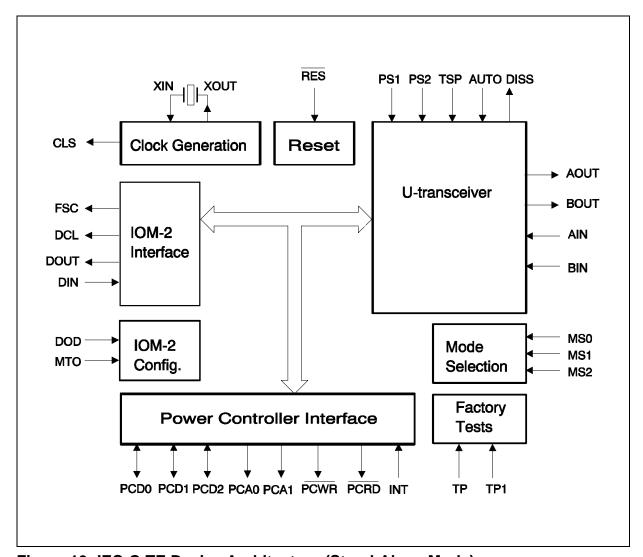

In stand-alone mode the following interfaces and functional blocks are used:

| <ul> <li>Mode Selection</li> </ul>             | see | pp. 26     |

|------------------------------------------------|-----|------------|

| <ul> <li>IOM-2 interface</li> </ul>            |     | pp. 30     |

| <ul> <li>IOM-2 configuration</li> </ul>        |     | pp. 36, 38 |

| <ul> <li>U-transceiver</li> </ul>              |     | pp. 40     |

| <ul> <li>Clock Generation</li> </ul>           |     | pp. 111    |

| Reset                                          |     | pp. 93     |

| <ul> <li>Power Controller Interface</li> </ul> |     | pp. 94     |

| <ul> <li>Factory Test Unit</li> </ul>          |     |            |

Figure 10 IEC-Q TE Device Architecture (Stand-Alone Mode)

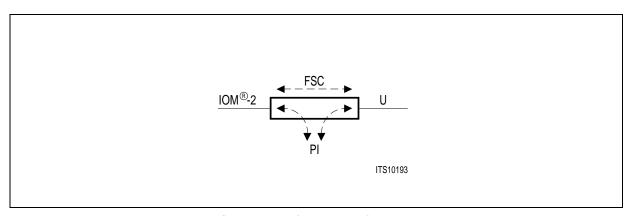

### 2.3 IOM<sup>®</sup>-2 Interface

The IOM-2 interface is used to interconnect telecommunication ICs. It provides a symmetrical full-duplex communication link, containing user data, control/programming and status channels. The structure used follows the 2B + 1D-channel structure of ISDN. The ISDN user data rate of 144 kbit/s (B1 + B2 + D) is transmitted in both directions over the interface.

The IOM-2 interface is a generalization and enhancement of the IOM-1 interface.

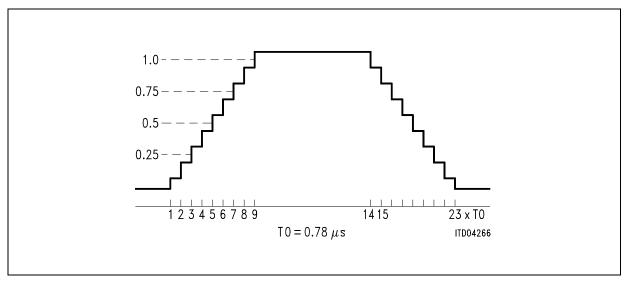

### 2.3.1 IOM®-2 Frame Structure

The IOM-2 interface comprises two clock lines for synchronization and two data lines.

Data is carried over Data Upstream (DU) and Data Downstream (DD) signals. The downstream and upstream direction are always defined with respect to the exchange. Downstream refers to information flow from the exchange to the subscriber and upstream vice versa respectively. The IOM-2 Interface Specification describes open drain data lines with external pull-up resistors. However, if operation is logically point-to-point, tristate operation is possible as well.

The data is clocked by a Data Clock (DCL) that operates at twice the data rate. Frames are delimited by an 8-kHz Frame Synchronization Clock (FSC). Incoming data is sampled on every second falling edge of the DCL clock.

Figure 11 IOM®-2 Clocks and Data Lines

Within one FSC period 32 bit or 96 bit are transmitted, corresponding to DCL frequencies of 512 kHz or 1.536 MHz.

Two optimized IOM-2 timing modes exist:

- NT mode for NT1 applications

- TE mode for terminal and intelligent NT applications

NT or TE mode is selected via pins MS0-2 in stand-alone mode and via bits MS0-2 in  $\mu$ P mode. Both the NT and TE mode utilize the same basic frame and clocking structure, but differ in the number and usage of the individual channels.

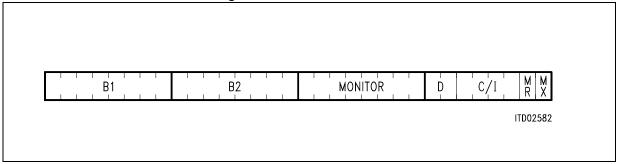

Figure 12 Basic Channel Structure of IOM®-2

Each frame consists of

- two 64 kbit/s channels B1 and B2

- the Monitor channel for transferring maintenance information

- two bits for the 16 kbit/s D-channel

- four command/indication (C/I) bits for controlling of layer-1 functions (U- and Stransceiver).

- two bits MR and MX for the handshake procedure in the Monitor channel

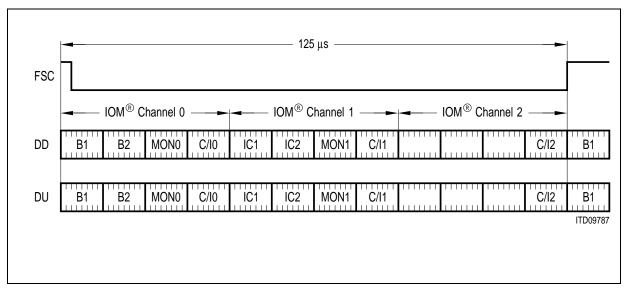

### 2.3.1.1 TE Mode Frame Structure

In TE mode the IEC-Q TE provides a data clock DCL with a frequency of 1536 kHz. As a consequence the IOM-2 interface provides three channels each with a nominal data rate of 256 kbit/s.

- Channel 0 contains 144 kbit/s (for 2B+D) plus Monitor and Command/Indication channels for the layer-1 device.

- Channel 1 contains two 64-kbit/s intercommunication channels plus Monitor and Command/Indication channels for other IOM-2 devices.

- Channel 2 is used for IOM bus arbitration (access to the TIC bus). Only the Command/ Indication bits are used in channel 2.

The IOM-2 signals are:

DIN, DOUT 768 kbit/s

DCL 1536 kHz output

FSC 8 kHz output

11.97

Figure 13 Definition of the IOM®-2 Frame in TE Mode

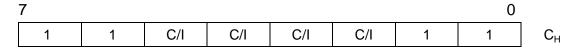

### - C/I0 in IOM®-2 Channel 0:

| DU / DD | D | D | C/I4 | C/I3 | C/I2 | C/I1 | MR | MX |

|---------|---|---|------|------|------|------|----|----|

|         |   |   |      |      |      |      |    | 1  |

**D:** two bits for the 16 kbit/s D-channel

**C/I:** The four command/indication (C/I) bits are used for control of the U-

transceiver (activation/deactivation and additional control

functions).

**MR**, **MX**: two bits MR and MX for the handshake in the Monitor channel 0

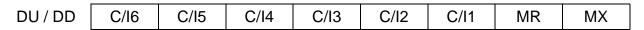

### - C/I1 in IOM®-2 Channel 1:

**C/I1 to C/I6** are used for control of a transceiver or an other device in IOM-2 channel 1 (activation/deactivation and additional control functions).

MR, MX: two bits MR and MX for handshake in the Monitor channel 1

### – C/I2 in IOM®-2 Channel 2:

DU DD

| 1 | 1 | BAC | TBA2 | TBA1 | TBA0 | 1 | 1 |

|---|---|-----|------|------|------|---|---|

| Е | Е | S/G | A/B  | 1    | 1    | 1 | 1 |

E: D-echo bits

**BAC-bit** (Bus ACcessed). When the TIC bus is occupied the BAC-bit is low.

**S/G-bit** (Stop/Go), available to a connected HDLC controller to determine if

it can access the D-channel (S/G = 1: stop, S/G = 0: go).

**A/B-bit** (available/blocked), supplementary bit for D-channel control.

(A/B = 1: D-channel available, A/B = 0: D-channel blocked).

TBA0-2: TIC Bus Address

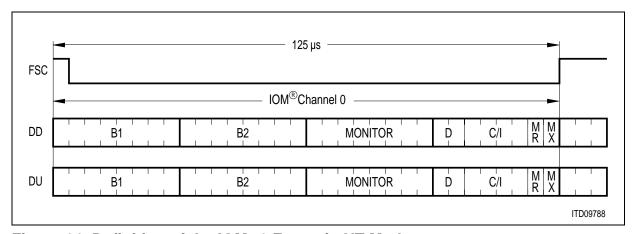

### 2.3.1.2 NT Mode Structure

In NT mode the IEC-Q TE provides a data clock DCL with a frequency of 512 kHz. As a consequence the IOM-2 interface provides only one channel with a nominal data rate of 256 kbit/s.

Channel 0 contains 144 kbit/s (for 2B+D) plus Monitor and Command/Indication channels.

The IOM-2 signals are:

DIN, DOUT 256 kbit/s

DCL 512 kHz output FSC 8 kHz output

Figure 14 Definition of the IOM®-2 Frame in NT Mode

### 2.3.2 IOM®-2 Command / Indication Channels

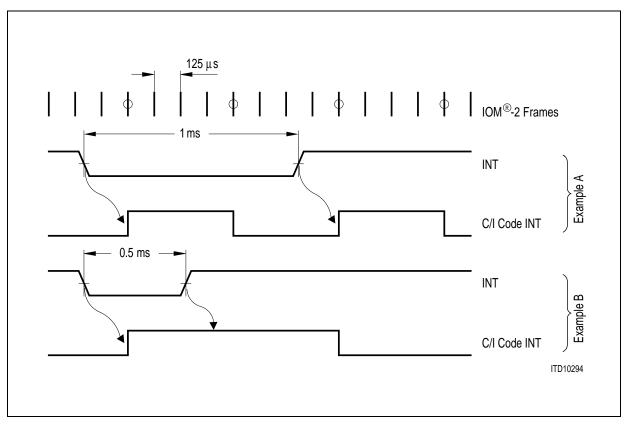

The Command/Indication channels carry real-time control and status information over the IOM-2 interface.

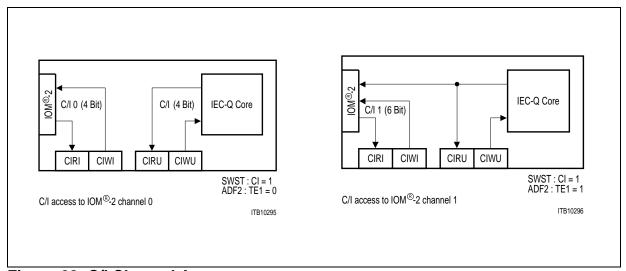

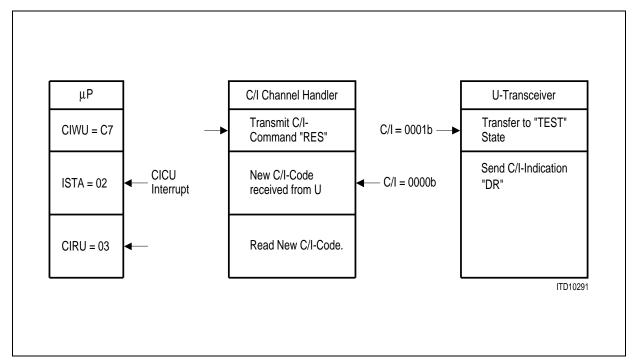

### C/I Channel 0

C/I channel 0 (C/I0) is available in both operational modes (NT and TE mode). The channel consists of four bits in each direction. Activation and deactivation of the U-transceiver is always controlled via the C/I0 channel. The C/I codes going to the U-transceiver are called "commands", those originating from it are referred to as "indications". The C/I codes of the U-transceiver are listed and explained in chapter 2.5.8 on page 74.

In **stand-alone mode** the C/I0 channel is controlled by an external device, e.g. the ICC, 3PAC, IPAC or ISAR.

In  $\mu$ P mode the C/I0 channel can either be controlled by an external device or via the microprocessor interface. For a description on how to access the C/I0 channel via the  $\mu$ P-interface please refer to chapter 2.6.3 on page 83.

### C/I Channel 1

C/I channel 1 (C/I1) is only available in TE mode (DCL = 1.536 MHz). The channel consists of six bits in each direction.

In **stand-alone mode** the C/I1 channel is ignored by the U-transceiver.

In **μP mode** it can be accessed via registers CIWI/U and CIRI/U (page 83).

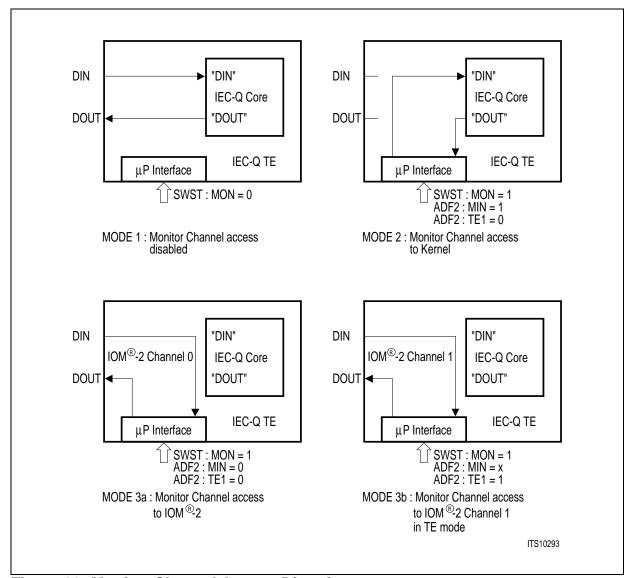

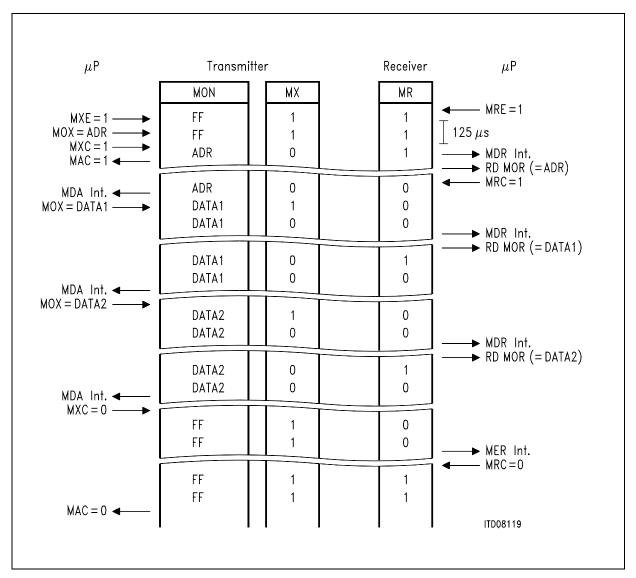

### 2.3.3 IOM<sup>®</sup>-2 Monitor Channel

The Monitor channel protocol is a handshake protocol used for programming and monitoring devices in Monitor channel "0" or "1". These can include the on-chip U-transceiver of the IEC-Q TE as well as external devices connected to the IOM-2 interface.

The Monitor channel operates on an asynchronous basis. While data transfers on the bus take place synchronized to frame sync, the flow of data is controlled by a handshake procedure. For example: data is placed onto the Monitor channel and the MX bit is activated. This data will be transmitted repeatedly once per 8-kHz frame until the transfer is acknowledged via the MR bit.

### **Monitor Channel 0**

Monitor channel 0 is available in both operational modes (NT and TE mode). The U-transceiver is always controlled and monitored via Monitor channel 0. The Monitor channel commands and indications of the U-transceiver are listed and explained on page 51-61.

In **stand-alone mode** the Monitor channel is controlled by an external device, e.g. the ICC, 3PAC, IPAC or ISAR.

In  $\mu P$  mode the Monitor channel can either be controlled by an external device or via the microprocessor interface. For a description on how to access the Monitor 0 channel via the  $\mu P$ -interface please refer to chapter 2.6.4 on page 84.

#### **Monitor Channel 1**

Monitor channel 1 is only available in TE mode (DCL = 1.536 MHz). The channel consists of six bits in each direction.

In **stand-alone mode** the Monitor 1 channel is ignored by the U-transceiver.

In  $\mu$ P mode it can be accessed via the microprocessor interface (page 83) to control an external device (e.g. ARCOFI).

**IOM®-2 Interface**

#### **Monitor Procedure 'Timeout'**

The U-transceiver offers an automatic reset (Monitor procedure "Timeout") for the Monitor routine. This reset function transfers the Monitor channel into the idle state (MR and MX set to high) by issuing "EOM" (End of Message) after a timer has elapsed. As an effect, unacknowledged Monitor messages sent by the U-transceiver are taken away from the Monitor channel.

The U-transceiver checks for unacknowledged Monitor messages every 5 ms. In case the timer expires "EOM" will be issued. The U-transceiver does not repeat the message, hence it will be lost.

In slow applications e.g. testing or evalution platforms this internal reset function may be disabled by setting

- Pin MTO in stand-alone mode

- Bit ADF2:MTO in μP mode.

If Monitor Timeout is disabled, no restrictions regarding the time for completing a Monitor transfer exists.

**IOM®-2 Interface**

# 2.3.4 Activation/Deactivation of IOM®-2 Clocks

The IOM-2 clocks may be switched off if the U-transceiver is in state 'Deactivated'. This reduces power consumption to a minimum. In this deactivated state the clock lines are low and the data lines are high. The power-down condition within the 'Deactivated' state will only be entered if no Monitor messages are pending on IOM-2.

For information on how to keep the IOM-2 clocks active in all states please refer to the application note 'Providing Clocks in Deactivated State' of 09.97.

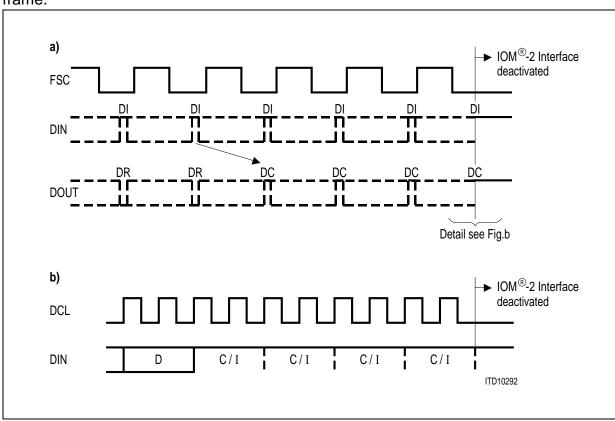

The **deactivation procedure** is shown in **figure 15**. After detecting the code DI (Deactivation Indication) the U-transceiver responds by transmitting DC (Deactivation Confirmation) during subsequent frames and stops the timing signals after the fourth frame.

Figure 15 Deactivation of the IOM®-2 Clocks

The IOM-2 clocks are **activated** automatically when the DIN line is pulled low or a line activation is detected on the U-interface. If a PSB 2186 (ISAC-S TE) or PEB 2070 (ICC) is connected to the IEC-Q TE via IOM-2, the DIN line of the IEC-Q TE is pulled low by

IOM®-2 Interface

setting the SPU bit of the ISAC-S TE or ICC to '1'. Otherwise, the DU line has to be pulled to low via an I/O port of the microcontroller

DCL is activated such that its first rising edge occurs with the beginning of the bit following the C/I0 channel. After the clocks have been enabled this is indicated by the PU code in the C/I0 channel.

## 2.3.5 Superframe Marker

The start of a new superframe on the U-interface may be indicated with a FSC high-phase lasting for one single DCL-period. A FSC high-phase of two DCL-periods is transmitted for all other IOM-2 frame starts.

The superframe marker is disabled if pin/bit MS2 = 0.

## 2.3.6 IOM®-2 Output Driver Selection

In  $\mu P$  mode the output type of the IOM dataline DOUT is selectable via bit ADF2:DOD. In stand-alone mode it is configured via pin DOD. Bit/pin DOD set to 0 selects tristate (reset value) and DOD set to 1 selects open drain outputs.

In the "open drain" mode pull-up resistors (1 k $\Omega$  – 5 k $\Omega$ ) are required on DOUT. FSC and DCL always are push pull.

**Microprocessor Interface**

## 2.4 Microprocessor Interface

The parallel/serial microprocessor interface can be selected to be either of the

- 1. Siemens/Intel non-multiplexed bus type with control signals CS, WR, RD

- 2. Motorola type with control signals CS, R/W, DS

- 3. **Siemens/Intel multiplexed** address/data bus type with control signals **CS**, **WR**, **RD**, **ALE**

- 4. Serial mode using control signals CDIN, CDOUT, CCLK and CS.

The selection is performed via pins ALE/CCLK and SMODE as follows:

Table 5 Microprocessor Interface Modes

|                       | ALE  | SMODE |

|-----------------------|------|-------|

| Siemens/Intel non-Mux | 0    | х     |

| Motorola              | 1    | х     |

| Siemens/Intel Mux     | edge | 0     |

| Serial                | edge | 1     |

The occurrence of an edge on ALE/CCLK, either positive or negative, at any time during the operation immediately selects interface type 3 or 4. A return to one of the other interface types is possible only if a hardware reset is issued.

# 2.4.1 Microprocessor Clock Output

The microprocessor clock is provided in  $\mu P$  mode on the MCLK-output. Four clock rates are provided by a programmable prescaler. These are 7.68 MHz, 3.84 MHz, 1.92 MHz and 0.96 MHz. Switching between the clock rates is realized without spikes. The oscillator remains active all the time. The clock is synchronized to the 15.36 MHz clock at the XIN pin.

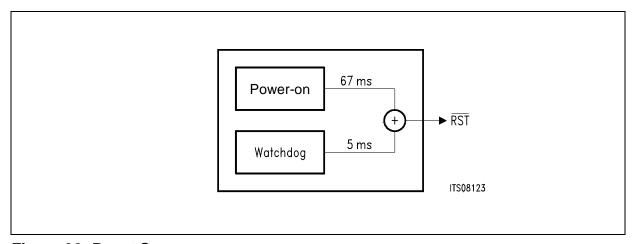

# 2.4.2 Watchdog Timer

The watchdog is enabled by setting the SWST:WT bit to "1". The value of SWST:WT after hardware reset (pin RES low and pin TSP low) is "0".

After the microcontroller has enabled the watchdog timer it has to write the bit patterns "10" and "01" in ADF:WTC1 and ADF:WTC2 within a period of 132 ms. If it fails to do so, a reset signal of 5 ms at pin RST is generated. The clock at pin MCLK remains active during this reset.

## 2.5 U-Transceiver

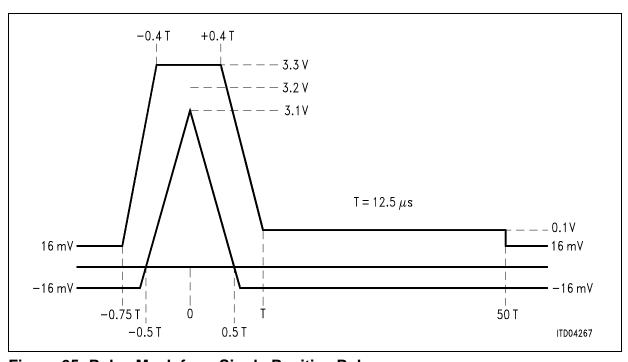

The U-interface establishes the direct link between the exchange and the terminal side over two copper wires. Transmission over the U-interface is performed at a rate of 80 kBaud. The code used is reducing two binary informations to one quaternary symbol (2B1Q) resulting in a total of 160 kbit/s to be transmitted. 144 kbit/s are user data (2B + D), 16 kbit/s are used for maintenance and synchronization information.

The IEC-Q TE uses two differential outputs (AOUT, BOUT) and two differential inputs (AIN, BIN) for transmission and reception. These differential signals are coupled via a hybrid and a transformer to the two-wire U-interface.

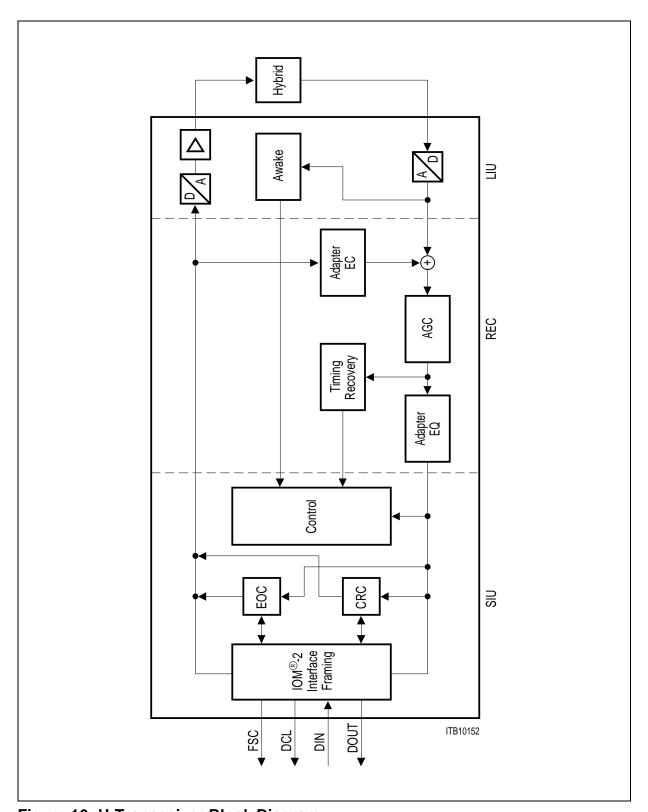

**Figure 16** shows a block diagram of the U-transceiver which can be subdivided in three main blocks:

SIU System Interface Unit

REC Receiver

LIU Line Interface Unit