Wired Communications

Never stop thinking.

Edition 2001-11-12

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# T-SMINTIX 4B3**T S**econd Gen. Modular ISDN NT (Intelligent e**X**tended)

PEF 81902 Version 1.1

Wired Communications

#### PEF 81902

| <b>Revision History</b>                       | r: 2001-11-12                                      | DS 1      |  |  |  |

|-----------------------------------------------|----------------------------------------------------|-----------|--|--|--|

| Previous Version:                             | Preliminary Data Sheet 06.01                       |           |  |  |  |

| Page                                          | Subjects (major changes since last revision)       |           |  |  |  |

| Table 18<br>Figure 34<br>Chapter 2.4.7.4      | Additional C/I-command LTD                         |           |  |  |  |

| Chapter 3.2.3<br>Chapter 4.3<br>Chapter 4.9.4 | The Framer / Deframer Loopback (DLB) is no more su | ipported  |  |  |  |

| Chapter 4.3                                   | Reset value of MASKU is FFh (not 00h)              |           |  |  |  |

| Chapter 4.3<br>Chapter 4.9.8                  | Reset value of FW-Version is 3Eh                   |           |  |  |  |

| Chapter 4.9.4                                 | Restriction of LOOP.LB1, LB2 and LBBD to Transpare | ent state |  |  |  |

| Chapter 5.2                                   | Input Leakage Current AIN, BIN: max. 30μA          |           |  |  |  |

| Chapter 5.4                                   | Reduced power consumption                          |           |  |  |  |

|                                               |                                                    |           |  |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

2001-11-12

| Table of Contents Pa |                                                  |      |  |

|----------------------|--------------------------------------------------|------|--|

| 1                    | Overview                                         | . 1  |  |

| 1.1                  | References                                       | . 2  |  |

| 1.2                  | Features                                         | . 3  |  |

| 1.3                  | Not Supported are                                |      |  |

| 1.4                  | Pin Configuration                                |      |  |

| 1.5                  | Block Diagram                                    | . 6  |  |

| 1.6                  | Pin Definitions and Functions                    | . 7  |  |

| 1.6.1                | Specific Pins and Test Modes                     | 12   |  |

| 1.7                  | System Integration                               | 13   |  |

| 2                    | Functional Description                           | . 16 |  |

| 2.1                  | Microcontroller Interfaces                       |      |  |

| 2.1.1                | Serial Control Interface (SCI)                   | 16   |  |

| 2.1.1.1              | Programming Sequences                            | 19   |  |

| 2.1.2                | Parallel Microcontroller Interface               | 21   |  |

| 2.1.3                | Microcontroller Clock Generation                 | 23   |  |

| 2.2                  | Reset Generation                                 | 24   |  |

| 2.3                  | IOM®-2 Interface                                 | 27   |  |

| 2.3.1                | IOM,-2 Functional Description                    | 27   |  |

| 2.3.2                | IOM,-2 Handler                                   | 28   |  |

| 2.3.2.1              | Controller Data Access (CDA)                     |      |  |

| 2.3.2.2              | Serial Data Strobe Signal                        |      |  |

| 2.3.3                | IOM,-2 Monitor Channel                           | 41   |  |

| 2.3.3.1              | Handshake Procedure                              |      |  |

| 2.3.3.2              | Error Treatment                                  |      |  |

| 2.3.3.3              | MONITOR Channel Programming as a Master Device   |      |  |

| 2.3.3.4              | MONITOR Channel Programming as a Slave Device    |      |  |

| 2.3.3.5              | Monitor Time-Out Procedure                       |      |  |

| 2.3.3.6              | MONITOR Interrupt Logic                          |      |  |

| 2.3.4                | C/I Channel Handling                             |      |  |

| 2.3.5                | D-Channel Access Control                         | _    |  |

| 2.3.5.1              | Application Example for D-Channel Access Control |      |  |

| 2.3.5.2              | TIC Bus Handling                                 |      |  |

| 2.3.5.3              | Stop/Go Bit Handling                             |      |  |

| 2.3.5.4              | D-Channel Arbitration                            |      |  |

| 2.3.5.5              | State Machine of the D-Channel Arbiter           |      |  |

| 2.3.6                | Activation/Deactivation of IOM®-2 Interface      |      |  |

| 2.4                  | U-Transceiver                                    |      |  |

| 2.4.1                | 4B3T Frame Structure                             |      |  |

| 2.4.2                | Maintenance Channel                              |      |  |

| 2.4.3                | Coding from Binary to Ternary Data               |      |  |

| 2.4.4                | Decoding from Ternary to Binary Data             |      |  |

| 2.4.4.1              | Monitoring of Code Violations                    | 64   |  |

Data Sheet

| Table of | Contents                                      | Page  |

|----------|-----------------------------------------------|-------|

| 2.4.4.2  | Block Error Counter (RDS Error Counter)       | 64    |

| 2.4.5    | Scrambler / Descrambler                       |       |

| 2.4.6    | Command/Indication Codes                      | 65    |

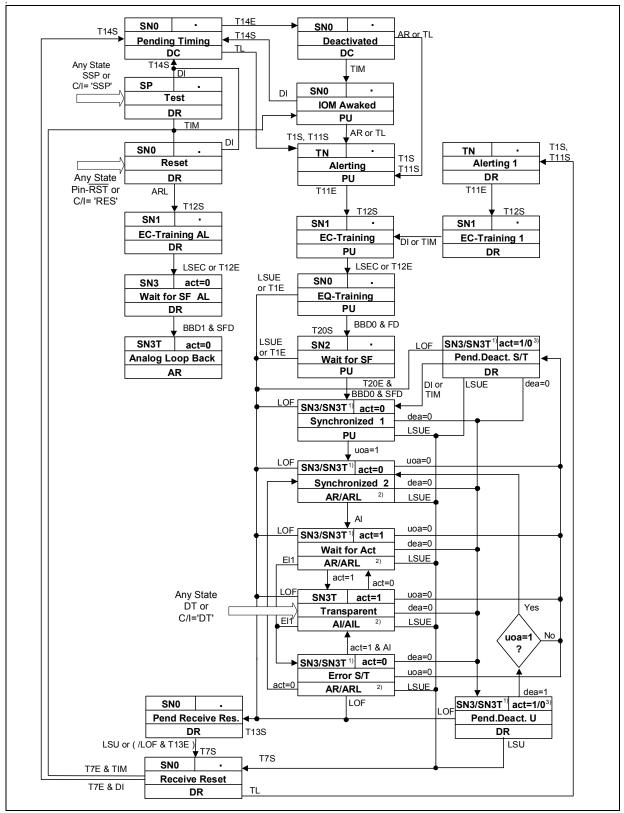

| 2.4.7    | State Machine for Activation and Deactivation | 66    |

| 2.4.7.1  | State Machine Notation                        | 66    |

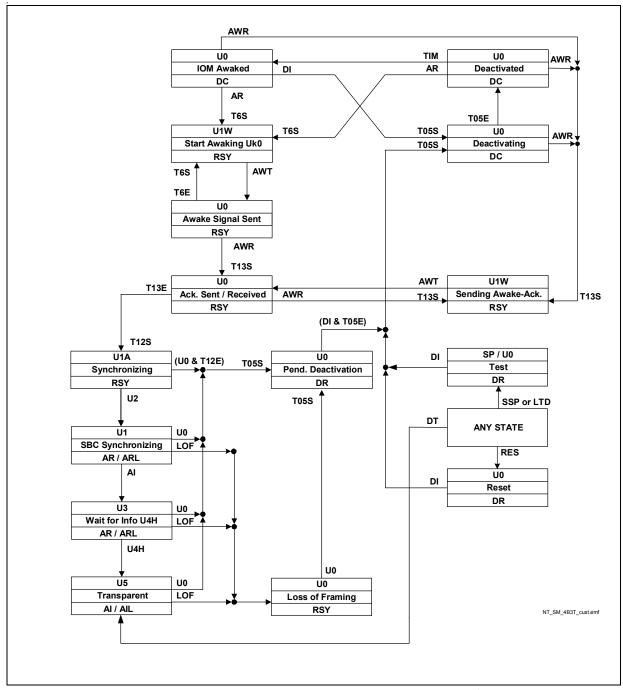

| 2.4.7.2  | Awake Protocol                                | 67    |

| 2.4.7.3  | NT State Machine (IEC-T / NTC-T Compatible)   | 70    |

| 2.4.7.4  | Inputs to the U-Transceiver                   | 71    |

| 2.4.7.5  | Outputs of the U-Transceiver                  | 73    |

| 2.4.7.6  | NT-States                                     | 74    |

| 2.4.8    | U-Transceiver Interrupt Structure             | 76    |

| 2.5      | S-Transceiver                                 | 78    |

| 2.5.1    | Line Coding, Frame Structure                  | 78    |

| 2.5.2    | S/Q Channels, Multiframing                    | 80    |

| 2.5.3    | Data Transfer between IOM,-2 and S0           | 81    |

| 2.5.4    | Loopback 2                                    | 81    |

| 2.5.5    | Control of S-Transceiver / State Machine      | 81    |

| 2.5.5.1  | C/I Codes                                     | 84    |

| 2.5.5.2  | State Machine NT Mode                         | 86    |

| 2.5.5.3  | State Machine LT-S Mode                       | 90    |

| 2.5.6    | S-Transceiver Enable / Disable                | 93    |

| 2.5.7    | Interrupt Structure S-Transceiver             | 94    |

| 2.6      | HDLC Controller                               | 95    |

| 2.6.1    | Message Transfer Modes                        | 95    |

| 2.6.2    | Data Reception                                | 96    |

| 2.6.2.1  | Structure and Control of the Receive FIFO     | 96    |

| 2.6.2.2  | Receive Frame Structure                       | . 102 |

| 2.6.3    | Data Transmission                             | . 104 |

| 2.6.3.1  | Structure and Control of the Transmit FIFO    | . 104 |

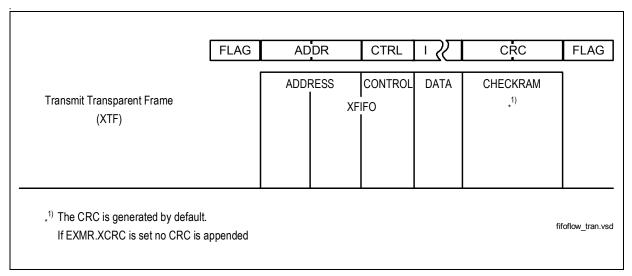

| 2.6.3.2  | Transmit Frame Structure                      | . 109 |

| 2.6.4    | Access to IOM,-2 channels                     | . 110 |

| 2.6.5    | Extended Transparent Mode                     | . 110 |

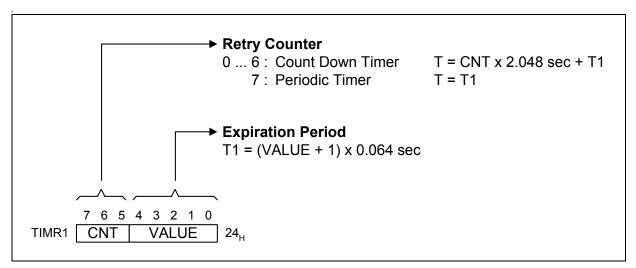

| 2.6.6    | Timer                                         | . 111 |

| 2.6.7    | HDLC Controller Interrupts                    |       |

| 2.6.8    | Test Function                                 |       |

| 2.6.9    | Reset Behavior                                | . 114 |

| 3        | Operational Description                       | . 115 |

| 3.1      | Layer 1 Activation/Deactivation               | . 115 |

| 3.1.1    | Generation of 4B3T Signal Elements            |       |

| 3.1.2    | Complete Activation Initiated by Exchange     |       |

| 3.1.3    | Complete Activation Initiated by TE           |       |

| 3.1.4    | Complete Activation Initiated by NT           |       |

| Table of                                                                                                                   | Contents                                                                                                                                                                                                                                                                                                                | Page                                                                          |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 3.1.5<br>3.1.6<br>3.2<br>3.2.1<br>3.2.2<br>3.2.2.1<br>3.2.2.2<br>3.2.3<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5 | Complete Deactivation Loop 2  Layer 1 Loopbacks Analog Loop-Back S-Transceiver Loopback No.2 Complete Loopback Loopback No.2 - Single Channel Loopbacks Local Loopbacks Featured By the LOOP Register  External Circuitry Power Supply Blocking Recommendation U-Transceiver S-Transceiver Oscillator Circuitry General | . 122<br>. 123<br>. 124<br>. 125<br>. 125<br>. 127<br>. 127<br>. 129<br>. 132 |

| 4                                                                                                                          | Register Description                                                                                                                                                                                                                                                                                                    |                                                                               |

| 4.1<br>4.2<br>4.3<br>4.3.1                                                                                                 | Address Space                                                                                                                                                                                                                                                                                                           | . 134                                                                         |

| 4.3.2                                                                                                                      | C/I-Code RESET 143  Mode Register Evaluation Timing                                                                                                                                                                                                                                                                     |                                                                               |

| 4.4<br>4.4.1                                                                                                               | Detailed HDLC Control and C/I Registers                                                                                                                                                                                                                                                                                 | . 145                                                                         |

| 4.4.2<br>4.4.3                                                                                                             | XFIFO - Transmit FIFO                                                                                                                                                                                                                                                                                                   | . 145                                                                         |

| 4.4.4<br>4.4.5                                                                                                             | MASKH - Mask Register HDLC                                                                                                                                                                                                                                                                                              | . 148                                                                         |

| 4.4.6<br>4.4.7                                                                                                             | CMDR - Command Register                                                                                                                                                                                                                                                                                                 | . 150                                                                         |

| 4.4.8<br>4.4.9                                                                                                             | EXMR - Extended Mode Register                                                                                                                                                                                                                                                                                           | . 153                                                                         |

| 4.4.10<br>4.4.11                                                                                                           | SAP1 - SAPI1 Register                                                                                                                                                                                                                                                                                                   | . 155                                                                         |

| 4.4.12<br>4.4.13                                                                                                           | RBCL - Receive Frame Byte Count Low                                                                                                                                                                                                                                                                                     | . 156                                                                         |

| 4.4.14<br>4.4.15                                                                                                           | TEI1 - TEI1 Register                                                                                                                                                                                                                                                                                                    | . 157                                                                         |

| 4.4.16<br>4.4.17                                                                                                           | RSTA - Receive Status Register                                                                                                                                                                                                                                                                                          | . 159                                                                         |

| 4.4.18<br>4.4.19<br>4.4.20                                                                                                 | CIR0 - Command/Indication Receive 0                                                                                                                                                                                                                                                                                     | . 161                                                                         |

| Table of | Contents                                                | Page  |

|----------|---------------------------------------------------------|-------|

| 4.4.21   | CIX1 - Command/Indication Transmit 1                    | . 162 |

| 4.5      | Detailed S-Transceiver Registers                        | . 163 |

| 4.5.1    | S_CONF0 - S-Transceiver Configuration Register 0        | . 163 |

| 4.5.2    | S_CONF2 - S-Transmitter Configuration Register 2        | . 164 |

| 4.5.3    | S_STA - S-Transceiver Status Register                   | . 165 |

| 4.5.4    | S_CMD - S-Transceiver Command Register                  | . 166 |

| 4.5.5    | SQRR - S/Q-Channel Receive Register                     | . 167 |

| 4.5.6    | SQXR- S/Q-Channel Transmit Register                     | . 167 |

| 4.5.7    | ISTAS - Interrupt Status Register S-Transceiver         | . 168 |

| 4.5.8    | MASKS - Mask S-Transceiver Interrupt                    | . 169 |

| 4.5.9    | S_MODE - S-Transceiver Mode                             | . 170 |

| 4.6      | Interrupt and General Configuration Registers           | . 171 |

| 4.6.1    | ISTA - Interrupt Status Register                        | . 171 |

| 4.6.2    | MASK - Mask Register                                    | . 172 |

| 4.6.3    | MODE1 - Mode1 Register                                  | . 173 |

| 4.6.4    | MODE2 - Mode2 Register                                  | . 174 |

| 4.6.5    | ID - Identification Register                            | . 175 |

| 4.6.6    | SRES - Software Reset Register                          | . 176 |

| 4.7      | Detailed IOM®-2 Handler Registers                       | . 176 |

| 4.7.1    | CDAxy - Controller Data Access Register xy              | . 176 |

| 4.7.2    | XXX_TSDPxy - Time Slot and Data Port Selection for CHxy | . 177 |

| 4.7.3    | CDAx_CR - Control Register Controller Data Access CH1x  | . 178 |

| 4.7.4    | S_CR - Control Register S-Transceiver Data              | . 179 |

| 4.7.5    | HCI_CR - Control Register for HDLC and Cl1 Data         | . 180 |

| 4.7.6    | MON_CR - Control Register Monitor Data                  | . 182 |

| 4.7.7    | SDS1_CR - Control Register Serial Data Strobe 1         | . 182 |

| 4.7.8    | SDS2_CR - Control Register Serial Data Strobe 2         | . 183 |

| 4.7.9    | IOM_CR - Control Register IOM Data                      |       |

| 4.7.10   | MCDA - Monitoring CDA Bits                              | . 186 |

| 4.7.11   | STI - Synchronous Transfer Interrupt                    |       |

| 4.7.12   | ASTI - Acknowledge Synchronous Transfer Interrupt       |       |

| 4.7.13   | MSTI - Mask Synchronous Transfer Interrupt              |       |

| 4.8      | Detailed MONITOR Handler Registers                      |       |

| 4.8.1    | MOR - MONITOR Receive Channel                           |       |

| 4.8.2    | MOX - MONITOR Transmit Channel                          |       |

| 4.8.3    | MOSR - MONITOR Interrupt Status Register                |       |

| 4.8.4    | MOCR - MONITOR Control Register                         |       |

| 4.8.5    | MSTA - MONITOR Status Register                          |       |

| 4.8.6    | MCONF - MONITOR Configuration Register                  |       |

| 4.9      | Detailed U-Transceiver Registers                        |       |

| 4.9.1    | OPMODE - Operation Mode Register                        |       |

| 4.9.2    | UCIR - C/I Code Read Register                           | . 192 |

#### PEF 81902

| Table of                                                                                 | Contents                                                                                                                                                                                                                                                              | Page                                                                          |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 4.9.3<br>4.9.4<br>4.9.5<br>4.9.6<br>4.9.7<br>4.9.8                                       | UCIW - C/I Code Write Register  LOOP - Loopback Register  RDS - Block Error Counter Register  ISTAU - Interrupt Status Register U-Interface  MASKU - Mask Register U-Interface  FW_VERSION                                                                            | . 192<br>. 194<br>. 194<br>. 195                                              |

| 5<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.5 | Electrical Characteristics  Absolute Maximum Ratings  DC Characteristics  Capacitances  Power Consumption  Supply Voltages  AC Characteristics  IOM®-2 Interface  Serial µP Interface  Parallel µP Interface  Reset  Undervoltage Detection Characteristics           | . 197<br>. 198<br>. 200<br>. 200<br>. 202<br>. 203<br>. 205<br>. 206<br>. 209 |

| 6                                                                                        | Package Outlines                                                                                                                                                                                                                                                      | . 212                                                                         |

| 7 7.1 7.1.1 7.1.2 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.2.5 7.3                                  | Appendix: Differences between Q- and T-SMINT,IX  Pinning Pin Definitions and Functions LED Pin ACT  U-Transceiver U-Interface Conformity U-Transceiver State Machines Command/Indication Codes Interrupt Structure Register Summary U-Transceiver  External Circuitry | . 215<br>. 215<br>. 216<br>. 216<br>. 217<br>. 220<br>. 221<br>. 223<br>. 226 |

| 8                                                                                        | Index                                                                                                                                                                                                                                                                 | . 221                                                                         |

| List of Fig | gures Pa                                                                 | ge |

|-------------|--------------------------------------------------------------------------|----|

| Figure 1    | Pin Configuration                                                        | 5  |

| Figure 2    | Block Diagram                                                            |    |

| Figure 3    | Application Example T-SMINT®IX: Low Cost Intelligent NT                  | 13 |

| Figure 4    | Control via µP Interface                                                 |    |

| Figure 5    | Control via IOM,-2 Interface                                             |    |

| Figure 6    | Serial Control Interface Timing                                          | 18 |

| Figure 7    | Serial Command Structure                                                 | 19 |

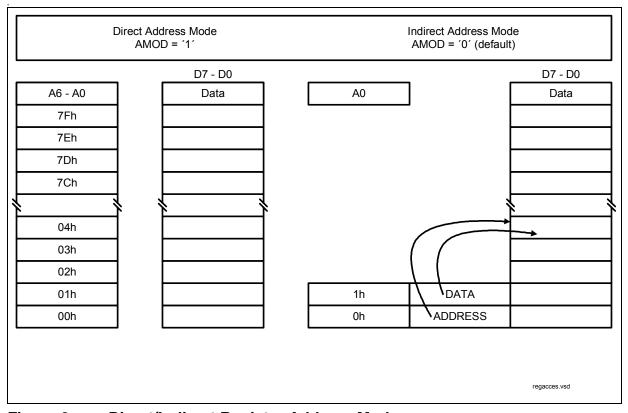

| Figure 8    | Direct/Indirect Register Address Mode                                    | 23 |

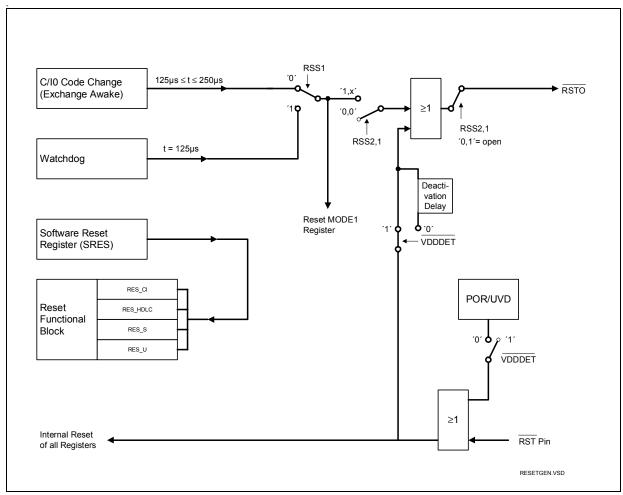

| Figure 9    | Reset Generation of the T-SMINT,IX                                       | 24 |

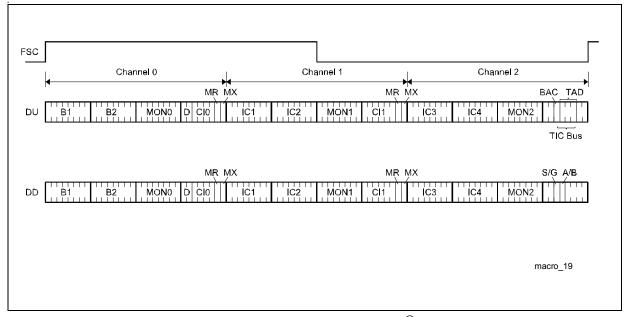

| Figure 10   | IOM®-2 Frame Structure of the T-SMINT,IX                                 | 27 |

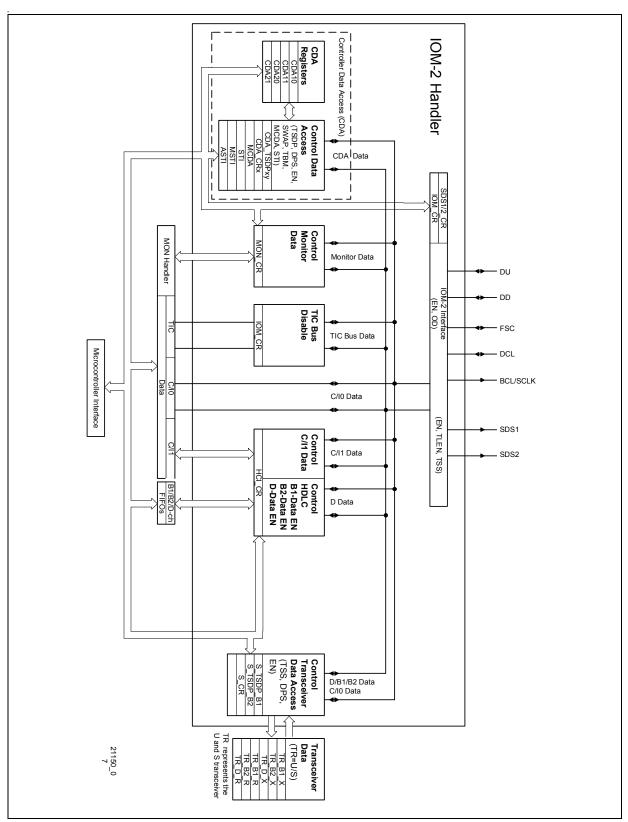

| Figure 11   | Architecture of the IOM,-2 Handler                                       | 29 |

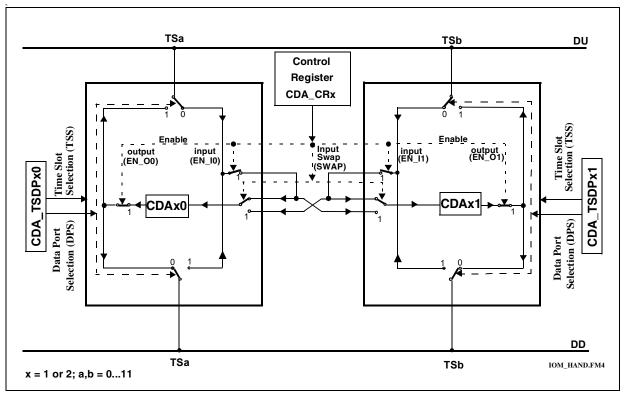

| Figure 12   | Data Access via CDAx0 and CDAx1 register pairs                           | 31 |

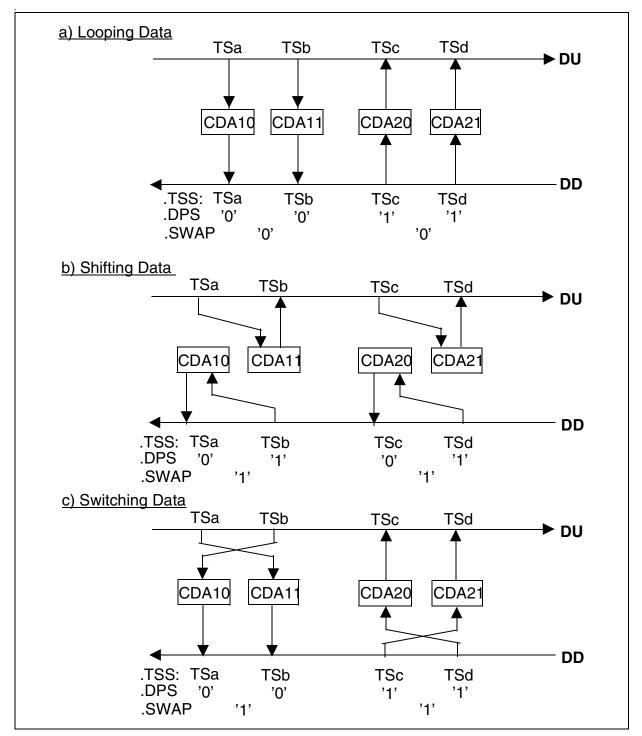

| Figure 13   | Examples for Data Access via CDAxy Registers                             | 32 |

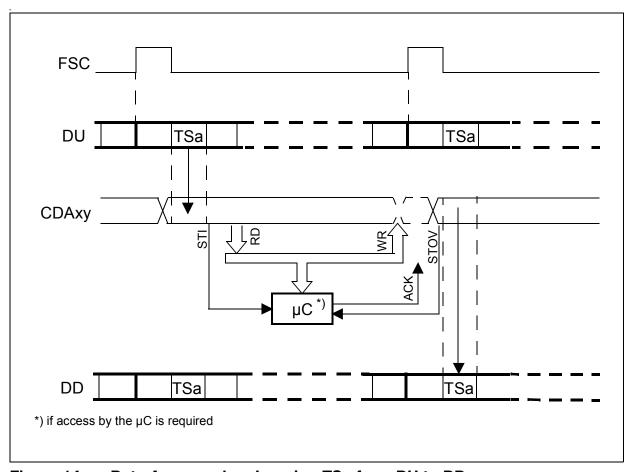

| Figure 14   | Data Access when Looping TSa from DU to DD                               | 33 |

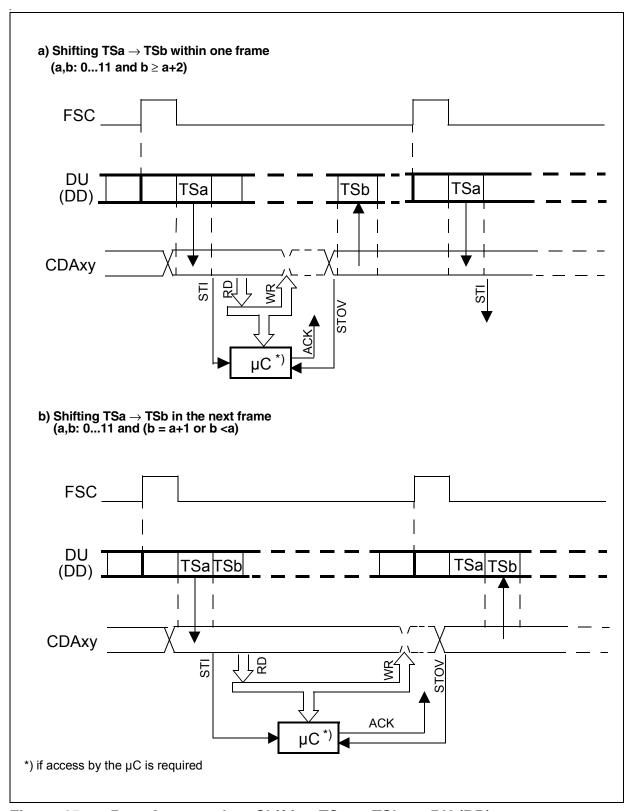

| Figure 15   | Data Access when Shifting TSa to TSb on DU (DD)                          | 34 |

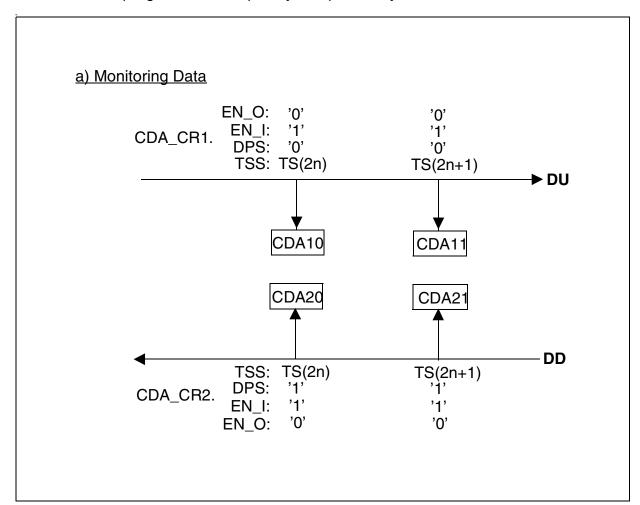

| Figure 16   | Example for Monitoring Data                                              | 35 |

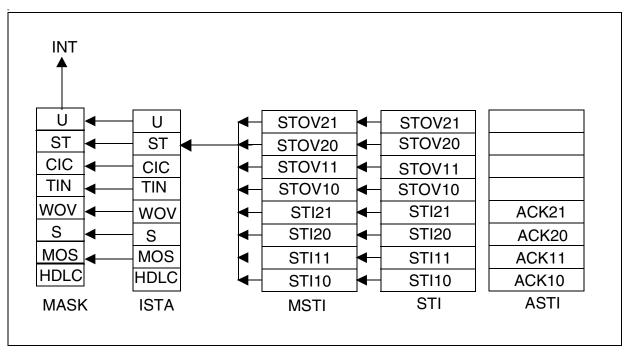

| Figure 17   | Interrupt Structure of the Synchronous Data Transfer                     | 38 |

| Figure 18   | Examples for the Synchronous Transfer Interrupt Control with one STI:    | ху |

|             | enabled 39                                                               |    |

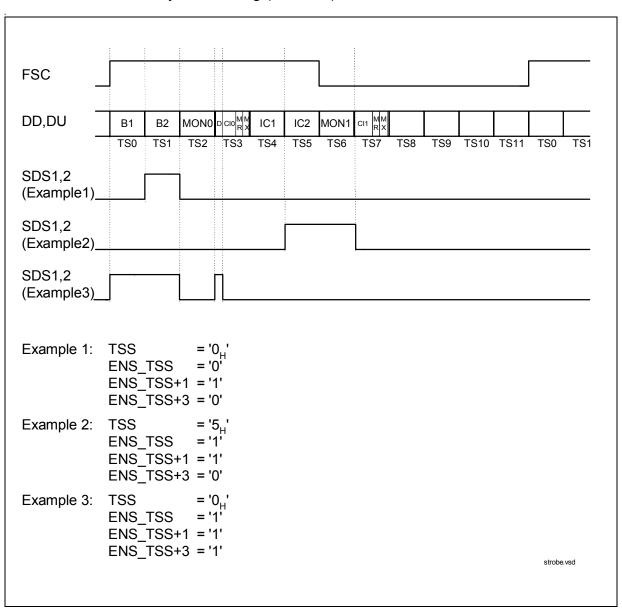

| Figure 19   | Data Strobe Signal Generation                                            | 40 |

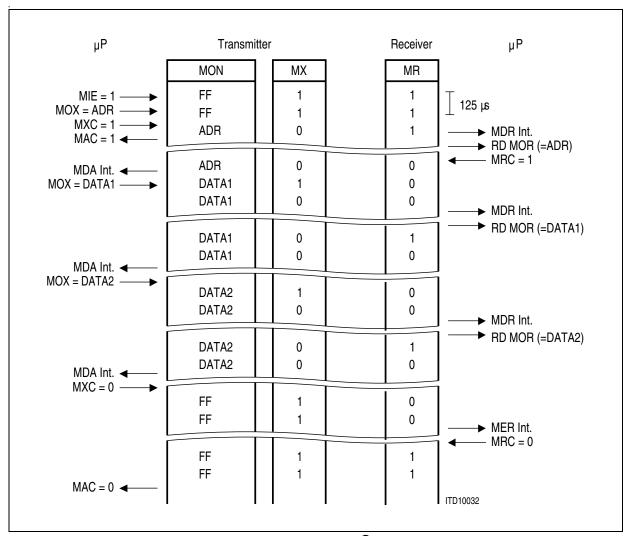

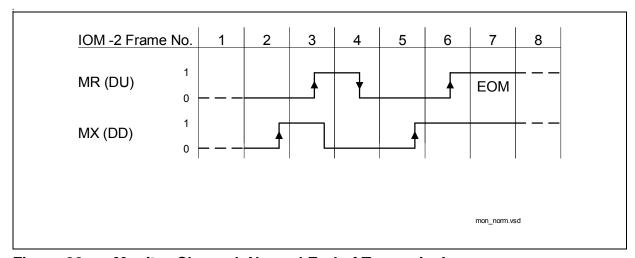

| Figure 20   | MONITOR Channel Protocol (IOM®-2)                                        | 43 |

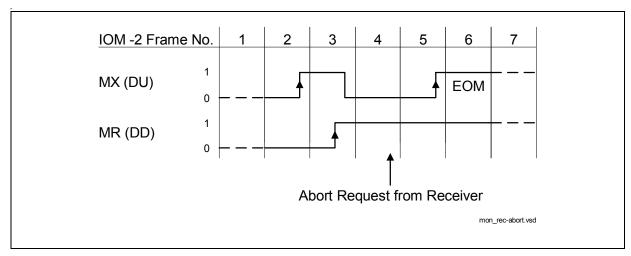

| Figure 21   | Monitor Channel, Transmission Abort requested by the Receiver            | 46 |

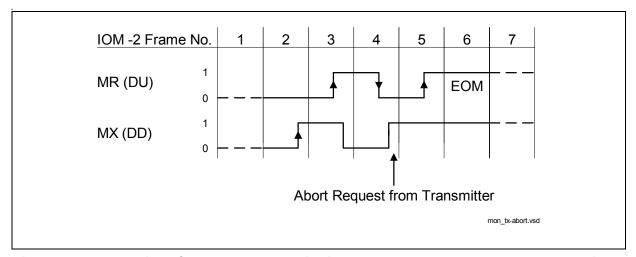

| Figure 22   | Monitor Channel, Transmission Abort requested by the Transmitter         | 46 |

| Figure 23   | Monitor Channel, Normal End of Transmission                              | 46 |

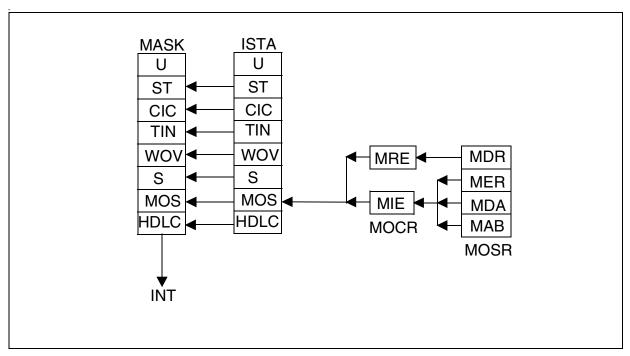

| Figure 24   | MONITOR Interrupt Structure                                              | 49 |

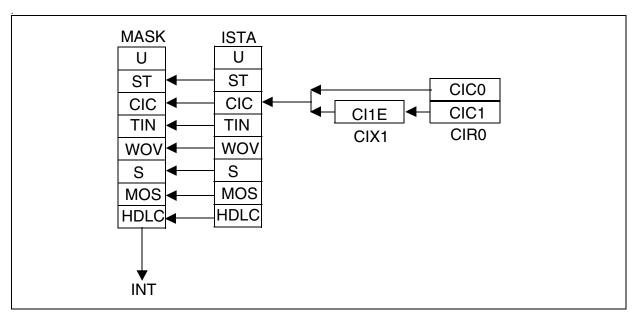

| Figure 25   | CIC Interrupt Structure                                                  |    |

| Figure 26   | D-Channel Arbitration: $\mu C$ has no HDLC and no Direct Access to TIC B | us |

|             | 51                                                                       |    |

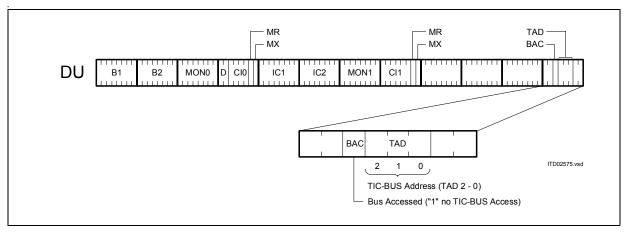

| Figure 27   | Structure of Last Octet of Ch2 on DU                                     | 52 |

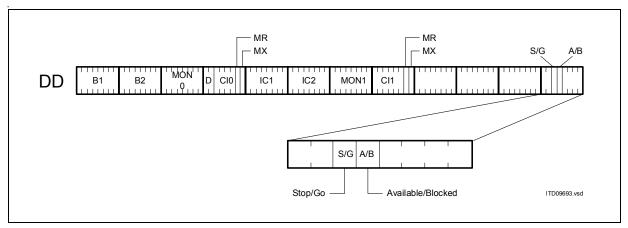

| Figure 28   | Structure of Last Octet of Ch2 on DD                                     |    |

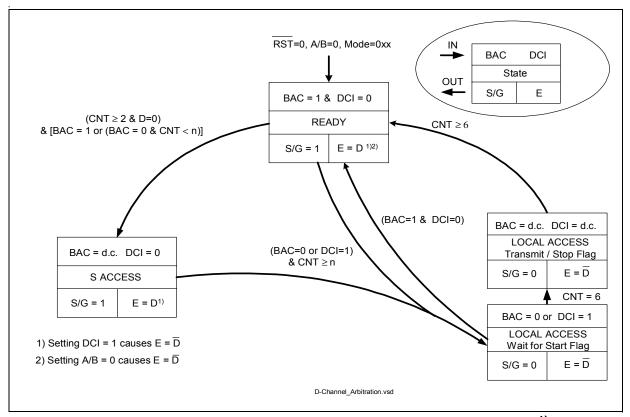

| Figure 29   | State Machine of the D-Channel Arbiter (Simplified View)                 |    |

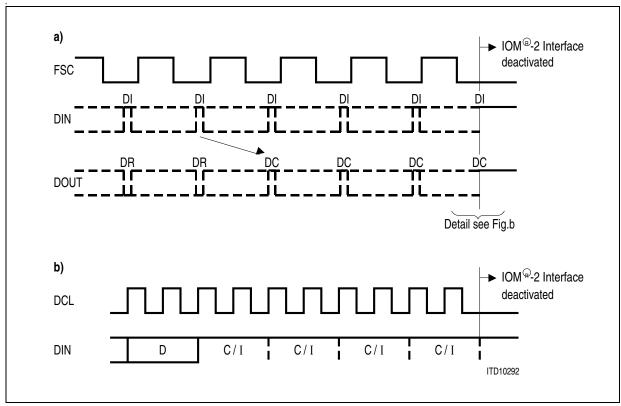

| Figure 30   | Deactivation of the IOM $^{	exttt{@}}$ -2 Clocks $\dots$                 |    |

| Figure 31   | State Diagram Example                                                    |    |

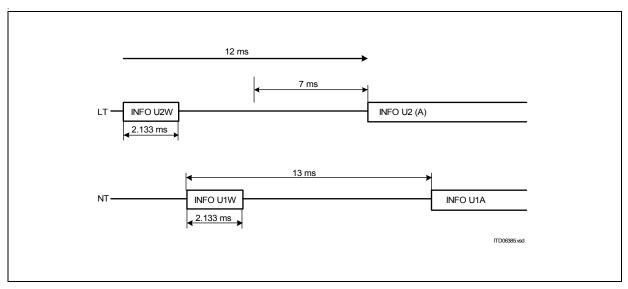

| Figure 32   | Awake Procedure initiated by the LT                                      |    |

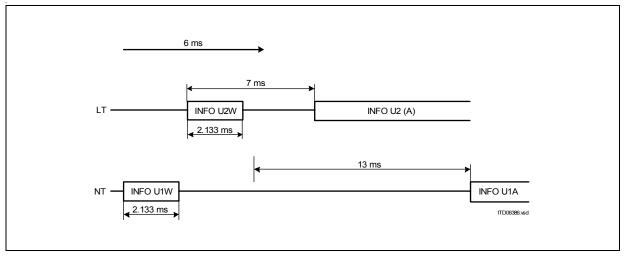

| Figure 33   | Awake Procedure initiated by the NT                                      |    |

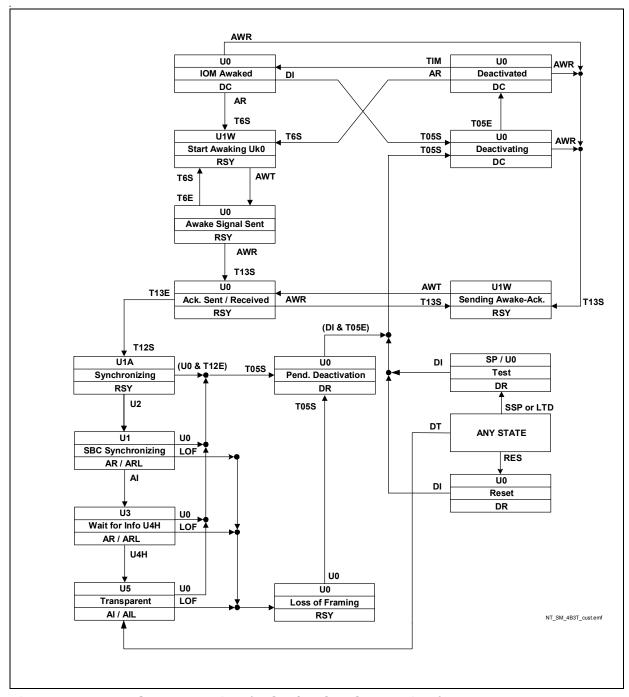

| Figure 34   | NT State Machine (IEC-T/NTC-T Compatible)                                |    |

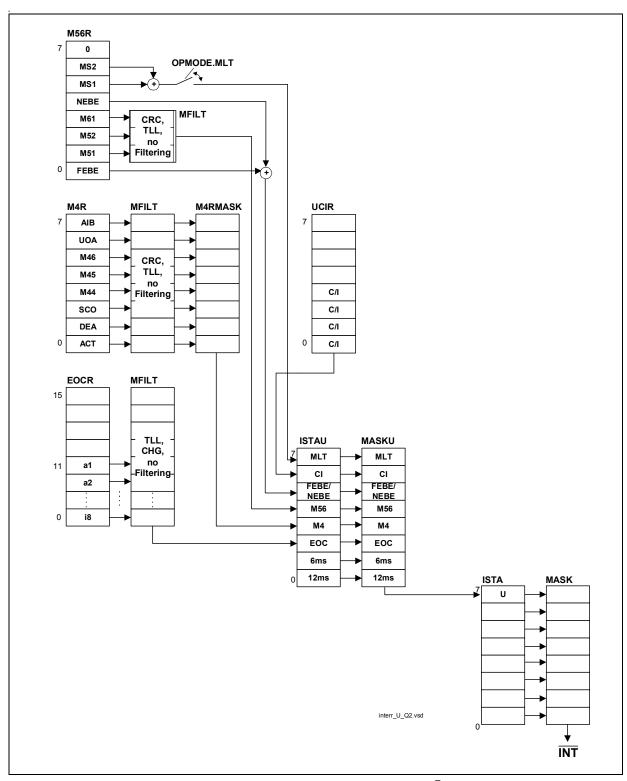

| Figure 35   | · ·                                                                      | 77 |

| Figure 36   | S/T -Interface Line Code                                                 |    |

| Figure 37   | ,                                                                        | 79 |

| Figure 38   |                                                                          | 82 |

| Figure 39   | State Diagram Notation                                                   |    |

| Figure 40   | State Machine NT Mode                                                    | 86 |

| List of Figures Pa |                                                       |     |

|--------------------|-------------------------------------------------------|-----|

| Figure 41          | State Machine LT-S Mode                               | 90  |

| Figure 42          | Interrupt Structure S-Transceiver                     |     |

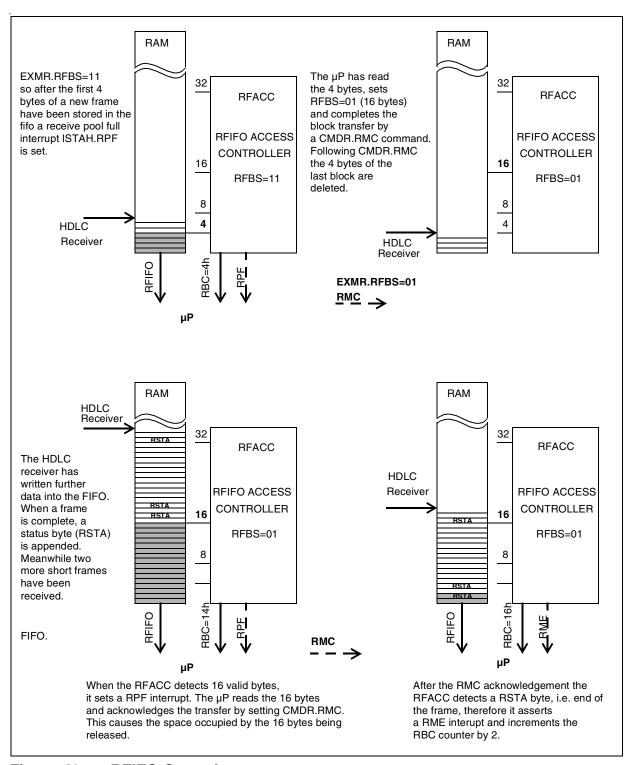

| Figure 43          | RFIFO Operation                                       |     |

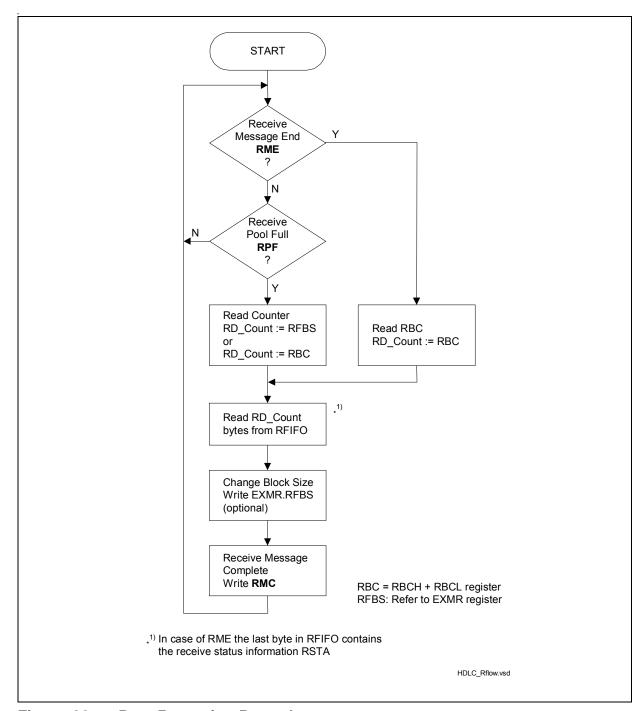

| Figure 44          | Data Reception Procedures                             |     |

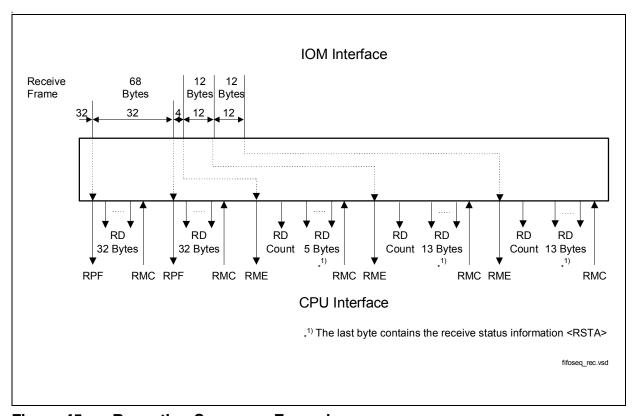

| Figure 45          | Reception Sequence Example                            |     |

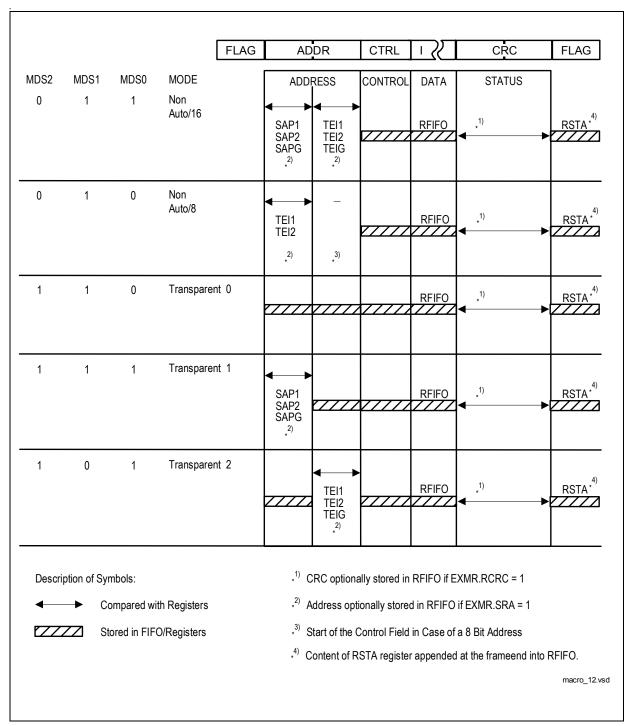

| Figure 46          | Receive Data Flow                                     |     |

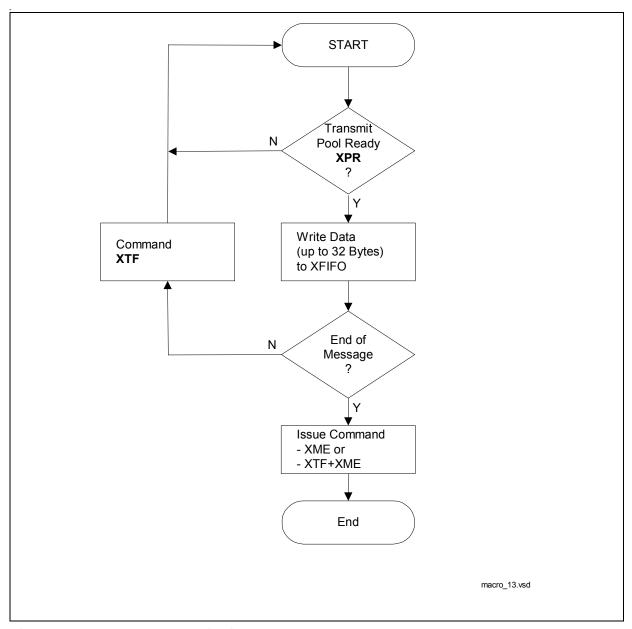

| Figure 47          | Data Transmission Procedure                           |     |

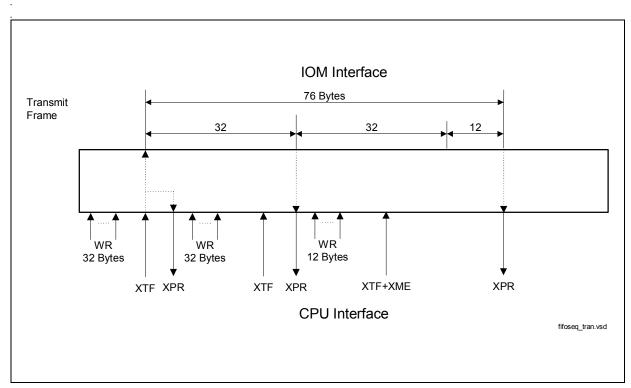

| Figure 48          | Transmission Sequence Example                         |     |

| Figure 49          | Transmit Data Flow                                    |     |

| Figure 50          | Timer Register                                        |     |

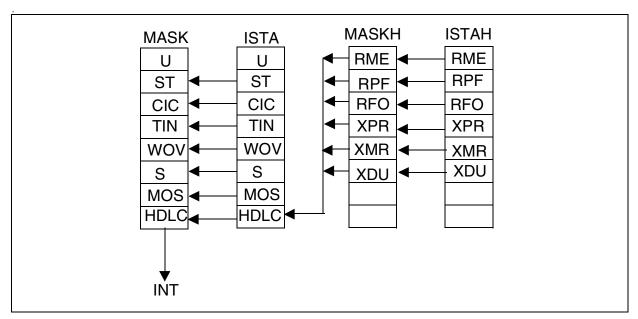

| Figure 51          | Interrupt Status Registers of the HDLC Controller     |     |

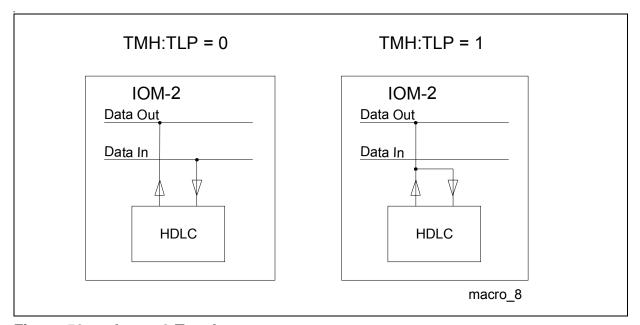

| Figure 52          | Layer 2 Test Loops                                    |     |

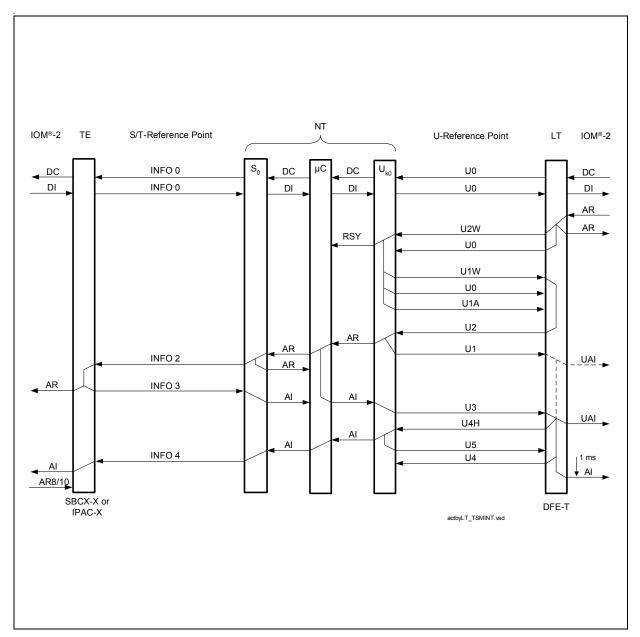

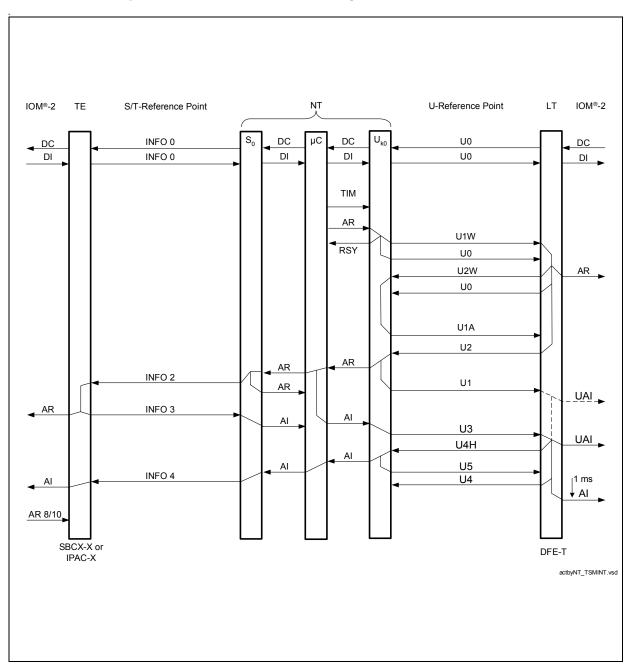

| Figure 53          | Activation Initiated by Exchange                      |     |

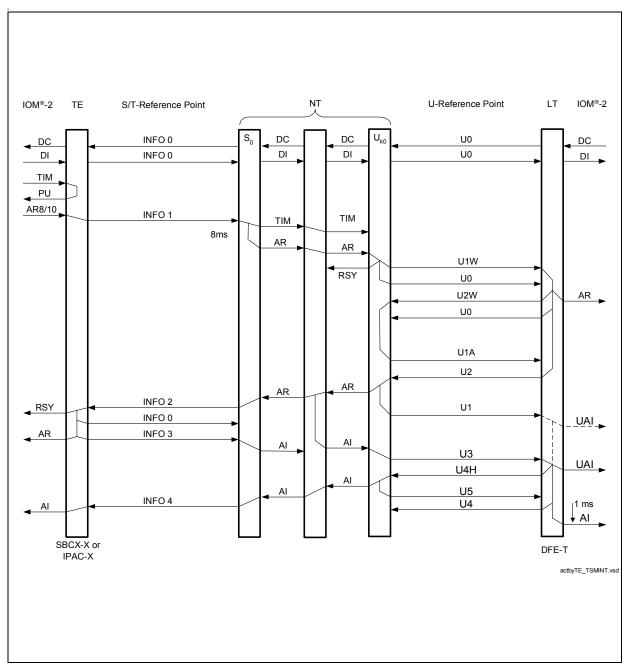

| Figure 54          | Activation Initiated by TE                            |     |

| Figure 55          | Activation Initiated by NT                            |     |

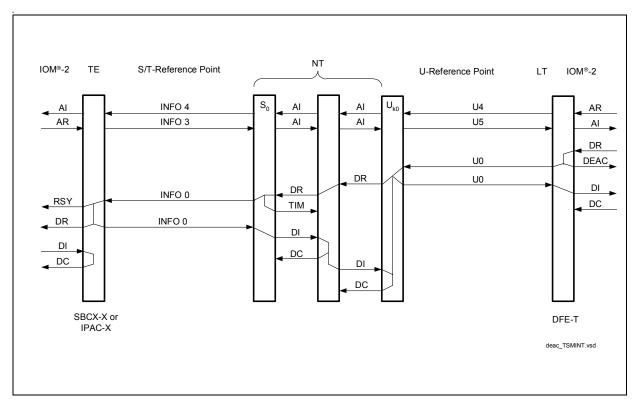

| Figure 56          | Complete Deactivation                                 |     |

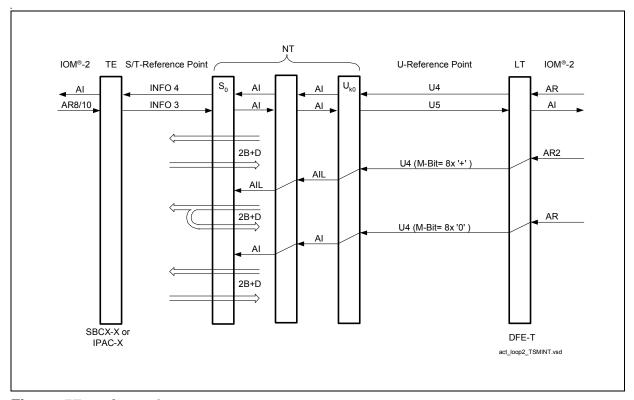

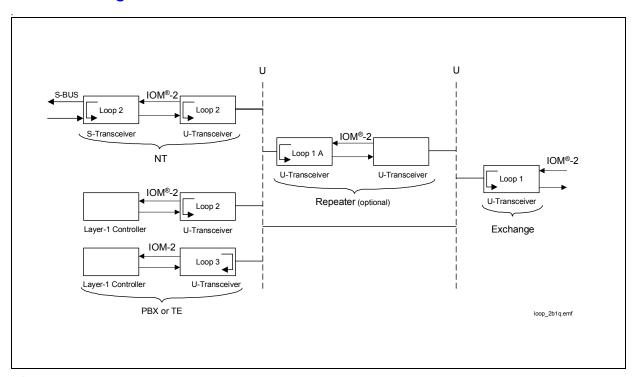

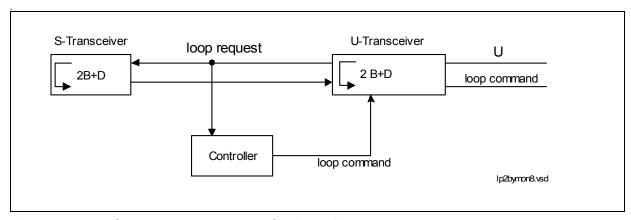

| Figure 57          | Loop 2                                                |     |

| Figure 58          | Test Loopbacks                                        |     |

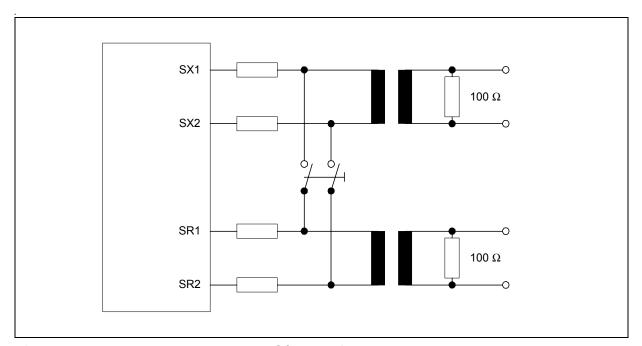

| Figure 59          | External Loop at the S/T-Interface                    |     |

| Figure 60          | Complete Loopback Options in NT-Mode                  |     |

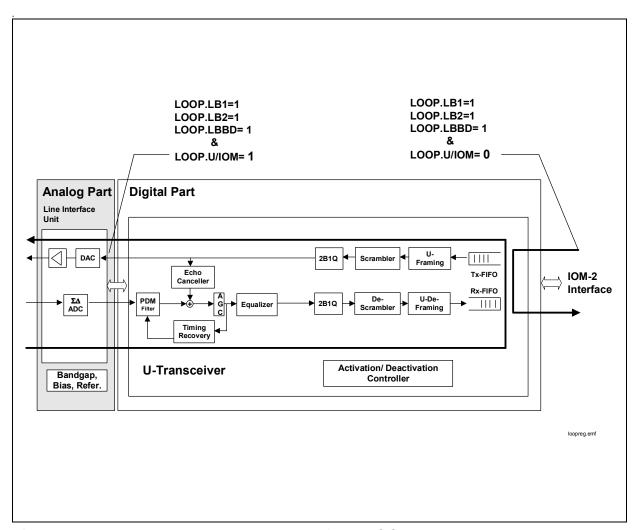

| Figure 61          | Loopbacks Featured by Register LOOP                   |     |

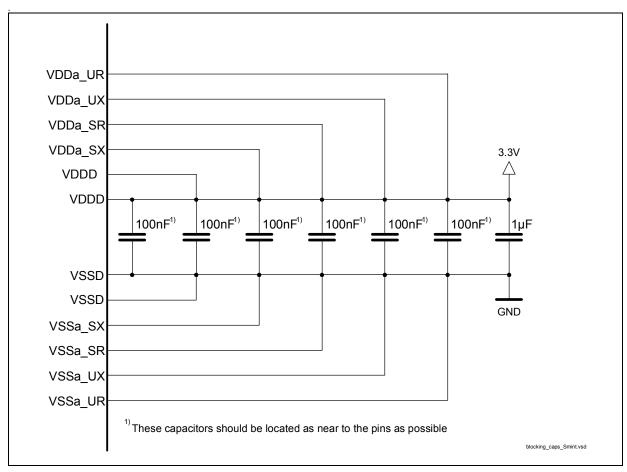

| Figure 62          | Power Supply Blocking                                 |     |

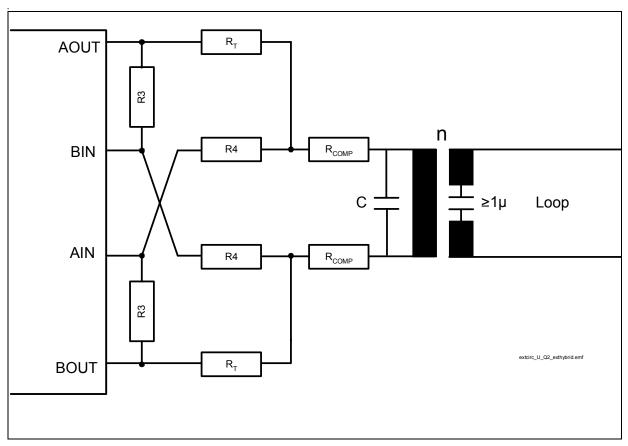

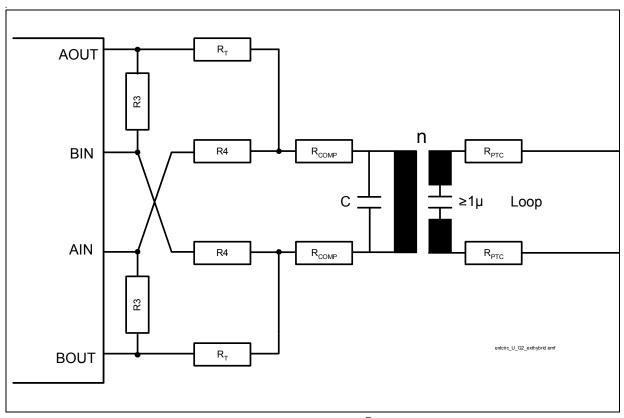

| Figure 63          | External Circuitry U-Transceiver with External Hybrid | 128 |

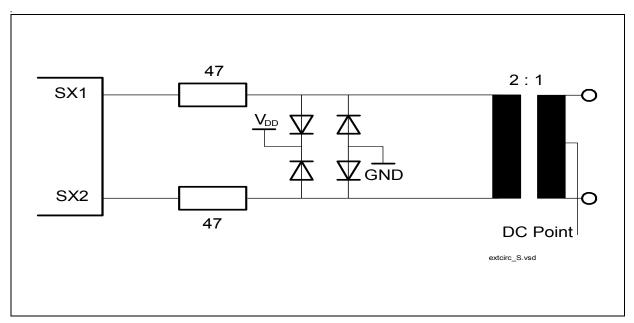

| Figure 64          | External Circuitry S-Interface Transmitter            | 131 |

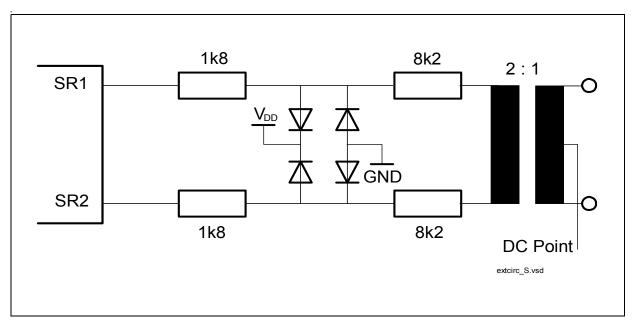

| Figure 65          | External Circuitry S-Interface Receiver               | 131 |

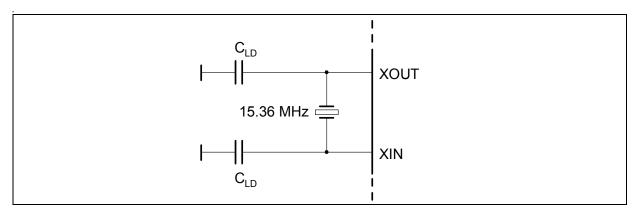

| Figure 66          | Crystal Oscillator                                    | 132 |

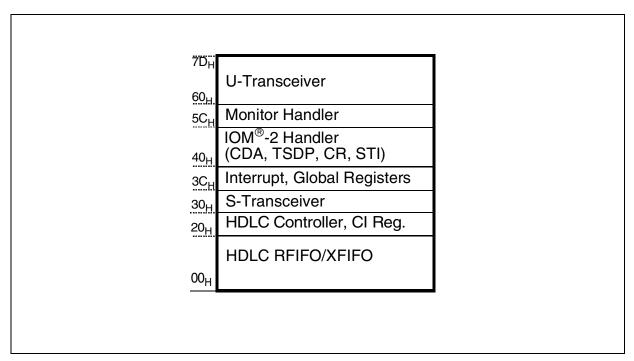

| Figure 67          | Address Space                                         | 133 |

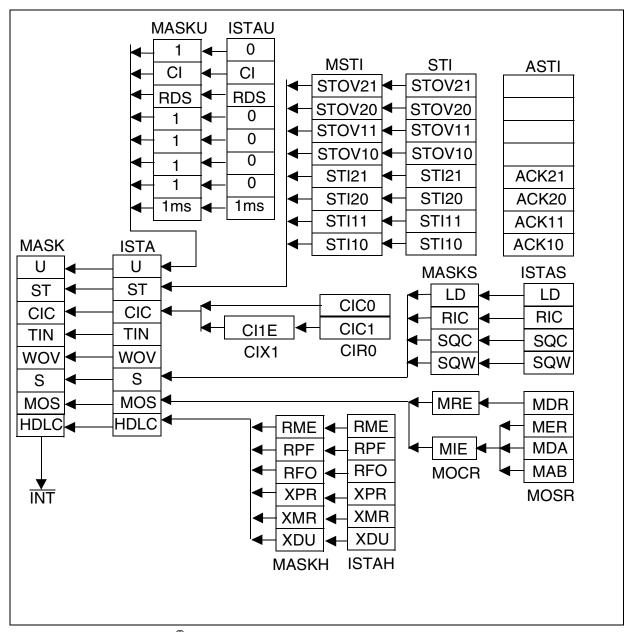

| Figure 68          | T-SMINT,IX Interrupt Status Registers                 | 134 |

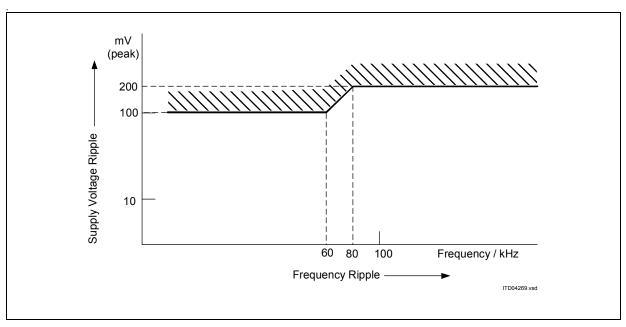

| Figure 69          | Maximum Sinusoidal Ripple on Supply Voltage           | 201 |

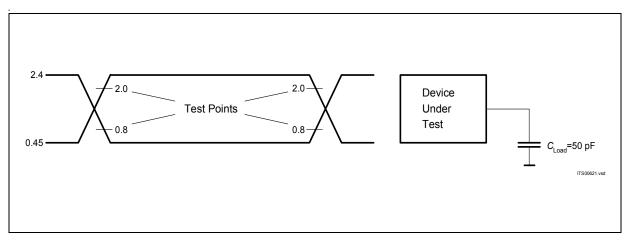

| Figure 70          | Input/Output Waveform for AC Tests                    | 202 |

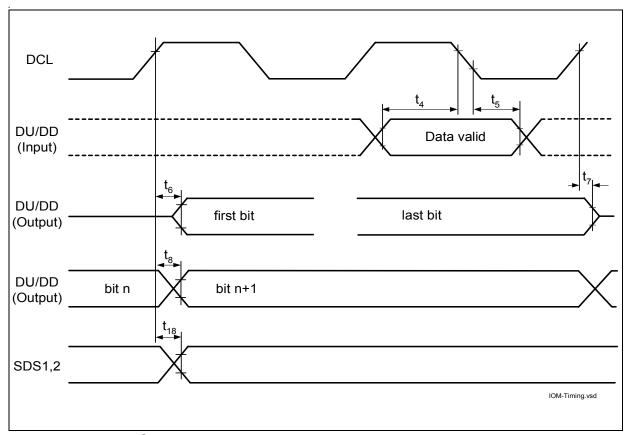

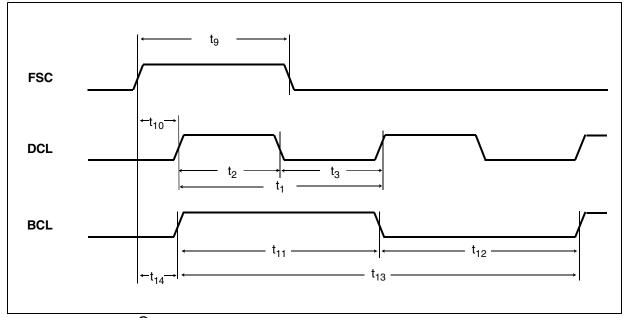

| Figure 71          | IOM®-2 Interface - Bit Synchronization Timing         | 203 |

| Figure 72          | IOM®-2 Interface - Frame Synchronization Timing       | 203 |

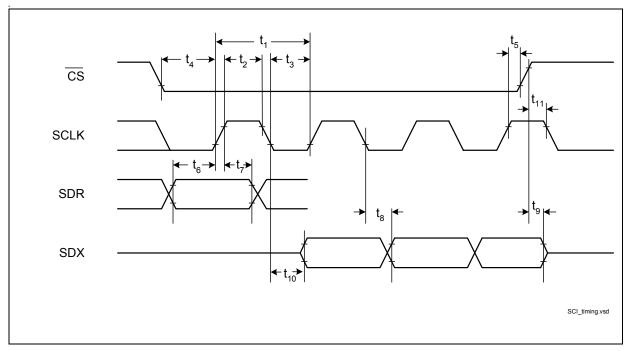

| Figure 73          | Serial Control Interface                              | 205 |

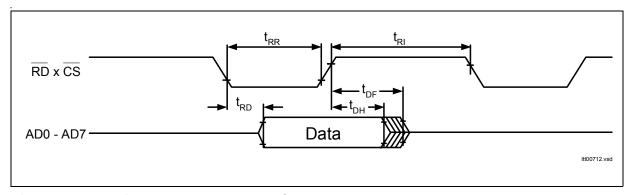

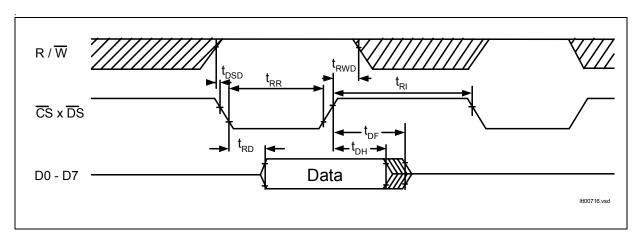

| Figure 74          | Microprocessor Read Cycle                             | 206 |

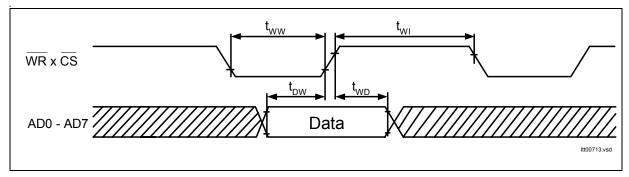

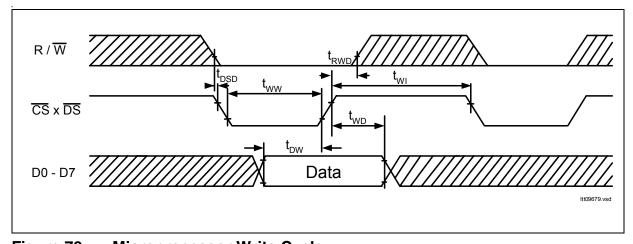

| Figure 75          | Microprocessor Write Cycle                            | 206 |

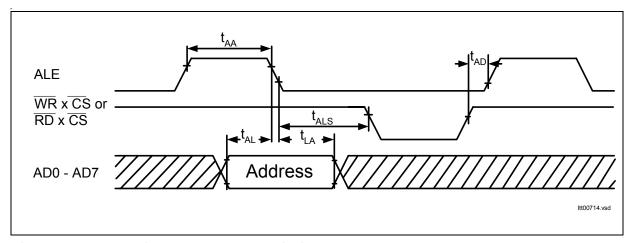

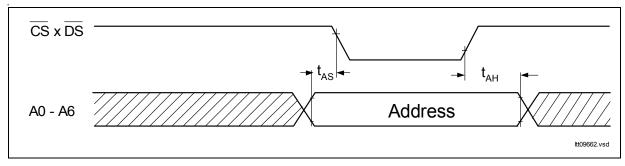

| Figure 76          | Multiplexed Address Timing                            | 206 |

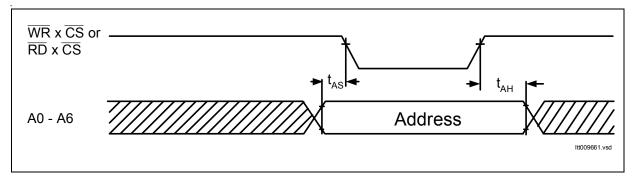

| Figure 77          | Non-Multiplexed Address Timing                        | 207 |

| Figure 78          | Microprocessor Read Timing                            | 207 |

| Figure 79          | Microprocessor Write Cycle                            | 207 |

| Figure 80          | Non-Multiplexed Address Timing                        | 208 |

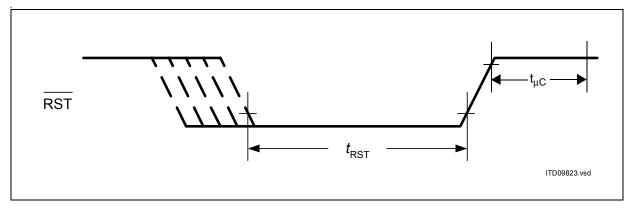

| Figure 81          | Reset Input Signal                                    | 209 |

| Figure 82          | Undervoltage Control Timing                           | 210 |

#### PEF 81902

| List of Figure | es                                                    | Page  |

|----------------|-------------------------------------------------------|-------|

| Figure 83      | NTC-Q Compatible State Machine Q-SMINT,IX: 2B1Q       | . 217 |

| Figure 84      | Simplified State Machine Q-SMINT,IX: 2B1Q             | . 218 |

| Figure 85      | IEC-T/NTC-T Compatible State Machine T-SMINT,IX: 4B3T | . 219 |

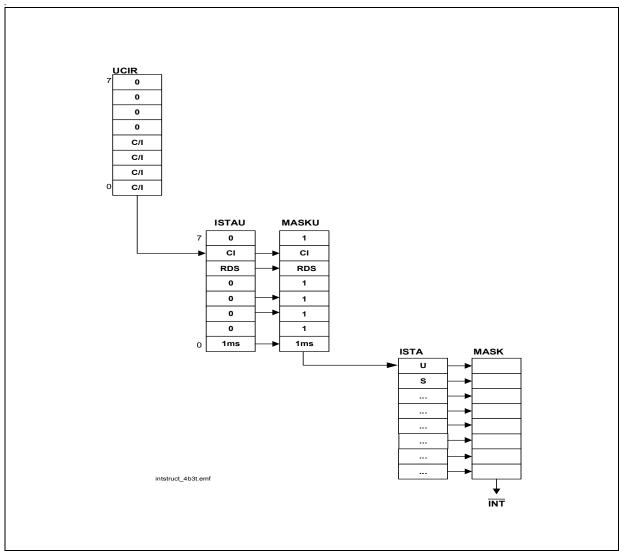

| Figure 86      | Interrupt Structure U-Transceiver Q-SMINT,IX: 2B1Q    | . 221 |

| Figure 87      | Interrupt Structure U-Transceiver T-SMINT,IX: 4B3T    | . 222 |

| Figure 88      | External Circuitry Q- and T-SMINT,IX                  | . 226 |

| List of Table | s                                                                   | Page  |

|---------------|---------------------------------------------------------------------|-------|

| Table 1       | NT Products of the 2nd Generation                                   | 1     |

| Table 2       | Pin Definitions and Functions                                       |       |

| Table 3       | ACT States                                                          | 12    |

| Table 4       | Interface Selection for the T-SMINT,IX                              | 16    |

| Table 5       | Header Byte Code                                                    | 19    |

| Table 6       | Bus Operation Modes                                                 | 21    |

| Table 7       | MCLK Frequencies                                                    | 23    |

| Table 8       | Reset Source Selection                                              | 25    |

| Table 9       | Examples for Synchronous Transfer Interrupts                        | 37    |

| Table 10      | Transmit Direction                                                  | 42    |

| Table 11      | Receive Direction                                                   | 42    |

| Table 12      | T-SMINT,IX Configuration Settings in Intelligent NT Applications    | 54    |

| Table 13      | Frame Structure A for Downstream Transmission LT to NT              | 59    |

| Table 14      | Frame Structure B for Upstream Transmission NT to LT                | . 61  |

| Table 15      | MMS 43 Coding Table                                                 | 62    |

| Table 16      | 4B3T Decoding Table                                                 | 63    |

| Table 17      | Active States                                                       | . 64  |

| Table 18      | C/I Codes                                                           | 65    |

| Table 19      | Differences to the former NT-SM of the IEC-T/NTC-T                  | . 71  |

| Table 20      | Timers                                                              | 72    |

| Table 21      | M Symbol Output                                                     | 74    |

| Table 22      | Signal Output on Uk0 in State Test                                  | 74    |

| Table 23      | C/I-Code Output                                                     |       |

| Table 24      | S/Q-Bit Position Identification and Multi-Frame Structure           | 80    |

| Table 25      | Receive Byte Count with RBC110 in the RBCH and RBCL registe         | rs 98 |

| Table 26      | Receive Information at RME Interrupt                                | . 104 |

| Table 27      | XPR Interrupt (availability of the XFIFO) after XTF, XME Commands   | s 106 |

| Table 28      | Timer                                                               | . 111 |

| Table 29      | 4B3T Signal Elements                                                | . 115 |

| Table 30      | Generation of the 4B3T Signal Elements                              |       |

| Table 31      | S/T-Interface Signals                                               |       |

| Table 32      | U-Transformer Parameters                                            |       |

| Table 33      | S-Transformer Parameters                                            |       |

| Table 34      | Crystal Parameters                                                  |       |

| Table 35      | Reset of U-Transceiver Functions During Deactivation or with C/I- C | code  |

| R             | ESET 144                                                            |       |

| Table 36      | Mode Register with Immediate Evaluation and Execution               |       |

| Table 37      | Maximum Input Currents                                              |       |

| Table 38      | S-Transceiver Characteristics                                       |       |

| Table 39      | U-Transceiver Characteristics                                       |       |

| Table 40      | Pin Capacitances                                                    |       |

| Table 41      | Reset Input Signal Characteristics                                  | . 209 |

#### PEF 81902

| List of Tables |                                   |     |

|----------------|-----------------------------------|-----|

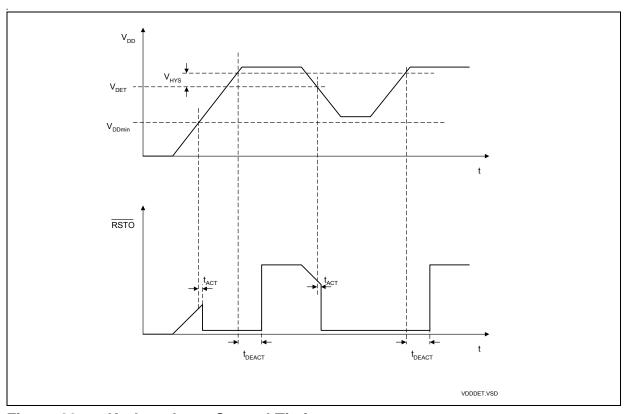

| Table 42       | Parameters of the UVD/POR Circuit | 210 |

| Table 43       | Design Number                     | 214 |

| Table 45       | ACT States                        | 215 |

#### 1 Overview

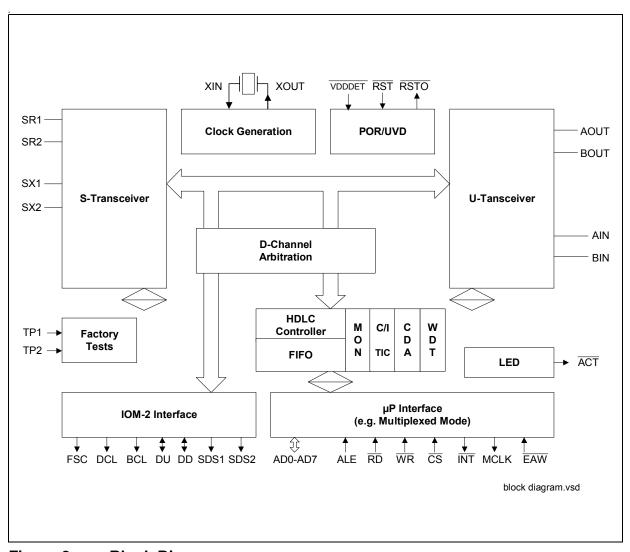

The **PEB 81902** (T-SMINT®IX) offers many features in addition to the PEB 8090 [9] which ease the realization of an intelligent NT.

The T-SMINT®IX features U-transceiver, S-transceiver, HDLC controller and an IOM®-2 interface on a single chip. A microcontroller interface provides access to both transceivers, the HDLC controller as well as to the IOM®-2 interface.

Main target applications of the T-SMINT®IX are intelligent NT applications which require one single HDLC controller.

**Table 1** on **Page 1** summarizes the 2nd generation NT products.

Table 1 NT Products of the 2nd Generation

|                                                                                                                              | PEF 80902  | PEF 81902                   | PEF 82902                   |

|------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------|-----------------------------|

|                                                                                                                              | T-SMINT®O  | T-SMINT <sup>®</sup> IX     | T-SMINT <sup>®</sup> I      |

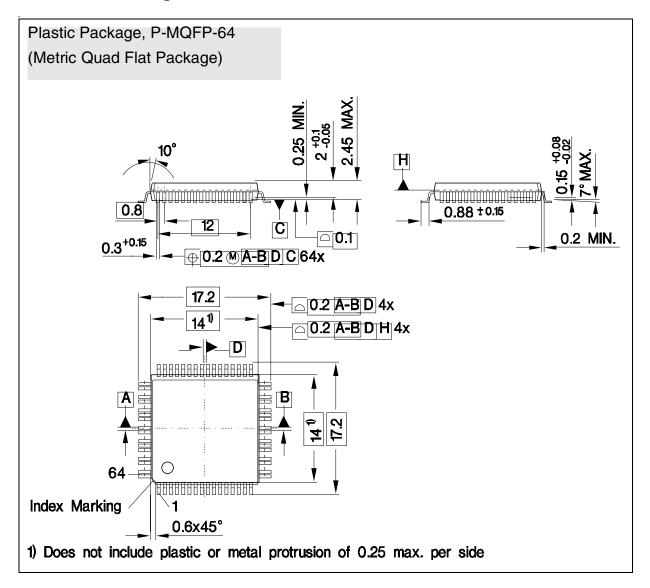

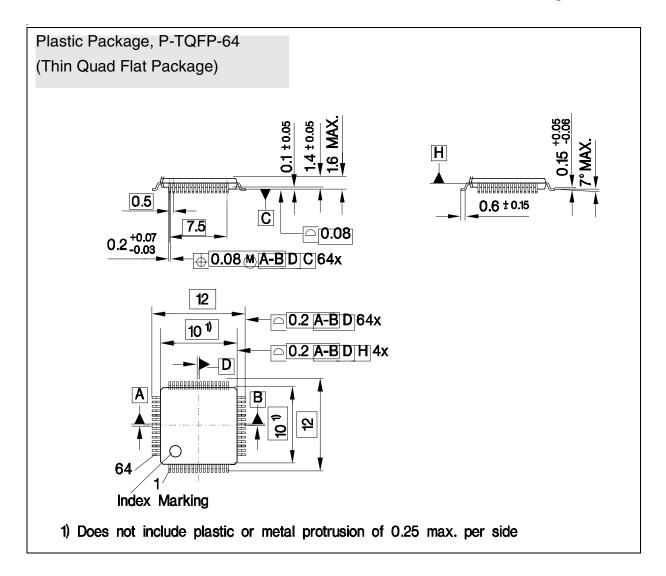

| Package                                                                                                                      | P-MQFP-    | P-MQFP-64                   | P-MQFP-64                   |

|                                                                                                                              | 44         | P-TQFP-64                   | P-TQFP-64                   |

| Register                                                                                                                     | no         | U+S+HDLC+ IOM®-2            | U+S+IOM <sup>®</sup> -2     |

| access                                                                                                                       |            |                             |                             |

| Access via                                                                                                                   | n.a        | parallel (or SCI or IOM®-2) | parallel (or SCI or IOM®-2) |

| MCLK,<br>watchdog timer,<br>SDS, BCL, D-<br>channel<br>arbitration,<br>IOM®-2 access<br>and<br>manipulation<br>etc. provided | no         | yes                         | yes                         |

| HDLC controller                                                                                                              | no         | yes                         | no                          |

| NT1 mode<br>available                                                                                                        | yes (only) | no                          | no                          |

| 1.1  | References                                                                                                                                                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]  | TS 102 080, Transmission and Multiplexing; ISDN basic rate access; Digital transmission system on metallic local lines, ETSI, November 1998                                                                              |

| [2]  | FTZ 1 TR 220 Technische Richtlinie, Spezifikation der ISDN Schnittstelle Uk0 Schicht 1, Deutsche Telecom AG, August 1991                                                                                                 |

| [3]  | TS 0284/96 Technische Spezifikation Intelligenter Netzabschluß (iNT) mit den Funktionen eines Terminaladapters TA 2a/b (ohne Internverkehr), Deutsche Telekom AG, März 2001                                              |

| [4]  | pr ETS 300 012 Draft, ISDN; Basic User Network Interface (UNI), ETSI, November 1996                                                                                                                                      |

| [5]  | T1.605-1991, ISDN-Basic Access Interface for S and T Reference Points (Layer 1 Specification), ANSI, 1991                                                                                                                |

| [6]  | I.430, ISDN User-Network Interfaces: Layer 1 Recommendations, ITU, November 1988                                                                                                                                         |

| [7]  | IEC-T, ISDN Echocancellation Circuit, PEB 20901 (IEC - TD) / PEB 20902 (IEC - TA), preliminary Target Specification 11.88, Siemens AG, 1988                                                                              |

| [8]  | SBCX, S/T Bus Interface Circuit Extended, PEB 2081 V3.4, User's Manual 11.96, Siemens AG, 1996                                                                                                                           |

| [9]  | NTC-T, Network Termination Controller (4B3T), PEB 8090 V1.1, Data Sheet 06.98, Siemens AG, 1998                                                                                                                          |

| [10] | INTC-Q, Intelligent Network Termination Controller (2B1Q), PEB 8191 V1.1, Data Sheet 10.97, Siemens AG, 1997                                                                                                             |

| [11] | Q-SMINTO, 2B1 <b>Q S</b> econd Gen. <b>M</b> odular <b>I</b> SDN <b>NT (O</b> rdinary), PEF 80912 Q-SMINTIX, 2B1 <b>Q S</b> econd Gen. <b>M</b> odular <b>I</b> SDN <b>NT (I</b> ntelligent e <b>X</b> ended), PEF 81912 |

|      | Q-SMINTI, 2B1 <b>Q S</b> econd Gen. <b>M</b> odular <b>I</b> SDN <b>NT (I</b> ntelligent), PEF 82912 V1.3, Data Sheets 03.01, Infineon AG, 2001                                                                          |

| [12] | IOM®-2 Interface Reference Guide, Siemens AG, 03.91                                                                                                                                                                      |

| [13] | SCOUT-S(X), Siemens Codec with S/T-Transceiver, PSB 2138x V1.1, Preliminary Data Sheet 08.98, Infineon Technologies AG, 1999                                                                                             |

| [14] | PITA, PCI Interface for Telephony/Data Applications V0.3, SICAN GmbH, September1997                                                                                                                                      |

| [15] | Dual Channel SLICOFI-2, HV-SLIC; DUSLIC; PEB3265, 4265, 4266; Data Sheet DS2, Infineon Technologies, July 2000.                                                                                                          |

### 4B3T Second Gen. Modular ISDN NT (Intelligent eXtended) T-SMINT®IX

PEF 81902

#### Version 1.1

#### 1.2 Features

#### Features known from the PEB 8090

- U-transceiver and S-transceiver on one chip

- U-interface (4B3T) conform to ETSI [1] and FTZ [2] :

- Meets all transmission requirements on all ETSI and FTZ loops with margin

- S/T-interface conform to ETSI [4], ANSI [5] and ITU

[6]

- Supports point-to-point and bus configurations

- Meets and exceeds all transmission requirements

- Access to IOM<sup>®</sup>-2 C/I and Monitor channels

- Power-on reset and Undervoltage Detection with no external components

- ESD robustness 2kV

## P-TQFP-64

#### **New Features**

- Conforms to 'Technische Spezifikation Intelligenter L Netzabschluß (iNT) mit den Funktionen eines Terminaladapters TA 2a/b' of Deutsche Telekom AG [3]

- Perfectly suited for low cost intelligent NTs that require one single HDLC controller

- Pin compatible with Q-SMINT®IX (2nd Generation)

- HDLC controller on chip, including

- HDLC access to B-channels, D-channel and any combination of them.

- Improved FIFO structure

- HDLC extended transparent mode

- Automatic D-channel arbitration between S-bus and local HDLC controller

- Parallel or serial µP-interface

- Siemens/Intel non-multiplexed (direct or indirect addressing)

| Туре      | Package   |

|-----------|-----------|

| PEF 81902 | P-MQFP-64 |

| PEF 81902 | P-TQFP-64 |

- Siemens/Intel multiplexed

- Motorola

- programmable MCLK (can be disabled)

- Enhanced IOM®-2 interface

- Timeslot access and manipulation

- BCL output; programmable and flexible strobes SDS1/2, e.g. active during several timeslots.

- Optional: All registers can be read and written to via new Monitor channel concept

- External Awake (EAW)

- Optional use of transformers with non-negligible resistance corresponding to up to  $20\Omega$  on the line side

- Optional: Implementation of S-transceiver statemachine in software

- Power-down mode and reset states (e.g. S-transceiver) for individual circuits

- Pin Vref and the according external capacitor removed

- Inputs accept 3.3V and 5V

- I/O (open drain) accepts pull-up to 3.3V<sup>1)</sup>

- LED signal is programmable to display the states specified in [3]; but can also automatically indicate the activation status (mode select via 1 bit).

- Lowest power consumption due to

- Low power CMOS technology (0.35μ)

- Newly optimized low power libraries

- High output swing on U- and S-line interface leads to minimized power consumption

- Single 3.3 Volt power supply

#### 1.3 Not Supported are ...

- No integrated hybrid is provided by the T-SMINT<sup>®</sup>IX. Therefore, an external hybrid is always required, which consists of only two additional resistors as compared to an integrated hybrid, but allows for more flexibility in board design.

- Auxiliary IOM<sup>®</sup>–2 interface

- SRA (capacitive receiver coupling is not suited for S-feeding)

- NT-Star with star point on the IOM®-2 bus (already not supported in NTC-T).

- HDLC Automode

- No access to S2-5 channels. Access only to S1 and Q channel as in Scout-S. No selection between transparent and non-auto mode provided.

<sup>1)</sup> Pull-ups to 5V must be avoided. A so-called 'hot-electron-effect' would lead to long term degradation.

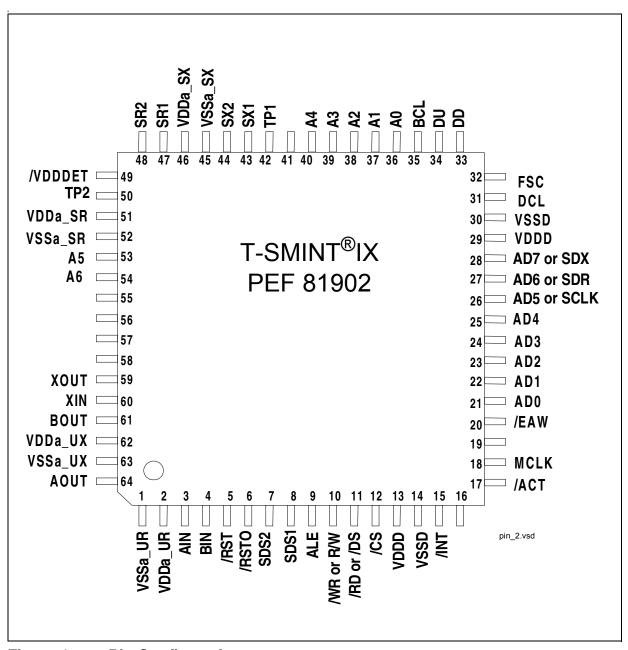

#### 1.4 Pin Configuration

Figure 1 Pin Configuration

#### 1.5 Block Diagram

Figure 2 Block Diagram

#### 1.6 Pin Definitions and Functions

Table 2

Pin Definitions and Functions

|    | Pin | Symbol  | Туре      | Function                                                                      |  |  |  |  |

|----|-----|---------|-----------|-------------------------------------------------------------------------------|--|--|--|--|

|    | 2   | VDDa_UR | _         | Supply voltage for U-Receiver $(3.3 \text{ V} \pm 5 \%)$                      |  |  |  |  |

|    | 1   | VSSa_UR | _         | Analog ground (0 V) U-Receiver                                                |  |  |  |  |

|    | 62  | VDDa_UX | _         | Supply voltage for U-Transmitter (3.3 V $\pm$ 5 %)                            |  |  |  |  |

|    | 63  | VSSa_UX | _         | Analog ground (0 V) U-Transmitter                                             |  |  |  |  |

|    | 51  | VDDa_SR | _         | Supply voltage for S-Receiver (3.3 V ± 5 %)                                   |  |  |  |  |

| 52 |     | VSSa_SR | _         | Analog ground (0 V) S-Receiver                                                |  |  |  |  |

|    | 46  | VDDa_SX | _         | Supply voltage for S-Transmitter $(3.3 \text{ V} \pm 5 \%)$                   |  |  |  |  |

|    | 45  | VSSa_SX | _         | Analog ground (0 V) S-Transmitter                                             |  |  |  |  |

|    | 29  | VDDD    | _         | Supply voltage digital circuits (3.3 V ± 5 %)                                 |  |  |  |  |

|    | 30  | VSSD    | _         | Ground (0 V) digital circuits                                                 |  |  |  |  |

|    | 13  | VDDD    | _         | Supply voltage digital circuits (3.3 V $\pm$ 5 %)                             |  |  |  |  |

|    | 14  | VSSD    | _         | Ground (0 V) digital circuits                                                 |  |  |  |  |

|    |     |         |           |                                                                               |  |  |  |  |

|    | 32  | FSC     | О         | Frame Sync: 8-kHz frame synchronization signal                                |  |  |  |  |

|    | 31  | DCL     | 0         | Data Clock: IOM®-2 interface clock signal (double clock): 1.536 MHz           |  |  |  |  |

|    | 35  | BCL     | 0         | Bit Clock:<br>The bit clock is identical to the IOM®-2 data rate<br>(768 kHz) |  |  |  |  |

|    | 33  | DD      | I/O<br>OD | Data Downstream: Data on the IOM®-2 interface                                 |  |  |  |  |

|    | 34  | DU      | I/O<br>OD | Data Upstream: Data on the IOM®-2 interface                                   |  |  |  |  |

Table 2

Pin Definitions and Functions (cont'd)

| Pi | n Symbo | Туре     | Function                                                                                                                                                                                                                                                                   |

|----|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8  | SDS1    | 0        | Serial Data Strobe1: Programmable strobe signal for time slot and/or D-channel indication on IOM®-2                                                                                                                                                                        |

| 7  | SDS2    | 0        | Serial Data Strobe2: Programmable strobe signal for time slot and/or D-channel indication on IOM®-2                                                                                                                                                                        |

|    |         |          |                                                                                                                                                                                                                                                                            |

| 12 | CS      | I        | Chip Select: A low level indicates a microcontroller access to the T-SMINT®IX                                                                                                                                                                                              |

| 26 |         | I<br>I/O | Serial Clock: Clock signal of the SCI interface if a serial interface is selected Multiplexed Bus Mode: Address/data bus Address/data line AD5 if the parallel interface is selected Non-Multiplexed Bus Mode: Data bus Data line D5 if the parallel interface is selected |

| 27 | SDR     | I        | Serial Data Receive: Receive data line of the SCI interface if a serial interface is selected                                                                                                                                                                              |

| 27 | AD6     | I/O      | Multiplexed Bus Mode: Address/data bus Address/data line AD6 if the parallel interface is selected Non-Multiplexed Bus Mode: Data bus Data line D6 if the parallel interface is selected                                                                                   |

Table 2Pin Definitions and Functions (cont'd)

| Pin                                    | Symbol                                 | Туре                     | Function                                                                                                                                                                                                                                                                                 |

|----------------------------------------|----------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                                     | SDX<br>AD7                             | OD/O                     | Serial Data Transmit: Transmit data line of the SCI interface if a serial interface is selected Multiplexed Bus Mode: Address/data bus Address/data line AD7 if the parallel interface is selected Non-Multiplexed Bus Mode: Data bus Data line D7 if the parallel interface is selected |

| 21<br>22<br>23<br>24<br>25             | AD0<br>AD1<br>AD2<br>AD3<br>AD4        | I/O<br>I/O<br>I/O<br>I/O | Multiplexed Bus Mode: Address/data bus Transfers addresses from the microcontroller to the T-SMINT®IX and data between the microcontroller and the T-SMINT®IX. Non-Multiplexed Bus Mode: Data bus. Transfers data between the microcontroller and the T-SMINT®IX (data lines D0-D4).     |

| 36<br>37<br>38<br>39<br>40<br>53<br>54 | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6 | <br>                     | Non-Multiplexed Bus Mode: Address bus transfers addresses from the microcontroller to the T-SMINT®IX. For indirect address mode only A0 is valid. Multiplexed Bus Mode Not used in multiplexed bus mode. In this case A0-A6 should directly be connected to VDD.                         |

| 11                                     | RD<br>DS                               | 1                        | Read Indicates a read access to the registers (Intel bus mode).  Data Strobe The rising edge marks the end of a valid read or write operation (Motorola bus mode).                                                                                                                       |

Table 2Pin Definitions and Functions (cont'd)

| Pin    | Symbol    | Туре       | Function                                                                                                                                                                                                                    |

|--------|-----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10     | WR<br>R/W | I          | Write Indicates a write access to the registers (Intel bus mode). Read/Write A HIGH identifies a valid host access as a read operation and a LOW identifies a valid host access as a write operation (Motorola bus mode).   |

| 9      | ALE       | I          | Address Latch Enable An address on the external address/data bus (multiplexed bus type only) is latched with the falling edge of ALE. ALE also selects the microcontroller interface type (multiplexed or non multiplexed). |

| 5      | RST       | I          | Reset: Low active reset input. Schmitt-Trigger input with hysteresis of typical 360mV. Tie to '1' if not used.                                                                                                              |

| 6      | RSTO      | OD         | Reset Output: Low active reset output.                                                                                                                                                                                      |

| 15     | ĪNT       | OD         | Interrupt Request:  INT becomes active if the T-SMINT®IX requests an interrupt.                                                                                                                                             |

| 18     | MCLK      | 0          | Microcontroller Clock: Clock output for the microcontroller                                                                                                                                                                 |

| 20     | EAW       | I          | External Awake: A low level on EAW during power down activates the clock generation of the T-SMINT®IX, i.e. the IOM®-2 interface provides FSC, DCL and BCL for read and write access. 1)                                    |

|        | ,         | 1          |                                                                                                                                                                                                                             |

| <br>43 | SX1       | 0          | S-Bus Transmitter Output (positive)                                                                                                                                                                                         |

| <br>44 | SX2       | 0          | S-Bus Transmitter Output (negative)                                                                                                                                                                                         |

| <br>47 | SR1       | <b>   </b> | S-Bus Receiver Input                                                                                                                                                                                                        |

| Table 2 | Pin Definitions and Functions | (cont'd) | ) |

|---------|-------------------------------|----------|---|

|---------|-------------------------------|----------|---|

| Pin               | Symbol | Туре | Function                                                                                                                                                                                                           |

|-------------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48                | SR2    | I    | S-Bus Receiver Input                                                                                                                                                                                               |

| 60                | XIN    | 1    | Crystal 1:<br>Connected to a 15.36 MHz crystal                                                                                                                                                                     |

| 59                | XOUT   | 0    | Crystal 2:<br>Connected to a 15.36 MHz crystal                                                                                                                                                                     |

|                   | _      |      |                                                                                                                                                                                                                    |

| 64                | AOUT   | 0    | Differential U-interface Output                                                                                                                                                                                    |

| <br>61            | BOUT   | 0    | Differential U-interface Output                                                                                                                                                                                    |

| <br>3             | AIN    | 1    | Differential U-interface Input                                                                                                                                                                                     |

| 4                 | BIN    | 1    | Differential U-interface Input                                                                                                                                                                                     |

| •                 |        |      |                                                                                                                                                                                                                    |

| 49                | VDDDET | 1    | VDD Detection: This pin selects if the V <sub>DD</sub> detection is active ('0') and reset pulses are generated on pin RSTO or whether it is deactivated ('1') and an external reset has to be applied on pin RST. |

| 17                | ACT    | 0    | Activation LED. Indicates the activation status of U- and S-transceiver. Can directly drive a LED (4mA).                                                                                                           |

| 42                | TP1    | I    | Test Pin 1. Used for factory device test. Tie to 'V <sub>SS</sub> '                                                                                                                                                |

| 50                | TP2    | I    | Test Pin 2. Used for factory device test. Tie to 'V <sub>SS</sub> '                                                                                                                                                |

| 16, 19,<br>41, 55 |        |      | Tie to '1'                                                                                                                                                                                                         |

| 56, 57,<br>58     | res    |      | Reserved These pins are reserved for future use. Do not connect.                                                                                                                                                   |

<sup>&</sup>lt;sup>1)</sup> This function of pin  $\overline{\text{EAW}}$  is different to that defined in Ref. [13]

I: Input

O: Output (Push-Pull)

OD: Output (Open Drain)

#### 1.6.1 Specific Pins and Test Modes

#### **LED Pin ACT**

A LED can be connected to pin  $\overline{ACT}$  to display four different states (off, slow flashing, fast flashing, on). It displays the activation status of the U- and S-transceiver according to Table 3. or it is programmable via two bits (LED1 and LED2 in register MODE2).

Table 3 ACT States

| Pin ACT      | LED           | U_Deactivated | U_Activated | S_Activated |

|--------------|---------------|---------------|-------------|-------------|

| $V_{DD}$     | OFF           | 1             | x           | x           |

| 2Hz (1 : 1)* | fast flashing | 0             | 0           | x           |

| 1Hz (3 : 1)* | slow flashing | 0             | 1           | 0           |

| GND          | ON            | 0             | 1           | 1           |

Note: \* denotes the duty cycle 'high': 'low'.

with:

**U\_Deactivated**: 'Deactivated State' as defined in **Chapter 2.4.7.6**.

**U\_Activated**: 'SBC Synchronizing', 'Wait for Info U4H', and 'Transparent' as defined in **Chapter 2.4.7.6**.

**S-Activated**: 'Activated State' as defined in **Chapter 2.5.5.2**.

Note: Optionally, pin  $\overline{ACT}$  can drive a second LED with inverse polarity (connect this additional LED to 3.3V only).

#### **Test Modes**

The test patterns on the S-interface ('2 kHz Single Pulses', '96 kHz Continuous Pulses') and on the U-interface ('Data Through', 'Send Single Pulses',) are invoked via C/I codes (TM1, TM2, DT, SSP). Setting SRES.RES\_U to '1' forces the U-transceiver into test mode 'Quiet Mode' (QM), i.e. the U-transceiver is hardware reset.

#### 1.7 System Integration

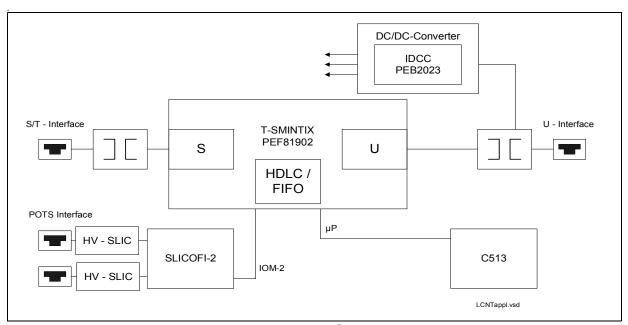

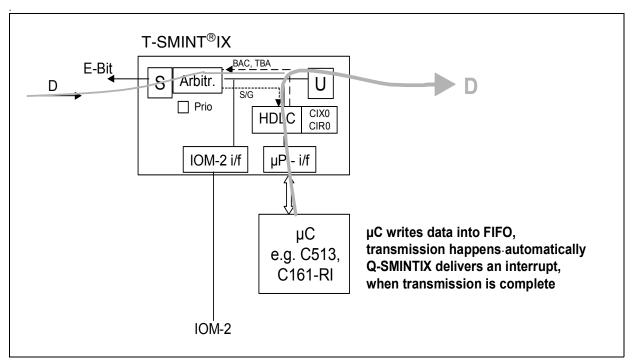

Figure 3 Application Example T-SMINT®IX: Low Cost Intelligent NT

The U-transceiver, the S-transceiver, the IOM®-2 channels and the HDLC-controller can be controlled and monitored via:

- a) the parallel or serial microprocessor interface

- Access of on-chip registers via  $\mu P$  interface Address/Data format

- Activation/Deactivation control of U- and S-transceiver via  $\mu P$  interface and C/I handler

- T-SMINT®IX is Monitor channel master

- TIC bus is transparent on  $IOM^{\otimes}$ -2 interface and is used for D-channel arbitration between S-transceiver and on-chip HDLC controller.

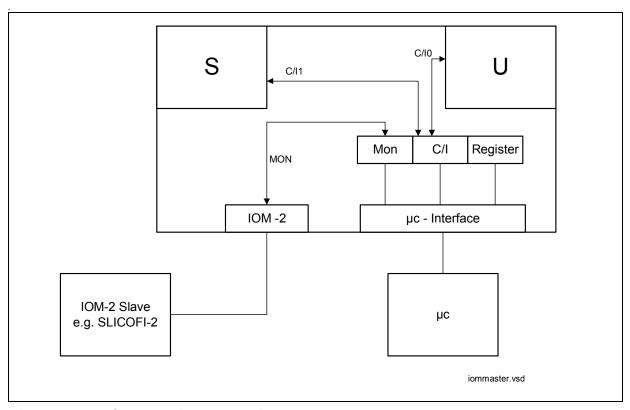

Figure 4 Control via µP Interface

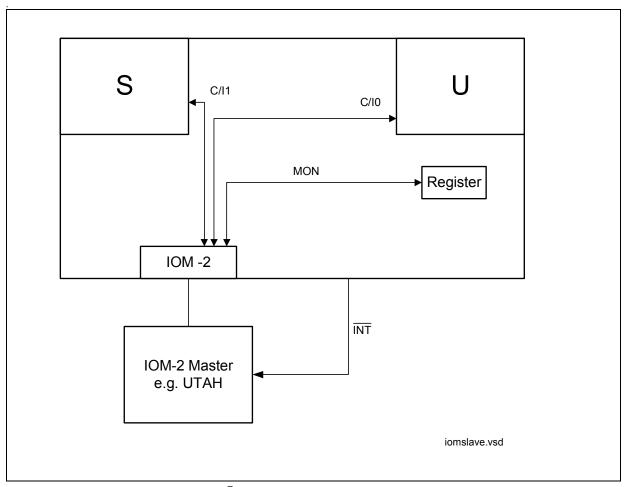

Alternatively, the T-SMINT®IX can be controlled via

- b) the IOM®-2 Interface

- Access of on-chip registers via the Monitor channel with Header/Address/Data format (Device is Monitor slave)

- Activation/Deactivation control of U- and S-transceiver via the C/I channels CI0 and CI1

- TIC bus is transparent on  $IOM^{\otimes}-2$  interface and is used for D-channel arbitration between S-transceiver and on-chip HDLC controller.

Figure 5 Control via IOM®-2 Interface

#### **2** Functional Description

#### 2.1 Microcontroller Interfaces

The T-SMINT®IX supports either a serial or a parallel microcontroller interface. For applications where no controller is connected to the T-SMINT®IX microcontroller interface, register programming is done via the IOM®-2 MONITOR channel from a master device. In such applications the T-SMINT®IX operates in the IOM®-2 slave mode (refer to the corresponding chapter of the IOM®-2 MONITOR handler).

The interface selections are all done by pinstrapping. The possible interface selections are listed in **Table 4**. The selection pins are evaluated when the reset input  $\overline{\mathsf{RST}}$  is released. For the pin levels stated in the tables the following is defined:

'High':dynamic pin value which must be 'High' when the pin level is evaluated  $V_{DD},\,V_{SS}$ :static 'High' or 'Low' level (tied to  $V_{DD},\,V_{SS}$ )

Table 4 Interface Selection for the T-SMINT®IX

| PINS            |                 | Serial/Parallel | PI              | INS             | Interface                                           |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------------------------------------------|

| WR<br>(R/W)     | RD<br>(DS)      | Interface       | cs              | ALE             | Type/Mode                                           |

|                 |                 |                 |                 | V <sub>DD</sub> | Motorola                                            |

| 'High'          | 'High'          | Parallel        | 'High'          | V <sub>SS</sub> | Siemens/Intel Non-Mux                               |

|                 |                 |                 |                 | edge            | Siemens/Intel Mux                                   |

| V <sub>SS</sub> | V <sub>SS</sub> | Serial          | 'High'          | V <sub>SS</sub> | Serial Control Interface(SCI)                       |

|                 |                 |                 | V <sub>SS</sub> | V <sub>SS</sub> | IOM <sup>®</sup> -2 MONITOR Channel<br>(Slave Mode) |

Note: For a selected interface mode which does not require all pins (e.g. address pins) the unused pins must be tied to  $V_{DD}$ .

The microcontroller interface also consists of a microcontroller clock generation at pin  $\overline{\text{MCLK}}$ , an interrupt request at pin  $\overline{\text{INT}}$ , a reset input pin  $\overline{\text{RST}}$  and a reset output pin  $\overline{\text{RSTO}}$ .

The interrupt request pin  $\overline{\text{INT}}$  (open drain output) becomes active if the T-SMINT  $^{\text{@}}$ IX requests an interrupt.

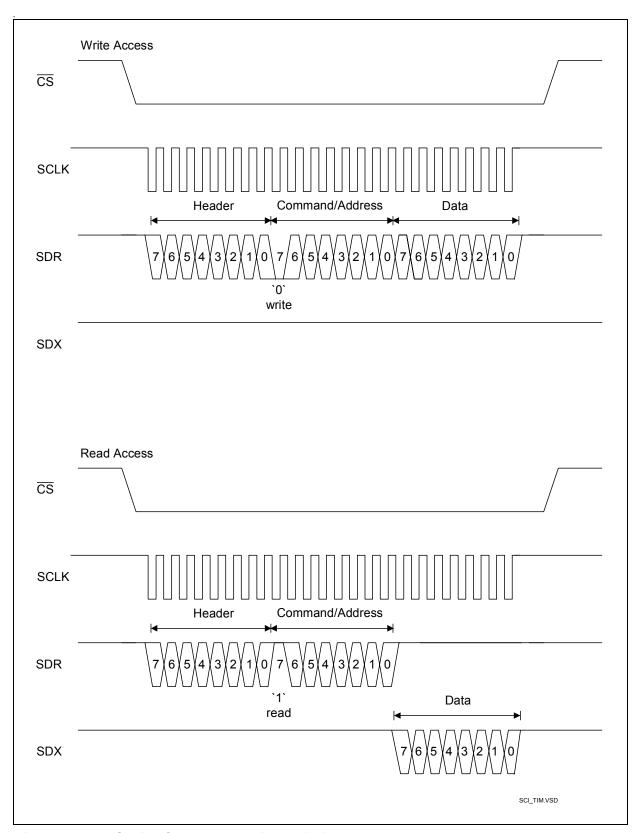

#### 2.1.1 Serial Control Interface (SCI)

The serial control interface (SCI) is compatible to the SPI interface of Motorola and to the Siemens C510 family of microcontrollers.

The SCI consists of 4 lines: SCLK, SDX, SDR and  $\overline{CS}$ . Data is transferred via the lines SDR and SDX at the rate given by SCLK. The falling edge of  $\overline{CS}$  indicates the beginning

of a serial access to the registers. The T-SMINT<sup>®</sup>IX latches incoming data at the rising edge of SCLK and shifts out at the falling edge of SCLK. Each access must be terminated by a rising edge of  $\overline{\text{CS}}$ . Data is transferred in groups of 8 bits with the MSB first.

Pad mode of SDX can be selected 'open drain' or 'push-pull' by programming MODE2.PPSDX.

Figure 6 shows the timing of a one byte read/write access via the serial control interface.

Figure 6 Serial Control Interface Timing

#### 2.1.1.1 Programming Sequences

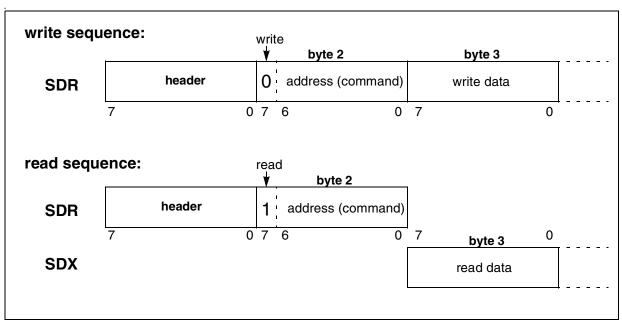

The basic structure of a read/write access to the T-SMINT®IX registers via the serial control interface is shown in **Figure 7**.

Figure 7 Serial Command Structure

A new programming sequence starts with the transfer of a header byte. The header byte specifies different programming sequences allowing a flexible and optimized access to the individual functional blocks of the T-SMINT®IX.

The possible sequences are listed in **Table 5** and are described after that.

Table 5Header Byte Code

| Header<br>Byte  | Sequence           | Sequence Type    | Access to                                      |

|-----------------|--------------------|------------------|------------------------------------------------|

| 40 <sub>H</sub> | Adr-Data-Adr-Data  | non-interleaved  | Address Range 00 <sub>H</sub> -7F <sub>H</sub> |

| 48 <sub>H</sub> |                    | interleaved      |                                                |

| 43 <sub>H</sub> | Adr-Data-Data-Data | Read-/Write-only | Address Range 00 <sub>H</sub> -7F <sub>H</sub> |

| 41 <sub>H</sub> |                    | non-interleaved  |                                                |

| 49 <sub>H</sub> |                    | interleaved      |                                                |

#### Header 40<sub>H</sub>: Non-interleaved A-D-A-D Sequences

The non-interleaved A-D-A-D sequences give direct read/write access to the address range 00<sub>H</sub>-7F<sub>H</sub> and can have any length. In this mode SDX and SDR can be connected

together allowing data transmission on one line. Example for a read/write access with header 40<sub>H</sub>:

| SDR | header | wradr | wrdata | rdadr |        | rdadr |        | wradr | wrdata |  |

|-----|--------|-------|--------|-------|--------|-------|--------|-------|--------|--|

| SDX |        |       |        |       | rddata |       | rddata |       |        |  |

#### Header 48<sub>H</sub>: Interleaved A-D-A-D Sequences

The interleaved A-D-A-D sequences give direct read/write access to the address range  $00_{H}$ -7F<sub>H</sub> and can have any length. This mode allows a time optimized access to the registers by interleaving the data on SDX and SDR.

Example for a read/write access with header 48<sub>H</sub>:

| SDR | header | wradr | wrdata | rdadr | rdadr  | wradr  | wrdata |  |  |

|-----|--------|-------|--------|-------|--------|--------|--------|--|--|

| SDX |        |       |        |       | rddata | rddata |        |  |  |

#### Header 43<sub>H</sub>: Read-/Write- only A-D-D-D Sequence

This mode (header  $43_{\rm H}$ ) can be used for a fast access to the HDLC FIFO data. Any address (rdadr, wradr) in the range between  $00_{\rm H}$ - $1F_{\rm H}$  gives access to the current FIFO location selected by an internal pointer which is automatically incremented with every data byte following the first address byte. Generally, it can be used for any register access to the address range  $00_{\rm H}$ - $7D_{\rm H}$ . The sequence can have any length and is terminated by the rising edge of  $\overline{\rm CS}$ .

Example for a write access with header 43<sub>H</sub>:

| SDR | header | wradr | wrdata<br>(wradr) |  |

|-----|--------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|

| SDX |        |       |                   |                   |                   |                   |                   |                   |                   |  |

Example for a read access with header 43<sub>H</sub>:

| SDR | header | rdadr |         |         |         |         |         |         |         |  |

|-----|--------|-------|---------|---------|---------|---------|---------|---------|---------|--|

| SDX |        |       | rddata  |  |

|     |        |       | (rdadr) |  |

#### Header 41<sub>H</sub>: Non-interleaved A-D-D-D Sequence

This sequence (header 41<sub>H</sub>) allows in front of the A-D-D-D write access a non-interleaved A-D-A-D read access. This mode is useful for reading status information before writing to the HDLC XFIFO. Generally, it can be used for any register access to

the address range  $00_{H}$ - $7D_{H}$ . The termination condition of the read access is the reception of the wradr. The sequence can have any length and is terminated by the rising edge of  $\overline{\text{CS}}$ .

Example for a read/write access with header 41<sub>H</sub>:

| SDR | header | rdadr |        | rdadr |        | wradr | wrdata<br>(wradr) | wrdata<br>(wradr) | wrdata<br>(wradr) |  |

|-----|--------|-------|--------|-------|--------|-------|-------------------|-------------------|-------------------|--|

| SDX |        |       | rddata |       | rddata |       |                   |                   |                   |  |

#### Header 49<sub>H</sub>: Interleaved A-D-D-D Sequence

This sequence (header  $49_H$ ) allows in front of the A-D-D-D write access an interleaved A-D-A-D read access. This mode is useful for reading status information before writing to the HDLC XFIFO. Generally, it can be used for any register access to the address range  $00_H$ - $7D_H$ . The termination condition of the read access is the reception of the wradr. The sequence can have any length and is terminated by the rising edge of  $\overline{\text{CS}}$ .

Example for a read/write access with header 49<sub>H</sub>:

| SDR | header | rdadr | rdadr  | wradr  | wrdata  | wrdata  | wrdata  |  |  |

|-----|--------|-------|--------|--------|---------|---------|---------|--|--|

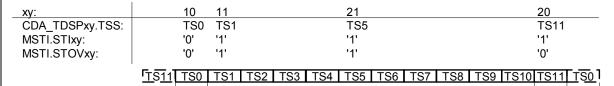

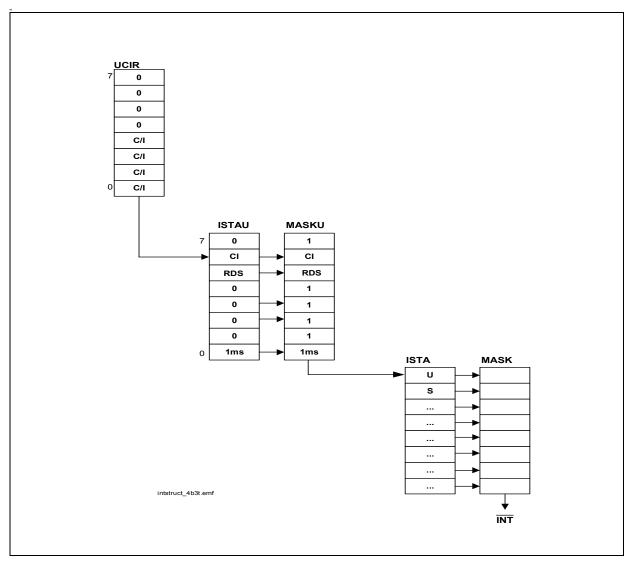

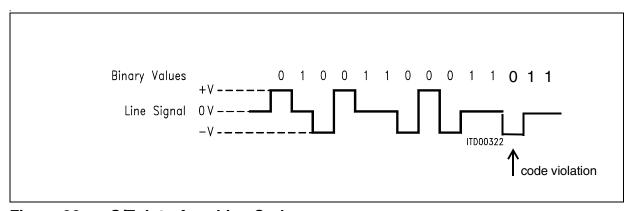

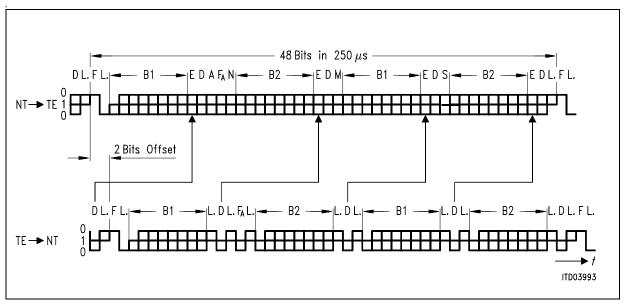

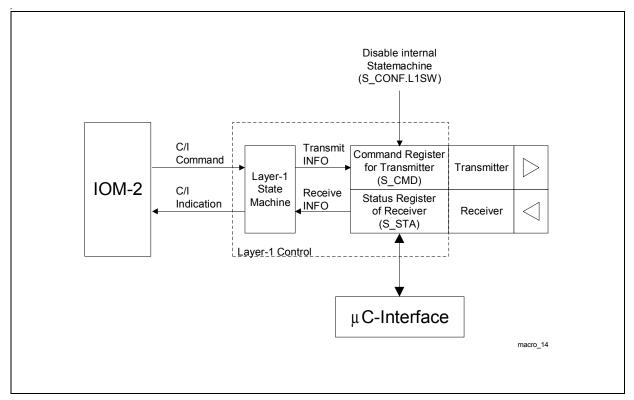

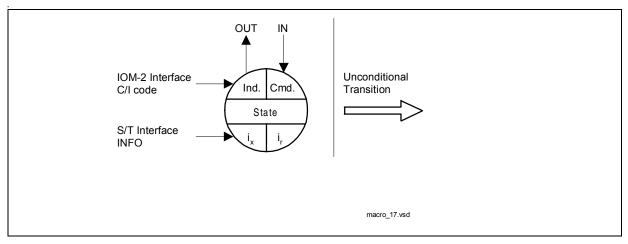

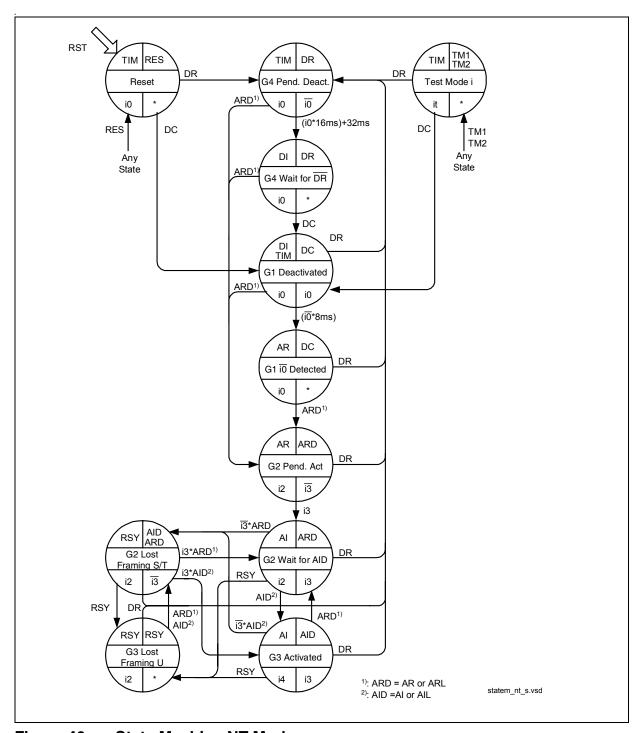

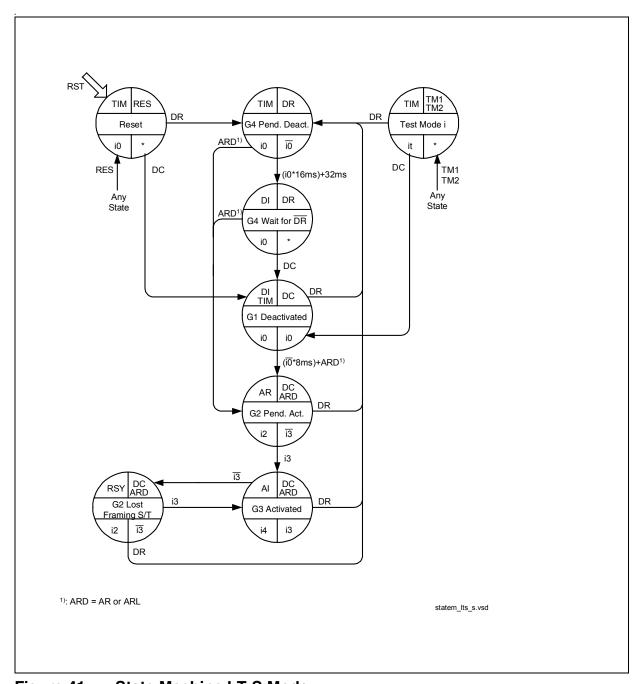

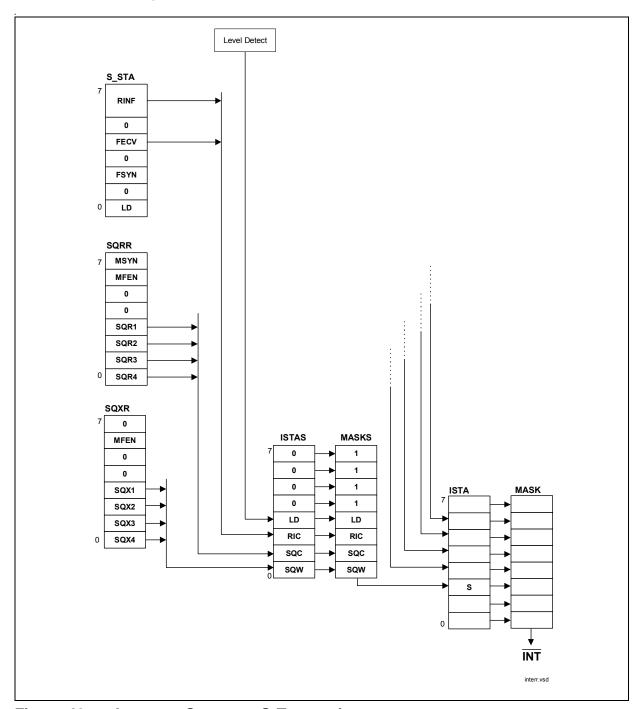

|     |        |       |        |        | (wradr) | (wradr) | (wradr) |  |  |