## **General Description**

The GOLD-SX is part of a complete chip set which covers all functions of a mobile radio for the Global System for Mobile communications, GSM. A mobile terminal which contains this chip set can meet all performance requirements set down in the Technical Specifications for GSM, PCN and PCS-1900.

GOLD-SX is used for advanced features. The function of the GOLD-SX is dependent on its firmware.

The first version of the GOLD-SX performs Half-Rate speech encoding including Voice Activity Detection (VAD) and Discontinuous Transmission (DTX), as well as Half-Rate speech decoding including Discontinuous Reception (DRX, Comfort Noise).

The second version performs Enhanced Full-Rate speech coding including all the DTX functions as in Half-Rate speech coding.

## **Features**

## Firmware:

The GOLD-SX is available in two versions with different mask programmed ROM code:

- Half-Rate Codec (GOLD-SXH):

- GSM Half-Rate Speech Codec (GSM 6.02, 6.06, 6.07, 6.20)

- Voice activity detection, VAD (GSM 6.42)

- Discontinuous transmission, DTX (GSM 6.41)

- Comfort noise generation, DRX (GSM 6.22)

| Туре                    | Package           |

|-------------------------|-------------------|

| PMB 2708_1-F (GOLD-SXH) | P-TQFP-64-1 (SMD) |

| PMB 2708_2-F (GOLD-SXE) | P-TQFP-64-1 (SMD) |

- Serial data exchange with Half-Rate Channel Codec and voiceband unit on GOLD-SP

- Serial data exchange with system simulator interfacing box (GSM 11.10)

- Enhanced Full-Rate Codec (GOLD-SXE):

- GSM Enhanced Full-Rate Codec (GSM 6.51, 6.53, 6.54, 6.60)

- Voice activity detection, VAD (GSM 6.82)

- Discontinuous transmission, DTX (GSM 6.81)

- Comfort noise generation, DRX (GSM 6.62)

- Serial data exchange with Enhanced Full-Rate Channel Codec and voiceband unit on GOLD-SP

- Serial data exchange with system simulator interfacing box (GSM 11.10)

## Hardware:

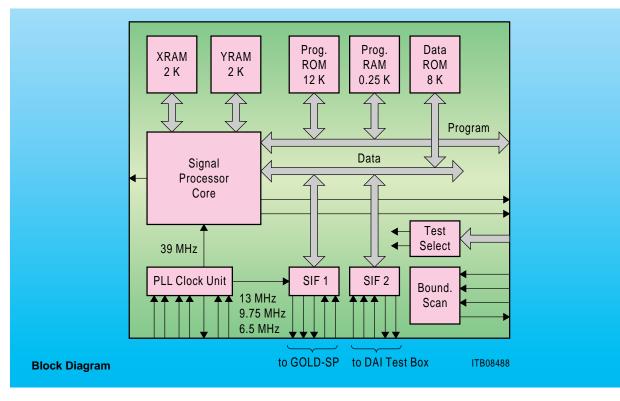

- DSP core of type SPCE (Siemens Signal Processor Core Enhanced) offering high performance (39 MIPS @ 39 MHz, 2.7 V) and current consumption (approx. 1.3 mA/MIPS)

- 12 K Program ROM and 0.25 K RAM, 8 K Data ROM on-chip

- PLL-based clock generation (13-MHz input)

- Package: P-TQFP-64, 10 × 10 mm<sup>2</sup>, 0.50 mm pitch

- 3-V supply voltage (± 10 %)