# HC55120, HC55121, HC55130, HC55131, HC55140, HC55141, HC55142, HC55143, HC55150, HC55151

Data Sheet June 2000 File Number 4659.5

# Low Power Universal SLIC Family

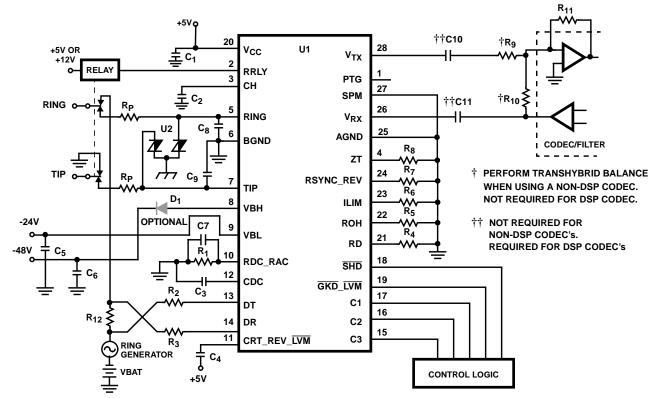

The UniSLIC14 is a family of Ultra Low Power SLICs. The feature set and common pinouts of the UniSLIC14 family positions it as a universal solution for: Plain Old Telephone Service (POTS), PBX, Central Office, Loop Carrier, Fiber in the Loop, ISDN-TA and NT1+, Pairgain and Wireless Local Loop.

The UniSLIC14 family achieves its ultra low power operation through: Its automatic single and dual battery selection (based on line length) and battery tracking anti clipping to ensure the maximum loop coverage on the lowest battery voltage. This architecture is ideal for power critical applications such as ISDN NT1+, Pairgain and Wireless local loop products.

The UniSLIC14 family has many user programmable features. This family of SLICs delivers a low noise, low component count solution for Central Office and Loop Carrier universal voice grade designs. The product family integrates advanced pulse metering, test and signaling capabilities, and zero crossing ring control.

The UniSLIC14 family is designed in the Intersil "Latch" free Bonded Wafer process. This process dielectrically isolates the active circuitry to eliminate any leakage paths as found in our competition's JI process. This makes the UniSLIC14 family compliant with "hot plug" requirements and operation in harsh outdoor environments.

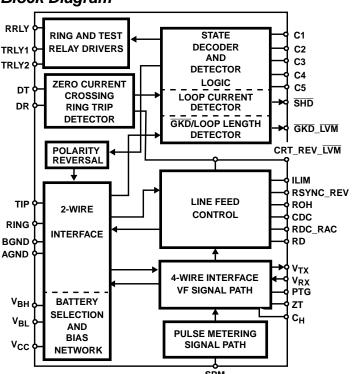

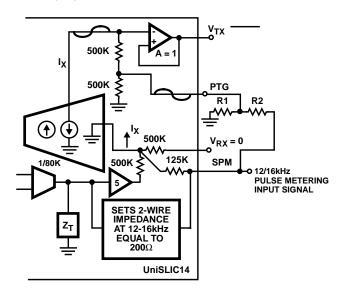

# **Block Diagram**

#### **Features**

- Ultra Low Active Power (OHT) < 60mW

- Single/Dual Battery Operation

- Automatic Silent Battery Selection

- Power Management/Shutdown

- Battery Tracking Anti Clipping

- Single 5V Supply with 3V Compatible Logic

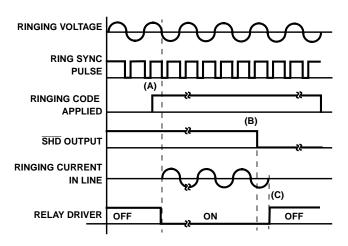

- Zero Crossing Ring Control

- Zero Voltage On/Zero Current Off

- Tip/Ring Disconnect

- · Pulse Metering Capability

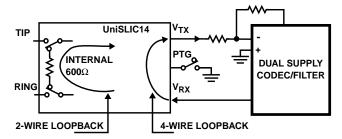

- · 4 Wire Loopback

- · Programmable Current Feed

- · Programmable Resistive Feed

- Programmable Loop Detect Threshold

- Programmable On-Hook and Off-Hook Overheads

- Programmable Overhead for Pulse Metering

- · Programmable Polarity Reversal Time

- Selectable Transmit Gain 0dB/-6dB

- 2 Wire Impedance Set by Single Network

- · Loop and Ground Key Detectors

- On-Hook Transmission

- Common Pinout

- HC55121

- Polarity Reversal

- HC55130

- -63dB Longitudinal Balance

- HC55140

- Polarity Reversal

- Ground Start

- Line Voltage Measurement

- 2 Wire Loopback

- -63dB Longitudinal Balance

- HC55142

- Polarity Reversal

- Ground Start

- Line Voltage Measurement

- 2.2V<sub>RMS</sub> Pulse Metering

- 2 Wire Loopback

- HC55150

- Polarity Reversal

- Line Voltage Measurement

- 2.2V<sub>RMS</sub> Pulse Metering

- 2 Wire Loopback

### **Applications**

- · Related Literature

- AN9871, User's Guide for UniSLIC14 Eval Board

# **Ordering Information**

| PART<br>NUMBER | MAX<br>LOOP<br>CURRENT<br>(mA) | POLARITY<br>REVERSAL | GND<br>START | GND<br>KEY | LINE<br>VOLTAGE<br>MEASUREMENT<br>† | PULSE<br>METERING | 2 TEST<br>RELAY<br>DRIVERS | 2 WIRE<br>LOOP-<br>BACK<br>† | LONGITUDINAL<br>BALANCE | TEMP<br>RANGE<br>(°C) | PKG.<br>NO.       |

|----------------|--------------------------------|----------------------|--------------|------------|-------------------------------------|-------------------|----------------------------|------------------------------|-------------------------|-----------------------|-------------------|

| HC55120CB      | 30                             |                      |              | •          |                                     |                   |                            |                              | 53dB                    | 0 to 70               | M28.3<br>SOIC     |

| HC55120CM      | 30                             |                      |              | •          |                                     |                   |                            |                              | 53dB                    | 0 to 70               | N28.45<br>PLCC    |

| HC55121IB      | 30                             | •                    |              | •          |                                     | •                 |                            | •                            | 53dB                    | -40 to<br>85          | M28.3<br>SOIC     |

| HC55121IM      | 30                             | •                    |              | •          |                                     | •                 |                            | •                            | 53dB                    | -40 to<br>85          | N28.45<br>PLCC    |

| HC55130IB      | 45                             |                      |              |            |                                     |                   |                            |                              | 63dB                    | -40 to<br>85          | M28.3<br>SOIC     |

| HC55130IM      | 45                             |                      |              |            |                                     |                   |                            |                              | 63dB                    | -40 to<br>85          | N28.45<br>PLCC    |

| HC55131IM      | 45                             |                      |              |            |                                     |                   | •                          |                              | 63dB                    | -40 to<br>85          | N32.45x55<br>PLCC |

| HC55140IB      | 45                             | •                    | •            | •          | •                                   |                   |                            | •                            | 63dB                    | -40 to<br>85          | M28.3<br>SOIC     |

| HC55140IM      | 45                             | •                    | •            | •          | •                                   |                   |                            | •                            | 63dB                    | -40 to<br>85          | N28.45<br>PLCC    |

| HC55141IM      | 45                             | •                    | •            | •          | •                                   |                   | •                          | •                            | 63dB                    | -40 to<br>85          | N32.45x55<br>PLCC |

| HC55142IB      | 45                             | •                    | •            | •          | •                                   | •                 |                            | •                            | 63dB                    | -40 to<br>85          | M28.3<br>SOIC     |

| HC55142IM      | 45                             | •                    | •            | •          | •                                   | •                 |                            | •                            | 63dB                    | -40 to<br>85          | N28.45<br>PLCC    |

| HC55143IM      | 45                             | •                    | •            | •          | •                                   | •                 | •                          | •                            | 63dB                    | -40 to<br>85          | N32.45x55<br>PLCC |

| HC55150CB      | 45                             | •                    |              |            | •                                   | •                 |                            | •                            | 55dB                    | 0 to 70               | M28.3<br>SOIC     |

| HC55150CM      | 45                             | •                    |              |            | •                                   | •                 |                            | •                            | 55dB                    | 0 to 70               | N28.45<br>PLCC    |

| HC55151CM      | 45                             | •                    |              |            | •                                   | •                 | •                          | •                            | 55dB                    | 0 to 70               | N32.45x55<br>PLCC |

<sup>†</sup> Available by placing SLIC in Test mode.

# **Device Operating Modes**

| C3 | C2 | C1 | DESCRIPTION                                                      | HC55120 | HC55121 | HC55130/1 | HC55140/1 | HC55142/3 | HC55150/1 |

|----|----|----|------------------------------------------------------------------|---------|---------|-----------|-----------|-----------|-----------|

| 0  | 0  | 0  | Open Circuit<br>4-Wire Loopback                                  | •       | •       | •         | •         | •         | •         |

| 0  | 0  | 1  | Ringing                                                          | •       | •       | •         | •         | •         | •         |

| 0  | 1  | 0  | Forward Active                                                   | •       | •       | •         | •         | •         | •         |

| 0  | 1  | 1  | Test Forward Active 2 Wire Loopback and Line Voltage Measurement |         | •       |           | •         | •         | •         |

| 1  | 0  | 0  | Tip Open Ground Start                                            |         |         |           | •         | •         |           |

| 1  | 0  | 1  | Reserved                                                         | •       | •       | •         | •         | •         | •         |

| 1  | 1  | 0  | Reverse Active                                                   |         | •       |           | •         | •         | •         |

| 1  | 1  | 1  | Test Reverse Active<br>Line Voltage Measurement                  |         |         |           | •         | •         | •         |

# **Absolute Maximum Ratings** T<sub>A</sub> = 25°C

| Temperature, Humidity                                                                   |

|-----------------------------------------------------------------------------------------|

| Storage Temperature Range65°C to 150°C                                                  |

| Operating Temperature Range40°C to 110°C                                                |

| Operating Junction Temperature Range40°C to 150°C                                       |

| Power Supply $(-40^{\circ}\text{C} \le \text{T}_{A} \le 85^{\circ}\text{C})$            |

| Supply Voltage V <sub>CC</sub> to GND0.4V to 7V                                         |

| Supply Voltage V <sub>BL</sub> to GND                                                   |

| Supply Voltage V <sub>BH</sub> to GND, Continuous75V to 0.4V                            |

| Supply Voltage V <sub>BH</sub> to GND, 10ms80V to 0.4V                                  |

| Relay Driver                                                                            |

| Ring Relay Supply Voltage0V to 14V                                                      |

| Ring Relay Current50mA                                                                  |

| Digital Inputs, Outputs (C1, C2, C3, C4, C5, SHD, GKD_LVM)                              |

| Input Voltage0.4V to V <sub>CC</sub>                                                    |

| Output Voltage (SHD, GKD_LVM Not Active)0.4V to VCC                                     |

| Output Current (SHD, GKD_LVM) 5mA                                                       |

| ESD Rating500V                                                                          |

| Gate Count                                                                              |

| Tipx and Ringx Terminals (- $40^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ $85^{\circ}$ C) |

| Tipx or Ringx Current100mA to 100mA                                                     |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1) | $\theta_{\sf JA}$       |

|--------------------------------------|-------------------------|

| 28 Lead PLCC Package                 | 52°C/W                  |

| 28 Lead SOIC Package                 | 45°C/W                  |

| 32 Lead PLCC Package                 | 66.2 <sup>o</sup> C/W   |

| Continuous Power Dissipation at 85°C |                         |

| 28 Lead PLCC Package                 | 1.5W                    |

| 28 Lead SOIC Package                 | 2.0W                    |

| 32 Lead PLCC Package                 |                         |

| Lead Temperature (Soldering 10s)     | 300°C                   |

| (PLCC, SOIC - Lead Tips Only) Derate | above 70 <sup>o</sup> C |

### **Tip and Ring Terminals**

| Tipx or Ringx, Current, Pulse < 10ms, T <sub>REP</sub> > 10s     | 2 <i>F</i> |

|------------------------------------------------------------------|------------|

| Tipx or Ringx, Current, Pulse < 1ms, T <sub>REP</sub> > 10s      | 5/         |

| Tipx or Ringx, Current, Pulse < 10μs, T <sub>REP</sub> > 10s     | 15/        |

| Tipx or Ringx, Current, Pulse $< 1\mu s$ , $T_{REP} > 10s \dots$ | 20/        |

| Tipx or Ringx, Pulse < 250ns, T <sub>REP</sub> > 10s             | 20/        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **Typical Operating Conditions**

These represent the conditions under which the device was developed and are suggested as guidelines.

| PARAMETER                           | CONDITIONS                                  | MIN             | TYP | MAX  | UNITS |

|-------------------------------------|---------------------------------------------|-----------------|-----|------|-------|

| Ambient Temperature                 | HC55120, HC55150/1                          | 0               | =   | 70   | °C    |

|                                     | HC55121, HC55130/1, HC55140/1,<br>HC55142/3 | -40             | -   | 85   | °C    |

| V <sub>BH</sub> with Respect to GND |                                             | -58             | -   | -8   | V     |

| V <sub>BL</sub> with Respect to GND |                                             | V <sub>BH</sub> | -   | 0    | V     |

| V <sub>CC</sub> with Respect to GND |                                             | 4.75            | -   | 5.25 | V     |

Electrical Specifications  $T_A = -40^{\circ}C$  to 85°C,  $V_{CC} = +5V$  ±5%,  $V_{BH} = -48V$ ,  $V_{BL} = -24V$ , PTG = Open,  $R_{P1} = R_{P2} = 0\Omega$ ,  $Z_T = 120k\Omega$ ,  $R_{LIM} = 38.3k\Omega$ ,  $R_D = 50k\Omega$ , RDC\_RAC = 20kΩ,  $R_{OH} = 40k\Omega$ ,  $R_{OH} = 40k\Omega$ ,

| PARAMETER                                                                                           | TEST CONDITIONS                                                                   | MIN | TYP                 | MAX | UNITS                                                   | HC55120         | HC55121  | HC55130/1       | HC55140/1 | HC55142/3       | HC55150/1 |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|---------------------|-----|---------------------------------------------------------|-----------------|----------|-----------------|-----------|-----------------|-----------|

| 2-WIRE PORT                                                                                         |                                                                                   |     | •                   |     |                                                         |                 |          | •               | •         |                 | •         |

| Overload Level, Off Hook<br>Forward and Reverse                                                     | 1% THD, I <sub>DCMET</sub> ≥ 18mA<br>(Note 2, Figure 1)                           | 3.2 | -                   | -   | V <sub>PEAK</sub>                                       | Forward<br>Only | •        | Forward<br>Only | •         | •               | •         |

| Overload Level, On Hook<br>Forward and Reverse                                                      | 1% THD, IDCMET ≤ 5mA<br>(Note 3, Figure 1)                                        | 1.3 | -                   | -   | V <sub>PEAK</sub>                                       | Forward<br>Only | •        | Forward<br>Only | •         | •               | •         |

| Input Impedance (Into Tip and Ring)                                                                 |                                                                                   | -   | Z <sub>T</sub> /200 | -   | Ω                                                       | •               | •        | •               | •         | •               | •         |

| Longitudinal Impedance (Tip, Ring)<br>Forward and Reverse                                           | 0 < f < 100Hz (Note 4, Figure 2)                                                  | -   | 0                   | -   | Ω/Wire                                                  | Forward<br>Only | •        | Forward<br>Only | •         | •               | •         |

| LONGITUDINAL CURRENT LIMIT (                                                                        | TIP, RING)                                                                        | •   | •                   |     |                                                         |                 |          |                 |           |                 | •         |

| $R_L = 736\Omega$                                                                                   | No False Detections, (Loop<br>Current), LB > 45dB (Notes 5, 6,<br>Figures 3A, 3B) | 28  | -                   | -   | mA <sub>RMS</sub> /Wire                                 | Forward<br>Only | •        | Forward<br>Only | •         | •               | •         |

| <u> </u>                                                                                            | >   ··· 1                                                                         |     |                     |     | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$  |                 |          |                 |           |                 |           |

| FIGURE 1. OVERLOAD LEVEL (OFF HOOK, ON HOOK) $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                                                                   |     |                     |     | El<br>=                                                 | c               | 368Ω<br> | TIP  RING  SH   | VRX -     | V <sub>TX</sub> |           |

| FIGURE 3A. LONGITUE                                                                                 | FIGURE 3A. LONGITUDINAL CURRENT LIMIT ON-HOOK (ACTIVE)                            |     |                     |     | FIGURE 3B. LONGITUDINAL CURRENT LIMIT OFF-HOOK (ACTIVE) |                 |          |                 |           |                 | E)        |

# Electrical Specifications $T_A = -40^{\circ}\text{C}$ to 85°C, $V_{CC} = +5\text{V} \pm 5\%$ , $V_{BH} = -48\text{V}$ , $V_{BL} = -24\text{V}$ , PTG = Open, $R_{P1} = R_{P2} = 0\Omega$ , $Z_T = 120\text{k}\Omega$ , $R_{LIM} = 38.3\text{k}\Omega$ , $R_D = 50\text{k}\Omega$ , RDC\_RAC = 20kΩ, $R_{OH} = 40\text{k}\Omega$ , $C_H = 0.1\mu\text{F}$ , $C_{DC} = 4.7\mu\text{F}$ , $C_{RT/REV} = 0.47\mu\text{F}$ , GND = 0V, $R_{CH} = 600\Omega$ . Unless Otherwise Specified. (•) Symbol used to indicate the test applies to the part. (NA) symbol used to indicate the test does not apply to the part. (Continued)

| PARAMETER                                              | TEST CONDITIONS                                                     | MIN | TYP | MAX | UNITS | HC55120         | HC55121 | HC55130/1       | HC55140/1 | HC55142/3 | HC55150/1 |

|--------------------------------------------------------|---------------------------------------------------------------------|-----|-----|-----|-------|-----------------|---------|-----------------|-----------|-----------|-----------|

| OFF-HOOK LONGITUDINAL BAL                              | ANCE                                                                |     |     |     |       | -W              | ļ.      |                 |           |           |           |

|                                                        |                                                                     |     |     |     |       | MIN             | MIN     | MIN             | MIN       | MIN       | MIN       |

| Longitudinal to Metallic (Note 7) Forward and Reverse  | IEEE 455 - 1985, $R_{LR}$ , $R_{LT}$ = 368Ω<br>Normal Polarity:     |     |     |     |       | Forward<br>Only |         | Forward<br>Only |           |           |           |

|                                                        | 0.2kHz < f < 1.0kHz, 0°C to 70°C                                    | -   | -   | -   | dB    | 53              | NA      | NA              | NA        | NA        | 55        |

|                                                        | 1.0kHz < f < 3.4kHz, 0°C to 70°C                                    | -   | -   | -   | dB    | 53              | NA      | NA              | NA        | NA        | 55        |

|                                                        | 0.2kHz < f < 1.0kHz, -40°C to 85°C                                  | -   | -   | -   | dB    | NA              | 53      | 63              | 63        | 63        | NA        |

|                                                        | 1.0kHz < f < 3.4kHz, -40°C to 85°C                                  | -   | -   | -   | dB    | NA              | 53      | 58              | 58        | 58        | NA        |

|                                                        | Reverse Polarity 0.2kHz < f < 3.4kHz, (Figure 4)                    | -   | -   | -   | dB    | NA              | 53      | NA              | 58        | 58        | 55        |

|                                                        |                                                                     |     |     |     |       | MIN             | MIN     | MIN             | MIN       | MIN       | MIN       |

| Longitudinal to Metallic (Note 7) Forward and Reverse  | $R_{LR}$ , $R_{LT} = 300\Omega$ ,<br>Normal Polarity:               |     |     |     |       | Forward<br>Only |         | Forward<br>Only |           |           |           |

|                                                        | 0.2kHz < f < 1.0kHz, 0°C to 70°C                                    | -   | -   | -   | dB    | 53              | NA      | NA              | NA        | NA        | 55        |

|                                                        | 1.0kHz < f < 3.4kHz, 0°C to 70°C                                    | -   | -   | -   | dB    | 53              | NA      | NA              | NA        | NA        | 55        |

|                                                        | 0.2kHz < f < 1.0kHz, -40°C to 85°C                                  | -   | -   | -   | dB    | NA              | 53      | 63              | 63        | 63        | NA        |

|                                                        | 1.0kHz < f < 3.4kHz, -40°C to 85°C                                  | -   | -   | -   | dB    | NA              | 53      | 58              | 58        | 58        | NA        |

|                                                        | Reverse Polarity 0.2kHz < f < 3.4kHz, (Figure 4)                    | -   | -   | -   | dB    | NA              | 53      | NA              | 58        | 58        | 55        |

|                                                        |                                                                     | •   |     |     |       | MIN             | MIN     | MIN             | MIN       | MIN       | MIN       |

| Longitudinal to 4-Wire (Note 9) (Forward and Reverse)  | Normal Polarity:                                                    |     |     |     |       | Forward<br>Only |         | Forward<br>Only |           |           |           |

|                                                        | 0.2kHz < f < $1.0$ kHz, $0$ <sup>o</sup> C to $70$ <sup>o</sup> C   | -   | -   | -   | dB    | 53              | NA      | NA              | NA        | NA        | 61        |

|                                                        | $1.0kHz < f < 3.4kHz, 0^{\circ}C \text{ to } 70^{\circ}C$           | -   | -   | -   | dB    | 53              | NA      | NA              | NA        | NA        | 61        |

|                                                        | 0.2kHz < f < $1.0$ kHz, $-40$ °C to $85$ °C                         | -   | -   | -   | dB    | NA              | 53      | 63              | 63        | 63        | NA        |

|                                                        | 1.0kHz < f < $3.4$ kHz, $-40$ <sup>o</sup> C to $85$ <sup>o</sup> C | -   | -   | -   | dB    | NA              | 53      | 58              | 58        | 58        | NA        |

|                                                        | Reverse Polarity 0.2kHz < f < 3.4kHz, (Figure 4)                    | -   | -   |     | dB    | NA              | 53      | NA              | 58        | 58        | 61        |

| Metallic to Longitudinal (Note 10) Forward and Reverse | FCC Part 68, Para 68.310 (Note 8) 0.2kHz < f < 3.4kHz, (Figure 5)   | 40  | 50  | -   | dB    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| 4-Wire to Longitudinal (Note 11) Forward and Reverse   | 0.2kHz < f < 3.4kHz, (Figure 5)                                     | 40  | -   | -   | dB    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

**Electrical Specifications**  $T_A = -40^{\circ}\text{C to }85^{\circ}\text{C}, V_{CC} = +5\text{V} \pm 5\%, V_{BH} = -48\text{V}, V_{BL} = -24\text{V}, PTG = \text{Open}, R_{P1} = R_{P2} = 0\Omega, Z_T = 120\text{k}\Omega, R_{LIM} = 38.3\text{k}\Omega, R_D = 50\text{k}\Omega, RDC\_RAC = 20\text{k}\Omega, R_{DH} = 40\text{k}\Omega, C_{H} = 0.1\mu\text{F}, C_{DC} = 4.7\mu\text{F}, C_{RT/REV} = 0.47\mu\text{F}, GND = 0\text{V}, RL = 600\Omega$  Unless Otherwise Specified. ( $\bullet$ ) Symbol used to indicate the test applies to the part. (NA) symbol used to indicate the test does not apply to the part. (Continued)

Electrical Specifications  $T_A = -40^{\circ}C \text{ to } 85^{\circ}C, \ V_{CC} = +5V \pm 5\%, \ V_{BH} = -48V, \ V_{BL} = -24V, \ PTG = Open, \ R_{P1} = R_{P2} = 0\Omega, \ Z_T = 120k\Omega, \ R_{LIM} = 38.3k\Omega, \ R_D = 50k\Omega, \ RDC_RAC = 20k\Omega, \ R_{OH} = 40k\Omega, \ C_H = 0.1\mu\text{F}, \ C_{DC} = 4.7\mu\text{F}, \ C_{RT/REV} = 0.47\mu\text{F}, \ GND = 0V, \ RL = 600\Omega \ Unless \ Otherwise \ Specified. }$  Symbol used to indicate the test applies to the part. (NA) symbol used to indicate the test does not apply to the part. (Continued)

| PARAMETER                                                               | TEST CONDITIONS                                                                   | MIN             | TYP  | MAX  | UNITS             | HC55120         | HC55121    | HC55130/1         | HC55140/1       | HC55142/3 | HC55150/ |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|------|------|-------------------|-----------------|------------|-------------------|-----------------|-----------|----------|

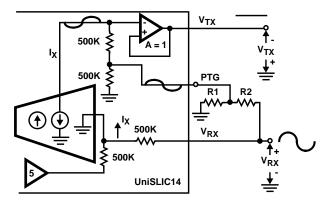

| 4-WIRE TRANSMIT PORT (V <sub>TX</sub> )                                 |                                                                                   |                 |      |      |                   |                 |            |                   |                 |           |          |

| Overload Level, Off Hook (I <sub>L</sub> ≥ 18mA)<br>Forward and Reverse | Figure 7) $T_A = 0^{\circ}C$ to $85^{\circ}C$                                     | 3.2             | -    | -    | V <sub>PEAK</sub> | Forward<br>Only | •          | Forward<br>Only   | •               | •         | •        |

|                                                                         | $T_A = -40^{\circ} \text{C} \text{ to } 0^{\circ} \text{C}$                       | 3.0             | -    | -    | $V_{PEAK}$        |                 |            |                   |                 |           |          |

| Overload Level, On Hook (I <sub>L</sub> ≤ 5mA)<br>Forward and Reverse   | (Z <sub>L</sub> > 20kΩ, 1% THD)<br>(Note 14, Figure 7)                            | 1.3             | -    | -    | V <sub>PEAK</sub> | Forward<br>Only | •          | Forward<br>Only   | •               | •         | •        |

| V <sub>TX</sub> Output Offset Voltage<br>Forward and Reverse            | $E_G = 0$ , $Z_L = \infty$ , (Note 15, Figure 7)                                  | -200            | -    | 200  | mV                | Forward<br>Only | •          | Forward<br>Only   | •               | •         | •        |

| Output Impedance<br>(Guaranteed by Design)                              | 0.2kHz < f < 03.4kHz                                                              | ,               | 0.1  | 1    | Ω                 | •               | •          | •                 | •               | •         | •        |

| 4-WIRE RECEIVE PORT (VRX)                                               |                                                                                   |                 |      |      |                   |                 |            |                   |                 |           |          |

| VRX Input Impedance<br>(Guaranteed by Design)                           | 0.2kHz < f < 3.4kHz                                                               | -               | 500  | 600  | kΩ                | •               | •          | •                 | •               | •         | •        |

| FREQUENCY RESPONSE (OFF-HO                                              | DOK)                                                                              |                 |      |      |                   |                 |            |                   |                 |           |          |

| 2-Wire to 4-Wire<br>Forward and Reverse                                 | Relative to 0dBm at 1.0kHz, $E_{RX} = 0V$<br>0.3kHz < f < 3.4kHz                  | -0.15           | _    | 0.15 | dB                | Forward<br>Only |            | Forward<br>Only   |                 |           |          |

|                                                                         | f = 8.0kHz (Note 16, Figure 8)                                                    | -               | 0.24 | 0.5  | dB                |                 | •          |                   | •               | •         | •        |

|                                                                         | f = 12kHz (Note 16, Figure 8)                                                     | -               | 0.58 | 1.0  | dB                | 1               |            |                   |                 |           |          |

|                                                                         | f = 16kHz (Note 16, Figure 8)                                                     | -               | 1.0  | 1.5  | dB                |                 |            |                   |                 |           |          |

| 4-Wire to 2-Wire<br>Forward and Reverse                                 | Relative to 0dBm at 1.0kHz, E <sub>G</sub> = 0V 0.3kHz < f < 3.4kHz               | -0.15           | -    | 0.15 | dB                | Forward<br>Only |            | Forward<br>Only   |                 |           |          |

|                                                                         | f = 8kHz (Note 17, Figure 8)                                                      | -0.5            | 0.24 | -    | dB                |                 | •          |                   | •               | •         | •        |

|                                                                         | f = 12kHz (Note 17, Figure 8)                                                     | -1.0            | 0.58 | -    | dB                |                 |            |                   |                 |           |          |

|                                                                         | f = 16kHz (Note 17, Figure 8)                                                     | -1.5            | 1.0  | -    | dB                |                 |            |                   |                 |           |          |

| 4-Wire to 4-Wire<br>Forward and Reverse                                 | Relative to 0dBm at 1.0kHz, $E_G = 0V$<br>0.3kHz < f < 3.4kHz (Note 18, Figure 8) | -0.15           | 1    | 0.15 | dB                | Forward<br>Only | •          | Forward<br>Only   | •               | •         |          |

|                                                                         | 8kHz, 12kHz, 16kHz (Note 18, Figure 8)                                            | -0.5            | 0    | 0.5  | dB                |                 |            |                   |                 |           |          |

| E <sub>G</sub>                                                          | OPEN ▼                                                                            | v <sub>TX</sub> |      |      |                   | R <sub>L</sub>  | TIP        | V <sub>TX</sub> - | V <sub>TX</sub> |           |          |

| FIGURE 8. FREQUENCY RESP<br>AND HARMONIC DI                             | ONSE, INSERTION LOSS, GAIN TRAC<br>STORTION                                       | KING            |      |      |                   | FIGU            | RE 9. IDLE | CHANNEL           | NOISE           |           |          |

# Electrical Specifications $T_A = -40^{\circ}\text{C}$ to 85°C, $V_{CC} = +5\text{V} \pm 5\%$ , $V_{BH} = -48\text{V}$ , $V_{BL} = -24\text{V}$ , PTG = Open, $R_{P1} = R_{P2} = 0\Omega$ , $Z_T = 120\text{k}\Omega$ , $R_{LIM} = 38.3\text{k}\Omega$ , $R_D = 50\text{k}\Omega$ , RDC\_RAC = 20kΩ, $R_{OH} = 40\text{k}\Omega$ , $C_H = 0.1\mu\text{F}$ , $C_{DC} = 4.7\mu\text{F}$ , $C_{RT/REV} = 0.47\mu\text{F}$ , GND = 0V, $R_{CH} = 600\Omega$ . Unless Otherwise Specified. (•) Symbol used to indicate the test applies to the part. (NA) symbol used to indicate the test does not apply to the part. (Continued)

| PARAMETER                                             | TEST CONDITIONS                                          | MIN   | TYP   | MAX   | UNITS                   | HC55120            | HC55121           | HC55130/1       | HC55140/1         | HC55142/3 | HC55150/1 |

|-------------------------------------------------------|----------------------------------------------------------|-------|-------|-------|-------------------------|--------------------|-------------------|-----------------|-------------------|-----------|-----------|

| INSERTION LOSS                                        |                                                          |       |       |       |                         |                    | •                 |                 | •                 |           |           |

| 2-Wire to 4-Wire                                      | 0dBm, 1kHz                                               |       |       |       |                         |                    |                   |                 |                   |           |           |

| Forward and Reverse                                   | PTG = Open (Note 19, Figure 8)                           | -0.2  | -     | 0.2   | dB                      | Forward            | •                 | Forward         | •                 | •         | •         |

|                                                       | PTG = GND (Note 20, Figure 8)                            | -6.22 | -6.02 | -5.82 | dB                      | Only               |                   | Only            |                   |           |           |

| 4-Wire to 2-Wire                                      | 0dBm, 1kHz (Note 21, Figure 8)                           | -0.2  | -     | 0.2   | dB                      | Forward            | •                 | Forward         |                   | •         | •         |

| Forward and Reverse                                   |                                                          |       |       |       |                         | Only               |                   | Only            |                   |           |           |

| GAIN TRACKING (Ref = -10dBm, a                        | at 1.0kHz)                                               |       |       |       |                         |                    |                   |                 |                   |           |           |

| 2-Wire to 4-Wire                                      | -40dBm to +3dBm (Note 22, Figure 8)                      | -0.1  | -     | 0.1   | dB                      | Forward            |                   | Forward         |                   |           |           |

| Forward and Reverse                                   | -55dBm to -40dBm (Note 22, Figure 8)                     | -0.2  | -     | 0.2   | dB                      | Only               | _                 | Only            | _                 | -         | _         |

| 4-Wire to 2-Wire                                      | -40dBm to +3dBm (Note 23, Figure 8)                      | -0.1  | -     | 0.1   | dB                      | Forward            | •                 | Forward         |                   |           |           |

| Forward and Reverse                                   | -55dBm to -40dBm (Note 23, Figure 8)                     | -0.2  | -     | 0.2   | dB                      | Only               |                   | Only            | •                 |           | •         |

| NOISE                                                 |                                                          |       | •     |       |                         |                    | •                 |                 | •                 |           | •         |

| Idle Channel Noise at 2-Wire                          | C-Message Weighting                                      | -     | 10.5  | 13    | dBrnC                   | Forward            |                   | Forward         |                   |           |           |

| Forward and Reverse                                   | Psophometric Weighting (Note 24, Note 30, Figure 9)      | -     | -79.5 | -77   | dBmp                    | Only               | •                 | Only            | •                 | •         | •         |

| Idle Channel Noise at 4-Wire                          | C-Message Weighting                                      | -     | 10.5  | 13    | dBrnC                   | Forward            |                   | Forward         |                   |           |           |

| Forward and Reverse                                   | Psophometrical Weighting<br>(Note 25, Note 30, Figure 9) | -     | -79.5 | -77   | dBmp                    | Only               | •                 | Only            | •                 | •         | •         |

| HARMONIC DISTORTION                                   |                                                          |       |       |       |                         |                    | l.                |                 |                   |           |           |

| 2-Wire to 4-Wire<br>Forward and Reverse               | 0dBm, 0.3kHz to 3.4kHz<br>(Note 26, Figure 7)            | -     | -67   | -50   | dB                      | Forward<br>Only    | •                 | Forward<br>Only | •                 | •         | •         |

| 4-Wire to 2-Wire<br>Forward and Reverse               | 0dBm, 0.3kHz to 3.4kHz<br>(Note 27, Figure 8)            | -     | -67   | -50   | dB                      | Forward<br>Only    | •                 | Forward<br>Only | •                 | •         | •         |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                                          |       |       |       |                         | V <sub>ВН</sub> «А | S I <sub>R1</sub> |                 | V <sub>TX</sub> — |           |           |

| FIGURE 10. CON                                        | FIGURE 10. CONSTANT LOOP CURRENT TOLERANCE               |       |       |       | FIGURE 11. TIPX VOLTAGE |                    |                   |                 |                   |           |           |

# Electrical Specifications $T_A = -40^{\circ}\text{C}$ to 85°C, $V_{CC} = +5\text{V} \pm 5\%$ , $V_{BH} = -48\text{V}$ , $V_{BL} = -24\text{V}$ , PTG = Open, $R_{P1} = R_{P2} = 0\Omega$ , $Z_T = 120\text{k}\Omega$ , $R_{LIM} = 38.3\text{k}\Omega$ , $R_D = 50\text{k}\Omega$ , RDC\_RAC = 20kΩ, $R_{OH} = 40\text{k}\Omega$ , $C_H = 0.1\mu\text{F}$ , $C_{DC} = 4.7\mu\text{F}$ , $C_{RT/REV} = 0.47\mu\text{F}$ , GND = 0V, $R_{CH} = 600\Omega$ . Unless Otherwise Specified. (•) Symbol used to indicate the test applies to the part. (NA) symbol used to indicate the test does not apply to the part. (Continued)

| PARAMETER                                                                             | TEST CONDITIONS                                                     | MIN                 | TYP       | MAX                 | UNITS | HC55120         | HC55121 | HC55130/1       | HC55140/1 | HC55142/3 | HC55150/1 |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------|-----------|---------------------|-------|-----------------|---------|-----------------|-----------|-----------|-----------|

| BATTERY FEED CHARACTERIST                                                             | ics                                                                 |                     |           |                     |       |                 | •       |                 |           | •         |           |

| Constant Loop Current Tolerance $I_L = 26.5 \text{mA}, R_{LIM} = 38.3 \text{k}\Omega$ | 18mA ≤ IL ≤ 45mA,<br>(Note 27, Figure 10)                           | 0.92I <sub>L</sub>  | ΙL        | 1.08I <sub>L</sub>  | mA    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| Forward and Reverse                                                                   |                                                                     |                     |           |                     |       |                 |         |                 |           |           |           |

| Tip Open State TIPX Leakage<br>Current                                                | S = Closed (Figure 11)                                              | -                   | -         | -200                | μА    | •               | •       | •               | •         | •         | •         |

| Tip Open State RINGX Current                                                          | $R_1 = 0\Omega$ , $V_{BH} = -48V$ , $R_{LIM} = 38.3k\Omega$         | 22.6                | 26.8      | 31                  | mA    |                 | •       | •               |           | •         |           |

|                                                                                       | $R_1 = 2.5k\Omega$ , $V_{BH} = -48V$ (Figure 11)                    | 15.5                | 17.1      | 18.2                | mA    |                 |         |                 |           |           |           |

| Tip Open State RINGX Voltage                                                          | 5mA < I <sub>R1</sub> < 26mA (Figure 11)                            | -                   | 42.8      | -                   | V     | •               | •       | •               | •         | •         | •         |

| Tip Voltage (Ground Start)                                                            | Active State, (S Open) $R_1 = 150\Omega$ (Figure 11)                | -5.3                | -4.8      | -4.3                | V     | NA              | NA      | NA              | •         | •         | NA        |

| Tip Voltage (Ground Start)                                                            | Active State, (S Closed) Tip Lead to -48V Through 7kΩ, Ring Lead to | -5.3                | -4.8      | -4.3                | V     | NA              | NA      | NA              | •         | •         | NA        |

|                                                                                       | Ground Through 150Ω (Figure 11)                                     |                     |           |                     |       |                 |         |                 |           |           |           |

| Open Circuit State Loop Current                                                       | (Active) $R_L = 0\Omega$                                            | -20                 | 0         | 20                  | μΑ    | •               | •       | •               | •         | •         | •         |

| LOOP CURRENT DETECTOR                                                                 |                                                                     |                     |           |                     |       |                 |         |                 |           |           |           |

| Programmable Threshold                                                                | $I_{LTh} = (500/R_D) \ge 5mA,$                                      | 0.9I <sub>LTh</sub> | $I_{LTh}$ | 1.11 <sub>LTh</sub> | mA    | Forward         |         | Forward         |           |           |           |

| Forward and Reverse                                                                   | I <sub>LTh</sub> = 8.5mA                                            |                     |           |                     |       | Only            | •       | Only            | •         | •         | •         |

|                                                                                       | $R_D = 58.8k\Omega$                                                 |                     |           |                     |       |                 |         |                 |           |           |           |

| GROUND KEY DETECTOR                                                                   |                                                                     |                     |           |                     |       |                 |         |                 |           |           |           |

| Ground Key Detector Threshold                                                         | Tip Open                                                            | 5                   | 8         | 11                  | mA    |                 |         | NA              |           |           | NA        |

| Tip/Ring Current Difference                                                           | Active (Note 29, R1 = $2.5k\Omega$ , Figure 12)                     | 12.5                | 20        | 27.5                | mA    |                 |         |                 |           |           |           |

| LINE VOLTAGE MEASUREMENT                                                              |                                                                     |                     |           | •                   |       |                 |         |                 | •         | •         |           |

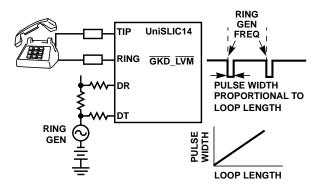

| Pulse Width (GKD_LVM)                                                                 | Pulse Width = (20)(C <sub>REV</sub> /I <sub>LIM</sub> )             | 0.32                | 0.36      | 0.4                 | ms/V  | NA              | NA      | NA              | •         | •         | •         |

| RING TRIP DETECTOR (DT, DR)                                                           |                                                                     |                     |           |                     |       |                 |         |                 |           |           |           |

| Ring Trip Comparator Current                                                          | Source Res = $2M\Omega$                                             | -                   | 2         | -                   | μΑ    | •               | •       | •               | •         | •         | •         |

| Input Common-Mode Range                                                               | Source Res = $2M\Omega$                                             | -                   | -         | ±200                | V     | •               | •       | •               | •         | •         | •         |

DIGITAL INPUTS (C1, C2, C3)

# Electrical Specifications $T_A = -40^{\circ}C \text{ to } 85^{\circ}C, \ V_{CC} = +5V \pm 5\%, \ V_{BH} = -48V, \ V_{BL} = -24V, \ PTG = Open, \ R_{P1} = R_{P2} = 0\Omega, \ Z_T = 120k\Omega, \ R_{LIM} = 38.3k\Omega, \ R_D = 50k\Omega, \ RDC_RAC = 20k\Omega, \ R_{OH} = 40k\Omega, \ C_H = 0.1\mu\text{F}, \ C_{DC} = 4.7\mu\text{F}, \ C_{RT/REV} = 0.47\mu\text{F}, \ GND = 0V, \ RL = 600\Omega. \ Unless \ Otherwise \ Specified. }$ Symbol used to indicate the test applies to the part. (NA) symbol used to indicate the test does not apply to the part. (Continued)

| PARAMETER                    | TEST CONDITIONS         | MIN | TYP  | MAX | UNITS | HC55120 | HC55121 | HC55130/1 | HC55140/1 | HC55142/3 | HC55150/1 |  |  |

|------------------------------|-------------------------|-----|------|-----|-------|---------|---------|-----------|-----------|-----------|-----------|--|--|

| RING RELAY DRIVER            | RING RELAY DRIVER       |     |      |     |       |         |         |           |           |           |           |  |  |

| V <sub>SAT</sub> at 30mA     | I <sub>OL</sub> = 30mA  | -   | 0.2  | 0.5 | V     | •       | •       | •         | •         | •         | •         |  |  |

| V <sub>SAT</sub> at 40mA     | I <sub>OL</sub> = 40mA  | -   | 0.52 | 0.8 | V     | •       | •       | •         | •         | •         | •         |  |  |

| Off State Leakage Current    | V <sub>OH</sub> = 13.2V | -   | 0.1  | 10  | μΑ    | •       | •       | •         | •         | •         | •         |  |  |

| TEST RELAY DRIVER (TRLY1, TR | LY2)                    |     |      |     |       |         |         | •         | •         |           |           |  |  |

| V <sub>SAT</sub> at 30mA     | I <sub>OL</sub> = 30mA  | -   | 0.3  | 0.5 | V     | NA      | NA      | NA/●      | NA/●      | NA/●      | NA/●      |  |  |

| V <sub>SAT</sub> at 40mA     | I <sub>OL</sub> = 40mA  | -   | 0.62 | 0.9 | V     | NA      | NA      | NA/●      | NA/®      | NA/•      | NA/●      |  |  |

| Off State Leakage Current    | V <sub>OH</sub> = 13.2V | -   | -    | 10  | μΑ    | NA      | NA      | NA/●      | NA/●      | NA/●      | NA/●      |  |  |

#### FIGURE 12. GROUND KEY DETECT

| Input Low Voltage, V <sub>IL</sub>                                   |                                                      | 0   | -  | 0.8             | V  | •               | •   | •               | •           | •           | •   |

|----------------------------------------------------------------------|------------------------------------------------------|-----|----|-----------------|----|-----------------|-----|-----------------|-------------|-------------|-----|

| Input High Voltage, VIH                                              |                                                      | 2.0 | -  | V <sub>CC</sub> | V  | •               | •   | •               | •           | •           | •   |

| Input Low Current, I <sub>IL</sub>                                   | V <sub>IL</sub> = 0.4V                               | -   | -  | -10             | μΑ | •               | •   | •               | •           | •           | •   |

| Input High Current, I <sub>IH</sub>                                  | V <sub>IH</sub> = 2.5V                               | -   | 25 | 50              | μΑ | •               | •   | •               | •           | •           | •   |

| DETECTOR OUTPUTS (SHD, GKD                                           | _LVM)                                                | •   |    |                 |    |                 |     | •               |             |             |     |

| SHD Output Low Voltage, V <sub>OL</sub><br>Forward, Reverse          | I <sub>OL</sub> = 1mA                                | -   | -  | 0.5             | V  | Forward<br>Only | •   | Forward<br>Only | •           | •           | •   |

| SHD Output High Voltage, V <sub>OH</sub><br>Forward, Reverse         | I <sub>OH</sub> = 100μA                              | 2.7 | -  |                 | V  | Forward<br>Only | •   | Forward<br>Only | •           | •           | •   |

|                                                                      | $I_{OL}$ = 1mA<br>R <sub>1</sub> = 2.5kΩ (Figure 11) | -   | -  | 0.5             | V  | GKD             | GKD | NA              | GKD_<br>LVM | GKD_<br>LVM | LVM |

| GKD_LVM Output High Voltage,<br>V <sub>OH</sub> Forward and Tip Open | I <sub>OH</sub> = 100μA                              | 2.7 | -  | -               | V  | GKD             | GKD | NA              | GKD_<br>LVM | GKD_<br>LVM | LVM |

| Internal Pull-Up Resistor                                            |                                                      | -   | 15 | -               | kΩ | •               | •   | •               | •           | •           | •   |

# Electrical Specifications $T_A = -40^{\circ}C \text{ to } 85^{\circ}C, \ V_{CC} = +5V \pm 5\%, \ V_{BH} = -48V, \ V_{BL} = -24V, \ PTG = Open, \ R_{P1} = R_{P2} = 0\Omega, \ Z_T = 120k\Omega, \ R_{LIM} = 38.3k\Omega, \ R_D = 50k\Omega, \ RDC_RAC = 20k\Omega, \ R_{OH} = 40k\Omega, \ C_H = 0.1\mu\text{F}, \ C_{DC} = 4.7\mu\text{F}, \ C_{RT/REV} = 0.47\mu\text{F}, \ GND = 0V, \ RL = 600\Omega. \ Unless \ Otherwise \ Specified. }$ Symbol used to indicate the test applies to the part. (NA) symbol used to indicate the test does not apply to the part. (Continued)

| PARAMETER                                                       | TEST CONDITIONS                                                       | MIN | TYP   | MAX   | UNITS | HC55120         | HC55121 | HC55130/1       | HC55140/1 | HC55142/3 | HC55150/1 |

|-----------------------------------------------------------------|-----------------------------------------------------------------------|-----|-------|-------|-------|-----------------|---------|-----------------|-----------|-----------|-----------|

| POWER DISSIPATION (VBH = -48)                                   | V, V <sub>BL</sub> = -24V)                                            | •   |       |       |       |                 | •       |                 |           |           |           |

| Open Circuit State                                              | C1, C2, C3 = 0, 0, 0                                                  | -   | 25    | -     | mW    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| On-Hook, Active                                                 | C1, C2, C3 = 0, 1, 0<br>C1, C2, C3 = 1, 1, 0                          |     |       |       |       |                 | •       |                 | •         | •         | •         |

| Forward and Reverse                                             | I <sub>L</sub> = 0mA, Longitudinal<br>Current = 0mA                   | -   | 52    | -     | mW    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| POWER SUPPLY CURRENTS (VB                                       | H = -48V, V <sub>BL</sub> = -24V)                                     | •   |       |       |       |                 |         | •               | •         | •         |           |

| V <sub>CC</sub> Current, I <sub>CC</sub>                        | Open Circuit State                                                    | -   | 2.25  | 3.0   | mA    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| V <sub>BH</sub> Current, I <sub>BH</sub>                        |                                                                       | -   | 0.3   | 0.45  | mA    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| V <sub>BL</sub> Current, I <sub>BL</sub>                        |                                                                       | -   | 0.022 | 0.035 | mA    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| V <sub>CC</sub> Current, I <sub>CC</sub><br>Forward and Reverse | Active State I <sub>L</sub> = 0mA, Longitudinal                       | -   | 2.7   | 3.6   | mA    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| V <sub>BH</sub> Current, I <sub>BH</sub><br>Forward and Reverse | Current = 0mA                                                         | -   | 0.8   | 1.06  | mA    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| V <sub>BL</sub> Current, I <sub>BL</sub><br>Forward and Reverse |                                                                       | -   | -     | 0.01  | mA    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| POWER SUPPLY REJECTION RA                                       | TIOS                                                                  | •   |       |       |       |                 | •       |                 | •         |           |           |

| V <sub>CC</sub> to 2 or 4 Wire Port<br>Forward and Reverse      | Active State $R_L = 600\Omega$<br>$50Hz < f < 3400Hz, V_{IN} = 100mV$ | -   | 40    | -     | dB    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| V <sub>BH</sub> to 2 or 4 Wire Port<br>Forward and Reverse      |                                                                       | -   | 40    | -     | dB    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| V <sub>BL</sub> to 2 or 4 Wire Port<br>Forward and Reverse      | 1                                                                     | -   | 40    | -     | dB    | Forward<br>Only | •       | Forward<br>Only | •         | •         | •         |

| TEMPERATURE GUARD                                               |                                                                       | •   | •     |       |       |                 | •       | •               | •         | •         |           |

| Junction Threshold Temperature                                  |                                                                       | -   | 175   | -     | °C    | •               | •       | •               | •         | •         | •         |

#### **Notes**

- 2. Overload Level (Two-Wire Port, Off Hook) The overload level is specified at the 2-wire port (V<sub>TR</sub>) with the signal source at the 4-wire receive port (E<sub>RX</sub>). R<sub>L</sub> = 600 $\Omega$ , I<sub>DCMET</sub>  $\geq$  18mA. Increase the amplitude of E<sub>RX</sub> until 1% THD is measured at V<sub>TR</sub>. Reference Figure 1.

- 3. Overload Level (Two-Wire Port, On Hook) The overload level is specified at the 2-wire port ( $V_{TR}$ ) with the signal source at the 4-wire receive port ( $E_{RX}$ ).  $R_L = \infty$ ,  $I_{DCMET} = 0$ mA. Increase the amplitude of  $E_{RX}$  until 1% THD is measured at  $V_{TR}$ . Reference Figure 1.

- 4. Longitudinal Impedance The longitudinal impedance is computed using the following equations, where TIP and RING voltages are referenced to ground. L<sub>ZT</sub>, L<sub>ZR</sub>, V<sub>T</sub>, V<sub>R</sub>, A<sub>R</sub> and A<sub>T</sub> are defined in Figure 2.

(TIP)  $L_{ZT} = V_T/A_T$ (RING)  $L_{ZR} = V_R/A_R$

where:  $E_L = 1V_{RMS}$  (0Hz to 100Hz)

- 5. Longitudinal Current Limit (On-Hook Active) On-Hook longitudinal current limit is determined by increasing the (60Hz) amplitude of E<sub>L</sub> (Figure 3A) until the 2-wire longitudinal current is greater than 28mA<sub>RMS</sub>/Wire. Under this condition, SHD pin remains low (no false detection) and the 2-wire to 4-wire longitudinal balance is verified to be greater than 45dB (LB<sub>2-4</sub> = 20log VTX/E<sub>L</sub>).

- 6. Longitudinal Current Limit (Off-Hook Active) Off-Hook longitudinal current limit is determined by increasing the (60Hz) amplitude of E<sub>L</sub> (Figure 3B) until the 2-wire longitudinal current is greater than 28mA<sub>RMS</sub>/Wire. Under this condition, SHD pin remains high (no false detection) and the 2-wire to 4-wire longitudinal balance is verified to be greater than 45dB (LB<sub>2-4</sub> = 20log VTX/E<sub>L</sub>).

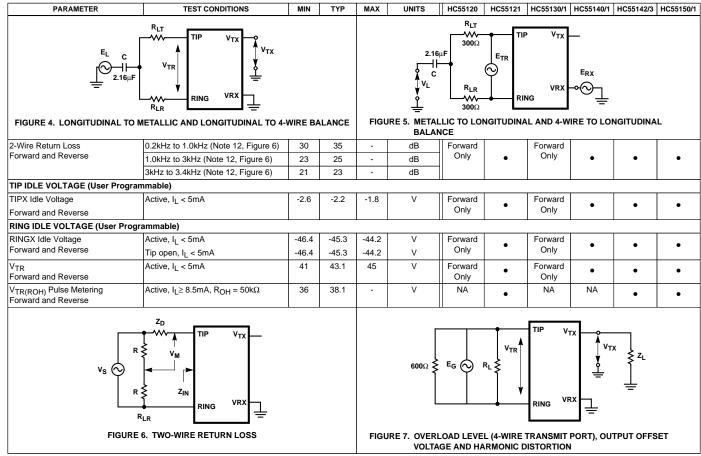

- 7. Longitudinal to Metallic Balance The longitudinal to metallic balance is computed using the following equation: BLME = 20 log (E<sub>L</sub>/V<sub>TR</sub>), where: E<sub>L</sub> and V<sub>TR</sub> are defined in Figure 4.

- Metallic to Longitudinal FCC Part 68, Para 68.310 The metallic to longitudinal balance is defined in this spec.

- Longitudinal to Four-Wire Balance The longitudinal to 4-wire balance is computed using the following equation:

BLFE = 20 log ( $E_L/V_{TX}$ ),  $E_L$  and  $V_{TX}$  are defined in Figure 4.

10. Metallic to Longitudinal Balance - The metallic to longitudinal balance is computed using the following equation:

$BMLE = 20 log (E_{TR}/V_L), E_{RX} = 0$

where:  $E_{TR}$   $V_I$  and  $E_{RX}$  are defined in Figure 5.

**11. Four-Wire to Longitudinal Balance** - The 4-wire to longitudinal balance is computed using the following equation:

BFLE =  $20 \log (E_{RX}/V_L)$ ,  $E_{TR}$  = source is removed.

where: E<sub>RX.</sub> V<sub>L</sub> and E<sub>TR</sub> are defined in Figure 5.

**12. Two-Wire Return Loss -** The 2-wire return loss is computed using the following equation:

r = -20 log (2V<sub>M</sub>/V<sub>S</sub>) where:  $Z_D$  = The desired impedance; e.g., the characteristic impedance of the line, nominally 600Ω. (Reference Figure 6).

13. Overload Level (4-Wire Port Off-Hook) - The overload level is specified at the 4-wire transmit port ( $V_{TX}$ ) with the signal source ( $E_G$ ) at the 2-wire port,  $Z_L = 20k\Omega$ ,  $R_L = 600\Omega$  (Reference Figure 7). Increase the amplitude of  $E_G$  until 1% THD is measured at  $V_{TX}$ . Note the PTG pin is open, and the gain from the 2-wire port to the 4-wire port is equal to 1.

- **14.** Overload Level (4-Wire Port On-Hook) The overload level is specified at the 4-wire transmit port ( $V_{TX}$ ) with the signal source ( $E_G$ ) at the 2-wire port,  $Z_L = 20k\Omega$ ,  $R_L = \infty$  (Reference Figure 7). Increase the amplitude of  $E_G$  until 1% THD is measured at  $V_{TX}$ . Note the PTG pin is open, and the gain from the 2-wire port to the 4-wire port is equal to 1.

- **15. Output Offset Voltage** The output offset voltage is specified with the following conditions:  $E_G = 0$ ,  $R_L = 600\Omega$ ,  $Z_L = \infty$  and is measured at  $V_{TX}$ .  $E_G$ ,  $R_L$ ,  $V_{TX}$  and  $Z_L$  are defined in Figure 7.

- 16. Two-Wire to Four-Wire Frequency Response The 2-wire to 4-wire frequency response is measured with respect to  $E_G$  = 0dBm at 1.0kHz,  $E_{RX}$  = 0V (VRX input floating),  $R_L$  = 600 $\Omega$ . The frequency response is computed using the following equation:

$F_{2-4} = 20 \log (V_{TX}/V_{TR})$ , vary frequency from 300Hz to 3.4kHz and compare to 1kHz reading.

$V_{TX}$ ,  $V_{TR}$ ,  $R_L$  and  $E_G$  are defined in Figure 8.

17. Four-Wire to Two-Wire Frequency Response - The 4-wire to 2-wire frequency response is measured with respect to  $E_{RX}=0$ dBm at 1.0kHz,  $E_G$  source removed from circuit,  $R_L=600\Omega$ . The frequency response is computed using the following equation:

$\rm F_{4-2}$  = 20 log (V\_{TR}/E\_{RX}), vary frequency from 300Hz to 3.4kHz and compare to 1kHz reading.

V<sub>TR</sub>, R<sub>I</sub> and E<sub>RX</sub> are defined in Figure 8.

18. Four-Wire to Four-Wire Frequency Response - The 4-wire to 4-wire frequency response is measured with respect to  $E_{RX}=0$ dBm at 1.0kHz,  $E_{G}$  source removed from circuit,  $R_{L}=600\Omega$ . The frequency response is computed using the following equation:

$F_{4-4}$  = 20 log ( $V_{TX}/E_{RX}$ ), vary frequency from 300Hz to 3.4kHz and compare to 1kHz reading.

V<sub>TX</sub> R<sub>I</sub> and E<sub>RX</sub> are defined in Figure 8.

19. Two-Wire to Four-Wire Insertion Loss (PTG = Open) - The 2-wire to 4-wire insertion loss is measured with respect to  $E_G = 0 dBm$  at 1.0kHz input signal,  $E_{RX} = 0$  (VRX input floating),  $R_L = 600\Omega$  and is computed using the following equation:

$L_{2-4} = 20 \log (V_{TX}/V_{TR})$

where:  $V_{TX}$ ,  $V_{TR}$ ,  $R_L$  and  $E_G$  are defined in Figure 8. (Note: The fuse resistors,  $R_F$ , impact the insertion loss. The specified insertion loss is for  $R_{F1} = R_{F2} = 0$ ).

20. Two-Wire to Four-Wire Insertion Loss (PTG = AGND) - The 2-wire to 4-wire insertion loss is measured with respect to E<sub>G</sub> = 0dBm at 1.0kHz input signal, E<sub>RX</sub> = 0 (VRX input floating), R<sub>L</sub> =  $600\Omega$  and is computed using the following equation:

$L_{2-4} = 20 \log (V_{TX}/V_{TR})$

where:  $V_{TX}$ ,  $V_{TR}$ ,  $R_L$  and  $E_G$  are defined in Figure 8. (Note: The fuse resistors,  $R_F$ , impact the insertion loss. The specified insertion loss is for  $R_{F1}=R_{F2}=0$ ).

21. Four-Wire to Two-Wire Insertion Loss - The 4-wire to 2-wire insertion loss is measured based upon  $E_{RX}$  = 0dBm, 1.0kHz input signal,  $E_G$  source removed from circuit,  $R_L$  =  $600\Omega$  and is computed using the following equation:

$L_{4-2} = 20 \log (V_{TR}/E_{RX})$

where:  $V_{TR}$ ,  $R_L$  and  $E_{RX}$  are defined in Figure 8.

22. Two-Wire to Four-Wire Gain Tracking - The 2-wire to 4-wire gain tracking is referenced to measurements taken for E<sub>G</sub> = -10dBm, 1.0kHz signal, E<sub>RX</sub> = 0 (VRX output floating), R<sub>L</sub> = 600Ω and is computed using the following equation.

G<sub>2.4</sub> = 20 • log (V<sub>TX</sub>/V<sub>TP</sub>) vary amplitude -40dBm to +3dBm, or

$G_{2-4} = 20 \bullet log (V_{TX}/V_{TR})$  vary amplitude -40dBm to +3dBm, or -55dBm to -40dBm and compare to -10dBm reading.

V<sub>TX</sub>, R<sub>L</sub> and V<sub>TR</sub> are defined in Figure 8.

- 23. Four-Wire to Two-Wire Gain Tracking The 4-wire to 2-wire gain tracking is referenced to measurements taken for E<sub>RX</sub> = -10dBm, 1.0kHz signal, E<sub>G</sub> source removed from circuit, R<sub>L</sub> = 600Ω and is computed using the following equation: G<sub>4-2</sub> = 20 log (V<sub>TR</sub>/E<sub>RX</sub>) vary amplitude -40dBm to +3dBm, or -55dBm to -40dBm and compare to -10dBm reading. V<sub>TR</sub>, R<sub>L</sub> and E<sub>RX</sub> are defined in Figure 8. The level is specified at the 4-wire receive port and referenced to a 600Ω impedance level.

- 24. Two-Wire Idle Channel Noise The 2-wire idle channel noise at  $V_{TR}$  is specified with the 2-wire port terminated in  $600\Omega$  ( $R_L$ ) and with the 4-wire receive port (VTX) floating (Reference Figure 9).

- 25. Four-Wire Idle Channel Noise The 4-wire idle channel noise at  $V_{TX}$  is specified with the 2-wire port terminated in  $600\Omega$  (R<sub>L</sub>). The noise specification is with respect to a  $600\Omega$  impedance level at  $V_{TX}$ . The 4-wire receive port (VTX) floating (Reference Figure 9).

- 26. Harmonic Distortion (2-Wire to 4-Wire) The harmonic distortion is measured within the voice band with the following conditions. E<sub>G</sub> = 0dBm at 1kHz, R<sub>L</sub> = 600Ω Measurement taken at V<sub>TX</sub>. (Reference Figure 7).

- 27. Harmonic Distortion (4-Wire to 2-Wire) The harmonic distortion is measured within the voice band with the following conditions. E $_{RX}$  = 0dBm0. Vary frequency between 300Hz and 3.4kHz, R $_{L}$  = 600 $\Omega$ . Measurement taken at V $_{TR}$ . (Reference Figure 8).

- **28. Constant Loop Current -** The constant loop current is calculated using the following equation:

- $I_L = 1000/R_{LIM} = V_{TR}/600$  (Reference Figure 10).

- 29. Ground Key Detector (TRIGGER) Ground the Ring pin through a 2.5kΩ resistor and verify that GKD goes low. (RESET) Disconnect the Ring pin and verify that GKD goes high.

- (Hysteresis) Compare difference between trigger and reset.

- **30. Electrical Test -** Not tested in production at -40°C.

# **Circuit Operation and Design Information**

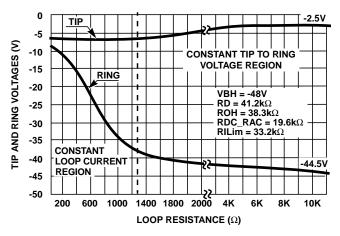

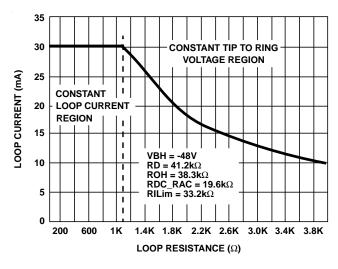

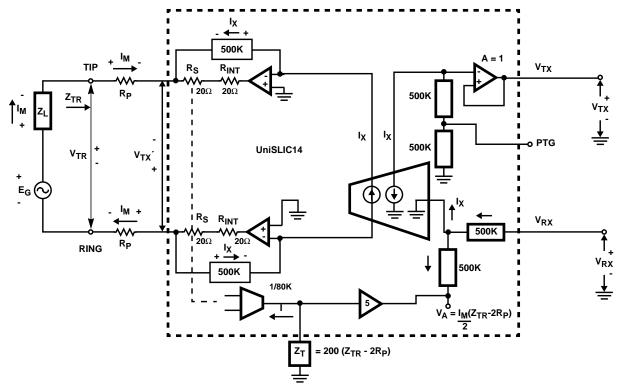

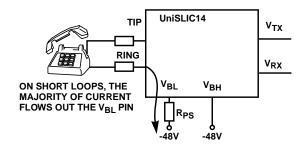

The UniSLIC14 family of SLICs are voltage feed current sense **S**ubscriber **L**ine **I**nterface **C**ircuits (SLIC). For short loop applications, the voltage between the tip and ring terminals varies to maintain a constant loop current. For long loop applications, the voltage between the tip and ring terminals are relatively constant and the loop current varies in proportion to the load.

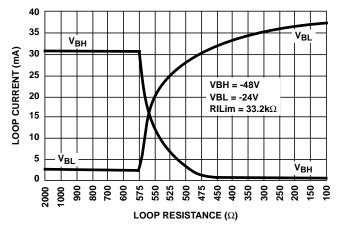

The tip and ring voltages for various loop resistances are shown in Figure 13. The tip voltage remains relatively constant as the ring voltage moves to limit the loop current for short loops.

The loop current for various loop resistances are shown in Figure 14. For short loops, the loop current is limited to the programmed current limit, set by RILIM. For long loop applications, the loop current varies in accordance with Ohms law for the given tip to ring voltage and the loop resistance.

FIGURE 13. TIP AND RING VOLTAGES vs LOOP RESISTANCE

FIGURE 14. LOOP CURRENT vs LOOP RESISTANCE

The following discussion separates the SLIC's operation into its DC and AC paths, then follows up with additional circuit and design information.

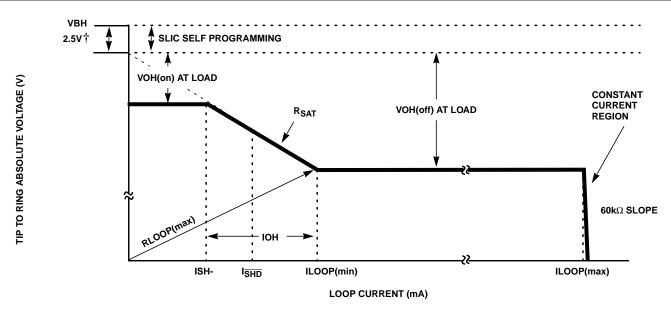

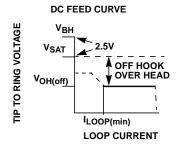

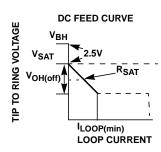

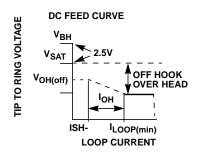

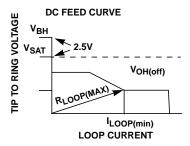

#### DC Feed Curve

The DC feed curve for the UniSLIC14 family is user programmable. The user defines the on hook and off hook overhead voltages (including the overhead voltage for off hook pulse metering if applicable), the maximum and minimum loop current limits, the switch hook detect threshold and the battery voltage. From these requirements, the DC feed curve is customized for optimum operation in any given application. An Excel spread sheet to calculate the external components can be downloaded off our web site www.intersil.com/telecom/unislic14.xls.

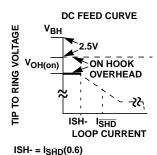

†Internal overhead voltage automatically generated by the SLIC.

FIGURE 15. UniSLIC14 DC FEED CURVE

# On Hook Overhead Voltage

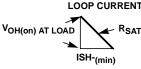

The on hook overhead voltage at the load ( $V_{OH}$ (on) at Load) is independent of the  $V_{BH}$  battery voltage. Once set, the on hook voltage remains constant as the  $V_{BH}$  battery voltage changes. The on hook voltage also remains constant over temperature and line leakages up to 0.6 times the

Switch Hook Detect threshold ( $I_{\overline{SHD}}$ ). The maximum loop current for a constant on hook overhead voltage is defined as ISH-.

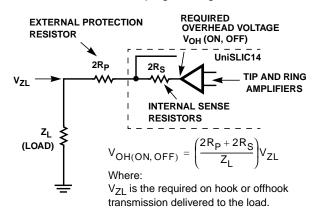

The on hook overhead voltage, required for a given signal level at the load, must take into account the AC voltage drop across the 2 external protection resistors ( $R_P$ ) and the 2 internal sense resistors ( $R_S$ ) as shown in Figure 16. The AC on hook overload voltage is calculated using Equation 1.

$$V_{OH(on) \text{ at Load}} = V_{sp(on)} \times \left(1 + \frac{2R_p + 2R_s}{Z_L}\right) + 1.5V$$

(EQ. 1)

#### where

V<sub>OH(on)</sub> at Load = On hook overhead voltage at load

V<sub>sp(on)</sub> = Required on hook transmission for speech

$R_P = Protection Resistors (Typically 30\Omega)$

$R_S$  = Internal Sense Resistors (40 $\Omega$ )

$Z_{I} = AC$  load impedance for (600 $\Omega$ )

1.5V = Additional on hook overhead voltage requirement

To account for any process and temperature variations in the performance of the SLIC, 1.5V is added to the overhead voltage requirement for the on hook case in Equation 1 and 2.0V for the off hook case in Equation 3. Note the 2.5V overhead is automatically generated in the SLIC and is not part of the external overhead programming.

FIGURE 16. OVERHEAD VOLTAGE OF THE TIP AND RING AMPLIFIERS

# Off Hook Overhead Voltage

The off hook overhead voltage V<sub>OH</sub>(off) at Load is also independent of the V<sub>BH</sub> battery voltage and remains constant over temperature. The required off hook overhead voltage is the sum of the AC and DC voltage drops across the internal sense resistors (R<sub>S)</sub>, the

protection resistors (R<sub>P</sub>), the required (peak) off hook voltage for speech ( $V_{sp(off)}$ ) and the required (peak) off hook voltage for the pulse metering ( $V_{pm(off)}$ ), if applicable.

The off hook overhead voltage is defined in Equation 2 and calculated using Equation 3.

$$V_{OH(off) \text{ at Load}} = V_{OH(Rsense)} + V_{sp(off)} + V_{pm(off)}$$

(EQ. 2)

where:

V<sub>OH(off)</sub> at Load = Off hook overhead voltage at load

$V_{OH}(R_{sense})$  = Required overhead for the DC voltage drop across sense resistors (2R<sub>S</sub> x Iloop<sub>(max)</sub>)

V<sub>sp(off)</sub> = Required (peak) off hook AC voltage for speech

V<sub>pm(off)</sub> = Required (peak) off hook AC voltage for pulse metering

$$\begin{split} V_{OH(off) \text{ at Load}} &= 80 \times I_{LOOP(max)} + V_{sp(off)} \times \left(1 + \frac{2R_p + 2R_S}{Z_L}\right) \\ &+ V_{pm(off)} \times \left(1 + \frac{2R_p + 2R_S}{Z_{pm}}\right) + 2.0V \end{split} \tag{EQ. 3}$$

where:

$80 = 2R_s + 2R_{INT}$  (reference Figure 17)

$Z_{pm}$  = Pulse metering load impedance (typically 200 $\Omega$ ).

2.0V = Additional off hook overhead voltage requirement

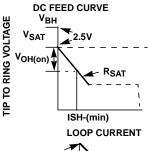

# R<sub>SAT</sub> Resistance Calculation

The  $R_{SAT}$  resistance of the DC feed curve is used to determine the value of the RDC\_RAC resistor (Equation 6). The value of this resistor has an effect on both the on hook and off hook overheads. In most applications the off hook condition will dominate the overhead requirements. Therefore, we'll start by calculating the  $R_{SAT}$  value for the off hook conditions and then verify that the on hook conditions are also satisfied.

I<sub>LOOP(min)</sub>

VOH(off) AT LOAD

When considering the Off hook condition, R<sub>SAT</sub> is equal to V<sub>OH(off)</sub> at Load divided by Iloop<sub>(min)</sub> (Equation 4).

For the given system requirements (recommended application circuit in back of data sheet): Iloop (min) = 20mA, Iloop (max) = 30mA, V<sub>sp(off)</sub> = 3.2V<sub>PEAK</sub>,

$V_{sp(off)} = 3.2V_{PEAK}$ ,  $V_{spm(off)} = 0V_{PEAK}$ ,  $V_{OH(off)}$  at Load = 8.34V the

value of  $R_{SAT(off)}$  is equal to 417 $\Omega$  as calculated in Equation 4.

$$R_{SAT(off)} = \frac{V_{OH(off) \text{ at Load}}}{I_{LOOP(min)}} = \frac{8.34 V}{20 \text{mA}} = 417 \Omega$$

(EQ. 4)

Before using this R<sub>SAT</sub> value, to calculate the RDC\_RAC resistor, we need to verify that the on hook requirements will also be met.

$$R_{SAT(on)} = \frac{2.85V}{7.2mA} = 395\Omega$$

The on hook overhead voltage calculated with the off hook RSAT (RSAT(off)), is given in Equation 5 and equals 3.0V. The on hook overhead calculated with Equation 1 equals 2.85V for the given system requirements (recommended application circuit in back of data sheet): Switch Hook Detect threshold = 12mA, ISH- = (0.6)12mA = 7.2mA, Vsp(on) = 0.775VRMS

Thus, the on hook overhead requirements of 2.85V will be

met if we use the R<sub>SAT(off)</sub> value.

$$V_{OH(on)} = (ISH-)(R_{SAT(off)})$$

(EQ. 5)

$V_{OH(on)} = 7.2 \text{mA} \times 417 \Omega$

$V_{OH(on)} = 3.0 \text{V}$

If the on hook overhead requirement is not met, then we need to use the  $R_{SAT(on)}$  value to determine the RDC\_RAC resistor value. The external saturation guard resistor RDC\_RAC is equal to 50 times  $R_{SAT}$ .

In the example above R<sub>SAT</sub> would equal 417 $\Omega$  and RDC\_RAC would then equal to 20.85k $\Omega$  (closest standard value is 21k $\Omega$ ).

$$RDC_RAC = 50 \times R_{SAT}$$

(EQ. 6)

The Switch Hook Detect threshold current is set by resistor  $R_D$  and is calculated using Equation 7. For the above example  $R_D$  is calculated to be 41.6k $\Omega$  (500/12mA). The next closest standard value is 41.2k $\Omega$ .

$$R_{D} = \frac{500}{I_{SHD}}$$

(EQ. 7)

The true value of ISH-, for the selected value of  $R_{\mbox{\scriptsize D}}$  is given by Equation 8:

ISH- =

$$\frac{500}{R_D}$$

(0.6) (EQ. 8)

For the example above, ISH- equals 7.28mA (500 x 0.6/41.2K). Verify that the value of ISH- is above the suspected line leakage of the application. The UniSLIC family will provide a constant on hook voltage level for leakage currents up to this value of line leakage.

The R<sub>OH</sub> resistor, which is used to set the offhook overhead voltage, is calculated using Equations 9 and 10.

I<sub>OH</sub> is defined as the difference between the I<sub>LOOP(min)</sub> and ISH-. Substituting Equation 8

for ISH- into Equation 9 and solving for  $R_{OH}$  defines  $R_{OH}$  in terms of  $I_{LOOP(min)}$  and  $R_{D\cdot}$

$$R_{OH} = \frac{500}{I_{OH}} = \frac{500}{I_{LOOP(min)} - ISH}$$

(EQ. 9)

Equation 10 can be used to determine the actual ISH- value resulting from the  $R_D$  resistor selected. The value of  $R_D$  should be the next standard value that is  $\underline{lower}$  than that calculated. This will insure meeting the  $I_{LOOP(min)}$  requirement. ROH for the above example equals  $39.1 k\Omega$ .