## **Zero Voltage Switch with Fixed Ramp**

## **Description**

The monolithic integrated bipolar circuit, TEA1024/TEA1124 is a zero voltage switch for triac control in domestic equipments. It offers not only the control of a triac in zero crossing mode but also the possibility of power control. This is why the IC contains a mains

synchronized ramp generator with 640 ms (1280 ms) duration (50 Hz). It is suitable for a typical load of 750 W (1000 W) meeting the Flicker Standard. (values in brackets relate to TEA1124.)

#### **Features**

- Direct supply from the mains

- Definite IC switching characteristics

- Very few external components

- Full wave drive no dc component in the load circuit

- Current consumption ≤ 1.5 mA

- Output short circuit protected

- Simple power control

- Integrated ramp generator

- Reference voltage variable by external resistance

- Pulse position optimization

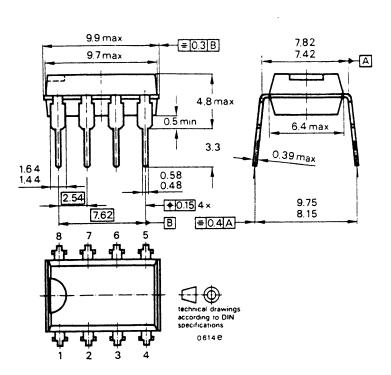

Package: DIP8

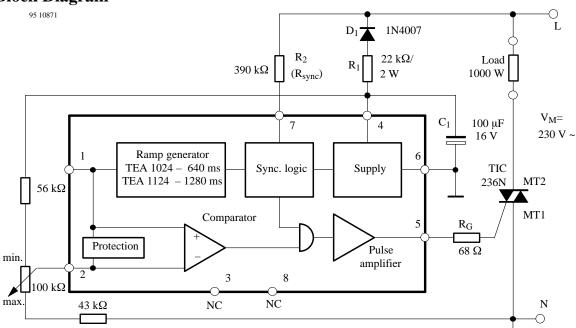

### **Block Diagram**

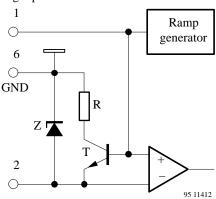

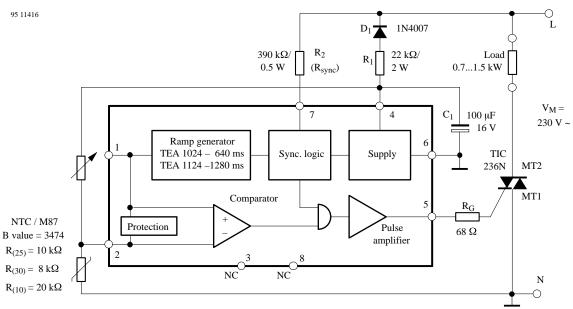

Figure 1. Typical block diagram - open loop power control

## **Power Supply and its Limitations**

The voltage limitation contained in the IC allows it to be powered from mains via series resistance  $R_1$  and rectifying diode  $D_1$  between Pin 6 (+ Pol/ $\perp$ ) and Pin 4 (-V<sub>S</sub>). The capacitor  $C_1$  smooths the supply voltage (see figure 1).

An internal temperature-compensated limiting circuit protects the module from random peaks of voltage on the mains, and delivers a defined reference voltage during the negative half-cycle.

### **Synchronization**

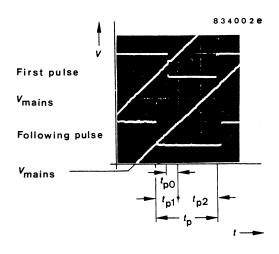

Figure 2. Pulse position optimization

The logic function is synchronized by means of a separate resistance  $R_2$  connected between Pin 7 and phase (voltage-synchronization). The width of the pulse can be varied between wide limits by choice of  $R_{sync}$ . The larger the value chosen, the wider the output pulse is on Pin 5. Automatic optimization of the phase of the pulse is necessary, since the latching current of the triac exceeds the steady current by a factor of 3.

The phase of the pulse is chosen so that ca. 1/3 of the pulse width appears before the transition through null and 2/3 after it (see electrical characteristics and figure 2).

In order to avoid phase-clipping after the switch-on the first third of the first pulse is automatically suppressed.

#### **Full-Wave Logic**

The full-wave logic ensures that only pairs of pulses can be released, and that these always begin with the positive dv/dt. The load is thus switched on for a minimum of one complete mains cycle. This means that the triac receives a minimum of two driving pulses, so that the unwanted d.c. component in the load circuit is definitely eliminated.

### **Pulse Amplifier**

The pulse amplifier connected to the output of the full-wave logic circuit, is proof against continuos short-circuits, and delivers negative output pulses of typ. 75 mA, via an integrated limiting resistance, to Pin 5.

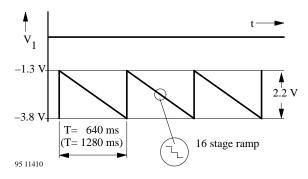

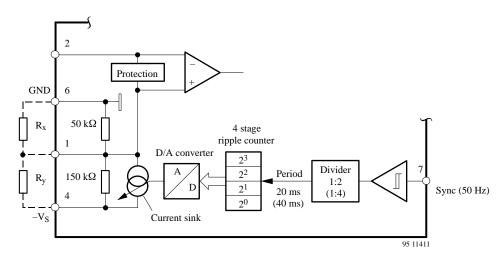

## Ramp Generator (Figures 3, 4)

Ramp voltage which is generated in the IC is available not only at reference Pin 1, but also at the non-inverted input of the comparator.

The current sink which is controlled by D/A converter influences the internal reference voltage at Pin 1 specified by voltage divider. The current sink is turned-off in the reset state of the D/A converter so that the voltage at Pin 1 is primarily specified via the internal voltage divider (ramp starting voltage).

In the maximum state of the 4 stage (5 stage – TEA1124) D/A converter, the current sink overtakes the maximum current, whereby the ramp's final (end) voltage has reached. External resistance  $R_x$ ,  $R_y$  shown in figure 4 are in position to influence the initial ramp voltage as well as the ramp amplitude. If the external resistances ratio  $R_x$ ,  $R_y$  is the same as that of the internal ratio, the ramp voltage at the beginning remains maintained (constant), only the amplitude is compressed.

Figure 3. Ramp diagram without external circuit

Figure 4. Principle diagram - Generation and evaluation of ramp

#### **Period**

- 1. The time required for one complete cycle of a regular. repeating signal, function, or series of emends.

- The tune between two consecutive transients of the pointer or indicating means of an electrical indicating instrument in the same disdain the rest position. Something called periodic fine.

## **Comparator**

The comparison of set value and measured value is carried out via the two comparator inputs Pin 1 and Pin 2. Here Pin 2 is the inverting input and has a circuit protecting it against interference spikes. Figure 5 shows the protective circuit of the comparator. Pin 1 is the non-inverting input.

Figure 5. Protective circuit of the comparator

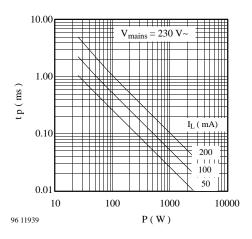

## Firing Pulse Width (Figures 6, 7)

It depends on the latching current as well as on the load current of the used triacs.

$$t_p[s] = \frac{3}{4 \pi f} \arcsin \frac{I_L \times V_M}{P \times \sqrt{2}}$$

whereas  $I_L[A] = Latching$  current of the triac

V<sub>M</sub>[V]= Mains voltage, effective

P[W] = Power load

f[1/s] = Mains frequency

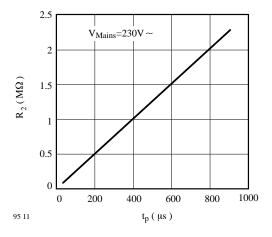

Firing pulse width is specified through the zero cross over identification which can be influenced by the sync. resistance.

$$R_{sync} \ [\Omega] = \frac{V_{M} \sqrt{2} \ sin \left(\frac{2}{3} \times \omega \times t_{p}\right) - 0.6}{2.5 \ \times 10^{-5}} - 1.4 \ \times 10^{3}$$

where

$t_p[s]$  = required ignition pulse width

Figure 6.

Figure 7.

## **Ignition (Firing) Current**

The necessary ignition current depends on the specified triac. With the help of a resistance, it is possible to limit its value:

$$R_{Gmax}[\Omega] \approx \frac{5.7 \ V - V_{Gmax}}{I_{Gmax}} - 25 \ \Omega$$

$$I_{p}[A] = \frac{I_{Gmax}}{T} \times t_{p}$$

whereas  $V_G[V]$ = Gate voltage of the triac

$I_G[A] = Max$ . gate current

$I_P[A]$  = Average gate current requirement

$t_P[s] = Ignition pulse width$

T[s] = Duration (of mains frequency)

## **Supply Voltage**

Due to higher trigger sensitivity of the triac it is supplied with negative signal. It can be supplied via diode and series resistance from the negative half wave of the mains. An internal parallel controller limits the voltage between Pin 5 and 7 to a typical value of 6.55 V.

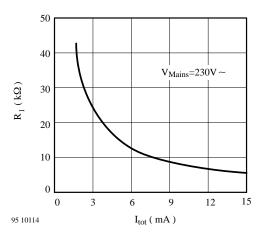

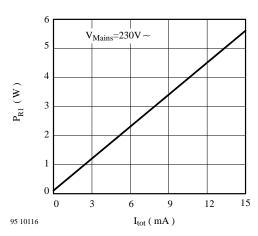

## **Dimensioning of the Series Resistance** $R_1$ (Figures 8, 9)

$$R_{1max} = 0.85 \ \frac{V_{Mmin} - V_{Smax}}{2 \ I_{tot}} \ -65 \ \Omega$$

$$I_{tot} = I_S + I_P + I_X$$

$P(R_1) = \frac{(V_M - V_S)^2}{2 R_1}$

$egin{array}{ll} V_M &= \mbox{Mains supply} \\ V_S &= \mbox{Limiting voltage of the IC} \end{array}$

= Total current requirement

= Current requirement for external circuit

Figure 8.

Figure 9.

# **TEA1024/TEA1124**

## **Absolute Maximum Ratings**

Reference point Pin 6

| Parameters                                                         |                    | Symbol                                        | Value                     | Unit |

|--------------------------------------------------------------------|--------------------|-----------------------------------------------|---------------------------|------|

| Current consumption $t \le 10 \mu s$                               | Pin 4              | $-I_S$ $i_S$                                  | 30<br>150                 | mA   |

| Sync. current $t \le 10 \mu s$                                     | Pin 7              | I <sub>Sync</sub> i <sub>Sync</sub>           | 5<br>40                   | mA   |

| Comparator input current                                           | Pin 2              | $\pm I_{\rm I}$                               | 1                         | mA   |

| Input voltages                                                     | Pin 1,4,5<br>Pin 5 | $\begin{array}{c c} -V_I \\ +V_I \end{array}$ | ≤ V <sub>S</sub><br>≤ 0.5 | V    |

| Power dissipation $T_{amb} = 45^{\circ}C$ $T_{amb} = 100^{\circ}C$ |                    | P <sub>tot</sub>                              | 400<br>125                | mW   |

| Junction temperature                                               |                    | Ti                                            | 125                       | °C   |

| Ambient temperature range                                          |                    | T <sub>amb</sub>                              | 0 to 100                  | °C   |

| Storage temperature range                                          |                    | T <sub>stg</sub>                              | -40 to + 125              | °C   |

#### **Thermal Resistance**

| Parameters       | Symbol            | Maximum | Unit |

|------------------|-------------------|---------|------|

| Junction ambient | R <sub>thJA</sub> | 200     | K/W  |

## **Electrical Characteristics**

Supply voltage  $-V_S = 5.6 \text{ V}$ ,  $T_{amb} = 25^{\circ}\text{C}$ , f = 50 Hz, reference point Pin 6, unless otherwise specified

| Parameters                | Test Condition                      | ıs / Pins      | Symbol                             | Min  | Тур                   | Max      | Unit |

|---------------------------|-------------------------------------|----------------|------------------------------------|------|-----------------------|----------|------|

| Supply voltage limitation | $-I_4 = 1 \text{ mA}$               | Pin 4          | $-V_S$                             | 5.7  |                       | 7.4      | V    |

| Current consumption       | Pos. half, cycle<br>Zero cross over | Pin 4          | $-I_S$                             |      |                       | 1        | mA   |

|                           | (Pin 5 open)<br>neg. half cycle     | Pin 4<br>Pin 4 | -I <sub>S</sub><br>-I <sub>S</sub> |      |                       | 1<br>1.8 |      |

| Synchronization           |                                     | Pin 7          |                                    |      |                       |          |      |

| Voltage limitation        | $\pm I_7 = 1 \text{ mA}$            |                | $\pm V_{I}$                        | 1.0  |                       | 1.8      | V    |

| Synchronization current   |                                     |                | ± I <sub>Sync</sub>                | 0.15 |                       |          | mA   |

| Zero cross detection      |                                     |                | $\pm I_{Sync}$                     |      | 25                    |          | μΑ   |

| Comparator, figure 5      |                                     |                |                                    |      |                       |          |      |

| Input zero voltage        |                                     | Pin 1, 2       | $V_{10}$                           |      | 10                    |          | mV   |

| Input quiescent current   |                                     | Pin 2          | $I_{B}$                            |      |                       | 1        | μΑ   |

| Common mode input range   |                                     | Pin 1, 2       | -V <sub>IC</sub>                   | 1    | (V <sub>S</sub> -1.6) |          | V    |

| Parameters                                    | Test Conditions / Pins                                              | Symbol                                             | Min | Тур                                        | Max | Unit |  |

|-----------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|-----|--------------------------------------------|-----|------|--|

| Ramp generator, figures 3, 4 Pin 1            |                                                                     |                                                    |     |                                            |     |      |  |

| Period                                        | TEA1024                                                             | T                                                  |     | 640                                        |     | ms   |  |

|                                               | TEA1124                                                             |                                                    |     | 1280                                       |     |      |  |

| Step number                                   |                                                                     | n                                                  |     | 16                                         |     |      |  |

| Initial voltage                               |                                                                     | $-V_1$                                             | 1.2 | 1.4                                        | 1.6 | V    |  |

| Final voltage                                 |                                                                     | $-V_1$                                             | 3.3 | 3.6                                        | 3.9 | V    |  |

| Internal reference                            |                                                                     |                                                    |     | $\left(\frac{V_s + 2.5\%}{4-7.5\%}\right)$ |     | V    |  |

| Temperature coefficient of internal reference |                                                                     | ±TC <sub>Ref</sub>                                 |     | 1.2                                        |     | mV/K |  |

| Pulse amplifier Pin 5                         |                                                                     |                                                    |     |                                            |     |      |  |

| Output pulse current                          | $V_G \le 1.5 \text{ V}$                                             | -I <sub>O</sub>                                    | 50  |                                            | 100 | mA   |  |

| Output pulse width                            | $V_{\text{Sync}} = 230 \text{ V} \sim,$ $R_2 = 220 \text{ k}\Omega$ | t <sub>0</sub><br>t <sub>1</sub><br>t <sub>2</sub> |     | 33<br>65<br>110                            |     | μs   |  |

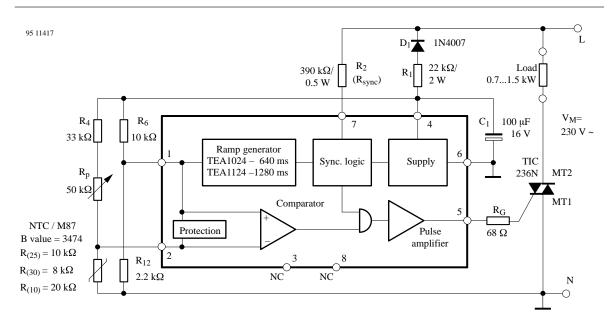

## **Applications**

Figure 10. Simple temperature regulation with maximum proportional range

# **TEA1024/TEA1124**

Figure 11. Temperature regulation with proportional range, 10 to 30  $^{\circ}$ C/ 640 ms ramp cycle

#### **Dimensions in mm**

Package: DIP8

## **TEA1024/TEA1124**

### **Ozone Depleting Substances Policy Statement**

It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423