# Chip Card & Security ICs

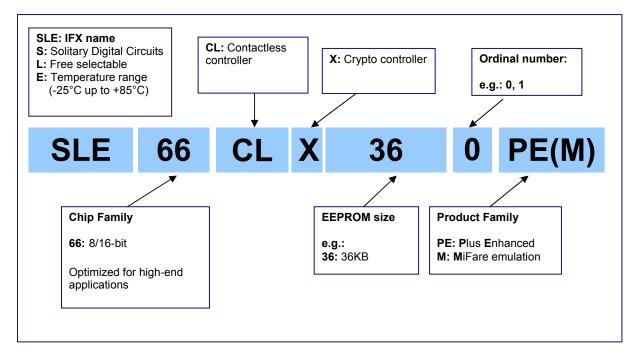

# SLE 66CLX360PE(M) Family

8/16-Bit High Security Dual Interface Controller For Contact based and Contactless Applications

# ISO/IEC 7816 and 14443 Type B & A Compliant Interfaces Contactless interface acc. ISO/IEC 18092 passive mode (SONY FeliCa® communication interface)

with Linear Addressing Instruction Set For Large Memories Optional MiFare® Classic 1K Emulation in 0.22 µm CMOS Technology

240-Kbyte User ROM, 7100-byte RAM, 36-Kbyte EEPROM

1100-Bit Advanced Crypto Engine supporting RSA and Elliptic Curve GF(p) certified RSA 2048-bit library available

112-Bit Dual Key DES Accelerator supporting DES, 3DES Algorithms

Preliminary Short Product Information

November 2006

#### Preliminary SLE 66CLX360PE(M) Family Short Product Information

Ref.: SPI\_SLE66CLX360PE\_091106.doc

This document contains preliminary information on a new product under development. Details are subject to change without notice.

#### Revision History: Current Version: 2006-11-09

Previous Releases:

| Page | Subjects (changes since last revision) |  |  |

|------|----------------------------------------|--|--|

|      |                                        |  |  |

|      |                                        |  |  |

|      |                                        |  |  |

|      |                                        |  |  |

|      |                                        |  |  |

#### Important: Further information is confidential and on request. Please contact: Infineon Technologies AG in Munich, Germany, Chip Card & Security ICs security.chipcard.ics@infineon.com

Published by Infineon Technologies AG, AIM CC 81726 Munich, Germany © Infineon Technologies AG 2006 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives world-wide (see address list). PayPass® is a registered trademark of MasterCard.

Visa® is a registered trademark of Visa USA Inc.

FeliCa® is a registered trademark of Sony Corp.

MIFARE® is a registered trademark of Philips Electronics N.V.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

8/16-Bit High Security Dual Interface Controller in 0.22 μm CMOS Technology for Contact and Contactless Operation with ISO/IEC 7816 and 14443 Type B & A Compliant Interfaces Contactless interface acc. ISO/IEC 18092 passive mode (SONY FeliCa® communication interface)

with MMU and Linear Addressing Instruction Set For Large Memories and optional MiFare® Classic 1K Emulation 240-Kbyte User ROM, 7100-byte RAM, 36-Kbyte EEPROM 1100-Bit Advanced Crypto Engine supporting RSA and Elliptic Curve GF (p) and 112-Bit Dual Key DES Accelerator supporting DES, 3DES algorithm

### **General Features**

- Enhanced low power non-standard architecture 8051 CPU with extended addressing modes for dual interface smart card and contactless applications

- Instruction set opcode compatible with standard 8051 processor with additional powerful instructions optimized for smart card application

- Execution time at least 6 times faster than standard 8051 processor at same external clock

- Additional enhanced instructions for direct physical memory access of >64-Kbyte

- Typically saves up to 90 % code space and increases execution speed up to 80%

- 240-Kbyte User ROM for operating system and application (programs & data)

- 256 bytes reserved ROM for Resource Management System (RMS) with Contactless optimized EEPROM write/erase routines

- 36-Kbyte Secure EEPROM in MicroSlim technology for application program and data

- MiFare® Classic 1-Kbyte Emulation (optional)

- 4-Kbyte reserved in User ROM

- 1-Kbyte additional EEPROM protected by RMS Firewall

- 6-Kbyte XRAM, 700-byte Crypto-RAM and 256-byte internal RAM for fast data processing

- Enhanced <u>Memory Management Unit with</u> application and user defined segment

- EEPROM voltage generated on chip

- Certified True Random Number Generator with firmware test function supporting AIS-31 requirements

- Dual Key Triple DES (DDES) Accelerator

- <u>A</u>dvanced <u>C</u>rypto <u>E</u>ngine with support of:

- Up to 1100-bit RSA calculation in Hardware

- Up to 2048-bit RSA calculation via fast and secure RSA 2048 crypto library (CC EAL5+ already certified with SLE66CX360PE)

- Elliptic Curves over GF(p)

- CC EAL5+ Certification planned according to BSI–PP-0002

- CRC Module according to ISO/IEC 3309 supporting CCIT V.41 & HDLC X25 with configurable initial values

- 16 Interrupt Vectors Module with 3 priority levels to ensure real time operation

- Internal clock controlled by PLL: up to 30MHz asynchronous clock frequency (optional use)

- Adjustable internal frequency according to available power or required performance

- Increased internal frequency for maximum performance

- Internal frequency adjusted to guarantee a given limited power consumption

- Two 16-bit Auto-reload Timers with interrupt capability for protocols, security checks & watch dog implementations

- Power saving sleep and clock stop modes

- Temperature range: contact-based: -25°C to +85°C contact-less: -25°C to +70°C

Short Product Information

Full operation either via Contact-based and/or Contactless interfaces controlled by Operating System enhances Security Level

#### **Contact-based Interface**

- Contact configuration and serial interface according to ISO/IEC 7816

- UART handling serial interface compliant with ISO/IEC 7816 supporting transmission protocols T=0/1 and up to Division Factor 8

- Supply voltage range: 5V ± 10% (Class A) 3V ± 10% (Class B) 1.8V ± 10% (Class C) (on request)

- Current consumption < 10 mA @ 5.5 V

- External CPU clock frequency: 1 to 7.5 MHz

- Internal CPU clock frequency: up to 30 MHz

- ESD protection larger than 6 kV

#### **Contactless Interface**

- Interface according to ISO/IEC 14443 for both Type A and Type B

- Interface according to ISO/IEC 18092 passive mode Interface (SONY FeliCa®)

- Carrier frequency 13.56 MHz

- Data rate in both directions up to 848 Kbit/s in type B operation up to 848 Kbit/s in type A operation up to 424Kbit/s in FeliCa® operation

- Anticollision & Transmission Protocol supported by open source application notes for both Type B & A

- Optional MiFare® Classic 1K Emulation supported by RMS functions

- Flexible Internal CPU clock frequency: fully configurable from 1.7MHz up to 30 MHz

- 256 bytes buffer for contactless data exchange (FiFo circular architecture)

- Parallel operation of CPU, Peripherals like DES, CRC and Contactless Interface for high demanding applications.

#### **MiFare® Classic Emulation**

- MiFare® Classic 1-Kbyte Memory Emulation

- MiFare® Classic operation controlled by RMS functions: same functionality and command set as given by the MiFare® Classic Chip

- Unique Identification number for MiFare®

- Personalisation of MiFare® Classic Memory also possible in Contact based only mode secured by RMS functions and passwords

## E<sup>2</sup>PROM Technology

- Byte wise EEPROM programming and read accesses

- Flexible page mode for 1 to 64 bytes write/erase operation

- 32 bytes security area including:

- 16 bytes chip unique identification number

- 16 bytes PROM area (OTP like)

- Fast personalisation mode ≤1.0 ms

- Typical Page Programming time of 2.2ms

- Enhanced ECC Module controlled by Operating System

- Platform prepared for flash-like erasing of up to 2-Kbyte EEPROM-segments

- Minimum of 500.000 Write/erase cycles @25°C per page

- Data retention for a minimum of 25 years @25°C

- EEPROM programming voltage generated on chip

### Memory Management and Protection Unit

- Addressable memory up to 16 Mbytes

- Separates OS (system mode) and Application (application mode) by usage of descriptors

- Enhanced multi-application support by 16 descriptors

- Separates optional MiFare® Classic 1Kbyte Emulation Memory from rest of EEPROM

- System routines called by interrupts

- Access Restrictions to peripherals in application mode controlled by OS

- Code execution from XRAM possible

## **Security Features**

#### **Operation state mechanism**

- Low and high voltage sensors

- Internal voltage sensor

- Frequency sensors and filters

- Light sensor

- Glitch sensors

- Temperature sensor

- Life Test function for sensors

- Internal power-on reset sensor

- Active Shield with automatic and user controlled attack detection

# Secure chip and firmware design

- Sparkling SFR encryption for DDES, ACE, RNG and CRC modules

- Security scrambled, dual rail pre-charge logic design & optimized chip layout against physical chip manipulation

- Bus Confusion

- Immediate internal RAM erase upon security reset detection

- Security Reset

- ROM code not visible due to implantation

- Mask dependant ROM code encrypted during production

- Chip unique encryption of the XRAM and EEPROM

- Flexible encryption of part or whole EEPROM by additional user-defined key

- Memory encryption/decryption module (MED) for XRAM, ROM and EEPROM against reverse engineering and power attacks

- 16 byte Unique Chip IDentification number for anti-clone countermeasure & secure tracking

- 16 bytes security PROM hardware protected (OTP like)

- Secure start of the operating system ensured by certified <u>Self Test Software (STS)</u>

- Certified EEPROM programming routines (RMS)

- Enhanced Error Correction Unit (ECU)

- Certified True Random Number Generator including firmware test function supporting AIS-31 requirements.

- High Speed SPA/DPA resistant <u>D</u>ual Key <u>DES</u> (DDES) Accelerator and <u>A</u>dvanced <u>C</u>rypto <u>E</u>ngine (ACE)

## Anti Snooping

- Automatic randomization and smoothing of power profile

- Non standard dedicated Smart Card CPU Core

- HW-countermeasures against SEMA/DEMA, SPA/DPA, DFA and Timing Attacks

- Active Shield with automatic and user controlled attack detection

#### **Targeted Evaluation**

- CC EAL5+

- Visa Level 3

- CAST

- EMVCo

### **Supported Standards**

- ISO/IEC 7816

- EMV 2000

- MasterCard PayPass® M/Stripe and M/Chip

- Visa Wave® and MSD

- GSM 11.1x

- ETSI TS 102 221

- ISO/IEC 14443

- ISO/IEC 18092 (passive mode)

- ISO/IEC 3309

- CCIT v.41

- HDLC X25

## **Application Support**

- HW-& SW-Tools (Emulator, ROM Monitor, Simulator, Evaluation Kit Proximity (Contactless Reader package), SmartMask™ package, Simulated Reader Software, etc.)

- Open Source Application Notes Tutorial (e.g.: T=0, T=1, DES and 3DES, Crypto Library, Anticollision and Contactless Transmission Protocols for both Type B and A, Card Coil Design Guide, Card Coil Antenna Reference Design List, etc.)

- Certified CC EAL5+ Crypto Library

- Worldwide Application Engineer Team and customer dedicated Field Application Engineers

- Dedicated Team for Contactless Design-in support and Analysis

- Regular Customer trainings on Cryptography, Contactless and Dual interface controllers including ISO/IEC 14443 related topics

- On-site trainings available on request

#### **Document References**

- Confidential Data Book SLE 66CL(X)xxxPE(M)

- Confidential Instruction Set SLE 66CxxxPE(M)

- Confidential Quick Reference SLE 66CxxxPE(M)

- Chip Qualification report

- Chip delivery specification for wafer with chiplayout (die size, orientation, ...)

- Module specification containing description of package, etc.

- Module Qualification report

#### **Development Tools Overview**

- Straight forward migration of existing tool chain for 66P towards 66PE family by firmware update

- Software Development Kit SDK CC

- ROM Monitor RM66P/PE-II with stand alone functionality for ROM mask qualification in the end user system

- Emulator ET66P/PE Hitex or ET66P/PE KSC

- Smart Mask<sup>™</sup> Package for chip evaluation

- Smart Mask<sup>™</sup> Dual Interface modules M8.4 (supplied by Infineon) supporting both ISO/IEC 14443 Type B & A and ISO/IEC 7816 for implantation process testing and production setup

- Evaluation Kit Proximity (Contactless reader package)

- Reader Optimization Kit

# **Cryptographic Timing Performances**

Timing performances are independent of the contact or contactless interface.

| Operation                                                         | Modulus     | Exponent    | Calculation<br>Time at<br>5 MHz | Calculation<br>Time at<br>15 MHz | Calculation<br>Time at<br>30 MHz |

|-------------------------------------------------------------------|-------------|-------------|---------------------------------|----------------------------------|----------------------------------|

| Modular Exponentiation                                            | 1024 bit    | 17 bit      | 20 ms                           | 7 ms                             | 3 ms                             |

| RSA Encrypt / RSA<br>Signature Verify                             | 2048 bit    | 17 bit      | 630 ms                          | 210 ms                           | 105 ms                           |

| Modular Exponentiation<br>RSA Decrypt / RSA<br>Signature Generate | 1024 bit    | 1024 bit    | 820 ms                          | 273 ms                           | 136 ms                           |

| Modular Exponentiation                                            | eq.1024 bit | eq.1024 bit | 250 ms                          | 83 ms                            | 41 ms                            |

| using CRT<br>RSA Decrypt / RSA<br>Signature Generate              | eq.2048 bit | eq.1024 bit | 1840 ms                         | 614 ms                           | 307 ms                           |

| DSA Signature Generate                                            | 512 bit     | 160 bit     | 97 ms                           | 32 ms                            | 16 ms                            |

| DSA Signature Verify                                              | 512 bit     | 160 bit     | 117 ms                          | 39 ms                            | 19 ms                            |

| DSA Signature Generate                                            | 1024 bit    | 160 bit     | 438 ms                          | 146 ms                           | 73 ms                            |

| DSA Signature Verify                                              | 1024 bit    | 160 bit     | 711 ms                          | 237 ms                           | 118 ms                           |

Performance Advanced Crypto Engine<sup>1</sup> Table 1

| Operation                                                                            | Data Block<br>Length | Encryption Time for an<br>8-byte Block including Data Transfer |        |       |  |

|--------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|--------|-------|--|

|                                                                                      |                      | 5 MHz                                                          | 15 MHz | 30MHz |  |

| High Speed and Secure<br>56-bit Single DES Encryption<br>(incl. key loading)         | 64 bit               | 37 µs                                                          | 12 µs  | 6 µs  |  |

| High Speed and Secure<br>56-bit Single DES Encryption                                | 64 bit               | 23 µs                                                          | 8 µs   | 4 µs  |  |

| High Speed and Secure<br>112-bit <b>Triple DES Encryption</b><br>(incl. key loading) | 64 bit               | 60 µs                                                          | 20 µs  | 10 µs |  |

| High Speed and Secure<br>112-bit Triple DES Encryption                               | 64 bit               | 35 µs                                                          | 12 µs  | 6 µs  |  |

Performance DDES Accelerator<sup>2</sup> Table 2

<sup>&</sup>lt;sup>1</sup> Preliminary values based on internal test results <sup>2</sup> Preliminary values based on internal test results

# **Ordering Information**

| Туре                     | Package           | Voltage<br>Range | Temperature<br>Range | Frequency<br>Range <sup>1</sup><br>(external<br>clock CB) | Frequency<br>Range<br>(internal<br>clock) |

|--------------------------|-------------------|------------------|----------------------|-----------------------------------------------------------|-------------------------------------------|

| SLE 66CLX360PE(M) – MCC8 | MCC8 <sup>2</sup> | 1.62 V           | – 25°C               | 1 MHz                                                     |                                           |

| SLE 66CLX360PE(M) – M8.4 | M8.4 <sup>3</sup> | to               | to                   | to                                                        | Up to 30MHz                               |

| SLE 66CLX360PE(M) – C    | Chip              | 5.5 V            | + 85°C               | 7.5 MHz                                                   |                                           |

Package Product Information<sup>4</sup> Table 3

**Short Product Information** www.infineon.com/security

<sup>&</sup>lt;sup>1</sup> External Contactless clock range according to ISO/IEC14443

<sup>2</sup> Pure Contactless Module (MCC8): for standard thickness inlays (330µm)

<sup>3</sup> Dual Interface Module (M8.4)

<sup>4</sup> Ordering Codes are available on request

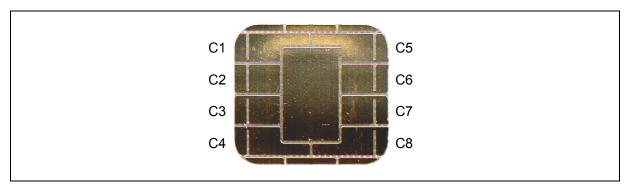

# **Pin Description and Pad Configuration**

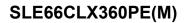

Figure 1 M8.4 Pin Configuration Wire-bonded Module (top view)

#### Figure 2 Pad Configuration (die)

| Symbol | Function                              |

|--------|---------------------------------------|

| VDD    | Supply voltage                        |

| RST    | Reset input                           |

| CLK    | Processor clock input                 |

| GND    | Ground                                |

| I/O    | Bi-directional data port              |

| LA     | Coil connection pin LA                |

| LB     | Coil connection pin LB                |

|        | VDD<br>RST<br>CLK<br>GND<br>I/O<br>LA |

Table 4

Pin Definitions and Functions

#### Short Product Information www.infineon.com/security

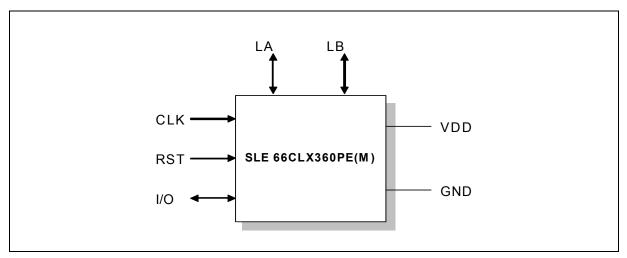

**Block Diagram Description**

Figure 3 Block Diagram of SLE 66CLX360PE(M)

Short Product Information www.infineon.com/security 10 / 14

11.2006

**Product Family Members**

| _               |                          |                                                | ROM (user  |      | Algorithms         |

|-----------------|--------------------------|------------------------------------------------|------------|------|--------------------|

| Product         | EEPROM                   | Available interfaces                           | available) | XRAM | supported          |

| SLE 66CL41PE    | 4k                       | ISO 14443 B&A                                  | 92k        | 2k   | DDES               |

|                 |                          |                                                |            |      |                    |

| SLE 66CL80PE    | 8k                       | ISO 14443 B&A, ISO 7816                        | 92k        |      | DDES               |

| SLE 66CL80PEM   | 8k + 1k Mifare data (*)  | ISO 14443 B&A, ISO 7816, MiFare Classic        | 88k        |      | DDES               |

| SLE 66CL80PES   | 8k                       | ISO 7816, ISO 14443 B&A, ISO18092 passive mode | 92k        | 2k   | DDES               |

|                 |                          |                                                |            |      |                    |

| SLE 66CL81PE    | 8k                       | ISO14443 B&A                                   | 92k        | 2k   | DDES               |

| SLE 66CL81PEM   | 8k + 1k Mifare data (*)  | ISO 14443 B&A, MiFare Classic                  | 88k        | 2k   | DDES               |

|                 |                          |                                                | -          |      |                    |

| SLE 66CL180PE   | 18k                      | ISO 14443 B&A, ISO 7816                        | 92k        |      | DDES               |

| SLE 66CL180PEM  | 16k + 1k Mifare data (*) | ISO 14443 B&A, ISO 7816, MiFare Classic        | 88k        | 2k   | DDES               |

| SLE 66CL180PES  | 18k                      | ISO 14443 B&A, ISO 7816, ISO18092 passive mode | 92k        | 2k   | DDES               |

|                 |                          |                                                | _          |      |                    |

| SLE 66CLX360PE  | 36k                      | ISO 14443 B&A, ISO 7816                        | 240k       |      | DES, RSA, EC GF(p) |

| SLE 66CLX360PEM | 36k + 1k Mifare data (*) | ISO 14443 B&A, ISO 7816, MiFare Classic        | 236k       |      | DES, RSA, EC GF(p) |

| SLE 66CLX360PES | 36k                      | ISO 14443 B&A, ISO 7816, ISO18092 passive mode | 240        | 6k   | DES, RSA, EC GF(p) |

|                 | 1                        |                                                |            |      |                    |

| SLE 66CLX800PE  | 80k                      | ISO 14443 B&A, ISO 7816                        | 240k       |      | DES, RSA, EC GF(p) |

| SLE 66CLX800PEM |                          | ISO 14443 B&A, ISO 7816, MiFare Classic        | 236k       |      | DES, RSA, EC GF(p) |

| SLE 66CLX800PES | 80k                      | ISO 14443 B&A, ISO 7816, ISO18092 passive mode | 240k       | 6k   | DES, RSA, EC GF(p) |

SLE 66CLX800PES

80k

Table 5 Product Family Table Selector

Short Product Information www.infineon.com/security 11 / 14

11.2006

#### **General Description**

The dual interface security controllers SLE 66CLX360PE(M) belong to the family of the Infineon Technologies SLE 66CxxxPE high-end security controller family in 0.22 µm CMOS technology which are designed for contactless security systems that requires continuous ongoing improvements with the highest degree of protection against fraudulent attacks.

SLE 66CLX360PE(M) is targeting dual interface and pure contactless smart card applications such as national electronic passports, ID cards, banking, security access, digital signature, SIM cards with embedded contactless interface and transport.

SLE 66CLX360PE(M) offers 240 Kbytes of User-ROM, 256 bytes internal RAM, 6 Kbytes XRAM, 700 bytes Crypto RAM and 36 Kbytes EEPROM, which can be used as data and as program memory. The non-volatile memory consists of high reliability cells to guarantee data integrity. This is especially important when the EEPROM is used as program memory.

It features ISO/IEC 14443 Type B contactless interfaces and Type A including MiFare® Classic as well as an ISO/IEC 7816 contact-based interface on a single chip that can be operated in parallel to answer the need of the upcoming mobile phones with a contactless interface. They also support symmetric and asymmetric public-key algorithms such like DES, 3DES, Elliptic Curves and RSA independently of the communication mode.

The CPU provides the high efficiency of the 8051 instruction set extended by additional powerful instructions with enhanced performance, memory sizes and security features tailored for contact and contactless smart card applications. Using the embedded PLL, the internal clock is adjustable up to 30 MHz independent from the carrier frequency of the magnetic field supplied by the contactless terminal.

The Memory Management Unit allows a secure separation of the operating system and the applications. Using the system/application mode, it allows to securely downloading applications in the field after card personalisation. Using the MMU transparent mode allows keeping the memory mapping for code compatibility to previous 66P Infineon security controller family member. These new features suit the requirements of the new generation of operating systems.

The UART supports the half-duplex transmission protocols T=0 and T=1 according to ISO/IEC 7816-3. All relevant transmission parameters can be adjusted by software, as e.g. the clock division factor, direct/inverse convention and the number of stop bits. To minimize the overall power consumption, the smart card controller can be set into sleep mode supporting clock stop mode.

Timers ease the implementation of advanced communication protocols such as T=CL (according to ISO/IEC 14443-4) and all other time critical processes for contactless communications. Both Timers features auto-reload mechanisms as well as their own dedicated interrupt vectors. Additional interrupts capability of the RF interface module allows real time operation of the pure contactless smart card with the contactless terminals.

**SLE 66CLX360PE(M) is able to communicate with** any Proximity Card Device (PCD) defined in ISO/IEC 14443 such as the Infineon Evaluation Kit Proximity. The power supply and data are received by an antenna, which consists of a coil with a few turns directly connected to the IC. DES acceleration by a factor of more than 500 compared to software solutions in combination with the **high data transfer rate up to 848 Kbit/s keep the transaction times short. For more independence and flexibility, the controller offers the two modulation type B and type A according ISO/IEC 14443.**

The Anticollision and Contactless Transmission Protocol are supported by open source application notes for both Type B and A in order to offer a maximum flexibility to the Operating System. Both Contactless Communication protocol may be implemented in the Operating System while the final selection of the Type B or A is based upon the personalisation data of the contactless smart card. The communication type can also be changed during runtime in the field. Thus, SLE 66CLX360PE(M) ensures a simplified handling of the ROM mask, high reactivity by a tailored personalisation during production of the contactless smart card in order to answer to the increasing market demand and applications.

The MiFare® Classic emulation enables each family member to be used in the already existing MiFare® infrastructure without further updates.

SLE 66CLX360PE(M) features a **new Resource Management System** (RMS\_E) which **optimizes Contactless EEPROM write/erase routines**. EEPROM programming is enhanced over the entire communication distance compared to the standard RMS. Thus, the reduction of programming times and power consumption is ensured independently of the use of the contact or the contactless interface.

The **CRC module** allows the easy generation of checksums according to ISO/IEC 3309 (16-Bit-CRC), thus it **supports the two different CRC calculation required for ISO/IEC 14443 Type B and Type A**. It **additionally features an configurable initial value to avoid checksum computation re-starting from zero** in the case interrupts requiring use of the CRC module are triggered. Therefore, data as well as program located in the EEPROM can be extra-secured by a CRC checksum enabling the Operating System to detect errors while downloading new application in the field.

To minimize the overall power consumption, the pure contactless smart card controller can be set into sleep mode.

The certified random number generator (RNG) is able to supply the CPU with true random numbers on all conditions. It allows creating session key used for authentication in open networks and enable secure downloading of new applications.

The **DDES module** supports symmetrical crypto algorithms according to the Data Encryption Standard in the Electronic Code Book Mode. It features two internal registers for storage of the two keys required for a Triple DES computation. Together with the fast contactless interface, it **offers high security and high speed for dual interface smart card applications**.

The Advanced Crypto Engine (ACE) is equipped with its own RAM of 700 bytes and supports all of today known public-key algorithms based on large integer modular arithmetic. It allows fast and efficient calculation of e.g. RSA operations with key lengths up to 2048 bit and Elliptic Curve GF (p).

As an important feature, SLE 66CLX360PE(M) provides a new and enhanced level of on-chip security, which fulfils the strong security requirements of a Common Criteria evaluation at an EAL5+ High level. Each security measure is designed to act as an integral part of the complete system in order to strengthen the system as a whole.

Thus, porting an **existing Operating System to SLE 66CLX360PE(M) requires only very limited changes** as it is typically reduced to add the Contactless Library and the Contactless Optimized Resource Management System (RMS\_E) to the existing Operating System.

SLE 66CLX360PE(M) integrates outstanding memory sizes, additional peripherals in combination with enhanced performance and optimized power consumption on a minimized die size.

In conclusion, SLE 66CLX360PE(M) fulfils the requirements of for both contact-based and contactless smart card applications such like electronic passport, national ID card, banking, security access, digital signature and transport. The family concept offers to select the right product for a given application in terms of available memory and price.

#### Glossary

| AES                 | Advanced Encryption Standard                                                                                                                                                      |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIS-31              | Functionality classes and evaluation methodology guidelines for physical random number generators defined by the German Institute for the Security of the Information Technology. |

| Caches              | Cache memories are Random Access Memories that the CPU can access more quickly than it can access regular RAM.                                                                    |

| CLK                 | Clock                                                                                                                                                                             |

| CPU                 | Central Processing Unit                                                                                                                                                           |

| CMOS                | Complementary Metal-Oxide Semiconductor, the technology used to manufacture most of<br>today's microchips.                                                                        |

| CRT                 | Chinese Remainder Theorem, computing technique                                                                                                                                    |

| DES, 3DES           | Data Encryption Standard                                                                                                                                                          |

| DSA                 | Digital Signature Algorithm                                                                                                                                                       |

| EAL 5+              | Common Criteria Certification level                                                                                                                                               |

| EC                  | Elliptic Curves                                                                                                                                                                   |

| EEPROM              | Electrically Erasable Programmable Read-Only Memory                                                                                                                               |

| ESD                 | Electrostatic Discharge, release of static electricity that can damage a chip                                                                                                     |

| Exponent            | Component of RSA key                                                                                                                                                              |

| F_4                 | Fermat Number $F_4$ , computing term.                                                                                                                                             |

| GF(2 <sup>m</sup> ) | Galois Field: finite field of $2^{m}$ elements represented by polynomials with degree < m                                                                                         |

| GF(p)               | Galois Field, set of whole numbers less than prime number $p$                                                                                                                     |

| I/O                 | Input/Output                                                                                                                                                                      |

| Modulus             | Component of RSA key                                                                                                                                                              |

| RAM                 | Random Access Memory                                                                                                                                                              |

| RISC                | Reduced Instruction Set Computer                                                                                                                                                  |

| RNG, TRNG           | Random Number Generator, True Random Number Generator                                                                                                                             |

| ROM                 | Read-Only Memory                                                                                                                                                                  |

| RSA                 | Rivest, Shamir and Adleman, inventors of the RSA cryptosystem                                                                                                                     |

| SHA-1               | Secure Hash Algorithm revision 1                                                                                                                                                  |

| STS                 | Self Test Software                                                                                                                                                                |

| T=0, T=1            | Communication Protocols defined in ISO 7816 standard                                                                                                                              |

| UART                | Universal Asynchronous Receiver/Transmitter                                                                                                                                       |

## Sales code name

Short Product Information www.infineon.com/security