### **General Description**

The MAX5105/MAX5106 nonvolatile, quad, 8-bit digitalto-analog converters (DACs) operate from a single +2.7V to +5.5V supply. An internal EEPROM stores the DAC states even after power is removed. Data from these nonvolatile registers automatically initialize the DAC outputs and operating states during power-up. Precision internal buffers swing Rail-to-Rail<sup>®</sup>, and the reference input range includes both ground and the positive rail.

The MAX5105/MAX5106 feature a software-controlled 10 $\mu$ A shutdown mode and a mute state that drives the DAC outputs to their respective REFL\_ voltages. The MAX5105 includes an asynchronous MUTE input, as well as a RDY/BSY output that indicates the status of the nonvolatile memory.

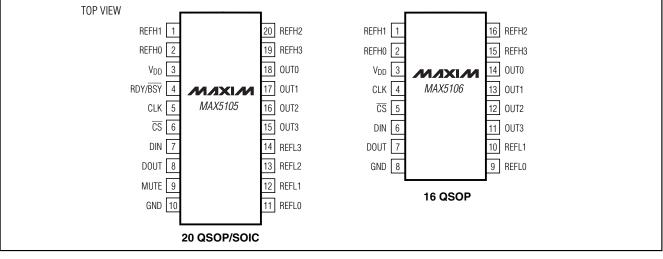

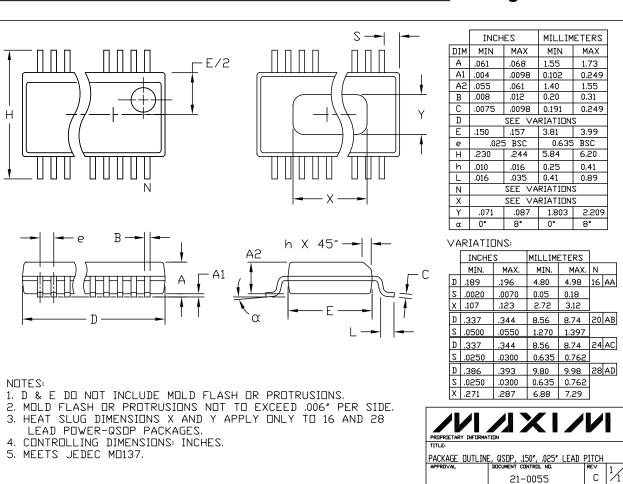

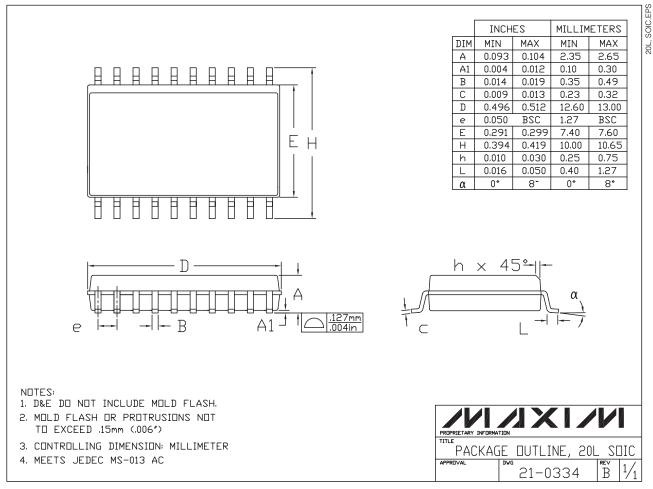

The MAX5105 is available in a 20-pin QSOP and 20-pin wide SO packages, and the MAX5106 is available in a 16-pin QSOP package.

### Applications

Digital Gain and Offset Adjustments

Programmable Attenuators

Portable Instruments

Power-Amp Bias Control

### Functional Diagram appears at end of data sheet.

Rail-to-Rail is a trademark of Nippon Motorola, Ltd.

SPI/QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

- On-Chip EEPROM Stores DAC States

- Power-On Reset Initialization of All Registers to Prestored States

- ♦ +2.7V to +5.5V Single-Supply Operation

- Four 8-Bit DACs with Independent High and Low Reference Inputs (MAX5105)

- ♦ Ground to V<sub>DD</sub> Reference Input Range

- ♦ Rail-to-Rail Output Buffers

- Low 1mA Supply Current

- Low Power 10µA (max) Shutdown Mode

- Small 20- or 16-Pin QSOP Package

- ◆ SPI™/QSPI™/MICROWIRE™-Compatible Serial Interface

- ♦ Asynchronous MUTE Input (MAX5105)

- RDY/BSY Pin to Indicate Memory Status (MAX5105)

- Wide Operating Temperature Range (-40°C to +85°C)

### \_Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX5105EEP | -40°C to +85°C | 20 QSOP     |

| MAX5105EWP | -40°C to +85°C | 20 SO       |

| MAX5106EEE | -40°C to +85°C | 16 QSOP     |

### Pin Configurations

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> , DIN, <del>CS</del> , CLK, MUTE to GND0.3V, +6V |

|------------------------------------------------------------------|

| DOUT, REFH_, REFL_, RDY/BSY,                                     |

| OUT_ to GND0.3V to (V <sub>DD</sub> + 0.3V)                      |

| Maximum Current into Any Pin±50mA                                |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )            |

| 16-Pin QSOP (derate 8.3mW/°C above +70°C)666.7mW                 |

| 20-Pin QSOP (derate 9.1mW/°C above +70°C)727.3mW                 |

| 20-Pin SO (derate 10mW/°C above +70°C)800mW                      |

|                                                                  |

| MAX510                            | 40°C to +85°C |

|-----------------------------------|---------------|

| Storage Temperature Range         |               |

| Junction Temperature              | +150°C        |

| Lead Temperature (soldering, 10s) | +300°C        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(V<sub>DD</sub> = V<sub>REFH</sub> = +2.7V to +5.5V, GND = V<sub>REFL</sub> = 0, C<sub>L</sub> = 100pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>DD</sub> = +3V and T<sub>A</sub> = +25°C.)

| PARAMETER                             | SYMBOL                                   | CONDITIONS                                                                                                       | MIN    | ТҮР                                            | MAX             | UNITS  |

|---------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------|-----------------|--------|

| STATIC ACCURACY                       |                                          | -                                                                                                                |        |                                                |                 |        |

| Resolution                            |                                          |                                                                                                                  | 8      |                                                |                 | Bits   |

| Integral Nonlinearity                 | INL                                      | Code range 10hex to F0hex,<br>I <sub>LOAD</sub> = 50μA                                                           |        |                                                | ±1              | LSB    |

|                                       |                                          | Full code range, $I_{LOAD} = 50\mu A$                                                                            |        |                                                | ±2              |        |

| Differential Nonlinearity<br>(Note 1) | DNL                                      | Code range 10hex to F0hex,<br>I <sub>LOAD</sub> = 50μA                                                           |        |                                                | ±0.5            | LSB    |

| (NOLE T)                              |                                          | Full code range, I <sub>LOAD</sub> = 50µA                                                                        |        |                                                | ±1              |        |

| Zero-Code Error                       | ZCE                                      | Code = 0Ahex                                                                                                     |        |                                                | ±20             | mV     |

| Zero-Code Temperature<br>Coefficient  |                                          | Code = 0Ahex                                                                                                     |        | ±20                                            |                 | µV/∘C  |

| Gain Error (Note 2)                   |                                          | Code = F0hex                                                                                                     |        |                                                | ±1              | LSB    |

| Gain-Error Temperature<br>Coefficient |                                          | Code = F0hex                                                                                                     |        | ±0.002                                         |                 | LSB/°C |

| Power-Supply Rejection Ratio          | PSRR                                     | Code = 0Ahex and FFhex, $V_{DD} = 2.7V$<br>to 5.5V, $V_{REFL} = 2.5V$ , $V_{REFL} = 0$ ,<br>$I_{LOAD} = 50\mu A$ |        |                                                | ±1              | LSB/V  |

| REFERENCE INPUT                       |                                          |                                                                                                                  |        |                                                |                 |        |

| Reference Input Voltage Range         | V <sub>REFH</sub> ,<br>V <sub>REFL</sub> |                                                                                                                  | 0      |                                                | V <sub>DD</sub> | V      |

| Input Resistance                      |                                          |                                                                                                                  | 92     | 256                                            | 413             | kΩ     |

| Input Resistance Matching             |                                          |                                                                                                                  |        | ±0.2                                           | ±1              | %      |

| Input Capacitance                     |                                          |                                                                                                                  |        | 10                                             |                 | pF     |

| DAC OUTPUTS                           |                                          |                                                                                                                  |        |                                                |                 |        |

| Output Voltage Range                  |                                          | N = input code, I <sub>LOAD</sub> = 0                                                                            | Vrefl_ | (VREFH -<br>VREFL)<br>x<br>(N/256)<br>+ VREFL_ |                 | V      |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>DD</sub> = V<sub>REFH</sub> = +2.7V to +5.5V, GND = V<sub>REFL</sub> = 0, C<sub>L</sub> = 100pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>DD</sub> = +3V and T<sub>A</sub> = +25°C.)

| PARAMETER                                | SYMBOL          | CON                                                               | DITIONS                                 | MIN                      | ТҮР  | МАХ | UNITS  |

|------------------------------------------|-----------------|-------------------------------------------------------------------|-----------------------------------------|--------------------------|------|-----|--------|

| Output Current (Note 3)                  |                 | $\Delta V_{OUT} < 1LSB$                                           |                                         |                          | ±1.0 |     | mA     |

| Amplifier Output Resistance<br>(Note 3)  |                 |                                                                   |                                         |                          | 3    |     | Ω      |

| DIGITAL INPUTS                           |                 |                                                                   |                                         | 1                        |      |     | -1     |

| Input High Voltage                       | VIH             |                                                                   |                                         | 0.7 x<br>V <sub>DD</sub> |      |     | V      |

| Input Low Voltage                        | VIL             |                                                                   |                                         |                          |      | 0.8 | V      |

| Input Current                            | l <sub>IN</sub> | $V_{IN} = 0 \text{ or } V_{DD}$                                   |                                         |                          |      | ±10 | μΑ     |

| Input Capacitance                        | CIN             |                                                                   |                                         |                          | 10   |     | рF     |

| DIGITAL OUTPUTS                          |                 |                                                                   |                                         |                          |      |     |        |

| Output High Voltage                      | V <sub>OH</sub> | ISOURCE = 0.4mA                                                   |                                         | V <sub>DD</sub><br>- 0.3 |      |     | V      |

| Output Low Voltage                       | VOL             | I <sub>SINK</sub> = 1mA                                           |                                         |                          |      | 0.4 | V      |

| Three-State Leakage Current              | ILEAK           |                                                                   |                                         |                          |      | ±10 | μΑ     |

| Three-State Output Capacitance           | Cout            |                                                                   |                                         |                          | 15   |     | pF     |

| DYNAMIC PERFORMANCE                      |                 |                                                                   |                                         |                          |      |     |        |

| CLK to OUT_ Settling Time (Note 4)       | tcos            |                                                                   |                                         |                          | 6    |     | μs     |

| Channel-to-Channel Crosstalk<br>(Note 5) |                 | V <sub>DD</sub> = +5V, code = F<br>V <sub>REFH</sub> = 2.5Vp-p at |                                         |                          | 85   |     | dB     |

|                                          |                 | V <sub>DD</sub> = +5V,                                            | V <sub>REFH</sub> = 2.5Vp-p at<br>1kHz  |                          | 58   |     | 10     |

| Signal to Noise Plus Distortion          | SINAD           | code = FFhex                                                      | V <sub>REFH</sub> = 2.5Vp-p at<br>10kHz |                          | 56   |     | - dB   |

| Multiplying Bandwidth                    |                 | V <sub>REFH</sub> = 0.5Vp-p, 30                                   | dB bandwidth                            |                          | 250  |     | kHz    |

| Reference Feedthrough                    |                 | V <sub>DD</sub> = +5V, code = C<br>V <sub>REFH</sub> = 2.5Vp-p at |                                         |                          | 86   |     | dB     |

| Clock Feedthrough                        |                 |                                                                   |                                         |                          | 4    |     | nV - s |

| DAC Output White Noise                   |                 |                                                                   |                                         |                          | 75   |     | nV/√Hz |

| Shutdown Recovery Time                   | tSDR            |                                                                   |                                         | Ì                        | 7    |     | μs     |

| Time to Shutdown                         | <b>t</b> SHDN   |                                                                   |                                         |                          | 2    |     | μs     |

| POWER SUPPLIES                           |                 |                                                                   |                                         |                          |      |     |        |

| Supply Voltage                           | V <sub>DD</sub> |                                                                   |                                         | 2.7                      |      | 5.5 | V      |

| Supply Current                           |                 | $I_{LOAD} = 0$ , digital inputs at GND or $V_{DD}$                |                                         |                          | 0.8  | 1.0 |        |

|                                          | IDD             | During nonvolatile wr                                             | ite operation                           |                          | 20   |     | mA     |

| Shutdown Current                         |                 |                                                                   |                                         |                          | 0.5  | 10  | μΑ     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{REFH} = +2.7V \text{ to } +5.5V, \text{ GND} = V_{REFL} = 0, C_L = 100\text{pF}, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD} = +3V$  and  $T_A = +25^{\circ}\text{C}$ .)

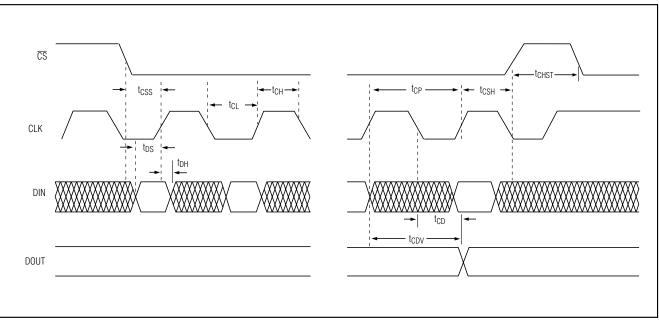

| PARAMETER                     | SYMBOL          | CONDITIONS                   | MIN | TYP     | MAX | UNITS  |

|-------------------------------|-----------------|------------------------------|-----|---------|-----|--------|

| DIGITAL TIMING                |                 |                              |     |         |     |        |

| CLK Period                    | tCP             |                              | 1   |         |     | μs     |

| CLK High Time                 | tсн             |                              | 300 |         |     | ns     |

| CLK Low Time                  | tCL             |                              | 300 |         |     | ns     |

| CS High Time                  | <b>t</b> CSHT   |                              | 150 |         |     | ns     |

| CS Setup Time                 | tcss            |                              | 100 |         |     | ns     |

| CS Hold Time                  | tCSH            |                              | 0   |         |     | ns     |

| DIN Setup Time                | tDS             |                              | 100 |         |     | ns     |

| DIN Hold Time                 | t <sub>DH</sub> |                              | 0   |         |     | ns     |

| CLK to DOUT Valid Time        | tCDV            | $C_{LOAD} = 100 pF$          |     |         | 1   | μs     |

| CLK to DOUT Propagation Delay | tCD             | $C_{LOAD} = 100 pF$          |     |         | 1   | μs     |

| DOUT Disable Time             | tCSD            | $C_{LOAD} = 100 pF$          |     |         | 250 | ns     |

| Nonvolatile Store Time        | <b>t</b> BUSY   |                              |     |         | 13  | ms     |

| NONVOLATILE MEMORY RELIA      | BILITY          |                              |     |         |     |        |

| Data Retention                |                 | MIL STD-883 Test Method 1008 |     | 100     |     | Years  |

| Endurance                     |                 | MIL STD-883 Test Method 1033 |     | 100,000 |     | Stores |

**Note 1:** Guaranteed monotonic.

Note 2: Gain error is: [100 x (V<sub>F0(MEAS</sub>) - ZCE - V<sub>F0(IDEAL</sub>))/V<sub>REFH</sub>]; where V<sub>F0(MEAS</sub>) is the DAC output voltage with input code F0hex. V<sub>F0(IDEAL</sub>) is the ideal DAC output voltage with input code F0hex (i.e., (V<sub>REFH</sub> - V<sub>REFL</sub>) × 240/256 + V<sub>REFL</sub>).

Note 3: In the voltage range, 0.5V < V<sub>OUT</sub> < V<sub>DD</sub> - 0.5V.

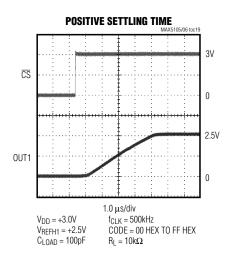

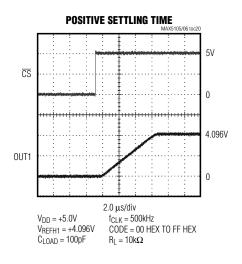

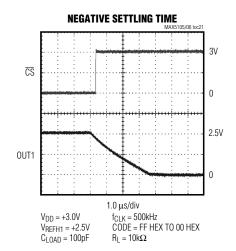

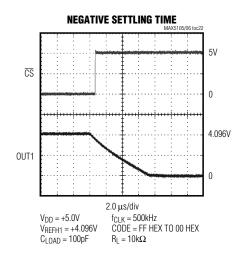

**Note 4:** Output settling time is measured from the 50% point of the rising edge of last CLK to 1/2LSB of V<sub>OUT</sub>'s final value for a code transition from 10hex to F0hex. See Figure 4.

**Note 5:** Channel-to-channel crosstalk is defined as the coupling from one driven reference with input code = FFhex to any other DAC output with the reference of that DAC at a constant value and input code = 00hex.

/N/IXI/N

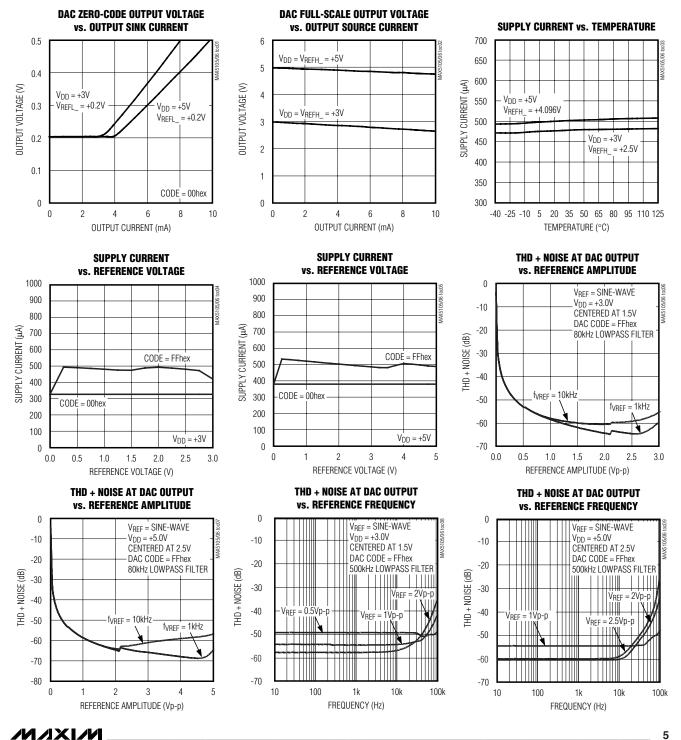

### **Typical Operating Characteristics**

( $R_L = \infty$ , code = FFhex,  $V_{REFL}$  = GND,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# MAX5105/MAX5106

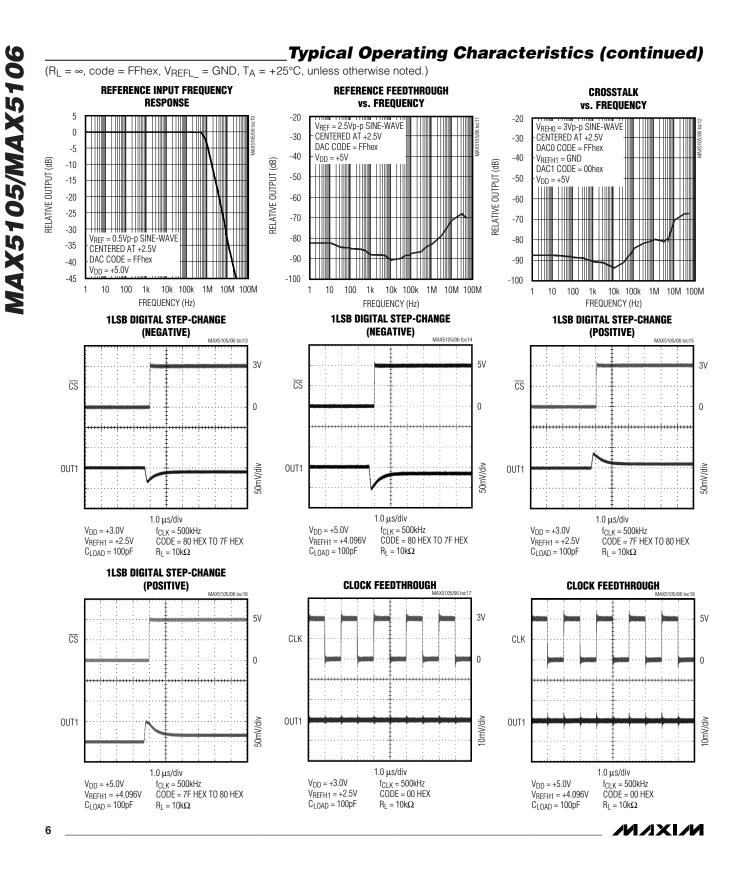

### **Typical Operating Characteristics (continued)**

(R<sub>L</sub> =  $\infty$ , code = FFhex, V<sub>REFL</sub> = GND, T<sub>A</sub> = +25°C, unless otherwise noted.)

| Р       | IN      | NAME            | FUNCTION                                                                                                                                               |

|---------|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX5105 | MAX5106 | NAME            | FUNCTION                                                                                                                                               |

| 1       | 1       | REFH1           | DAC1 High Reference Input                                                                                                                              |

| 2       | 2       | REFH0           | DAC0 High Reference Input                                                                                                                              |

| 3       | 3       | V <sub>DD</sub> | Positive Supply Voltage                                                                                                                                |

| 4       | _       | RDY/BSY         | Ready/Busy Open-Drain Output. Indicates the state of the nonvolatile memory. Connect a 100k $\Omega$ pullup resistor from RDY/BSY to V <sub>DD</sub> . |

| 5       | 4       | CLK             | Serial Clock Input                                                                                                                                     |

| 6       | 5       | CS              | Chip Select Input                                                                                                                                      |

| 7       | 6       | DIN             | Serial Data Input                                                                                                                                      |

| 8       | 7       | DOUT            | Serial Data Output                                                                                                                                     |

| 9       | _       | MUTE            | Mute Input. Drives all DAC outputs to their respective REFL_ voltages.                                                                                 |

| 10      | 8       | GND             | Ground. Serves as REFL2 and REFL3 for the MAX5106.                                                                                                     |

| 11      | 9       | REFL0           | DAC0 Low Reference Input                                                                                                                               |

| 12      | 10      | REFL1           | DAC1 Low Reference Input                                                                                                                               |

| 13      | —       | REFL2           | DAC2 Low Reference Input                                                                                                                               |

| 14      | —       | REFL3           | DAC3 Low Reference Input                                                                                                                               |

| 15      | 11      | OUT3            | DAC3 Output                                                                                                                                            |

| 16      | 12      | OUT2            | DAC2 Output                                                                                                                                            |

| 17      | 13      | OUT1            | DAC1 Output                                                                                                                                            |

| 18      | 14      | OUTO            | DAC0 Output                                                                                                                                            |

| 19      | 15      | REFH3           | DAC3 High Reference Input                                                                                                                              |

| 20      | 16      | REFH2           | DAC2 High Reference Input                                                                                                                              |

### **Detailed Description**

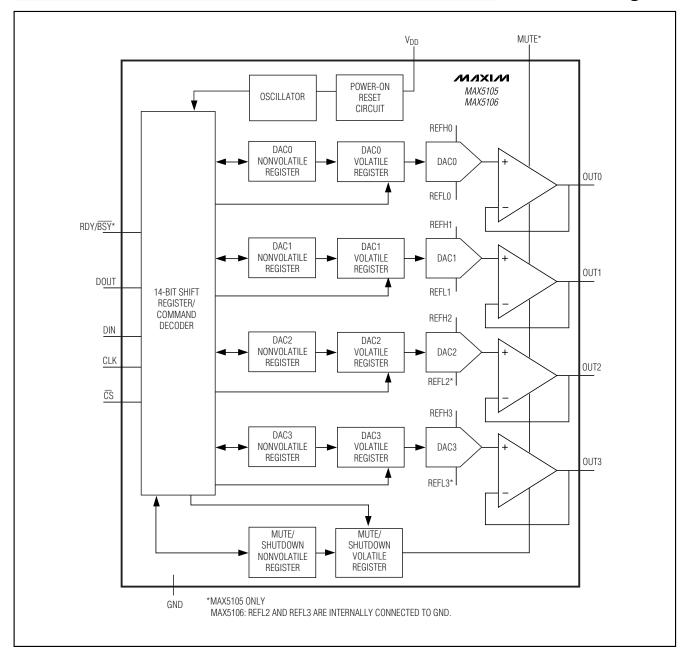

The MAX5105/MAX5106 quad, 8-bit DACs feature an internal, nonvolatile EEPROM, which stores the DAC states for initialization during power-up. These devices consist of four resistor string DACs, four rail-to-rail buffers, a 14-bit shift register, oscillator, power-on reset (POR) circuitry, and five volatile and five nonvolatile memory registers (*Functional Diagram*). The shift register decodes the control and address bits, routing the data to the proper memory registers. Data can be written to a selected volatile register, immediately updating

the DAC output, or can be written to a selected non-volatile register for storage.

The five volatile registers retain data as long as the device is enabled and powered. Once power is removed or the device is shut down, the volatile registers are cleared. The nonvolatile registers retain data even after power is removed. On power-up, the POR circuitry and internal oscillator control the transfer of data from the nonvolatile registers to the volatile registers, which automatically initializes the device upon startup. Data can be read from the nonvolatile registers through DOUT.

**Pin Description**

| Bit in<br>Register | D7<br>(MSB) | D6   | D5   | D4   | D3       | D2       | D1       | D0<br>(LSB) |

|--------------------|-------------|------|------|------|----------|----------|----------|-------------|

| Controlling        | Mute        | Mute | Mute | Mute | Shutdown | Shutdown | Shutdown | Shutdown    |

| Function           | DAC3        | DAC2 | DAC1 | DAC0 | DAC3     | DAC2     | DAC1     | DAC0        |

Table 1. Mute/Shutdown Register Mapping

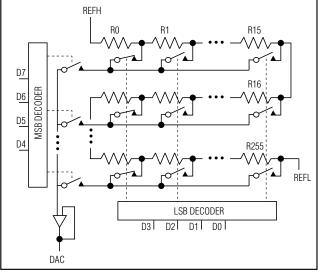

Figure 1. DAC Simplified Circuit Diagram

### **DAC Operation**

The MAX5105/MAX5106 use a matrix decoding architecture for the DACs, which saves power in the overall system. A resistor string placed in a matrix fashion divides down the difference between the external reference voltages,  $V_{REFH}$  and  $V_{REFL}$ . Row and column decoders select the appropriate tab from the resistor string, providing the needed analog voltages. The resistor string presents a code-independent input impedance to the reference and guarantees a monotonic output. Figure 1 shows a simplified diagram of one of the four DACs.

### **Output Buffer Amplifiers**

All MAX5105/MAX5106 analog outputs are internally buffered by precision unity-gain followers that slew at about 0.5V/ $\mu$ s. The outputs can swing from GND to VDD. With a VREFL\_ to VREFH\_ (or VREFH\_to VREFL\_) output transition, the amplifier outputs typically settle to  $\pm 1/2$ LSB in 6 $\mu$ s when loaded with 10k $\Omega$  in parallel with 100pF.

The software mute/shutdown command independently drives each output to its respective REFL\_ voltage

M/IXI/M

(mute) or to a high-impedance state (shutdown). Placing all four DACs in shutdown reduces supply current to  $10\mu A$  (max). The MAX5105 also provides an asynchronous MUTE input, simultaneously driving all DAC outputs to their respective REFL\_voltages.

### Internal EEPROM

The MAX5105/MAX5106 internal EEPROM consists of five nonvolatile registers that retain the DAC output and operating states after the device is powered down. Four registers store data for each DAC, and one stores the mute and shutdown states for the device.

### **DAC Registers**

The MAX5105/MAX5106 have eight 8-bit DAC registers, four volatile and four nonvolatile, that store DAC data. The four volatile DAC registers hold the current value of each DAC. Data is written to these registers in two ways: directly from DIN or loaded from the respective nonvolatile registers (see *Serial Input Data Format and Control Codes*). These registers are cleared when the device is shut down or power is removed.

The four nonvolatile registers retain the DAC values even after power is removed. Stored data is accessed in two ways: transferring data to a volatile register to update the respective DAC output or reading data through DOUT (see *Serial Input Data Format and Control Codes*). On power-up, the device is automatically initialized with data stored in the nonvolatile registers.

### Mute/Shutdown Registers

The MAX5105/MAX5106 have two 8-bit mute/shutdown registers that store the operating state of each DAC. The four MSBs hold the mute states, and the four LSBs hold the shutdown states (Table 1). The volatile registers hold the current mute/shutdown state of each DAC. Like the DAC registers, the nonvolatile mute/shutdown register maintains its data after the device is powered down, and the contents can be read on DOUT. The volatile register is initialized with the nonvolatile data on power-up and can be loaded through DIN or from the nonvolatile register (see *Serial Input Data Format and Control Codes*).

|       | 14-BIT SERIAL WORD |    |    |    |    | FUNCTION          |                                                                                                                                                                                                                           |

|-------|--------------------|----|----|----|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START | C1                 | C0 | A2 | A1 | A0 | D7-D0             | FUNCTION                                                                                                                                                                                                                  |

| 1     | 0                  | 0  | 0  | 0  | 0  | 8-bit DAC<br>data | Write DAC data to DAC0 nonvolatile register. Output remains unchanged.                                                                                                                                                    |

| 1     | 0                  | 0  | 0  | 0  | 1  | 8-bit DAC<br>data | Write DAC data to DAC1 nonvolatile register. Output remains unchanged.                                                                                                                                                    |

| 1     | 0                  | 0  | 0  | 1  | 0  | 8-bit DAC<br>data | Write DAC data to DAC2 nonvolatile register. Output remains unchanged.                                                                                                                                                    |

| 1     | 0                  | 0  | 0  | 1  | 1  | 8-bit DAC<br>data | Write DAC data to DAC3 nonvolatile register. Output remains unchanged.                                                                                                                                                    |

| 1     | 0                  | 0  | 1  | 0  | 0  | 8-bit DAC<br>data | Write shutdown and mute states to nonvolatile register. A 1 in bits D7–D4 mutes the respective DAC; a 1 in bits D3–D0 shuts down the respective DAC (Table 1). Outputs remain unchanged.                                  |

| 1     | 0                  | 1  | 0  | 0  | 0  | 8-bit DAC<br>data | Write DAC data to DAC0 volatile register and update OUT0.<br>All other DAC outputs remain unchanged.                                                                                                                      |

| 1     | 0                  | 1  | 0  | 0  | 1  | 8-bit DAC<br>data | Write DAC data to DAC1 volatile register and update OUT1.<br>All other DAC outputs remain unchanged.                                                                                                                      |

| 1     | 0                  | 1  | 0  | 1  | 0  | 8-bit DAC<br>data | Write DAC data to DAC2 volatile register and update OUT2.<br>All other DAC outputs remain unchanged.                                                                                                                      |

| 1     | 0                  | 1  | 0  | 1  | 1  | 8-bit DAC<br>data | Write DAC data to DAC3 volatile register and update OUT3.<br>All other DAC outputs remain unchanged.                                                                                                                      |

| 1     | 0                  | 1  | 1  | 0  | 0  | 8-bit DAC<br>data | Write shutdown and mute states to volatile register. A 1 in bits D7–D4 mutes the respective DAC; a 1 in bits D3–D0 shuts down the respective DAC (Table 1). DAC outputs updated to their respective mute/shutdown states. |

| 1     | 1                  | 0  | 0  | 0  | 0  | xxxxxxxx          | Read DAC0 nonvolatile register. Contents of DAC0 nonvolatile register available on DOUT. D7–D0 are ignored, and all DAC outputs remain unchanged.                                                                         |

| 1     | 1                  | 0  | 0  | 0  | 1  | xxxxxxxx          | Read DAC1 nonvolatile register. Contents of DAC1 nonvolatile register available on DOUT. D7–D0 are ignored, and all DAC outputs remain unchanged.                                                                         |

| 1     | 1                  | 0  | 0  | 1  | 0  | xxxxxxxx          | Read DAC2 nonvolatile register. Contents of DAC2 nonvolatile register available on DOUT. D7–D0 are ignored, and all DAC outputs remain unchanged.                                                                         |

| 1     | 1                  | 0  | 0  | 1  | 1  | xxxxxxxx          | Read DAC3 nonvolatile register. Contents of DAC3 nonvolatile register available on DOUT. D7–D0 are ignored, and all DAC outputs remain unchanged.                                                                         |

| 1     | 1                  | 0  | 1  | 0  | 0  | xxxxxxxx          | Read mute/shutdown nonvolatile register. Contents of mute/shutdown nonvolatile register available on DOUT. D7–D0 are ignored, and all DAC outputs remain unchanged.                                                       |

### **Table 2. Serial Interface Programming Commands**

|       |    | 14-BI | T SERIA | L WOR | D  |          | FUNCTION                                                                                                                                                                                                                                     |

|-------|----|-------|---------|-------|----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START | C1 | C0    | A2      | A1    | A0 | D7-D0    | FUNCTION                                                                                                                                                                                                                                     |

| 1     | 1  | 1     | 0       | 0     | 0  | ****     | Load DAC0 nonvolatile register. Contents of DAC0 nonvolatile register are loaded into the corresponding volatile register and OUT0 updated. D7–D0 are ignored, and all other DAC outputs remain unchanged.                                   |

| 1     | 1  | 1     | 0       | 0     | 1  | xxxxxxxx | Load DAC1 nonvolatile register. Contents of DAC1 nonvolatile register are loaded into the corresponding volatile register and OUT1 updated. D7–D0 are ignored, and all other DAC outputs remain unchanged.                                   |

| 1     | 1  | 1     | 0       | 1     | 0  | xxxxxxxx | Load DAC2 nonvolatile register. Contents of DAC2 nonvolatile register are loaded into the corresponding volatile register and OUT2 updated. D7–D0 are ignored, and all other DAC outputs remain unchanged.                                   |

| 1     | 1  | 1     | 0       | 1     | 1  | xxxxxxxx | Load DAC3 nonvolatile register. Contents of DAC3 nonvolatile register are loaded into the corresponding volatile register and OUT3 updated. D7–D0 are ignored, and all other DAC outputs remain unchanged.                                   |

| 1     | 1  | 1     | 1       | 0     | 0  | xxxxxxxx | Load mute/shutdown nonvolatile register. Contents of<br>mute/shutdown nonvolatile register are loaded into the<br>mute/shutdown volatile register, and all DACs are placed into their<br>respective mute/shutdown states. D7–D0 are ignored. |

### Table 2. Serial Interface Programming Commands (continued)

### **Serial Interface**

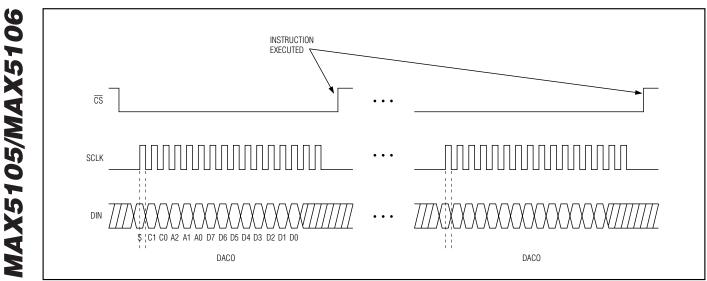

The MAX5105/MAX5106 communicate with microprocessors ( $\mu$ Ps) through a synchronous, full-duplex 3wire interface (Figure 2). Data is sent MSB first and is transmitted in one 14-bit word. A 4-wire interface adds a line for RDY/BSY (MAX5105), indicating the status of the nonvolatile memory. Data is transmitted and received simultaneously.

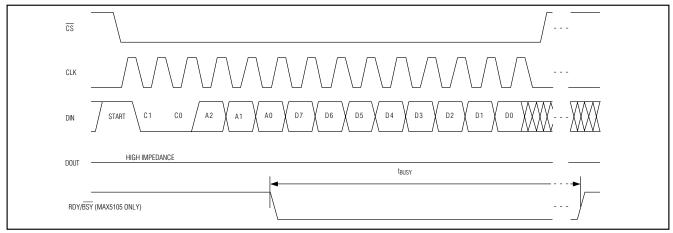

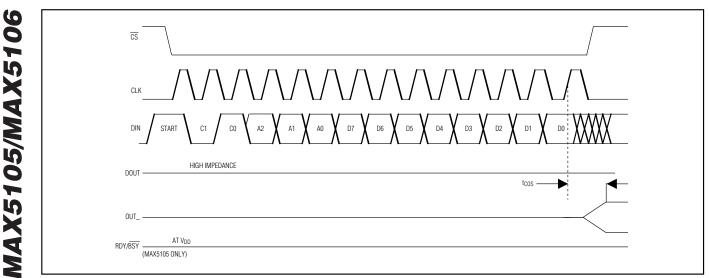

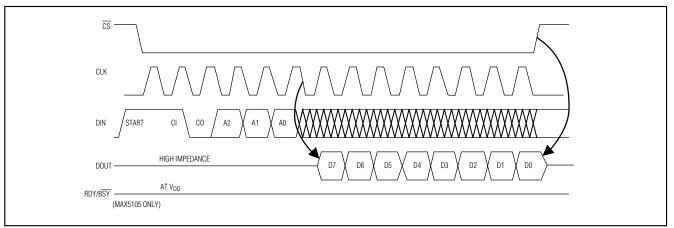

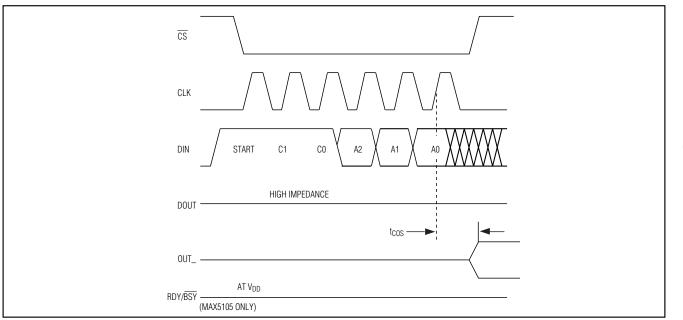

Figure 3 shows the detailed serial interface timing. Note that the clock should be low if it is stopped between updates. DOUT is high impedance until a valid read command and address is written to the device.

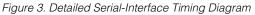

Serial data is clocked into the 14-bit shift register in an MSB-first format, with the start-bit, configuration, and address information preceding the actual DAC data. Data is clocked in on CLK's rising edge while  $\overline{\text{CS}}$  is low.

$\overline{\text{CS}}$  must be low to enable the device. If  $\overline{\text{CS}}$  is high, the interface is disabled and DOUT remains unchanged.  $\overline{\text{CS}}$  must go low at least 100ns before the first rising edge of the clock pulse to properly clock in the first bit. With  $\overline{\text{CS}}$  low, data is clocked into the shift register on the rising edge of the external serial clock.

### Serial Input Data Format and Control Codes

The 14-bit serial input format, shown in Figure 4, comprises one start bit, two control bits (C0, C1), three address bits (A0, A1, A2), and eight data bits (D7–D0). The 5-bit address/control code configures the DAC as shown in Table 2.

### **Nonvolatile Store Command**

The nonvolatile store command loads the 8-bit DAC data into the selected nonvolatile DAC register, or the DAC operating states into the mute/shutdown nonvolatile register. The nonvolatile store command does not affect the current DAC outputs or operating states. Once the control and address bits are clocked in, RDY/BSY (MAX5105) goes low until the nonvolatile store operation is complete. For the MAX5106, wait the maximum 13ms store time before writing a new word to the device. Do not write new data to the device until RDY/BSY (MAX5105) returns high, or the 13ms store time (MAX5106) has elapsed. Figure 5 shows the non-volatile store command timing diagram.

Figure 2. 3-Wire Interface Timing

### **Table 3. Nonvolatile Store Command**

| START | C1 | CO | A2 | A1      | AO | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

|-------|----|----|----|---------|----|----|----|----|-------|------|----|----|----|

| 1     | 0  | 0  |    | Address |    |    |    |    | 8-Bit | Data |    |    |    |

### **Table 4. Register Write Command**

|       | -  |    |    |         |    |            |    |    |    |    |    |    |    |  |

|-------|----|----|----|---------|----|------------|----|----|----|----|----|----|----|--|

| START | C1 | C0 | A2 | A1      | AO | D7         | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

| 1     | 0  | 1  |    | Address |    | 8-Bit Data |    |    |    |    |    |    |    |  |

### Table 5. Nonvolatile Read Command

| START | C1 | C0 | A2 | A1      | A0 | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

|-------|----|----|----|---------|----|----|----|----|-------|------|----|----|----|

| 1     | 1  | 0  |    | Address |    |    |    |    | Don't | Care |    |    |    |

### Table 6. Nonvolatile Load Command

| START | C1 | C0 | A2 | A1      | A0 | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

|-------|----|----|----|---------|----|----|----|----|-------|------|----|----|----|

| 1     | 1  | 1  |    | Address |    |    |    |    | Don't | Care |    |    |    |

### Table 7. Mute/Shutdown Modes

| START | C1 | C0 | A2 | A1 | A0 | D7                  | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

|-------|----|----|----|----|----|---------------------|----|----|----|----|----|----|----|--|

| 1     | 0  | 0  | 1  | 0  | 0  | Mute/Shutdown State |    |    |    |    |    |    |    |  |

Figure 5. Nonvolatile Store Command Timing Diagram

The nonvolatile store command is ignored if all DACs are muted or in shutdown.

### **Register Write Command**

This command directly loads the DAC data to the selected DAC volatile register and updates the respec-

tive output on the rising edge CLK corresponding to D0. The mute/shutdown volatile register is also accessible through this command by setting A2 high. A 1 in any of the four MSBs (D7–D4) mutes the selected DAC; a 1 in any of the four LSBs (D3–D0) disables the selected DAC (Table 1). The DAC operating states change

M/XI/M

13

MAX5105/MAX5106

Figure 6. Register Write Command Timing Diagram

Figure 7. Nonvolatile Read Command Timing Diagram

on the rising edge of CLK corresponding to D0. The register write command does not affect data stored in the nonvolatile memory. Figure 6 shows the register write command timing diagram.

### Nonvolatile Read Command

The nonvolatile read command makes the data from the selected nonvolatile register available to external devices. Data is clocked out on DOUT during the eight clock cycles following <u>A0</u>. DOUT returns to a highimpedance state when <u>CS</u> goes high. This command has no effect on the DAC outputs, operating states, or contents of the nonvolatile registers. Figure 7 shows the nonvolatile read command timing diagram. RDY/BSY remains high while a read is taking place.

Figure 8. Nonvolatile Load Command Timing Diagram

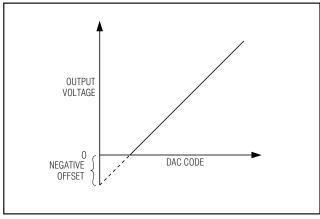

Figure 9. Effect of Negative Offset (Single Supply)

### **Nonvolatile Load Command**

The nonvolatile load command writes the contents of the selected nonvolatile register to the corresponding volatile register during the eight clock cycles following A0. This updates the respective DAC output or changes the operating state of the device on the rising edge of CLK corresponding to A0. This command does not affect the data in the nonvolatile register. Figure 8 shows the nonvolatile load command timing diagram. RDY/BSY remains high while a volatile register load is taking place.

### **Mute/Shutdown Modes**

The MAX5105/MAX5106 feature software-controlled mute and shutdown modes. The shutdown mode places the DAC outputs in a high-impedance state and reduces quiescent current consumption to  $10\mu$ A (max) with all DACs disabled.

Mute drives the selected DAC output to the corresponding REFL\_ voltage. The volatile DAC register retains its data, and the output returns to its previous state when mute is removed. The MAX5105 also features an asynchronous MUTE input that mutes all DACs.

The output buffers are individually disabled/muted with ones in the proper data bits (D7–D0) (Table 1).

When all DACs are muted or shut down, the nonvolatile store command is ignored. If the mute/shutdown novolatile register is used to shut down or mute all of the DACs, use the register write command to change the operating state of the device. Do this by executing a register write command that changes the contents of the mute/shutdown volatile register. Following this, the nonvolatile store command is again recognized.

### **Power-On Reset**

The power-on reset (POR) controls the initialization of the MAX5105/MAX5106. During this time, the on-chip oscillator is enabled and used to load the volatile DAC and mute/shutdown registers with data from the EEPROM.

This initialization period takes about 80µs with the DAC registers loading first and the mute/shutdown register loading last. During this time, the DAC outputs are held in the mute state and the serial interface is disabled. Once the mute/shutdown register is loaded, the DAC outputs are updated to their stored data and operating states, and the serial interface is enabled.

### **Applications Information**

### **DAC Linearity and Offset Voltage**

The output buffer can have a negative input offset voltage that would normally drive the output negative, but since there is no negative supply, the output remains at GND (Figure 9). When linearity is determined using the end-point method, it is measured between code 10 (0Ahex) and full-scale code (FFhex) after the offset and gain error are calibrated out. With a single supply, negative offset causes the output not to change with an input code transition near zero (Figure 9). Thus, the lowest code that produces a positive output is the lower endpoint.

### **External Voltage Reference**

The MAX5105/MAX5106 have two reference inputs for each DAC, REFH\_, and REFL\_. REFH\_ sets the full-scale voltage, while REFL\_ sets the zero code output. REFL2 and REFL3 are internally connected to GND in the MAX5106. A 256k $\Omega$  typical input impedance at REFH\_ is code independent. The output voltage from these devices can be represented by a digitally programmable voltage source as follows:

$V_{OUT} = [(V_{REFH} - V_{REFL}) \times (N / 256)] + V_{REFL}$

where N is the decimal value of the DAC's binary input code.

### **Power Sequencing**

The voltage applied to REFH\_ and REFL\_ should not exceed V<sub>DD</sub> at any time. If proper power sequencing is not possible, connect an external Schottky diode between REFH\_ and REFL\_ and V<sub>DD</sub> to ensure compliance with the absolute maximum ratings. Do not apply signals to the digital inputs before the device is fully powered up.

### Power-Supply Bypassing and Ground Management

Digital or AC transient signals on GND can create noise at the analog output. Return GND to the highest-quality ground available. Bypass V<sub>DD</sub> with a  $0.1\mu$ F capacitor, located as close to the device as possible. Bypass REF\_ to GND with a  $0.1\mu$ F capacitor. Carefully printed circuit board ground layout minimizes crosstalk between the DAC outputs and digital inputs.

### **Chip Information**

TRANSISTOR COUNT: 32,000 PROCESS: CMOS

\_Functional Diagram

MAX5105/MAX5106

### **Package Information**

Ë

QSOP.I

### \_Package Information (continued)

19

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2001 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.