## **General Description**

The MAX5951 is a 12V pulse-width modulated (PWM), step-down, DC-DC controller. The device operates over the input-voltage range of 8V to 16V or 5V ±10%, and provides an adjustable output from 0.8V to 5.5V. The device delivers up to 10A of load current with excellent load-and-line regulation.

The MAX5951 PWM section utilizes a voltage-mode control scheme for good noise immunity and offers external compensation, allowing for maximum flexibility with a wide selection of inductor values and capacitor types. The device operates at a fixed switching frequency that is programmable from 100kHz to 1MHz and can be synchronized to an external clock signal though the SYNCIN input. The device includes undervoltage lockout (UVLO) and digital soft-start. Protection features include lossless valley-mode current limit, hiccup-mode output short-circuit protection, and thermal shutdown.

The MAX5951 is available in a space-saving 5mm x 5mm, 32-pin thin QFN package and is specified for operation over the -40°C to +85°C extended temperature range. Refer to the MAX5950 data sheet for a pincompatible PWM controller with hot swap.

## **Applications**

PCI-e Express Modules™ General 12V or 5V Input PWM Controllers **Blade Servers RAID Base Stations**

Workstations

PCI-e Express Modules is a trademark of PCI-SIG.

# **Features**

- ♦ 8V to 16V or 5V ±10% Input-Voltage Range

- **♦ Lossless Valley-Mode Current Sensing**

- ♦ Output Voltage Adjustable from 0.8V to 5.5V

- ♦ Voltage-Mode Control

- **♦** External Compensation for Maximum Flexibility

- ♦ Digital Soft-Start

- **♦** Sequencing or Ratiometric Tracking

- ♦ Startup Synchronization

- **♦ Programmable PGOOD Output**

- ♦ Programmable Switching Frequency from 100kHz to 1MHz

- **♦** External Frequency Synchronization

- ♦ SYNCIN and SYNCOUT Enable 180° Out-of-Phase Operation

- **♦** Thermal Shutdown and Short-Circuit Protection

- ♦ Space-Saving, 5mm x 5mm, 32-Pin TQFN Package

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|-------------|----------------|-----------------|-------------|

| MAX5951ETJ+ | -40°C to +85°C | 32 TQFN         | T3255-4     |

<sup>+</sup>Denotes lead-free package.

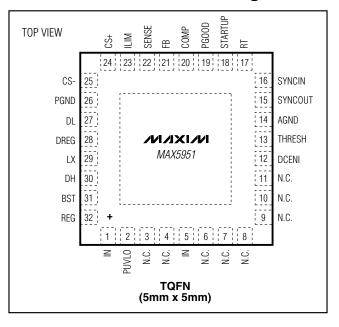

## Pin Configuration

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| IN to AGNDBST to AGND             | 0.3V to +30V                     |

|-----------------------------------|----------------------------------|

| BST to LX                         |                                  |

| CS- to AGND                       | ,                                |

| REG, DREG, PUVLO, DCENI, SYNCIN,  | - ,                              |

| SENSE to AGND                     |                                  |

| RT, ILIM, STARTUP, PGOOD, FB, CS+ |                                  |

| SYNCOUT, COMP to AGND             | 0.3V to $(V_{REG} + 0.3V)$       |

| DL to PGND                        | 0.3V to (V <sub>DREG</sub> + 6V) |

| DH to LX                          | 0.3V to $(V_{BST} + 0.3V)$       |

| PGND to AGND                      | 0.3V to +0.3V                    |

| Input Current (any pin)           | ±50mA                            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ C | C)       |

|------------------------------------------------------|----------|

| 32-Pin TQFN (derate 34.5 mW/°C abov                  |          |

| 32-Pin TQFN ( $\theta_{JA}$ )                        | +29°C/W  |

| 32-Pin TQFN (θ <sub>JC</sub> )                       | +2.1°C/W |

| Operating Ambient Temperature Range                  |          |

| Maximum Junction Temperature                         | +150°C   |

| Storage Temperature Range                            |          |

| Lead Temperature (soldering, 10s)                    | +300°C   |

|                                                      |          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=12V \text{ or } V_{IN}=V_{REG}=5V, V_{DREG}=V_{REG}, V_{PGND}=0V, V_{SYNCIN}=0V, R_{RT}=100 k\Omega, R_{ILIM}=60 k\Omega, C_{REG}=2.2 \mu F, T_A=T_J=-40 ^{\circ}C \text{ to } +85 ^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A=T_J=+25 ^{\circ}C.) \text{ (Note 1)}$

| PARAMETER                                     | SYMBOL             | CONDITIONS                                                      | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------------|--------------------|-----------------------------------------------------------------|-------|-------|-------|-------|

| Input-Voltage Range                           | VIN                |                                                                 | 8     |       | 16    | V     |

| input-voitage hange                           | V IN               | V <sub>IN</sub> = V <sub>REG</sub> = V <sub>DREG</sub> (Note 2) | 4.5   |       | 5.5   | V     |

| Standby Supply Current                        |                    | V <sub>IN</sub> = 16V, V <sub>PUVLO</sub> = 0V                  |       | 0.3   | 0.5   | mA    |

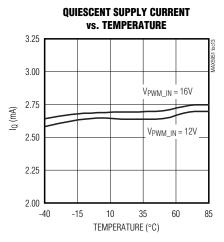

| Quiescent Supply Current                      |                    | $V_{IN} = 16V, V_{FB} = 0.9V$                                   |       | 1.6   | 2.6   | mA    |

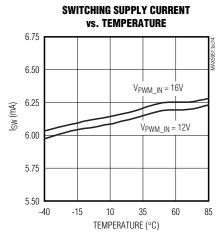

| Switching Supply Current                      |                    | $V_{IN} = 16V$ , $V_{FB} = 0V$                                  |       | 5.0   | 8.0   | mA    |

| PWM UVLO                                      |                    |                                                                 |       |       |       |       |

| Default PWM Undervoltage<br>Lockout Threshold |                    | V <sub>IN</sub> rising                                          | 6.7   |       | 7.3   | V     |

| PWM Undervoltage Lockout<br>Hysteresis        |                    |                                                                 |       | 0.7   |       | V     |

| PUVLO Threshold                               | V <sub>PUVLO</sub> | V <sub>PUVLO</sub> rising                                       | 1.202 | 1.220 | 1.238 | V     |

| PUVLO Hysteresis                              |                    |                                                                 |       | 122   |       | mV    |

| PUVLO Input Impedance                         |                    |                                                                 | 180   | 310   | 500   | kΩ    |

| PWM DCENI CONTROL                             |                    |                                                                 |       |       |       |       |

| DCENI Comparator Input<br>Common-Mode Range   |                    |                                                                 | 0     |       | 3     | V     |

| DCENI Comparator Offset                       |                    | V <sub>DCENI</sub> - V <sub>THRESH</sub>                        | -10   |       | +10   | mV    |

| DCENI Comparator Hysteresis                   |                    |                                                                 |       | 100   |       | mV    |

| DCENI Input Current                           |                    |                                                                 | -1    |       | +1    | μΑ    |

| THRESH Operating Voltage<br>Range             |                    |                                                                 | 0.6   |       | 2.5   | V     |

| TUDECH Input Current                          |                    | V <sub>THRESH</sub> > 0.6V                                      | -1.5  |       | +1    |       |

| THRESH Input Current                          |                    | VTHRESH < 0.3V                                                  | -5    |       | +1    | μΑ    |

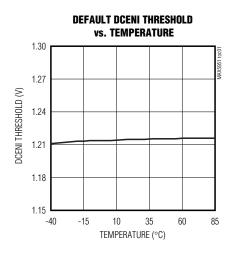

| Default DCENI Threshold                       |                    | VTHRESH < 0.3V                                                  | 1.202 | 1.22  | 1.238 | V     |

2 \_\_\_\_\_\_*MAXIM*

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=12V \text{ or } V_{IN}=V_{REG}=5V, V_{DREG}=V_{REG}, V_{PGND}=0V, V_{SYNCIN}=0V, R_{RT}=100k\Omega, R_{ILIM}=60k\Omega, C_{REG}=2.2\mu F, T_A=T_J=-40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A=T_J=+25^{\circ}C$ .) (Note 1)

| PARAMETER                                 | SYMBOL           | CONDITIONS                                                | S                                  | MIN                    | TYP | MAX                       | UNITS |

|-------------------------------------------|------------------|-----------------------------------------------------------|------------------------------------|------------------------|-----|---------------------------|-------|

| PWM PGOOD OUTPUT                          | - 1              |                                                           |                                    |                        |     |                           | l     |

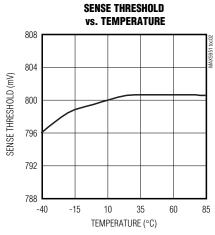

| SENSE Threshold                           |                  | V <sub>SENSE</sub> rising                                 |                                    | 788                    | 800 | 812                       | mV    |

| SENSE Hysteresis                          |                  |                                                           |                                    |                        | 100 |                           | mV    |

| SENSE Input Bias Current                  |                  |                                                           |                                    | -1                     |     | +1                        | μΑ    |

| PGOOD Internal Pullup Current             |                  |                                                           |                                    |                        | 10  |                           | μΑ    |

| PGOOD Output Voltage Low                  |                  | IPGOOD = -2.4mA                                           |                                    |                        |     | 50                        | mV    |

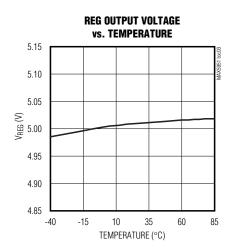

| INTERNAL VOLTAGE REGULAT                  | OR               |                                                           |                                    |                        |     |                           |       |

| Output Voltage Set Point                  | VREG             |                                                           |                                    | 4.7                    |     | 5.3                       | V     |

| Line Regulation                           |                  | V <sub>IN</sub> = 8V to 16V                               |                                    |                        |     | 1                         | mV/V  |

| Load Regulation                           |                  | IREG = 0 to 50mA                                          |                                    |                        |     | 150                       | mV    |

| PWM OSCILLATOR                            | •                |                                                           |                                    |                        |     |                           |       |

| Oscillator Frequency Range                | fsw              | VSYNCIN = 0V, fSW = 5 x 10                                | <sup>10</sup> / R <sub>RT</sub> Hz | 100                    |     | 1000                      | kHz   |

|                                           |                  |                                                           | fsw < 500kHz                       | -2.5                   |     | +2.5                      | 0/    |

| Consillator Annual Consillator            |                  | $T_A = T_J = +25$ °C                                      | fsw > 500kHz                       | -4                     |     | +4                        | %     |

| Oscillator Accuracy                       |                  | T T 1000 1 0500                                           | fsw < 500kHz                       | -3.5                   |     | +3.5                      | 0/    |

|                                           |                  | $T_A = T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | fsw > 500kHz                       | -5                     |     | +5                        | %     |

| RT Voltage                                | V <sub>RT</sub>  | $50$ k $\Omega$ < R <sub>RT</sub> < $500$ k $\Omega$      |                                    |                        | 2   |                           | V     |

| Maximum Duty Cycle                        |                  | V <sub>SYNCIN</sub> = 0V, V <sub>IN</sub> = 12V           |                                    | 82                     | 88  |                           | %     |

| SYNCIN High-Level Voltage                 |                  |                                                           |                                    | 2.1                    |     |                           | V     |

| SYNCIN Low-Level Voltage                  |                  |                                                           |                                    |                        |     | 0.8                       | V     |

| SYNCIN Pulldown Resistor                  |                  |                                                           |                                    | 50                     | 100 | 150                       | kΩ    |

| SYNCIN Rising to SYNCOUT Falling Delay    |                  |                                                           |                                    |                        | 10  |                           | ns    |

| SYNCIN Falling to SYNCOUT<br>Rising Delay |                  |                                                           |                                    |                        | 30  |                           | ns    |

| Maximum SYNCIN Frequency                  |                  |                                                           |                                    | 1                      |     |                           | MHz   |

| SYNCOUT Voltage High                      | VHSYNCOUT        | ISYNCOUT = +1.2mA                                         |                                    | V <sub>REG</sub> - 0.1 |     |                           | V     |

| SYNCOUT Voltage Low                       | VLSYNCOUT        | ISYNCOUT = -2.4mA                                         |                                    |                        |     | 50                        | mV    |

| PWM ERROR AMPLIFIER                       | -                | <u>'</u>                                                  |                                    |                        |     |                           |       |

| FB Input Range                            |                  |                                                           |                                    | 0                      |     | V <sub>REF</sub>          | V     |

| FB Input Current                          |                  |                                                           |                                    | -250                   |     | +250                      | nA    |

| COMP Output Voltage Range                 |                  | I <sub>COMP</sub> = -500μA to +500μA                      |                                    | 0.25                   |     | V <sub>REG</sub> -<br>0.5 | V     |

| Open-Loop Gain                            |                  |                                                           |                                    |                        | 80  |                           | dB    |

| Unity-Gain Bandwidth                      | f <sub>GBW</sub> |                                                           |                                    |                        | 2.5 |                           | MHz   |

| Reference Voltage                         | V <sub>REF</sub> | I <sub>COMP</sub> = -500μA to +500μA                      |                                    | 792                    | 800 | 808                       | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=12V \text{ or } V_{IN}=V_{REG}=5V, V_{DREG}=V_{REG}, V_{PGND}=0V, V_{SYNCIN}=0V, R_{RT}=100k\Omega, R_{ILIM}=60k\Omega, C_{REG}=2.2\mu F, T_{A}=T_{J}=-40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_{A}=T_{J}=+25^{\circ}C.) \text{ (Note 1)}$

| PARAMETER                                                             | SYMBOL           | CONDITIONS                                                                | MIN  | TYP  | MAX  | UNITS  |

|-----------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|------|------|------|--------|

| PWM COMPARATOR                                                        |                  | •                                                                         |      |      |      |        |

| Comparator Offset Voltage                                             |                  |                                                                           |      | 0.3  |      | V      |

| Comparator Propagation Delay                                          |                  |                                                                           |      | 40   |      | ns     |

| PWM DIGITAL SOFT-START                                                |                  | •                                                                         |      |      |      |        |

| Soft-Start Duration                                                   |                  |                                                                           |      | 1024 |      | Clocks |

| Defense Neltens Otens                                                 |                  |                                                                           |      | 128  |      | Steps  |

| Reference Voltage Steps                                               |                  |                                                                           |      | 6.3  |      | mV     |

| PWM RAMP GENERATOR                                                    |                  | ·                                                                         |      |      |      | •      |

| Ramp Amplitude                                                        |                  |                                                                           |      | 1.8  |      | V      |

| PWM CURRENT-LIMIT COMPARA                                             | ATOR AND H       | ICCUP MODE                                                                |      |      |      | 1      |

| Cycle-by-Cycle Valley Current-<br>Limit Threshold Adjustment<br>Range |                  | Limit = V <sub>ILIM</sub> / 10                                            | 50   |      | 350  | mV     |

| Cycle-by-Cycle Valley Current-                                        |                  | V <sub>ILIM</sub> = 0.5V                                                  | 44.5 |      | 55.5 |        |

| Limit Threshold Tolerance                                             |                  | V <sub>ILIM</sub> = 3.5V                                                  | 330  |      | 366  | mV     |

| ILIM Reference Current                                                |                  | $V_{ILIM} = 0 \text{ to } 3.5V, T_A = T_J = +25^{\circ}C$                 | 19   | 20   | 21   | μA     |

| ILIM Reference Current Tempco                                         |                  | 7 77 0                                                                    |      | 3333 |      | ppm/°C |

| CS+, CS- Input Bias Current                                           |                  | $V_{CS+} = 0V$ , $V_{CS-} = -0.3V$ , current out of the $CS_{-}$          | -1   |      | +20  | μΑ     |

| PWM HICCUP MODE                                                       | J                |                                                                           |      |      |      | 1      |

| Number of Cumulative Current-<br>Limit Events to Hiccup               | N <sub>CL</sub>  |                                                                           |      | 8    |      | Clocks |

| Number of Consecutive<br>Noncurrent-Limit Cycles to Clear<br>NCL      | N <sub>CLR</sub> |                                                                           |      | 3    |      | Clocks |

| Hiccup Timeout                                                        | NHT              |                                                                           |      | 512  |      | Clocks |

| PWM STARTUP INPUT                                                     |                  | ·                                                                         |      |      |      |        |

| STARTUP Threshold                                                     | Vsut             |                                                                           | 1.1  |      | 1.9  | V      |

| STARTUP Threshold Hysteresis                                          |                  |                                                                           |      | 250  |      | mV     |

| Internal Pullup Current                                               | ISTART           |                                                                           |      | 10   |      | μΑ     |

| STARTUP Output Voltage Low                                            |                  | ISTARTUP = -2.4mA                                                         |      |      | 0.1  | V      |

| PWM DH DRIVER                                                         | •                | •                                                                         |      |      |      |        |

| Peak Source Current                                                   |                  | V <sub>DH,LX</sub> = 0V, pulse width < 100ns,<br>V <sub>BST,LX</sub> = 5V |      | 2    |      | А      |

| Peak Sink Current                                                     |                  | V <sub>DH,LX</sub> = 5V, pulse width < 100ns,<br>V <sub>BST,LX</sub> = 5V |      | 2    |      | А      |

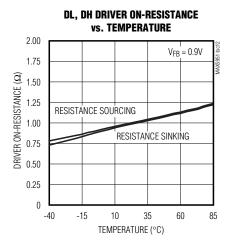

| DH Resistance Sourcing                                                |                  | $I_{DH} = 50$ mA, $V_{BST,LX} = 5V$                                       |      | 1    | 3    | Ω      |

| DH Resistance Sinking                                                 |                  | I <sub>DH</sub> = -50mA, V <sub>BST,LX</sub> = 5V                         |      | 1    | 3    | Ω      |

4 \_\_\_\_\_\_*NIXI/*M

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=12V \text{ or } V_{IN}=V_{REG}=5V, V_{DREG}=V_{REG}, V_{PGND}=0V, V_{SYNCIN}=0V, R_{RT}=100k\Omega, R_{ILIM}=60k\Omega, C_{REG}=2.2\mu F, T_A=T_J=-40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A=T_J=+25^{\circ}C$ .) (Note 1)

| PARAMETER                    | PARAMETER SYMBOL CONDITIONS |                                                                      |  | TYP | MAX | UNITS |

|------------------------------|-----------------------------|----------------------------------------------------------------------|--|-----|-----|-------|

| PWM DL DRIVER                |                             |                                                                      |  |     |     |       |

| Peak Source Current          |                             | V <sub>DL</sub> = 0V, pulse width < 100ns,<br>V <sub>DREG</sub> = 5V |  | 2   |     | А     |

| Peak Sink Current            |                             | V <sub>DL</sub> = 5V, pulse width < 100ns,<br>V <sub>DREG</sub> = 5V |  | 2   |     | А     |

| DL Resistance Sourcing       |                             | I <sub>DL</sub> = 50mA, V <sub>DREG</sub> = 5V                       |  | 1   | 3   | Ω     |

| DL Resistance Sinking        |                             | I <sub>DL</sub> = -50mA, V <sub>DREG</sub> = 5V                      |  | 1   | 3   | Ω     |

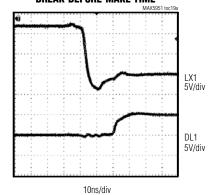

| Break-Before-Make Time       |                             |                                                                      |  | 25  |     | ns    |

| THERMAL SHUTDOWN             |                             |                                                                      |  |     |     |       |

| Thermal Shutdown Temperature |                             | T <sub>J</sub> rising                                                |  | 135 | •   | °C    |

| Thermal Shutdown Hysteresis  |                             |                                                                      |  | 15  | •   | °C    |

**Note 1:** Limits at -40°C are guaranteed by design and are not production tested.

Note 2: For 5V applications, connect REG directly to IN.

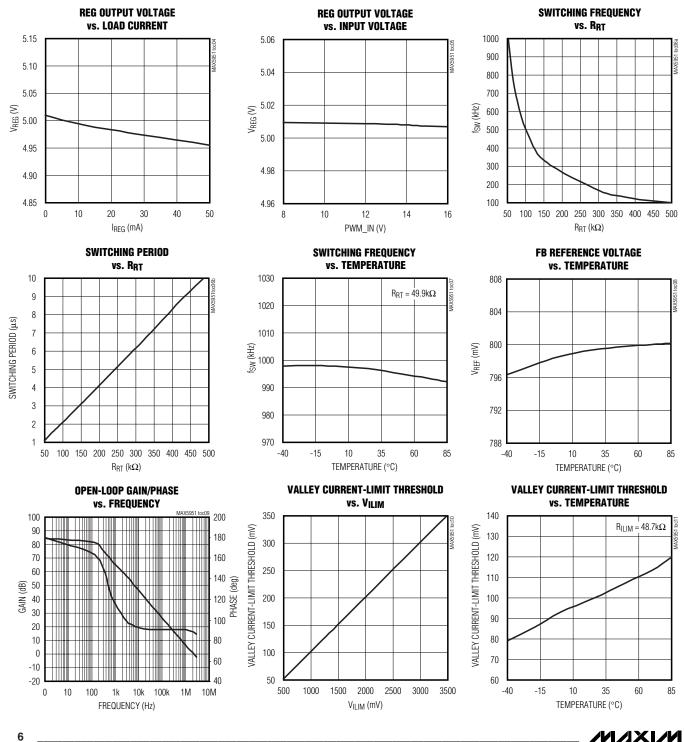

## Typical Operating Characteristics

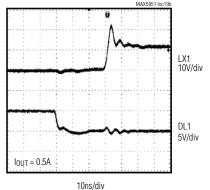

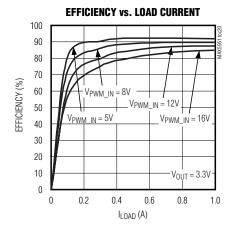

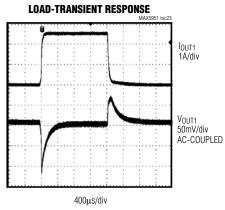

$(\textit{Typical Operating Circuits}. \ V_{IN} = 12 V \ \text{or} \ V_{IN} = V_{REG} = 5 V, \ V_{DREG} = V_{REG}, \ V_{PGND} = 0 V, \ V_{SYNCIN} = 0 V, \ R_{RT} = 49.9 k\Omega, \ R_{ILIM} = 48.7 k\Omega, \ C_{REG} = 2.2 \mu F, \ T_{A} = +25 ^{\circ} C.)$

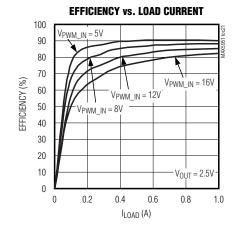

## Typical Operating Characteristics (continued)

(Typical Operating Circuits.  $V_{IN} = 12V$  or  $V_{IN} = V_{REG} = 5V$ ,  $V_{DREG} = V_{REG}$ ,  $V_{PGND} = 0V$ ,  $V_{SYNCIN} = 0V$ ,  $V_{RT} = 49.9k\Omega$ ,  $V_{RT} = 48.7k\Omega$ ,  $V_{REG} = 2.2\mu F$

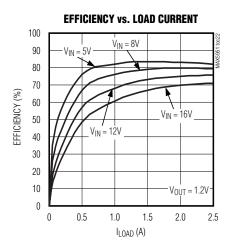

## Typical Operating Characteristics (continued)

(Typical Operating Circuits.  $V_{IN} = 12V$  or  $V_{IN} = V_{REG} = 5V$ ,  $V_{DREG} = V_{REG}$ ,  $V_{PGND} = 0V$ ,  $V_{SYNCIN} = 0V$ ,  $V_{RRT} = 49.9k\Omega$ ,  $V_{RRT} = 48.7k\Omega$ ,  $V_{RRG} = 2.2\mu F$ ,  $V_{RRG} = 2.2\mu F$ ,  $V_{RRG} = 2.2\mu F$ ,  $V_{RRG} = 49.9k\Omega$ ,  $V_{RRG} = 48.7k\Omega$ ,  $V_{RRG} = 49.9k\Omega$

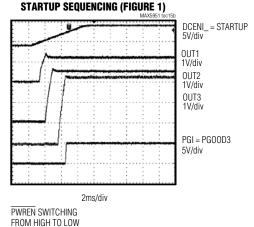

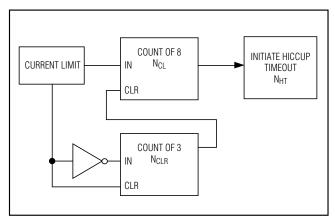

# PGOOD SEQUENCING (FIGURE 1) MAXSSS1 tocl 5a 5V/div OUT1 11V/div OUT2 11V/div OUT3 11V/div PGOOD3 5V/div

DCENI = STARTUP

OUT1

1V/div OUT2 1V/div

OUT3 1V/div

PGOOD\_

5V/div

#### 400µs/div PWREN SWITCHING FROM HIGH TO LOW

## Typical Operating Characteristics (continued)

(Typical Operating Circuits.  $V_{IN} = 12V$  or  $V_{IN} = V_{REG} = 5V$ ,  $V_{DREG} = V_{REG}$ ,  $V_{PGND} = 0V$ ,  $V_{SYNCIN} = 0V$ ,  $V_{RRT} = 49.9k\Omega$ ,  $V_{RRT} = 48.7k\Omega$ ,  $V_{RRG} = 2.2\mu$ F,  $V_{RRT} = 49.9k\Omega$ .

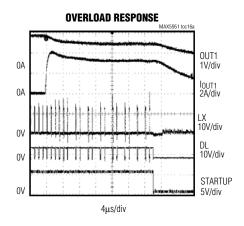

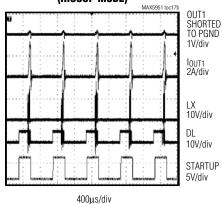

#### **OVERLOAD RESPONSE (HICCUP MODE)**

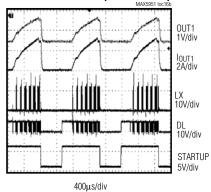

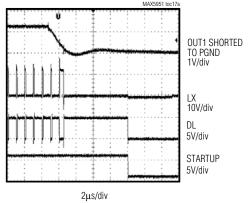

# SHORT-CIRCUIT RESPONSE (HICCUP MODE)

#### BREAK-BEFORE-MAKE TIME

#### **SHORT-CIRCUIT RESPONSE**

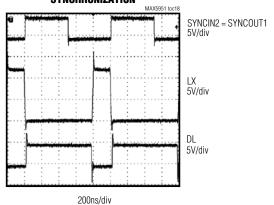

#### **SYNCHRONIZATION**

#### **BREAK-BEFORE-MAKE TIME**

## Typical Operating Characteristics (continued)

$(\textit{Typical Operating Circuits}. \ V_{IN} = 12V \ or \ V_{IN} = V_{REG} = 5V, \ V_{DREG} = V_{REG}, \ V_{PGND} = 0V, \ V_{SYNCIN} = 0V, \ R_{RT} = 49.9k\Omega, \ R_{ILIM} = 48.7k\Omega, \ C_{REG} = 2.2\mu F, \ T_{A} = +25^{\circ}C.)$

## \_\_\_\_\_Pin Description

| PIN        | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5       | IN      | Supply Input Connection. Connect to an external voltage source from 8V to 16V. For 5V input application, connect IN = REG to a 5V $\pm$ 10% source. Connect an external divider from IN to PUVLO to AGND to lower the startup voltage.                                                                                                                                                                 |

| 2          | PUVLO   | PWM UVLO Divider Center Point. Use an external divider to override the internal PWM UVLO divider. The rising threshold is set to 1.220V with 122mV hysteresis. Leave PUVLO unconnected for the default PWM UVLO.                                                                                                                                                                                       |

| 3, 4, 6–11 | N.C.    | No Connection. Do not connect.                                                                                                                                                                                                                                                                                                                                                                         |

| 12         | DCENI   | DC-DC Enable Input. DCENI must be above V <sub>THRESH</sub> for the PWM controller to start. Connect to REG if not used.                                                                                                                                                                                                                                                                               |

| 13         | THRESH  | DC-DC Enable Input Threshold Set. Connect a resistive divider from REG to THRESH to AGND to set the DCENI threshold. Connect to ground for a default threshold of 1.220V.                                                                                                                                                                                                                              |

| 14         | AGND    | Analog Ground Connection. Solder the exposed pad to a large AGND plane. Connect AGND and PGND together at one point near the input bypass capacitor return terminal.                                                                                                                                                                                                                                   |

| 15         | SYNCOUT | Synchronization Output. SYNCOUT is a synchronization signal to drive the SYNCIN of a second MAX5950 or MAX5951, if used. Leave SYNCOUT unconnected when not used.                                                                                                                                                                                                                                      |

| 16         | SYNCIN  | Synchronization Input. SYNCIN accepts the SYNCOUT from another MAX5950 or MAX5951 and shifts switching by 180°, allowing the reduction of the input bypass capacitors. When used, drive with a frequency at least 20% higher than the frequency programmed through the RT pin. If phase staggering is desired, use 50% duty cycle. Connect SYNCIN to AGND when not used.                               |

| 17         | RT      | Oscillator Timing Resistor Connection. Connect a $500k\Omega$ to $50k\Omega$ resistor from RT to AGND to program the switching frequency from 100kHz to 1MHz.                                                                                                                                                                                                                                          |

| 18         | STARTUP | Startup Input. STARTUP coordinates simultaneous soft-start for multiple converters. See the <i>Tracking (STARTUP)</i> section.                                                                                                                                                                                                                                                                         |

| 19         | PGOOD   | Power-Good Output. PGOOD output goes high when SENSE is above V <sub>REF</sub> and STARTUP is high.                                                                                                                                                                                                                                                                                                    |

| 20         | COMP    | Error-Amplifier Output. Connect COMP to the compensation feedback network.                                                                                                                                                                                                                                                                                                                             |

| 21         | FB      | Feedback Regulation Point. Connect to the center tap of a resistive divider from the converter output to AGND to set the output voltage. The FB voltage regulates to the reference voltage.                                                                                                                                                                                                            |

| 22         | SENSE   | Output Voltage Sense. Connect a resistive divider from the converter output to SENSE to AGND to monitor the programmed output voltage. SENSE is compared to the internal reference, V <sub>REF</sub> .                                                                                                                                                                                                 |

| 23         | ILIM    | Valley Current-Limit Set Output. Connect a $25k\Omega$ to $175k\Omega$ resistor, $R_{ILIM}$ , from ILIM to AGND to program the valley current-limit threshold from 50mV to 350mV. ILIM sources $20\mu A$ out to $R_{ILIM}$ . The resulting voltage divided by 10 is the valley current limit. Alternatively, a resistive divider from REG to ILIM to AGND can be used to set the valley current limit. |

## Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                        |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | CS+  | Positive Current-Sense Input. Connect CS+ to the synchronous MOSFET source (connected to PGND).                                                                                                                                                                 |

| 25  | CS-  | Negative Current-Sense Input. Connect CS- to the synchronous MOSFET drain (connected to LX).                                                                                                                                                                    |

| 26  | PGND | Power-Ground Connection. Connect the input filter capacitor's negative terminal, the source of the synchronous MOSFET, and the output filter capacitor's return to PGND. Connect externally to AGND at a single point near the input capacitor return terminal. |

| 27  | DL   | Low-Side Gate-Driver Output. DL is the gate-driver output for the synchronous MOSFET.                                                                                                                                                                           |

| 28  | DREG | Gate-Drive Supply for the Low-Side MOSFET Driver. Connect externally to REG and the anode of the boost diode.                                                                                                                                                   |

| 29  | LX   | Source Connection of the High-Side MOSFET and Drain Connection of the Synchronous MOSFET. Connect the inductor and the negative side of the boost capacitor to LX.                                                                                              |

| 30  | DH   | High-Side Gate-Driver Output. DH drives the gate of the high-side MOSFET.                                                                                                                                                                                       |

| 31  | BST  | High-Side Gate-Driver Supply. Connect BST to the cathode of the boost diode and to the positive terminal of the boost capacitor.                                                                                                                                |

| 32  | REG  | 5V Regulator Output. Bypass with a 2.2µF ceramic capacitor to AGND.                                                                                                                                                                                             |

| EP  | EP   | Exposed Pad. Connect the exposed pad to AGND.                                                                                                                                                                                                                   |

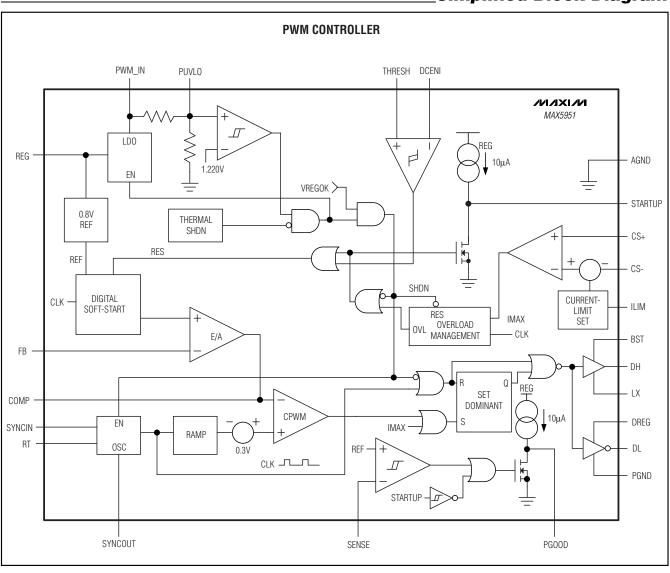

## Detailed Description

The MAX5951 is a PWM, step-down, DC-DC controller. The device operates over the input-voltage range of 8V to 16V or 5V  $\pm10\%$  (VIN = VREG) and provides an adjustable output from 0.8V to 5.5V. The device delivers up to 10A of load current with excellent load-and-line regulation.

The MAX5951 PWM controller utilizes a voltage-mode control scheme for good noise immunity and offers external compensation allowing for maximum flexibility with a wide selection of inductor values and capacitor types. The device operates at a fixed switching frequency that is programmable from 100kHz to 1MHz and can be synchronized to an external clock signal through the SYNC input. The device includes UVLO and digital soft-start. Protection features include valley-mode current limit, hiccup-mode output short-circuit protection, and thermal shutdown.

## PWM Controller

#### **PWM UVLO**

V<sub>IN</sub> must exceed the default PWM UVLO threshold (7V typ) before any PWM operation can commence. The UVLO circuitry keeps the MOSFET drivers, oscillator, and all the internal circuitry shut down to reduce current consumption.

Override the internal PWM UVLO divider by connecting an external resistive divider from IN to PUVLO to AGND. The PUVLO threshold is 1.220V with 122mV hysteresis.

#### **Digital Soft-Start**

The MAX5951 soft-start feature allows the load voltage to ramp up in a controlled manner, eliminating output voltage overshoot. Soft-start begins after  $V_{\rm IN}$  exceeds the UVLO threshold. The soft-start circuitry gradually ramps up the reference voltage. This controls the rate of rise of the output voltage and reduces input surge currents during startup. The soft-start duration is 1024 clock cycles. The output voltage is incremented through 128 equal steps. The output reaches regulation when soft-start is completed, regardless of output capacitance and load.

#### Internal Linear Regulator (REG)

REG is the output terminal of a 5V LDO, which is powered from IN and provides power to the IC. Bypass REG to AGND with a 2.2µF ceramic capacitor. Place the capacitor physically close to the MAX5951 to provide good bypassing. REG is intended for powering only the internal circuitry and should not be used to supply power to external loads.

#### Low-Side MOSFET Driver Supply (DREG)

DREG is the supply input for the low-side MOSFET driver. Connect DREG to REG externally. Adding an RC filter ( $5\Omega$  resistor and 2.2µF ceramic capacitor) from REG to DREG filters out the high peak currents of the MOSFET drivers.

#### **High-Side MOSFET Driver Supply (BST)**

BST supplies the power for the high-side MOSFET drivers. Connect the bootstrap diode from BST to DREG (anode at DREG and cathode at BST). Connect a bootstrap 1µF ceramic capacitor between BST and LX.

#### **MOSFET Gate Drivers (DH, DL)**

The high-side (DH) and low-side (DL) drivers drive the gates of the external n-channel MOSFETs. The drivers' 2A peak source-and-sink current capability provides ample drive to ensure fast rise and fall times of the switching MOSFETs. Short rise and fall times minimize switching losses. For low output-voltage applications where the duty cycle is less than 50%, choose a high-side MOSFET (Q2) with a moderate RDS(ON). Choose a low-side MOSFET (Q1) with a very low RDS(ON).

The gate driver circuitry also provides a break-beforemake time (25ns, typ) to prevent shoot-through currents during transition.

# Oscillator/Synchronization Input (SYNCIN)/ Synchronization Output (SYNCOUT)

Use an external resistor at RT to program the MAX5951 switching frequency from 100kHz to 1MHz.

Choose the appropriate resistor at RT to calculate the desired output switching frequency (fsw):

$f_{SW}(Hz) = (5 \times 10^{10}) / R_{RT}(\Omega)$

Connect an external clock (SYNCOUT from another MAX5950 or MAX5951) at SYNCIN for external clock

synchronization. For proper synchronization, the external frequency must be at least 20% higher than the frequency programmed through the RT input. If SYNCIN is 50% duty cycle, SYNCOUT is shifted by 180°, allowing the reduction of the DC-DC converter input bypass capacitor.

SYNCOUT is a synchronization signal that is used to drive the SYNCIN of a second MAX5950 or MAX5951.

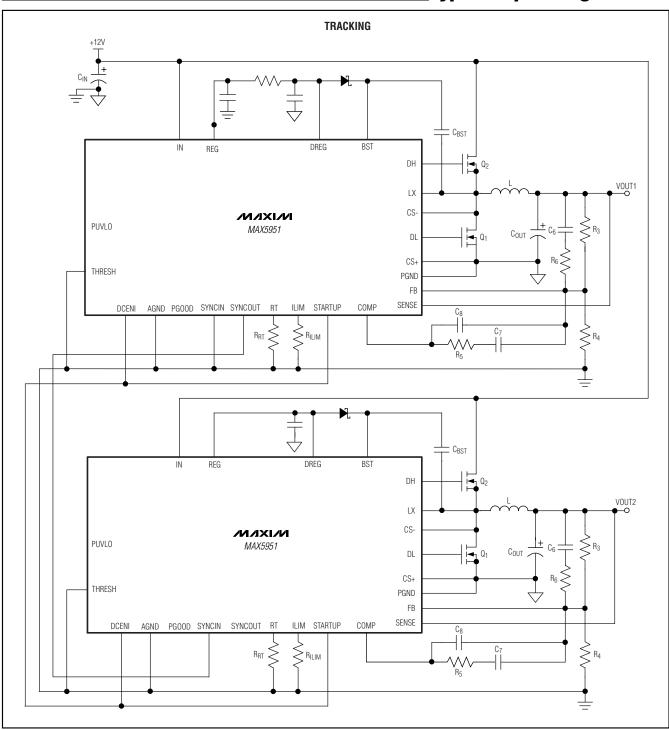

#### Tracking (STARTUP)

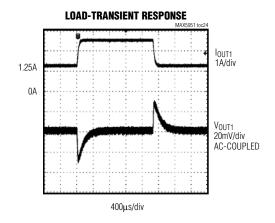

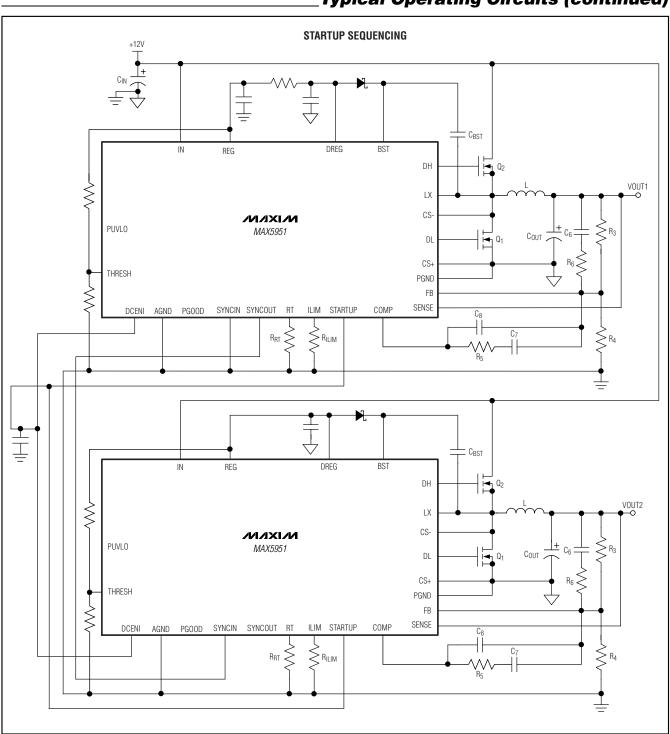

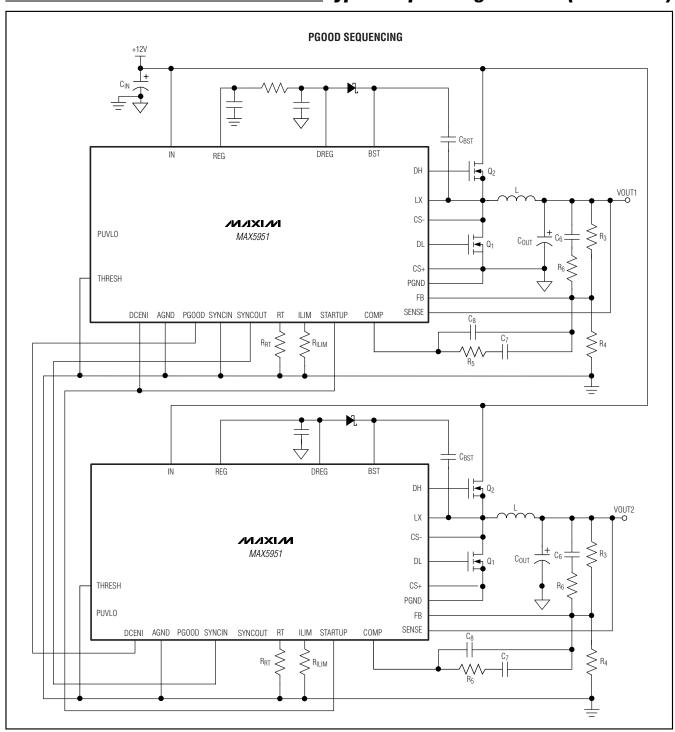

The STARTUP input in conjunction with digital soft-start provides simple ratiometric tracking. When using multiple MAX5950s or MAX5951s, in addition to connecting SYNCIN and SYNCOUT signals appropriately, connect the STARTUP of all the devices together. STARTUP synchonizes the soft-start of all the devices' references, and hence their respective output voltages track ratiometrically. See Figure 1 and the *Typical Operating Circuits*.

The STARTUP input has an internal 10µA pullup current, but can be driven by external logic. When using multiple converters, connect the STARTUP of all the devices together.

#### Startup Sequencing (DCENI, THRESH)

The DCENI input must be above VTHRESH for the PWM controller to start. By connecting the DCENI inputs of multiple devices together and having different start thresholds (VTHRESH\_), the startup of the PWM controllers can be staggered to provide power sequencing. Connect a resistive divider from REG to THRESH to AGND to set the start thresholds of each device. Connect THRESH to AGND to produce a default 1.220V threshold for DCENI. See Figure 1 and the Typical Operating Circuits.

#### Power-Good Sequencing (PGOOD, SENSE)

The PGOOD outputs and DCENI inputs can be daisy-chained to generate power sequencing. The PGOOD output is pulled high when the voltage at SENSE is above  $V_{REF}$  (800mV, typ). Connect a resistive divider from the power-supply output voltage to SENSE to AGND to set the power-good threshold. See Figure 1 and the *Typical Operating Circuits*.

\_\_\_\_\_MIXIM

Figure 1. Tracking, STARTUP Sequencing, and PGOOD Sequencing Configurations

#### **Error Amplifier**

The output of the internal error amplifier (COMP) is available for frequency compensation (see the *Compensation Design Guidelines* section). The inverting input is FB; the output is COMP. The error amplifier has an 80dB open-loop gain and a 2.5MHz GBW product. See the *Typical Operating Characteristics* for the Open-Loop Gain and Phase vs. Frequency graph.

#### **PWM Comparator**

An internal ramp is compared against the output of the error amplifier to generate the PWM signal. The amplitude of the ramp, V<sub>RAMP</sub>, is 1.8V.

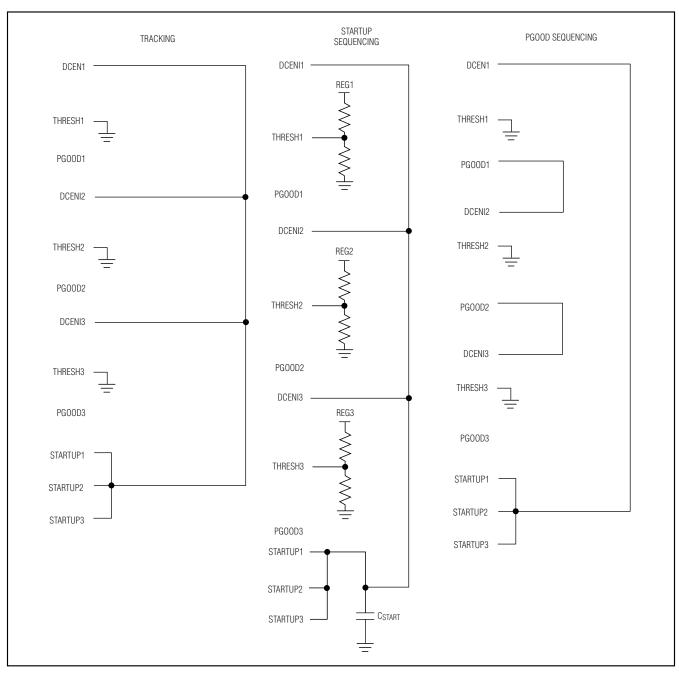

#### Output Short-Circuit Protection (Hiccup Mode)

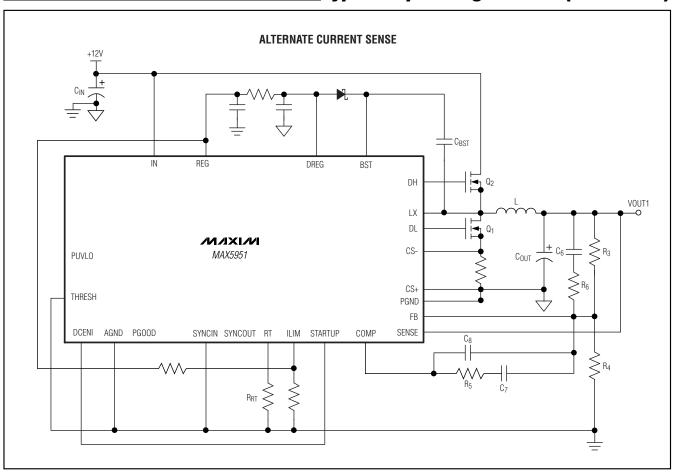

The current-limit circuit employs a lossless valley current-limiting algorithm that uses the MOSFET's on-resistance as the current-sensing element. Once the high-side MOSFET turns off, the voltage across the low-side MOSFET is monitored. If the voltage across the low-side MOSFET (RDS(ON) x INDUCTOR) does not exceed the current-limit threshold, the high-side MOSFET turns on normally at the start of the next cycle. If the voltage across the low-side MOSFET exceeds the current-limit threshold just before the beginning of a new PWM cycle, the controller skips that cycle. During severe overload or short-circuit conditions, the switching frequency of the device appears to decrease because the on-time of the low-side MOSFET extends beyond a clock cycle.

If the current-limit threshold is exceeded for eight cumulative clock cycles (N<sub>CL</sub>), the device shuts down (both DH and DL are pulled low) for 512 clock cycles (hiccup timeout) and restarts with a soft-start sequence. If three consecutive cycles pass without a current-limit event, the

count of NCL is cleared (see Figure 2). Hiccup mode protects against continuous output short circuit.

#### **Thermal-Overload Protection**

The MAX5951 features an integrated thermal-overload protection with temperature hysteresis. Thermal-overload protection limits the total power dissipation in the device and protects it in the event of an extended thermal fault condition. When the die temperature exceeds +135°C, an internal thermal sensor shuts down the device, turning off the power MOSFETs and allowing the die to cool. After the die temperature falls by +15°C, the part restarts with a soft-start sequence.

## PWM Controller Design Procedures

#### **Setting the Undervoltage Lockout**

Connect an external resistive divider from IN to PUVLO to AGND to override the internal PWM UVLO divider. The rising threshold at PUVLO is set to 1.220V with 120mV hysteresis. First select the PUVLO to AGND resistor (R2), then calculate the resistor from IN to PUVLO (R1) using the following equation:

$$R1 = R2 \times \left[ \frac{V_{IN}}{V_{PUVLO}} - 1 \right]$$

where  $V_{IN}$  is the input voltage at which the converter needs to turn on,  $V_{PUVLO} = 1.220V$ , and R2 is chosen to be less than  $20k\Omega$ . See Figure 3.

Leave PUVLO unconnected for the default PWM UVLO threshold. In this case, an internal voltage-divider monitors the supply voltage at IN and allows startup when IN rises above 7V (typ).

Figure 2. Hiccup Block Diagram

Figure 3. External PWM UVLO Divider

#### **Setting the Output Voltage**

Connect a resistive divider from OUT to FB to AGND to set the output voltage. First, calculate the resistor from OUT to FB using the guidelines in the *Compensation Design Guidelines* section. Once R3 is known, calculate R4 using the following equation:

$$R4 = \frac{R3}{\left[\frac{V_{OUT}}{V_{FB}} - 1\right]}$$

where  $V_{FB} = 0.8V$ .

#### **Inductor Selection**

Three key inductor parameters must be specified for operation with the MAX5951: inductance value (L), peak inductor current (IPEAK), and inductor saturation current (ISAT). The minimum required inductance is a function of operating frequency, input-to-output voltage differential, and the peak-to-peak inductor current (ΔIP-P). Higher  $\Delta$ IP-P allows for a lower inductor value. A lower inductance value minimizes size and cost and improves largesignal and transient response, but reduces efficiency due to higher peak currents and higher peak-to-peak output voltage ripple for the same output capacitor. A higher inductance increases efficiency by reducing the ripple current; however, resistive losses due to extra wire turns can exceed the benefit gained from lower ripple current levels especially when the inductance is increased without also allowing for larger inductor dimensions. A good rule of thumb is to choose  $\Delta I_{P-P}$ egual to 30% of the full-load current. Calculate the inductor using the following equation:

$$L = \frac{V_{OUT}(V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times \Delta I_{P-P}}$$

V<sub>IN</sub> and V<sub>OUT</sub> are typical values so that efficiency is optimum for typical conditions. The switching frequency is programmable between 100kHz and 1000kHz (see the *Oscillator/Synchronization Input (SYNCIN)/Synchronization Output (SYNCOUT)* section). The peak-to-peak inductor current, which reflects the peak-to-peak output ripple, is worst at the maximum input voltage. See the output capacitor selection section to verify that the worst-case output current ripple is acceptable. The inductor saturation current (ISAT) is also important to avoid runaway current during continuous output short-circuit conditions. Select an inductor with an ISAT specification higher than the maximum peak current.

#### **Input Capacitor Selection**

The discontinuous input current of the buck converter causes large input ripple currents; therefore, the input capacitor must be carefully chosen to withstand the input ripple current and maintain the input voltage ripple within design requirements. The total voltage ripple is the sum of  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the input capacitor), which peaks at the end of the on cycle. Calculate the input capacitance and ESR required for a specified ripple using the following equations:

$$\begin{aligned} \text{ESR} &= \frac{\Delta V_{\text{ESR}}}{\left(I_{\text{LOAD(MAX)}} + \frac{\Delta I_{P-P}}{2}\right)} \\ C_{\text{IN}} &= \frac{I_{\text{LOAD(MAX)}} \times \left(\frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)}{\Delta V_{\text{O}} \times f_{\text{SW}}} \end{aligned}$$

where

$$\Delta I_{P-P} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times f_{SW} \times L}$$

$I_{LOAD(MAX)}$  is the maximum output current,  $\Delta I_{P-P}$  is the peak-to-peak inductor current, and  $f_{SW}$  is the switching frequency.

The MAX5951 includes UVLO hysteresis to avoid possible unintentional chattering during turn-on. Use additional bulk capacitance if the input source impedance is high. When the input voltage is near the UVLO, additional input capacitance helps avoid possible undershoot below the UVLO threshold during transient loading.

## **Output Capacitor Selection**

The allowed output-voltage ripple and the maximum deviation of the output voltage during load steps determine the required output capacitance and its ESR. The output ripple is mainly composed of  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the voltage drop across the ESR of the output capacitor). The equations for calculating the peak-to-peak output-voltage ripple are:

$$\Delta V_{Q} = \frac{\Delta I_{P-P}}{8 \times C_{OUT} \times f_{SW}}$$

$$\Delta V_{ESR} = ESR \times \frac{\Delta I_{P-P}}{2}$$

$\Delta V_{ESR}$  and  $\Delta V_Q$  are not directly additive since they are out of phase from each other. If using ceramic capacitors, which generally have low ESR,  $\Delta V_Q$  dominates. If using electrolytic capacitors,  $\Delta V_{ESR}$  dominates.

The allowable deviation of the output voltage during load transients also affects the choice of capacitance. its ESR, and its equivalent series inductance (ESL). The output capacitor supplies the load current during a load step until the controller responds with a greater duty cycle. The response time (tRESPONSE) depends on the closed-loop bandwidth of the converter (see the Compensation Design Guidelines section). The resistive drop across the output capacitor's ESR, the drop across the capacitor's ESL, and the capacitor discharge cause a voltage droop during the load-step. Use a combination of low-ESR tantalum/aluminum electrolyte and ceramic capacitors for better load transient and voltage ripple performance. Surface-mount capacitors and capacitors in parallel help reduce the ESL. Keep maximum output-voltage deviation below the tolerable limits of the electronics being powered. Use the following equations to calculate the required ESR, ESL, and capacitance value during a load step:

$$ESR = \frac{\Delta V_{ESR}}{|_{STEP}}$$

$$C_{OUT} = \frac{|_{STEP} \times t_{RESPONSE}}{\Delta V_{Q}}$$

$$ESL = \frac{\Delta V_{ESL} \times t_{STEP}}{|_{STEP}}$$

where ISTEP is the load step, tSTEP is the rise time of the load step, and tRESPONSE is the response time of the controller.

#### Setting the Current Limit

Connect a  $25 k\Omega$  to  $175 k\Omega$  resistor,  $R_{ILIM}$ , from ILIM to AGND to program the valley current-limit threshold between 50mV and 350mV. ILIM sources  $20 \mu A$  out to  $R_{ILIM}$ . The resulting voltage divided by 10 is the valley current-limit threshold.

The MAX5951 uses a valley current-sense method for current limiting. The voltage drop across the low-side MOSFET due to its on-resistance is used to sense the inductor current. The voltage drop across the low-side MOSFET at the valley point and at  $I_{LOAD(MAX)}$  is:

$$V_{VALLEY} = R_{DS(ON)}(T) \times \left(I_{LOAD(MAX)} - \frac{\Delta I_{P-P}}{2}\right)$$

RDS(ON) is the on-resistance of the low-side MOSFET, which is temperature dependent,  $I_{LOAD(MAX)}$  is the maximum DC load current, and  $\Delta I_{P-P}$  is the peak-to-peak inductor current.

The 20µA current source, ILIM reference current, has a temperature coefficient of 3333ppm/°C. This allows the valley current-limit threshold:

$$\frac{R_{ILIM} \times 20 \mu A(T)}{10}$$

to track and compensate for the increase in the synchronous MOSFET's RDS(ON) with increasing temperature. MOSFETs typically have a temperature coefficient range within 3000ppm/°C to 7000ppm/°C. Refer to the MOSFET data sheet for a device-specific temperature coefficient.

At a given temperature, the calculated  $V_{VALLEY}$  must be less than the minimum valley current-limit threshold specified.

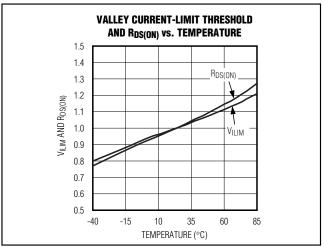

Figure 4 illustrates the effect of MAX5951 ILIM reference current temperature coefficient to compensate for the variation of the MOSFET RDS(ON) over the operating junction temperature range.

#### **Power MOSFET Selection**

When selecting the MOSFETs, consider the total gate charge, RDS(ON), power dissipation, the maximum drain-to-source voltage, package thermal impedance, and desired current limit. The product of the MOSFET gate charge and on-resistance is a figure of merit, with a lower number signifying better performance. Choose MOSFETs optimized for high-frequency switching applications. The average gate-drive current from the MAX5951's output is proportional to the frequency and gate charge required to drive the MOSFET. The power dissipated in the MAX5951 is proportional to the input voltage and the average drive current (see the *Power Dissipation* section).

Figure 4. Current-Limit Threshold and RDS(ON) vs. Temperature

16 \_\_\_\_\_\_\_/N/JXI/M

#### **Compensation Design Guidelines**

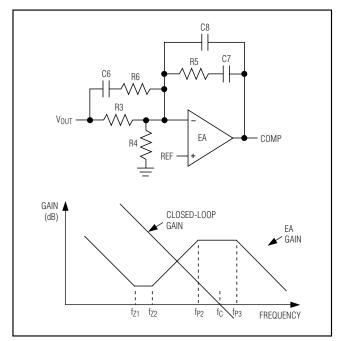

The MAX5951 uses a voltage-mode control scheme that regulates the output voltage by comparing the error amplifier output (COMP) with an internal ramp to produce the required duty cycle. The output lowpass LC filter creates a double pole at the resonant frequency, which has a gain drop of -40dB/decade. The compensation network must compensate for this gain drop and phase shift in order to achieve a stable closed-loop system.

The basic regulator loop consists of a power modulator, an output feedback divider, and a voltage-error amplifier. The power modulator has a DC gain set by  $V_{IN}/V_{RAMP}$ , with a double pole and a single zero set by the output inductance (L), the output capacitance (COUT), and its equivalent series resistance (ESR). Below are equations that define the power modulator:

$$\begin{aligned} G_{MOD(DC)} &= \frac{V_{IN}}{V_{RAMP}} \\ f_{LC} &= \frac{1}{2\pi\sqrt{L \times C_{OUT}}} \\ f_{ZESR} &= \frac{1}{2\pi \times C_{OUT} \times R_{ESR}} \end{aligned}$$

GAIN (dB)

C10SED-LOOP

GAIN

C10SED-LOOP

GAIN

EA

GAIN

FREQUENCY

Figure 5. Error-Amplifier Compensation Circuit (Closed-Loop and Error-Amplifier Gain Plot) for Ceramic Capacitors

The switching frequency is programmable between 100kHz and 1000kHz by an external resistor at RT. The crossover frequency (fc), which is the frequency when the closed-loop gain is equal to unity, should be set to fsw / 10 or fgBw / 25, whichever is lower.

The error amplifier must provide a gain-and-phase boost to compensate for the rapid gain-and-phase loss from the LC double pole. This is accomplished by utilizing type 3 compensation (see Figures 5 and 6) that introduces two zeros and three poles into the control loop. The error amplifier has a low-frequency pole (fp1) at the origin; two zeros at:

$$f_{Z1} = \frac{1}{2\pi \times R5 \times C7}$$

and:

$$f_{Z2} = \frac{1}{2\pi \times R3 \times C6}$$

and higher frequency poles at:

$$f_{P2} = \frac{1}{2\pi \times R6 \times C6}$$

and:

$$f_{P3} = \frac{1}{2\pi \times R5 \times C8}$$

Figure 6. Error-Amplifier Compensation Circuit (Closed-Loop and Error-Amplifier Gain Plot) for Higher ESR Output Capacitors

#### Compensation when fc < fzesr

Figure 5 shows the error-amplifier feedback, as well as its gain response for circuits that use low-ESR output capacitors (ceramic). In this case, fc occurs before fzesr.

fz<sub>1</sub> is set to 0.5 x f<sub>LC</sub> and fz<sub>2</sub> is set to f<sub>LC</sub> in order to compensate for the gain-and-phase loss due to the double pole. Choose the inductor (L) and output capacitor (C<sub>OUT</sub>) as described in the *Inductor Selection* and *Output Capacitor Selection* sections.

Pick a value for the feedback resistor R5 in Figure 5 (values between  $1k\Omega$  and  $10k\Omega$  are adequate). C7 is then calculated as:

$$C7 = \frac{1}{2\pi \times 0.5 \times f_{1,C} \times R5}$$

fC occurs between fz2 and fp2. The circuit is implemented with C7 >> C8 and R3 >> R6, in which case, the error amplifier gain ( $G_{EA}$ ) at fC is due primarily to C6 and R5. Therefore:

$$G_{EA(fc)} = 2\pi \times f_C \times C6 \times R5$$

The modulator gain at fc is:

$$G_{MOD(fC)} = \frac{G_{MOD(DC)}}{(2\pi)^2 \times L \times C_{OUT} \times f_C^2}$$

Since  $GEA(fC) \times GMOD(fC) = 1$ , C6 is calculated by:

$$C6 = \frac{f_C \times L \times C_{OUT} \times 2\pi}{R5 \times G_{MOD(DC)}}$$

R3 is then calculated as:

$$R3 \approx \frac{1}{2\pi \times f_{LC} \times C6}$$

fp2 is set at 1/2 the switching frequency (fsw). R6 is then calculated by:

$$R6 = \frac{1}{2\pi \times C6 \times 0.5 \times f_{SW}}$$

fp3 is set at 5 x fc. Therefore, C8 is calculated as:

$$C8 = \frac{1}{2\pi \times R5 \times 5 \times f_C}$$

#### Compensation when fc > fzesr

For larger ESR capacitors such as tantalum and aluminum electrolytic, fzesr can occur before fc. If fc > fzesr, then fc occurs between fp2 and fp3. fz1 and fz2 remain the same as before; however, fp2 is now set equal to fzesr. The output capacitor's ESR zero frequency is higher than flc but lower than the closed-loop crossover frequency. The equations that define the error amplifier's poles and zeros (fz1, fz2, fp1, fp2, and fp3) are the same as before. However, fp2 is now lower than the closed-loop crossover frequency. Figure 5 shows the error-amplifier feedback, as well as its gain response for circuits that use higher ESR output capacitors (tantalum, aluminum electrolytic, etc.).

Pick a value for feedback resistor R5 in Figure 5 (values between  $1k\Omega$  and  $10k\Omega$  are adequate). C7 is then calculated as:

$$C7 = \frac{1}{2\pi \times 0.5 \times f_{LC} \times R5}$$

The circuit is implemented with C7 >> C8 and R3 >> R6, in which case the error-amplifier gain between fp2 and fp3 is approximately equal to:

The modulator gain at fc is:

$$G_{MOD(fC)} = \frac{G_{MOD(DC)}}{(2\pi)^2 \times L \times C_{OUT} \times f_C^2}$$

Since  $G_{EA(fC)} \times G_{MOD(fC)} = 1$ , R6 can then be calculated as:

$$R6 \approx \frac{R5 \times G_{MOD(DC)}}{(2\pi)^2 \times L \times C_{OUT} \times f_C^2}$$

fp2 is set to fzesr. C6 is then calculated as:

$$C6 = \frac{C_{OUT} \times ESR}{R6}$$

R3 is then calculated as:

$$R3 \approx \frac{1}{2\pi \times \int_{C} \times C6}$$

f<sub>P3</sub> is set at 5 x f<sub>C</sub>. Therefore, C8 is calculated as:

$$C8 = \frac{1}{2\pi \times R5 \times 5 \times f_{C}}$$

## PWM Controller Applications Information

#### **Power Dissipation**

The 32-pin TQFN thermally enhanced package can dissipate 2.7W. Calculate power dissipation in the MAX5951 as a product of the input voltage and the total REG output current (IREG). IREG includes quiescent current (IQ) and gate drive current (IDREG):

$$I_{REG} = I_{Q} + [f_{SW} \times (Q_{G1} + Q_{G2})]$$

where Q<sub>G1</sub> and Q<sub>G2</sub> are the total gate charge of the low-side and high-side external MOSFETs. f<sub>SW</sub> is the switching frequency of the converter, and I<sub>Q</sub> is the quiescent current of the device at the switching frequency.

Use the following equation to calculate the maximum power dissipation (P<sub>DMAX</sub>) in the chip at a given ambient temperature (T<sub>A</sub>):

$P_{DMAX} = 34.5 \times (150 - T_{A})$

#### **PC Board Layout Guidelines**

Use the following guidelines to lay out the switching voltage regulator:

- Place the IN and DREG bypass capacitors close to the MAX5951 PGND pin. Place the REG bypass capacitor close to the AGND pin.

- 2) Minimize the area and length of the high-current loops from the input capacitor, upper switching MOSFET, inductor, and output capacitor back to the input capacitor negative terminal.

- 3) Keep short the current loop formed by the synchronous switching MOSFET, inductor, and output capacitor.

- 4) Keep AGND and PGND isolated and connect them at one single point close to the negative terminal of the input filter capacitor.

- 5) Run the current-sense lines CS+ and CS- close to each other to minimize the loop area.

- 6) Avoid long traces between the REG/DREG bypass capacitors, driver output of the MAX5951, MOSFET gates, and PGND. Minimize the loop formed by the REG bypass capacitors, bootstrap diode, bootstrap capacitor, the MAX5951, and the upper MOSFET gate.

- Place the bank of output capacitors close to the load.

- 8) Distribute the power components evenly across the board for proper heat dissipation.

- Provide enough copper area at and around the switching MOSFETs and inductor to aid in thermal dissipation.

- 10) Use 2oz copper to keep the trace inductance and resistance to a minimum. Thin copper PC boards can compromise efficiency since high currents are involved in the application. Also, thicker copper conducts heat more effectively, thereby reducing thermal impedance.

## Simplified Block Diagram

20 \_\_\_\_\_\_/VIXI/M

## **Typical Operating Circuits**

## \_Typical Operating Circuits (continued)

22 \_\_\_\_\_\_\_/VI/XI/M

# Typical Operating Circuits (continued)

## Typical Operating Circuits (continued)

\_\_\_\_\_Chip Information

PROCESS: BiCMOS

24 \_\_\_\_\_\_\_/VIXI/M

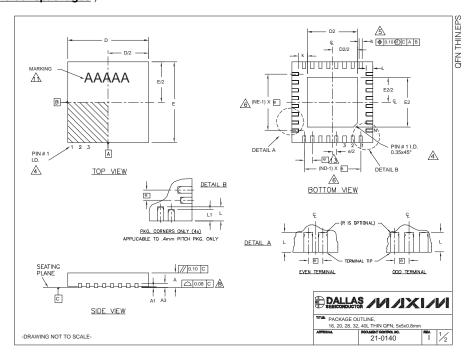

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|        | COMMON DIMENSIONS |        |      |           |       |            |      |           |      |           |       |            |           |      |     |

|--------|-------------------|--------|------|-----------|-------|------------|------|-----------|------|-----------|-------|------------|-----------|------|-----|

| PKG.   | 1                 | 6L 5x  | 5    | 2         | OL 5  | <b>(</b> 5 | 2    | 8L 5      | ι5   | 3         | 2L 5> | ι <b>5</b> | 4         | 0L 5 | :5  |

| SYMBOL | MIN.              | NOM.   | MAX. | MIN.      | NOM.  | MAX.       | MIN. | NOM.      | MAX. | MIN.      | NOM.  | MAX.       | MIN.      | NOM. | MAX |

| Α      | 0.70              | 0.75   | 0.80 | 0.70      | 0.75  | 0.80       | 0.70 | 0.75      | 0.80 | 0.70      | 0.75  | 0.80       | 0.70      | 0.75 | 0.8 |

| A1     | 0                 | 0.02   | 0.05 | 0         | 0.02  | 0.05       | 0    | 0.02      | 0.05 | 0         | 0.02  | 0.05       | 0         | 0.02 | 0.0 |

| A3     | 0.                | 20 RE  | F.   | 0.        | 20 RE | F.         | 0.   | 20 RE     | F.   | 0.        | 20 RE | F.         | 0.20 REF. |      |     |

| b      | 0.25              | 0.30   | 0.35 | 0.25      | 0.30  | 0.35       | 0.20 | 0.25      | 0.30 | 0.20      | 0.25  | 0.30       | 0.15      | 0.20 | 0.2 |

| D      | 4.90              | 5.00   | 5.10 | 4.90      | 5.00  | 5.10       | 4.90 | 5.00      | 5.10 | 4.90      | 5.00  | 5.10       | 4.90      | 5.00 | 5.1 |

| E      | 4.90              | 5.00   | 5.10 | 4.90      | 5.00  | 5.10       | 4.90 | 5.00      | 5.10 | 4.90      | 5.00  | 5.10       | 4.90      | 5.00 | 5.1 |

| е      | 0                 | .80 BS | SC.  | 0.65 BSC. |       | 0.50 BSC.  |      | 0.50 BSC. |      | 0.40 BSC. |       |            |           |      |     |

| k      | 0.25              | -      |      | 0.25      | -     | -          | 0.25 |           |      | 0.25      |       |            | 0.25      | 0.35 | 0.4 |

| L      | 0.30              | 0.40   | 0.50 | 0.45      | 0.55  | 0.65       | 0.45 | 0.55      | 0.65 | 0.30      | 0.40  | 0.50       | 0.40      | 0.50 | 0.6 |

| L1     | -                 | -      | -    | -         | -     | -          | -    | -         | -    | -         | -     | -          | 0.30      | 0.40 | 0.5 |

| N      |                   | 16     |      |           | 20    |            | 28   |           | 32   |           |       | 40         |           |      |     |

| ND     | 4                 |        |      |           | 5     |            |      | 7         |      | 8         |       |            |           | 10   |     |

| NE     | 4                 |        | 5    |           | 7     |            | 8    |           |      | 10        |       |            |           |      |     |

| JEDEC  |                   | WHHE   | 3    | ,         | WHHC  |            | V    | WHHD-1    |      | WHHD-2    |       |            |           |      |     |

| IOTES: |  |

|--------|--|

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESO 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- $\underline{ \begin{tabular}{ll} \triangle\\ 0.25\mbox{ mm}\mbox{ APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25\mbox{ mm}\mbox{ AND }0.30\mbox{ mm}\mbox{ FROM TERMINAL TIP.} \end{tabular}$

- AND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- ⚠ COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR

T2855-3 AND T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6.

ADD T2855-6

- WARPAGE SHALL NOT EXCEED 0.10 mm

- MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 12. NUMBER OF LEADS SHOWN ARE FOUNDED EXCIPCE SHEET.

LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "0", ±0.05.

| DALLA SEMICONDUCTO | \$ /VI/JX                               |      | VI  |

|--------------------|-----------------------------------------|------|-----|

| ™LE PACKAGE C      |                                         |      |     |

| 16, 20, 28, 3      | <ol><li>40L THIN QFN, 5x5x0.8</li></ol> | mm   |     |

| APPROVAL           | DOCUMENT CONTROL NO.                    | REV. | 2/  |

|                    | 21-0140                                 | -1   | 1/2 |

EXPOSED PAD VARIATIONS MIN. NOM. MAX. MIN. NOM. MAX. ±0.15

T4055-1 3.20 3.30 3.40 3.20 3.30 3.40

T1655N-1 3.00 T2055-4

NO NO

NO

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2006 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products, Inc.