Data Sheet, V 2.2, June 2007

# SAK-CIC310-OSMX2HT FlexRay Communication Controller IFLEX Step A11

## Microcontrollers

Never stop thinking

Edition 2007-06 Published by Infineon Technologies AG 81726 München, Germany

© Infineon Technologies AG 2007. All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Data Sheet, V 2.2, June 2007

# SAK-CIC310-OSMX2HT FlexRay Communication Controller IFLEX Step A11

## Microcontrollers

Never stop thinking

Downloaded from **Elcodis.com** electronic components distributor

| TriCore <sup>®</sup> , C166 <sup>®</sup> , Infineon <sup>®</sup> , Infineon Technologies <sup>®</sup> , $$ m, and GPTA <sup>®</sup> are |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| trademarks of Infineon Technologies AG.                                                                                                 |

| FlexRay <sup>™</sup> and the FlexRay logo                                                                                               |

| Consortium.                                                                                                                             |

| We Listen to Your Comments                                                                                                              |

| Any information within this document that you feel is wrong, unclear or missing at all?                                                 |

Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

| 1                                                 | Summary of Features                                                                                                                                           | . 7                  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4              | Functional Description         MLI Host Link (Option One)         SSC Host Link (Option Two)         Parallel Host Link (Option Three)         DMA Controller | 10<br>11<br>13       |

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3 | General Device Information Block Diagram Pin Definition and Functions Package Outline Pin Description Ordering Information                                    | 16<br>19<br>19<br>20 |

| <b>4</b><br>4.1<br>4.1.1                          | Electrical Parameters                                                                                                                                         | 43                   |

| 4.1.2                                             | Pad Driver and Input Classes Definitions                                                                                                                      |                      |

| 4.1.3                                             | Absolute Maximum Ratings                                                                                                                                      |                      |

| 4.1.4                                             | Operating Conditions                                                                                                                                          |                      |

| 4.2                                               | DC Parameters                                                                                                                                                 |                      |

| 4.2.1                                             | Input/Output Characteristics                                                                                                                                  |                      |

| 4.2.2                                             | External Clock Drive                                                                                                                                          |                      |

| 4.2.3                                             | Power Supply Current                                                                                                                                          | 49                   |

| 4.3                                               | AC Characteristic Targets                                                                                                                                     | 50                   |

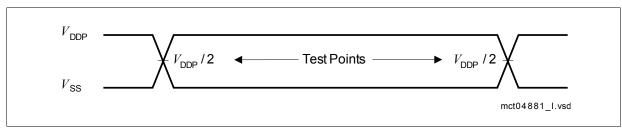

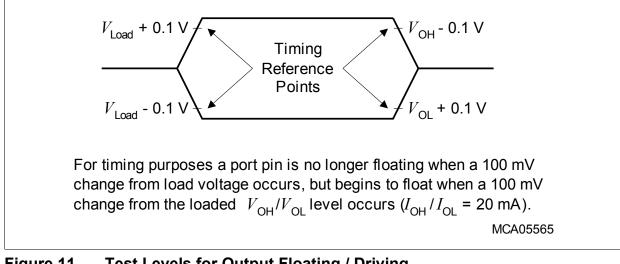

| 4.3.1                                             | Testing Waveforms                                                                                                                                             |                      |

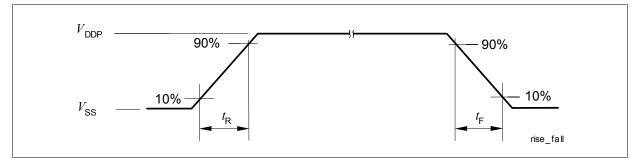

| 4.3.2                                             | Output Rise/Fall Times                                                                                                                                        | 51                   |

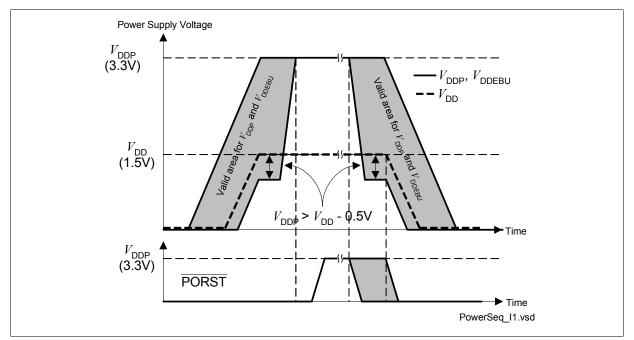

| 4.3.3                                             | Power Sequencing                                                                                                                                              | 52                   |

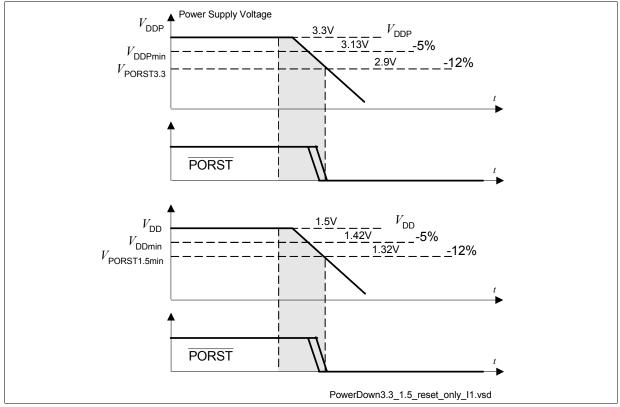

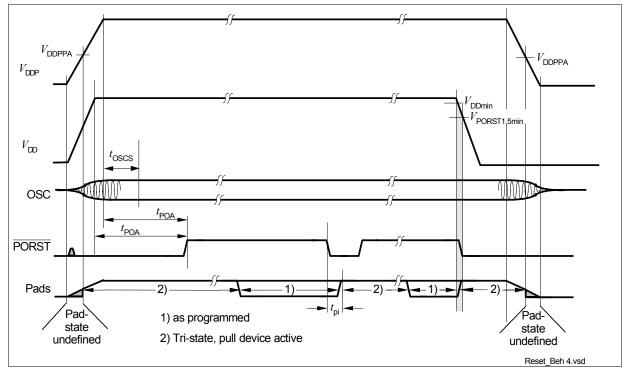

| 4.3.4                                             | Power, Pad and Reset Timing                                                                                                                                   | 53                   |

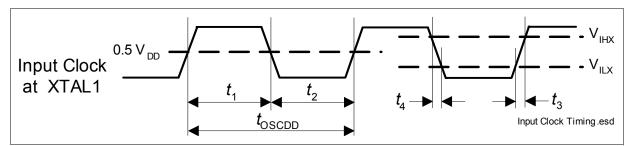

| 4.3.5                                             | Input Clock Timing                                                                                                                                            | 55                   |

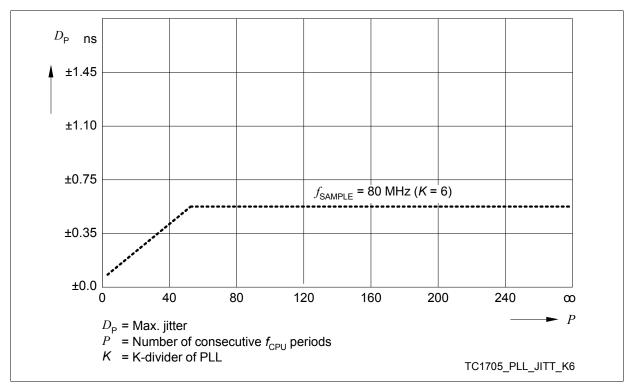

| 4.3.6                                             | Phase Locked Loop (PLL)                                                                                                                                       | 56                   |

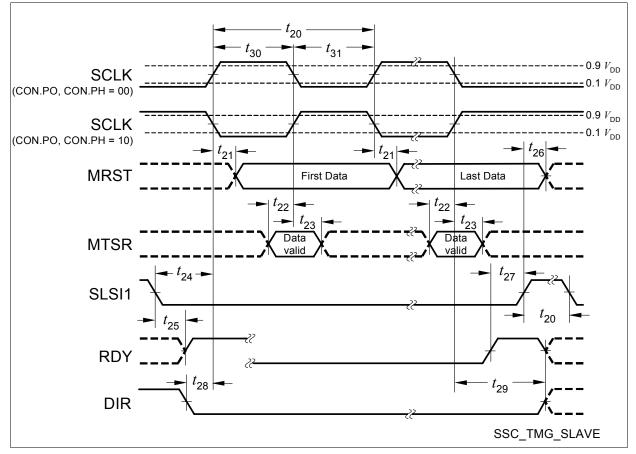

| 4.3.7                                             | Synchronous Serial Channel (SSC) Slave Mode Timing                                                                                                            | 58                   |

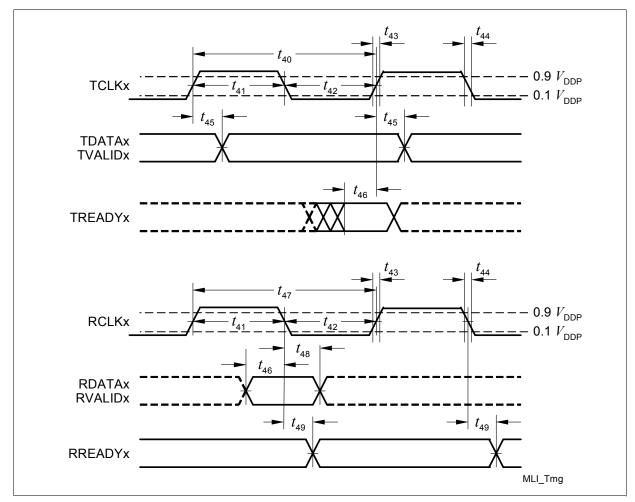

| 4.3.8                                             | MLI Interface Timing                                                                                                                                          | 60                   |

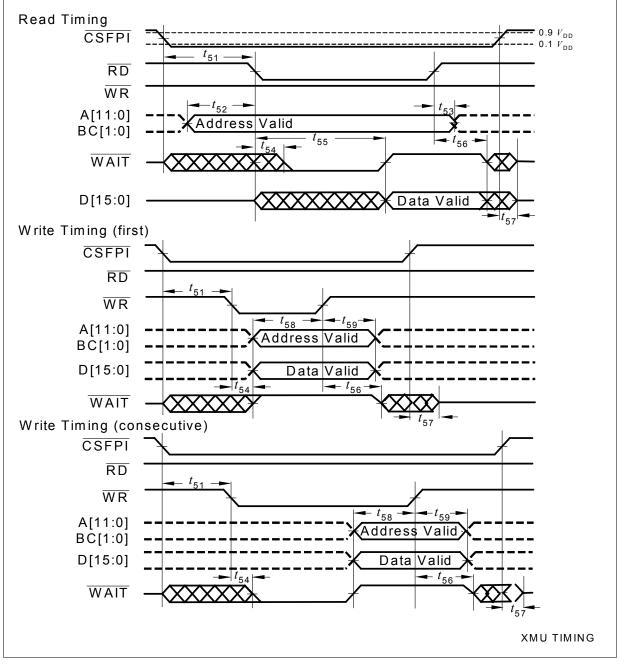

| 4.3.9                                             | XMU External Access Timing                                                                                                                                    | 62                   |

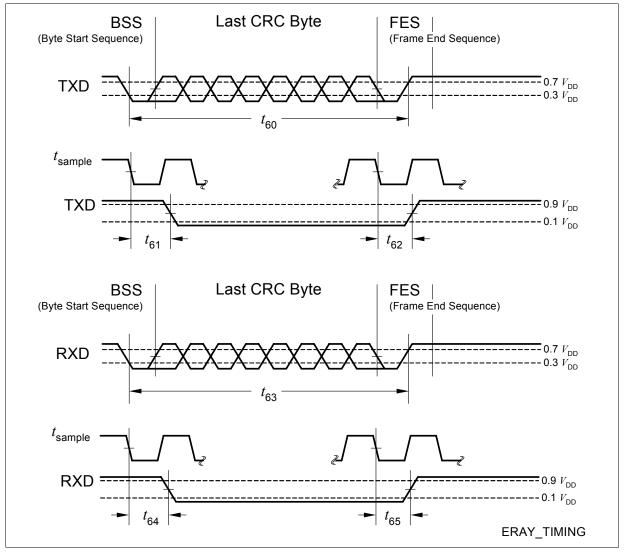

| 4.3.10                                            | ERAY Interface Timing                                                                                                                                         |                      |

| 4.4                                               | Package and Reliability                                                                                                                                       |                      |

| 4.4.1                                             | Package Parameters (PG-TQFP-64)                                                                                                                               | 66                   |

| 4.4.2                                             | Package Outline                                                                                                                                               |                      |

| 4.4.3                                             | Quality Declarations                                                                                                                                          |                      |

| 4.4.4                                             | Thermal Considerations                                                                                                                                        | 68                   |

# FlexRay Communication Controller IFLEX

### SAK-CIC310-OSMX2HT

## **1** Summary of Features

The major functions supported by the SAK-CIC310-OSMX2HT are summarized in this section.

- A powerful FlexRay v2.1 Protocol Controller

- Certified to be conform with FlexRay protocol specification v2.1

- Data rates of up to 10 MBit/s on each channel

- Up to 128 message buffers configurable

- 8 Kbyte of Message RAM for storage of e.g. 128 message buffers with maximum

48 Byte data field or up to 30 messages with 254 Byte data field

- Configuration of message buffers with different payload lengths

- One configurable receive FIFO

- Each message buffer can be configured as Receive Buffer, as Transmit Buffer, or as part of the receive FIFO

- Host access to message buffers via Input and Output Buffer.

Input Buffer: holds message to be transferred to the Message RAM

Output Buffer: holds message read from the Message RAM

- Filtering for frame ID, channel ID, and cycle counter

- Network Management supported

- Two Channels enabling one redundant FlexRay Bus

- All data formats are little-endian

- Independent 8-Channel DMA Controller

- 8 selectable request inputs per DMA channel

- Programmable priority of DMA channels within the DMA sub-block (2 levels)

- Software and hardware DMA request generation

- Hardware requests by selected peripherals

- Individually programmable operation modes for each DMA channel

- Single Mode: stops and disables DMA channel after a predefined number of DMA transfers

- Continuous Mode: DMA channel remains enabled after a predefined number of DMA transfers; DMA transaction can be repeated.

- Programmable address modification

- Support of circular buffer addressing mode

- Programmable data width of a DMA transaction: 8-bit, 16-bit, or 32-bit

- Individual register set for each DMA channel

- Source and destination address register

- Channel control and status register

- Transfer count register

Downloaded from Elcodis.com electronic components distributor

### **Summary of Features**

- Flexible interrupt generation

- 16-bit External Memory Interface Unit (XMU)

- 16-bit wide data bus (D[15:0])

- Automatic data assembly/disassembly operation

- Data width of external bus master can be 8-bit or 16-bit

- 13-bit wide address bus (A[12:0])

- Address extension mechanism to 32-bit

- Read (RD) and write (WR) Bus control signal

- External synchronous/asynchronous wait state bus control signal (WAIT)

- External master chip select (CSFPI) to access on-chip devices connected to the crossbar switch

- High performing on-chip crossbar bus structure

- 32-bit crossbar slave interface for FlexRay

- 32-bit crossbar slave interface for Ports and System Control

- 32-bit crossbar slave interface for MLI communication

- 32-bit crossbar slave interface for MLI and DMA peripheral

- 32-bit crossbar master interface for Host Communication Interfaces

- 32-bit crossbar master interface for DMA

- Versatile High-Speed Synchronous Serial Channels (SSC) for Host Communication

- Full-duplex or half-duplex operation

- Automatic half-duplex pad control

- SSC supports proprietary protocol to drive an integrated move engine

- Maximum Master Mode baud rate:  $f_{SSC}$  / 2 Maximum baud rate (master mode) of 40 MBit/s (@ 80 MHz module clock)

- Maximum Slave Mode baud rate:  $f_{SSC}$  / 4 Maximum baud rate (slave mode) of 20 MBit/s (@ 80 MHz module clock)

- Versatile High-Speed Micro Link interfaces (MLI) for serial inter-processor communication and Host Communication

- Fully transparent read/write access supported (including remote programming)

- Complete address range of target controller available

- Special protocol to transfer data, address offset, or address offset and data

- Error control using a parity bit

- 32-bit, 16-bit, and 8-bit data transfers

- Address offset width: from 1 to 16 bit

- Baud rate: f<sub>MLI</sub> / 2 (symmetric shift clock approach), baud rate definition by the corresponding fractional divider Maximum baud rate of 40 MBit/s (@ 80 MHz module clock)

- Full automotive temperature range: -40°C to +125°C

- 26 digital general purpose I/O lines, 20 digital general purpose input lines

- Digital I/O ports with 3.3 V capability

- Clock Generation Unit with PLL

- Core supply voltage of 1.5 V

- I/O voltage of 3.3 V

Downloaded from Elcodis.com electronic components distributor

### **Summary of Features**

• One Package Option only (PG-TQFP-64)

As the FlexRay Protocol Controller is on a separate chip, the so called standalone Communication Controller, the access is handled via serial or parallel communication links. These three types of link options are discussed in the following chapter.

### 2 Functional Description

The SAK-CIC310-OSMX2HT IC is supposed to be connected to devices of the Infineon AUDO-NG 32bit microcontroller device family. The connection has to be done in a way that today's AUDO-NG 32-bit microcontroller MLI, ASC, or SSC interfaces remain untouched. On the other hand the FlexRay Communication controller requires communication bandwidth of 10 MBit/s and more to download the full message bandwidth of the two FlexRay links. Beside this requirement additionally the SAK-CIC310-OSMX2HT needs to be operative with a minimum pin account and area. Therefore two small serial interfaces (MLI, SSC) and an additional parallel interface are implemented.

For the SAK-CIC310-OSMX2HT concept three options are implemented in parallel to minimize the risk and to increase the options for a system composed out of the SAK-CIC310-OSMX2HT and an AUDO-NG 32-bit microcontroller device and still to handle the application requirements. These three interfaces are the SSC Interface (usable as SPI and synchronous ASC Interface), a parallel Interface, and the Micro Link Interface (MLI). All AUDO-NG 32-bit microcontroller family member are equipped with serial interfaces (ASC and SSC).

Three options are presented for the system solution based on these three communication interfaces.

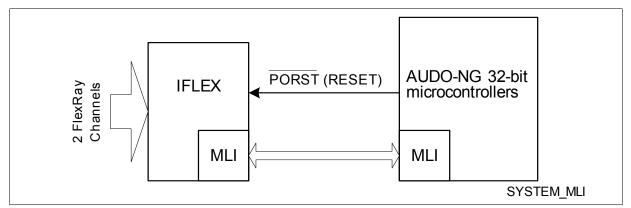

### 2.1 MLI Host Link (Option One)

The first and preferred option is to connect the SAK-CIC310-OSMX2HT via the MLI interface to the AUDO-NG 32bit microcontroller family. The MLI has the advantage realizing a fast and smart communication interface with a low pin count and SPI like SW protocol handling. The transmission rate is high enough to handle the data traffic that is generated from the SAK-CIC310-OSMX2HT FlexRay Protocol engine to the AUDO-NG 32-bit microcontroller device and vice versa.

### **MLI Feature Set**

- Serial communication from the MLI transmitter to MLI receiver of another controller

- Fully transparent read/write access supported (including remote programming)

- Complete address range of target controller available

- Special protocol to transfer data, address offset, or address offset and data

- Error control using a parity bit

- 32-bit, 16-bit, and 8-bit data transfers

- Address offset width: from 1 to 16 bit

- Baud rate: f<sub>MLI</sub> / 2 (symmetric shift clock approach), baud rate definition by the corresponding fractional divider Maximum baud rate of 40 MBit/s (@ 80 MHz module clock)

Data Sheet

### Figure 1 SAK-CIC310-OSMX2HT and AUDO-NG 32bit Microcontroller Device Connected via MLI

The connectivity features of the MLI enables also connecting two different SAK-CIC310-OSMX2HT devices with the host This requires two sets of MLI interface signals bonded out of the host MLI.

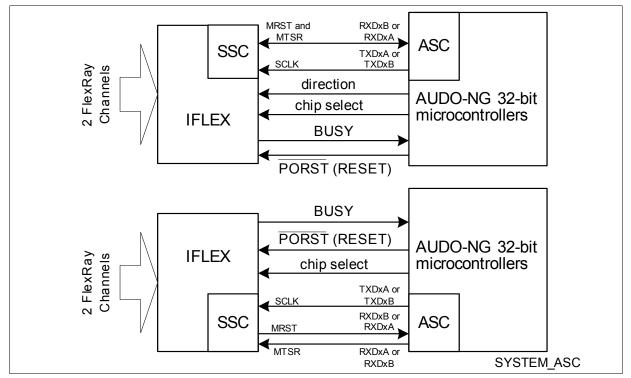

### 2.2 SSC Host Link (Option Two)

The second option is to connect the SAK-CIC310-OSMX2HT via a SSC (SPI) interface to e.g. the AUDO-NG 32-bit microcontroller family or the (X)C166 16-bit microcontroller family. Pin count are in a similar range compared with the MLI interface. The SW handling cost more host performance than the MLI interface requires. The single SPI link does not provide enough bandwidth to handle the maximum bandwidth FlexRay may require, but fulfil the needs of applications with lower bandwidth requirements.

### SSC Feature Set

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Automatic pad control possible

- Flexible data format

- Programmable number of data bits: 2 to 16-bit

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Baud rate (master): f<sub>SSC</sub> / 2; Maximum master mode baud rate of 40 MBit/s (@ 80 MHz module clock)

- Baud rate (slave): f<sub>SSC</sub> / 4; Maximum slave mode baud rate of 20 MBit/s (@ 80 MHz module clock)

- Interrupt generation

On a transmitter empty condition

Data Sheet

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

- SSC supports proprietary protocol to drive an integrated move engine.

- Note: Even so the SSC can be flexible configured, the SSC move engine can only handle 16 bit, Slave Mode, Full-duplex mode and Half-duplex mode, leading edge is high to low, shift on leading edge.

### Figure 2 SAK-CIC310-OSMX2HT and AUDO-NG 32bit Microcontroller Device Connected by SPI

The SSC is configured in a manner it could communicate to the ASC of the TriCore family. The TriCore ASC is configured in a manner using both RXDxA and RXDxB of the ASC as MRST and MTSR and the TXDxA or TXDxB as Clock.

### Figure 3 SAK-CIC310-OSMX2HT and AUDO-NG 32bit Microcontroller Device Connected via ASC

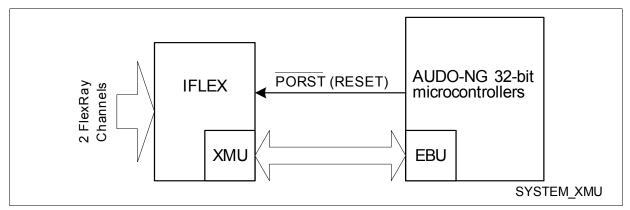

### 2.3 Parallel Host Link (Option Three)

The third option is to connect the SAK-CIC310-OSMX2HT via the parallel interface e.g. the AUDO-NG 32-bit microcontroller family or the (X)C166 16-bit microcontroller family. The parallel interface provides enough bandwidth to handle the maximum data traffic generated by the SAK-CIC310-OSMX2HT FlexRay Protocol Controller to the AUDO-NG 32-bit microcontroller device and vice versa.

### XMU Features

- 16-bit wide data bus (D[15:0])

- Data width of external bus master can be 8 or 16 bit.

- Automatic data assembly/disassembly operation

- 13-bit wide address bus (A[12:0])

- Bus control signals

- Read ( $\overline{RD}$ ) and write ( $\overline{WR}$ )

- Two byte control signals (BC[1:0])

- External synchronous/asynchronous wait state control (WAIT)

- External master chip select (CSFPI) to access on-chip devices connected to the MIF Bus

Data Sheet

### Figure 4 SAK-CIC310-OSMX2HT and AUDO-NG 32bit Microcontroller Device Connected via XMU

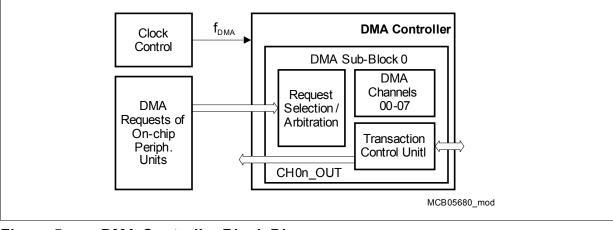

### 2.4 DMA Controller

The Direct Memory Access (DMA) Controller of the SAK-CIC310-OSMX2HT transfers data from data source locations to data destination locations without intervention of the Host Controller. One data move operation is controlled by one DMA channel. Eight DMA channels are provided. The Bus Switch provides the connection of the DMA Sub-Block to the ERAY Peripheral, Host Communication peripheral, Ports, and an MLI bus interface. **Figure 5** shows the implementation details and interconnections of the DMA module.

DMA Controller Block Diagram

### Features

- 8 independent DMA channels

- Up to 8 selectable request inputs per DMA channel

- 2-level programmable priority of DMA channels within a DMA Sub-Block

- Software and hardware DMA request

- Hardware requests by selected on-chip peripherals and external inputs

- Programmable priority of the DMA Sub-Blocks on the crossbar switch

- Buffer capability for move actions on the buses (at least 1 move per bus is buffered).

- Individually programmable operation modes for each DMA channel

- Single mode: stops and disables DMA channel after a predefined number of DMA transfers

- Continuous mode: DMA channel remains enabled after a predefined number of DMA transfers; DMA transaction can be repeated.

- Programmable address modification

- Full 32-bit addressing capability of each DMA channel

- 4 GByte address range

- Support of circular buffer addressing mode

- Programmable data width of DMA transfer/transaction: 8-bit, 16-bit, or 32-bit

- Micro Link bus interface support

- Register set for each DMA channel

- Source and destination address register

- Channel control and status register

- Transfer count register

- Flexible interrupt generation (the service request node logic for the MLI channels is also implemented in the DMA module)

- Read/write requests of the System Bus Side to the Remote Peripherals are bridged to the Remote Peripheral Bus (only the DMA is master on the RPB)

### **3 General Device Information**

This section provides an overview of the entire architecture of the SAK-CIC310-OSMX2HT companion chip.

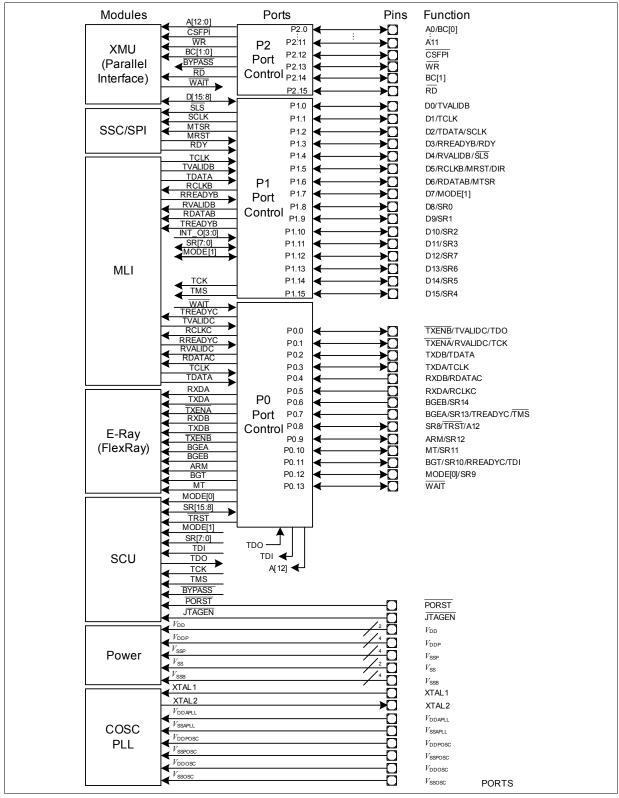

The overall building blocks of the SAK-CIC310-OSMX2HT are:

- FlexRay v2.1 protocol controller

- Slave (SPI) SSC interface

- MLI interface

- Parallel external memory interface unit (XMU).

- 8 independent channel DMA

- Dual Voltage Power Supply

- One Package Option only (PG-TQFP-64)

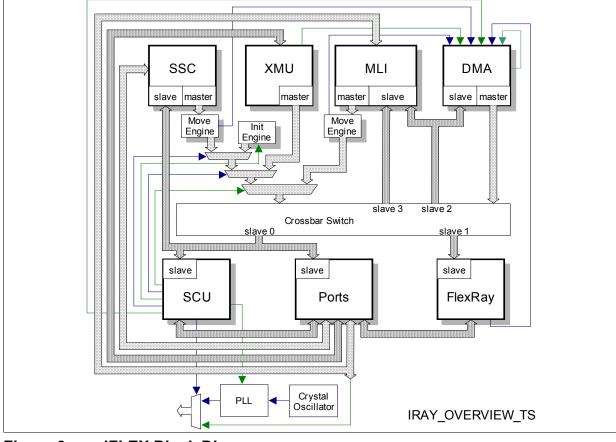

### 3.1 Block Diagram

Figure 6 summarizes the overall architecture of the SAK-CIC310-OSMX2HT.

### Figure 6 IFLEX Block Diagram

In **Figure 6** the block diagram of the IFLEX is shown. This concept allows the access to the FlexRay Protocol Controller for the host CPU without sacrificing any of the features

Data Sheet

of the FlexRay Protocol Controller. This can be achieved, as all registers of the FlexRay Protocol Controller are mapped to the crossbar switch. This crossbar switch can be accessed via one of the three host interfaces, which were introduced in **Chapter 2**. The interface selection is done via the mode signals MODE[0] and MODE[1], which can be directly connected to the supply voltage or via pull-up/down resistors (of about 10-47 k $\Omega$ ).

| Mode[1]        | Mode[0]        | Selected Host Interface     |

|----------------|----------------|-----------------------------|

| 0 <sub>B</sub> | 0 <sub>B</sub> | XMU Host Interface activate |

| 1 <sub>B</sub> | 0 <sub>B</sub> |                             |

| 0 <sub>B</sub> | 1 <sub>B</sub> | MLI Host Interface activate |

| 1 <sub>B</sub> | 1 <sub>B</sub> | SSC Host Interface activate |

### Table 1Host Interface Select

The cross bar switch allows two parallel data operations, one initiated by the DMA, the other by either the MLI, XMU, or SSC move engine and serving different ports of the crossbar switch to slave interfaces. The address ranges of the slave ports are:

- 1. Slave Port 0 serves the address range from  $0000\ 0800_{\rm H}$  to  $0000\ 0FFF_{\rm H}$

- 2. Slave Port 1 serves the address range from 0000  $1000_{H}$  to 0000  $1FFF_{H}$

- 3. Slave Port 2 serves the address range from 0000  $0200_{\rm H}$  to 0000  $07FF_{\rm H}$

- 4. Slave Port 3 serves all addresses 0000  $0000_{\rm H}$  to 0000  $01FF_{\rm H}$  and 0000  $2000_{\rm H}$  to FFFF FFFF\_H

So apart from a possible loss of speed due to the serial interfaces the complete functionality of the FlexRay Protocol Controller is maintained.

The crossbar switch domain is completely separated from the address domain on the CPU chip. The addresses of all modules on the FlexRay Communication Controller are 32-bit addresses. Transactions between the CPU and the SSC are executed with the SSC transmission protocol and a high level protocol to drive the move engine, transactions between the MLI and the CPU use the MLI transmission protocol and transactions between the XMU and the CPU are based on the XMU transmission protocol.

Each transaction via any of the three host interfaces is defined by address, data, data width and type of frame. The address, where data is read from or written to, is related to the crossbar switch address domain. The data width may be 8, 16, or 32 bit for the MLI, 8 or 16 bit for the XMU, and 16 bit for the SSC. The type of frame may be a read or write access or an answer frame to a read access. The Move Engines request access to the bus via the Bus Master. The Flex Protocol Controller and the MLI may send an interrupt to the DMA.

There are several cases:

- The MLI, XMU, or the SSC interfaces requests to write.

- The MLI, XMU, or the SSC interfaces requests to read.

- The FlexRay Communication Controller requests to write.

- A general peripheral beside the FlexRay Communication Controller requests to read.

Half-word (16-bit) accesses, read and write, are only allowed for half-word aligned addresses (even addresses). Therefore if doing a half-word (16-bit) access, the least significant address bit (A0) is ignored (assumed to be to 0) by the modules of the SAK-CIC310-OSMX2HT. Therefore if addressing a half-word with an odd address n, a half-word is read instead from address n-1 (ignoring least significant address bit: n AND FFFF FFFE<sub>H</sub>).

Word accesses (32-bit), read and write, are only allowed for word aligned addresses (addresses modulo 4 = 0). Therefore if doing a word (32-bit) access, the two least significant address bits (A0 and A1) are ignored (assumed to be to 0) by the modules of the SAK-CIC310-OSMX2HT. Therefore if addressing a word with an address n (n modulo 4 = {1,2,3}), a word is read instead from address (n AND FFFF FFFC<sub>H</sub>) (ignoring the two least significant address bits).

### 3.2 Pin Definition and Functions

To enable a clean power-up, the majority of pins have a "enable pad supply" (ENPS) function. This ENPS is pad supply ( $V_{DDP}$ ) driven. So only if the pad supply and the core supply is stable, the output pads may be activated. Four pins do no support ENPS: JTAGEN, PORST, XTAL1, and XTAL2. In case of a low voltage signal at the input port ENPS (PORST) the output port PAD activates the weak pull-up and disables the output driver independent of the port direction. In case of a high voltage signal at the input port ENPS (PORST) the bidirectional platform pads operate in normal mode.

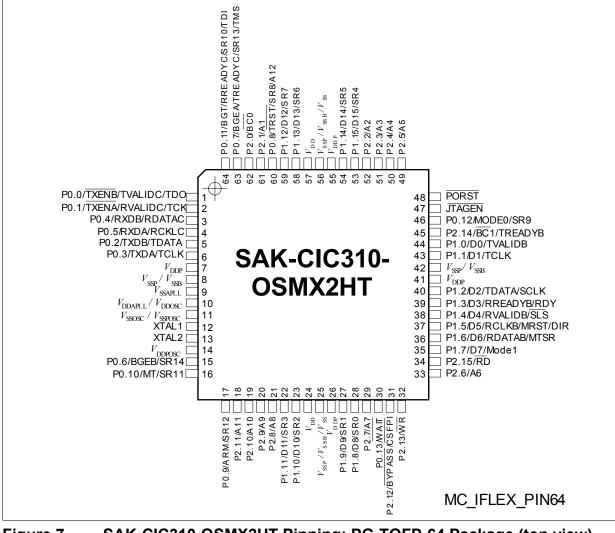

### 3.2.1 Package Outline

The package outline and the signals of the pins are summarized in Figure 7.

Figure 7 SAK-CIC310-OSMX2HT Pinning: PG-TQFP-64 Package (top view)

### 3.2.2 Pin Description

| Table 2 | Pin Definitions and Functions |

|---------|-------------------------------|

|         |                               |

| Symbol                    | Pin            | I/O | Function                                                                                                                                                |

|---------------------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | PG-<br>TQFP-64 |     |                                                                                                                                                         |

| FlexRay Bu                | us Interface   | 9   |                                                                                                                                                         |

| TXENB/<br>TVALIDC/<br>TDO | 1              | I/O | Port 0 line 0<br>FlexRay Transmit Enable<br>(Channel B)<br>JTAG Module Serial Data Output<br>JTAG Enable Mode only<br>MLI Transmit Channel Valid Output |

| TXENA/<br>RVALIDC/<br>TCK | 2              | I/O | Port 0 line 1<br>FlexRay Transmit Enable<br>(Channel A)<br>JTAG Module Clock Input (TCK)<br>JTAG Enable Mode only<br>MLI Receive Channel Valid Input C  |

| RXDB/<br>RCLKC            | 3              | I   | Port 0 line 4<br>FlexRay Data Receiver Input<br>(Channel B)<br>MLI Receive Channel Clock Input C                                                        |

| RXDA/<br>RDATAC           | 4              | I   | Port 0 line 5<br>FlexRay Data Receiver Input<br>(Channel A)<br>MLI Receive Channel Data Input C                                                         |

| TXDB/<br>TCLK             | 5              | I/O | Port 0 line 2<br>FlexRay Data Transmitter Output<br>(Channel B)<br>MLI Transmit Channel Clock Output                                                    |

| TXDA/<br>TDATA            | 6              | I/O | Port 0 line 3<br>FlexRay Data Transmitter Output<br>(Channel A)<br>MLI Transmit Channel Data Output                                                     |

| Table 2                           | 1                     | 1   | s and Functions (cont'd)                                                                                                                                                                                                                                                                                      |

|-----------------------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                            | Pin<br>PG-<br>TQFP-64 | I/O | Function                                                                                                                                                                                                                                                                                                      |

|                                   |                       |     |                                                                                                                                                                                                                                                                                                               |

| BGEB/<br>SR14                     | 15                    | 1   | Port 0 line 6<br>FlexRay Bus Guardian Enable<br>(Channel B)<br>Interrupt Request input line 14<br>The logic 0 level at this pin indicates an interrupt request<br>from the external host device.                                                                                                              |

| MT/<br>SR11                       | 16                    | I/O | Port 0 line 10<br>FlexRay Bus Guardian Macro Tick<br>FlexRay corrected Macro Tick Clock<br>Interrupt Request Input/Output line 11<br>The logic 0 level at this pin indicates an interrupt request<br>from/to the external host device.                                                                        |

| ARM/<br>SR12                      | 17                    | I/O | <ul> <li>Port 0 line 9</li> <li>FlexRay Bus Guardian Arm Signal</li> <li>Indicates the begin of a communication cycle to the bus guardian.</li> <li>Interrupt Request Input/Output line 12</li> <li>The logic 0 level at this pin indicates an interrupt request from/to the external host device.</li> </ul> |

| BGEA/<br>TMS/<br>SR13/<br>TREADYC | 63                    | 1   | Port 0 line 7<br>FlexRay Bus Guardian Enable<br>(Channel A)<br>JTAG Module State Machine Control Input<br>JTAG Enable Mode only<br>Interrupt Request input line 13<br>The logic 0 level at this pin indicates an interrupt request<br>from the external host device.<br>MLI Transmit Channel Ready Input C    |

| Symbol                           | Pin            | I/O | Function                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                | PG-<br>TQFP-64 |     |                                                                                                                                                                                                                                                                                                                                                                      |

| BGT/<br>TDI/<br>SR10/<br>RREADYC | 64             | I/O | Port 0 line 11<br>FlexRay Bus Guardian Tick<br>Used by the Macro Tick Watchdog of the Bus Guardian<br>as Time Base<br>JTAG Module Serial Data Input<br>JTAG Enable Mode only.<br>Interrupt Request Input/Output line 10<br>The logic 0 level at this pin indicates an interrupt request<br>from/to the external host device.<br>MLI Receive Channel Ready Output C   |

| Host Interfa                     | aces           |     |                                                                                                                                                                                                                                                                                                                                                                      |

| BC[1]/<br>TREADYB                | 45             |     | Port 2 line 14<br>$MODE = 00_B$ :<br>XMU Byte control line 1<br>Controls the byte access to corresponding byte location<br>D[15:8]<br>$MODE = 01_B$ :<br>MLI Transmit Channel Ready Input B<br>$MODE = 10_B$ :<br>XMU Byte control line 1<br>Controls the byte access to corresponding byte location<br>D[15:8]<br>$MODE = 11_B$ :<br>Port 2 line 14<br>(input only) |

| D0/<br>TVALIDB                   | 44             | I/O | Port 1 line 0<br>MODE = $00_B$ :<br>XMU Data bus Line 0<br>MODE = $01_B$ :<br>MLI Transmit Channel Valid Output<br>MODE = $10_B$ :<br>XMU Data Bus line 0<br>MODE = $11_B$ :<br>Port 1 line 0 (Input/Output)                                                                                                                                                         |

I

| Table 2                    | Pin Defi              | nition | s and Functions (cont'd)                                                                                                                                                                                                                                      |

|----------------------------|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                     | Pin<br>PG-<br>TQFP-64 | I/O    | Function                                                                                                                                                                                                                                                      |

| D1/<br>TCLK                | 43                    | I/O    | Port 1 line 1<br>$MODE = 00_B$ :<br>XMU Data Bus Line 1<br>MODE = 01B:<br>MLI Transmit Channel Clock Output<br>$MODE = 10_B$ :<br>XMU Data Bus Line 1<br>$MODE = 11_B$ :<br>Port 1 line 1 (Input/Output)                                                      |

| D2/<br>TDATA/<br>SCLK      | 40                    | I/O    | Port 1 line 2<br>$MODE = 00_B$ :<br>XMU Data Bus Line 2<br>$MODE = 01_B$ :<br>MLI Transmit Channel Data Output<br>$MODE = 10_B$ :<br>XMU Data Bus Line 2<br>$MODE = 11_B$ :<br>SSC Serial Channel Clock (Input/Output)                                        |

| D3/<br>RREADYB<br>/<br>RDY | 39                    | I/O    | Port 1 line 3 $MODE = 00_B$ :XMU Data Bus Line 3 $MODE = 01_B$ :MLI Receive Channel Ready Output B $MODE = 10_B$ :XMU Data Bus Line 3 $MODE = 11_B$ :SSC Ready Signal (Output)Output signal indicating that the standalone device is ready for data transfer. |

| Table 2                         | Pin Defi       | nition | s and Functions (cont'd)                                                                                                                                                                                                                                                                                           |

|---------------------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                          | Pin            | I/O    | Function                                                                                                                                                                                                                                                                                                           |

|                                 | PG-<br>TQFP-64 |        |                                                                                                                                                                                                                                                                                                                    |

| D4/<br><u>RVA</u> LIDB/<br>SLS  | 38             | I/O    | Port 1 line 4<br>$MODE = 00_B$ :<br>XMU Data Bus Line 4<br>$MODE = 01_B$ :<br>MLI Receive Channel Valid Input B<br>$MODE = 10_B$ :<br>XMU Data Bus Line 4<br>$MODE = 11_B$ :<br>SSC Select Slave<br>Input used to enable SSC action when active.                                                                   |

| D5/<br>RCLKB/<br>MRST/<br>DIR   | 37             | I/O    | Port 1 line 5<br>$MODE = 00_B$ :<br>XMU Data Bus Line 5<br>$MODE = 01_B$ :<br>MLI Receive Channel Clock Input B<br>$MODE = 10_B$ :<br>XMU Data Bus Line 5<br>$MODE = 11_B$ :<br>SPI Master Receive Slave Transmit<br>Serial data output<br>Alternative:<br>Direction of SPI Half-Duplex communication.             |

| D6/<br>RDATAB/<br>MTSR/<br>MRST | 36             | Ι/Ο    | Port 1 line 6<br>$MODE = 00_B$ :<br>XMU Data Bus Line 6<br>$MODE = 01_B$ :<br>MLI Receive Channel Data Input B<br>$MODE = 10_B$ :<br>XMU Data Bus Line 6<br>$MODE = 11_B$ :<br>SPI Master Transmit Slave Receive<br>Serial data input<br>SPI Slave Transmit Master Receive<br>Serial data input (half duplex mode) |

| Table 2Pin Definitions and Functions (cont'd) |                |     | s and Functions (cont'd)                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                        | Pin            | I/O | Function                                                                                                                                                                                                                                                                                                                    |

|                                               | PG-<br>TQFP-64 |     |                                                                                                                                                                                                                                                                                                                             |

| Parallel Ho                                   | st Interfac    | e   |                                                                                                                                                                                                                                                                                                                             |

| BC[0]                                         | 62             | 1   | Port 2 line 0<br>MODE = $00_B$ :<br>XMU Byte control line 0<br>Controls the byte access to corresponding byte location<br>D[7:0]<br>MODE = $01_B$ :<br>Port 2 line 0<br>MODE = $10_B$ :<br>XMU Byte control line 0<br>Controls the byte access to corresponding byte location<br>D[7:0]<br>MODE = $11_B$ :<br>Port 2 line 0 |

| A[1]                                          | 61             | 1   | Port 2 line 1<br>$MODE = 00_B$ :<br>XMU Address bus line 1<br>The XMU Address Bus Lines serve as external address<br>bus<br>$MODE = 01_B$ :<br>Port 2 line 1<br>$MODE = 10_B$ :<br>XMU Address bus line 1<br>The XMU Address Bus Lines serve as external address<br>bus<br>$MODE = 11_B$ :<br>Port 2 line 1                 |

| Table 2 | Pin Defi              | nitior | ns and Functions (cont'd)                                                                                                                                                                                                                                      |

|---------|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin<br>PG-<br>TQFP-64 | I/O    | Function                                                                                                                                                                                                                                                       |

| A[2]    | 52                    |        | Port 2 line 2 $MODE = 00_B$ :XMU Address bus line 2The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 1 $MODE = 10_B$ :XMU Address bus line 2The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 2 |

| A[3]    | 51                    | 1      | Port 2 line 3 $MODE = 00_B$ :XMU Address bus line 3The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 1 $MODE = 10_B$ :XMU Address bus line 3The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 3 |

| Symbol | Pin            | I/O | Function                                                                                                                                                                                                                                                       |

|--------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | PG-<br>TQFP-64 |     |                                                                                                                                                                                                                                                                |

| A[4]   | 50             |     | Port 2 line 4 $MODE = 00_B$ :XMU Address bus line 4The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 1 $MODE = 10_B$ :XMU Address bus line 4The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 4 |

| A[5]   | 49             |     | Port 2 line 5MODE = $00_B$ :XMU Address bus line 5The XMU Address Bus Lines serve as external addressbusMODE = $01_B$ :Port 2 line 1MODE = $10_B$ :XMU Address bus line 5The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 5    |

| Table 2 |                | 1   | as and Functions (cont'd)                                                                                                                                                                                                                                      |

|---------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin            | I/O | Function                                                                                                                                                                                                                                                       |

|         | PG-<br>TQFP-64 | Ţ   |                                                                                                                                                                                                                                                                |

| A[6]    | 33             | 1   | Port 2 line 6 $MODE = 00_B$ :XMU Address bus line 6The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 1 $MODE = 10_B$ :XMU Address bus line 6The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 6 |

| A[7]    | 29             |     | Port 2 line 7 $MODE = 00_B$ :XMU Address bus line 7The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 1 $MODE = 10_B$ :XMU Address bus line 7The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 7 |

| Table 2 | Pill Dell             |     | ns and Functions (cont'd)                                                                                                                                                                                                                                      |

|---------|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin<br>PG-<br>TQFP-64 | I/O | Function                                                                                                                                                                                                                                                       |

| A[8]    | 21                    | 1   | Port 2 line 8 $MODE = 00_B$ :XMU Address bus line 8The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 1 $MODE = 10_B$ :XMU Address bus line 8The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 8 |

| A[9]    | 20                    | 1   | Port 2 line 9MODE = $00_B$ :XMU Address bus line 9The XMU Address Bus Lines serve as external addressbusMODE = $01_B$ :Port 2 line 1MODE = $10_B$ :XMU Address bus line 9The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 9    |

| Table 2 | Pin Defi              | nitior | ns and Functions (cont'd)                                                                                                                                                                                                                                           |

|---------|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin<br>PG-<br>TQFP-64 | I/O    | Function                                                                                                                                                                                                                                                            |

| A[10]   | 19                    |        | Port 2 line 10 $MODE = 00_B$ :XMU Address bus line 9The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 1 $MODE = 10_B$ :XMU Address bus line 10The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 9    |

| A[11]   | 18                    | 1      | Port 2 line 11 $MODE = 00_B$ :XMU Address bus line 11The XMU Address Bus Lines serve as external addressbus $MODE = 01_B$ :Port 2 line 11 $MODE = 10_B$ :XMU Address bus line 11The XMU Address Bus Lines serve as external addressbusMODE = $11_B$ :Port 2 line 11 |

| Table 2    | Pin Defi              | Pin Definitions and Functions (cont'd) |                                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------|-----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol     | Pin<br>PG-<br>TQFP-64 | I/O                                    | Function                                                                                                                                                                                                                                                                                                                   |  |  |  |

| D8/<br>SR0 | 28                    | 1/0                                    | Port 1 line 8 $MODE = 00_B$ :XMU Data bus Line 8 $MODE = 01_B$ :Port 1 line 8 (Input/Output) $MODE = 10_B$ :XMU Data Bus line 8 $MODE = 11_B$ :Port 1 line 8 (Input/Output)Alternative:Interrupt Request Input/Output line 0The logic 0 level at this pin indicates an interrupt request from/to the external host device. |  |  |  |

| D9/<br>SR1 | 27                    | 1/0                                    | Port 1 line 9 $MODE = 00_B$ :XMU Data bus Line 9 $MODE = 01_B$ :Port 1 line 9 (Input/Output) $MODE = 10_B$ :XMU Data Bus line 9 $MODE = 11_B$ :Port 1 line 9 (Input/Output)Alternative:Interrupt Request Input/Output line 1The logic 0 level at this pin indicates an interrupt requestfrom/to the external host device.  |  |  |  |

| Table 2     | Pin Defi             | Pin Definitions and Functions (cont'd) |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-------------|----------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol      | Pin<br>PG-           | I/O                                    | Function                                                                                                                                                                                                                                                                                                                        |  |  |  |

| D10/<br>SR2 | <b>TQFP-64</b><br>23 | 1/0                                    | Port 1 line 10 $MODE = 00_B$ :XMU Data bus Line 10 $MODE = 01_B$ :Port 1 line 10 (Input/Output) $MODE = 10_B$ :XMU Data Bus line 10 $MODE = 11_B$ :Port 1 line 10 (Input/Output)Alternative:Interrupt Request Input/Output line 2The logic 0 level at this pin indicates an interrupt request from/to the external host device. |  |  |  |

| D11/<br>SR3 | 22                   | 1/0                                    | Port 1 line 11 $MODE = 00_B$ :XMU Data bus Line 11 $MODE = 01_B$ :Port 1 line 11 (Input/Output) $MODE = 10_B$ :XMU Data Bus line 11 $MODE = 11_B$ :Port 1 line 11 (Input/Output)Alternative:Interrupt Request Input/Output line 3The logic 0 level at this pin indicates an interrupt request from/to the external host device. |  |  |  |

| Table 2     | Pin Defi              | nition | is and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol      | Pin<br>PG-<br>TQFP-64 | I/O    | Function                                                                                                                                                                                                                                                                                                                                                                   |

| D12/<br>SR7 | 59                    | 1/0    | Port 1 line 12 $MODE = 00_B$ :XMU Data bus Line 12 $MODE = 01_B$ :12 (Input/Output) $MODE = 10_B$ :XMU Data Bus line 12 $MODE = 11_B$ :Port 1 line 12 (Input/Output)Alternative:Interrupt Request Input/Output line 7The logic 0 level at this pin indicates an interrupt request from/to the external host device.                                                        |

| D13/<br>SR6 | 58                    | 1/0    | Port 1 line 13<br>MODE = $00_B$ :<br>XMU Data bus Line 13<br>MODE = $01_B$ :<br>Port 1 line 13 (Input/Output)<br>MODE = $10_B$ :<br>XMU Data Bus line 13<br>MODE = $11_B$ :<br>Port 1 line 13 (Input/Output)<br>Alternative:<br>Interrupt Request Input/Output line 6<br>The logic 0 level at this pin indicates an interrupt request<br>from/to the external host device. |

| Table 2     | Pin Defi       | nition | s and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol      | Pin            | I/O    | Function                                                                                                                                                                                                                                                                                                                                                                   |

|             | PG-<br>TQFP-64 |        |                                                                                                                                                                                                                                                                                                                                                                            |

| D14/<br>SR5 | 54             | 1/0    | Port 1 line 14<br>MODE = $00_B$ :<br>XMU Data bus Line 14<br>MODE = $01_B$ :<br>Port 1 line 14 (Input/Output)<br>MODE = $10_B$ :<br>XMU Data Bus line 14<br>MODE = $11_B$ :<br>Port 1 line 14 (Input/Output)<br>Alternative:<br>Interrupt Request Input/Output line 5<br>The logic 0 level at this pin indicates an interrupt request<br>from/to the external host device. |

| D15/<br>SR4 | 53             | 1/0    | Port 1 line 15<br>MODE = $00_B$ :<br>XMU Data bus Line 15<br>MODE = $01_B$ :<br>Port 1 line 15 (Input/Output)<br>MODE = $10_B$ :<br>XMU Data Bus line 15<br>MODE = $11_B$ :<br>Port 1 line 15 (Input/Output)<br>Alternative:<br>Interrupt Request Input/Output line 4<br>The logic 0 level at this pin indicates an interrupt request<br>from/to the external host device. |

| RD          | 34             | 1      | Port 2 line 15<br>MODE = $00_B$ :<br>XMU Read control line<br>Active during read operation<br>MODE = $01_B$ :<br>Port 2 line 15<br>MODE = $10_B$ :<br>XMU Read control line<br>Active during read operation<br>MODE = $11_B$ :<br>Port 2 line 15                                                                                                                           |

| Table 2     | Pin Defi              | nition | s and Functions (cont'd)                                                                                                                                                                                                                                                   |

|-------------|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol      | Pin<br>PG-<br>TQFP-64 | I/O    | Function                                                                                                                                                                                                                                                                   |

| WR          | 32                    |        | Port 2 line 13<br>$MODE = 00_B$ :<br>XMU Write control line<br>Active during write operation input line<br>$MODE = 01_B$ :<br>Port 2 line 13<br>$MODE = 10_B$ :<br>XMU Write control line<br>Active during write operation input line<br>$MODE = 11_B$ :<br>Port 2 line 13 |

| WAIT        | 30                    | I/O    | Port 0 line 13<br>MODE = $00_B$ :<br>XMU Wait output<br>MODE = $01_B$ :<br>Port 0 line 13<br>MODE = $10_B$ :<br>XMU Wait output<br>MODE = $11_B$ :<br>Port 0 line 13                                                                                                       |

| Control Sig | gnals                 |        |                                                                                                                                                                                                                                                                            |

| PORST       | 48                    | 1      | Power-on Reset                                                                                                                                                                                                                                                             |

| JTAGEN      | 47                    | I      | <b>JTAG Enabled Mode Selection</b> /<br>Pin JTAGEN selects whether JTAG Enabled Mode is<br>used to access the SAK-CIC310-OSMX2HT device.<br>$\overline{\text{JTAGEN}} = 0_{\text{B}}$ : JTAG Enabled Mode<br>$\overline{\text{JTAGEN}} = 1_{\text{B}}$ : Normal Mode       |

| Symbol                 | Pin            | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | PG-<br>TQFP-64 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TRST/<br>SR8/<br>A[12] | 60             | Ι/Ο | Port 0 line 8<br>Interrupt Request Input/Output Line 8<br>The logic 0 level at this pin indicates an interrupt request<br>to/from the external host device.<br>MODE = $00_B$ :<br>XMU Address bus line 12<br>The XMU Address Bus Lines serve as external address<br>bus<br>MODE = $01_B$ :<br>Port 0 line 8 or<br>Interrupt Request Input/Output Line 8<br>The logic 0 level at this pin indicates an interrupt request<br>to/from the external host device.<br>MODE = $10_B$ :<br>XMU Address bus line 12<br>The XMU Address Bus Lines serve as external address<br>bus<br>MODE = $10_B$ :<br>XMU Address Bus Lines serve as external address<br>bus<br>MODE = $11_B$ :<br>Port 0 line 8 or<br>Interrupt Request Input/Output Line 8<br>The logic 0 level at this pin indicates an interrupt request<br>to/from the external host device. |

|                        |                |     | Test Reset<br>(JTAG Enable Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Table 2                       | Pin Definitions and Functions (cont'd) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|----------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                        | Pin                                    | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | PG-<br>TQFP-64                         | •   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MODE[0]/<br>SR9 <sup>1)</sup> | 46 <sup>2)</sup>                       | I/O | Port 0 line 12<br>Interface Selection 0<br>Pin MODE 0 selects if the on-chip serial Host<br>Communication Links (MLI or SSC) or the parallel XMU<br>Host Communication Link is enabled for communicating<br>to the SAK-CIC310-OSMX2HT device.<br>MODE 0 = $0_B$ : On-chip XMU<br>MODE 0 = $1_B$ : On-chip SSC or MLI<br>After latching the initial state with the rising edge of the<br>PORST signal (e.g. external pull-up or pull-down<br>resistors), this MODE 0 pin can be used as: Interrupt<br>Request Input/Output Line 9<br>The logic 0 level at this pin indicates an interrupt request<br>to/from the external host device. |

| Table 2                      | 1              |     | s and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|------------------------------|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                       | Pin            | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                              | PG-<br>TQFP-64 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| D7/<br>Mode[1] <sup>3)</sup> | 35             | I/O | Port 1 line 7<br>MODE = $00_B$ :<br>XMU Data Bus Line 7<br>MODE = $01_B$ :<br>Interface Selection 1<br>Pin MODE 1 selects if the on-chip serial MLI<br>Communication Link or the serial SPI Host<br>Communication Link is enabled for communicating to the<br>SAK-CIC310-OSMX2HT device if Mode[0] = 1.<br>MODE[0] = 1 AND MODE[1] = $0_B$ : On-chip MLI<br>MODE[0] = 1 AND MODE[1] = $1_B$ : On-chip SSC<br>After latching the initial state with the rising edge of the<br>PORST signal (e.g. external pull-up or pull-down<br>resistors), this MODE 1 pin can be used as standard IO<br>pin.<br>MODE = $10_B$ :<br>XMU Data Bus Line 7<br>Active during write operation input line<br>MODE = $11_B$ :<br>Interface Selection 1<br>Pin MODE 1 selects if the on-chip serial MLI<br>Communication Link or the serial SPI Host<br>Communication Link is enabled for communicating to the<br>SAK-CIC310-OSMX2HT device if Mode[0] = 1.<br>MODE[0] = 1 AND MODE[1] = $0_B$ : On-chip MLI<br>MODE[0] = 1 AND MODE[1] = $0_B$ : On-chip SSC<br>After latching the initial state with the rising edge of the<br>PORST signal (e.g. external pull-up or pull-down<br>resistors), this MODE 1 pin can be used as standard IO<br>pin. |  |  |  |  |

| Table 2                       | Pin Defi       | nition    | s and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                        | Pin            | I/O       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                |