# W83627SF WINBOND I/O

#### **W83627SF Data Sheet Revision History**

|    | Pages | Dates      | Version | Version on Web | Main Contents   |

|----|-------|------------|---------|----------------|-----------------|

| 1  | n.a.  | 2000/09/17 | 0.50    |                | First published |

| 2  | All   | 2000/11/15 | 0.60    |                | New composition |

| 3  |       |            |         |                |                 |

| 4  |       |            |         |                |                 |

| 5  |       |            |         |                |                 |

| 6  |       |            |         |                |                 |

| 7  |       |            |         |                |                 |

| 8  |       |            |         |                |                 |

| 9  |       |            |         |                |                 |

| 10 |       |            |         |                |                 |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

## TABLE OF CONTENTS

| GENERAL DESCRIPTION                                                                                             | 1  |

|-----------------------------------------------------------------------------------------------------------------|----|

| PIN CONFIGURATION FOR W83627SF                                                                                  | 6  |

| 1. PIN DESCRIPTION                                                                                              | 7  |

| 1.1 LPC INTERFACE                                                                                               | 7  |

| 1.2 FDC INTERFACE                                                                                               | 8  |

| 1.3 MULTI-MODE PARAILEL PORT                                                                                    | 9  |

| 1.4 SERIAL PORT INTERFACE                                                                                       | 13 |

| 1.5 KBC INTERFACE                                                                                               | 15 |

| 1.6 ACPI INTERFACE                                                                                              | 15 |

| 1.7 GAME PORT & MIDI PORT                                                                                       | 16 |

| 1.8 GENERAL PURPOSE I/O PORT                                                                                    | 17 |

| 1.8.1 General Purpose I/O Port 1 (Power source is Vcc)                                                          | 17 |

| 1.8.2 General Purpose I/O Port 2 (Power source is Vcc)                                                          | 17 |

| 1.8.3 General Purpose I/O Port 3 (Power souce is VSB)                                                           | 18 |

| 1.9 SMART CARD INTERFACE AND GENERAL PURPOSE I/O PORT 7 (POWERED BY VCC EXCEPT SCPSNT# WHICH IS POWERED BY VSB) |    |

| 1.10 GENERAL PURPOSE I/O PORT 4 (POWERED BY GP4PWR)                                                             | 20 |

| 1.11 GENERAL PURPOSE I/O PORT 5, 6 (POWERED BY VCC)                                                             | 20 |

| 1.12 32KHZ CRYSTAL OSCILLATOR                                                                                   | 21 |

| 1.13 POWER PINS                                                                                                 | 21 |

| 2. LPC (LOW PIN COUNT) INTERFACE                                                                                | 22 |

| 3. FDC FUNCTIONAL DESCRIPTION                                                                                   | 23 |

| 3.1 W83627SF FDC                                                                                                | 23 |

| 3.1.1 AT interface                                                                                              | 23 |

| 3.1.2 FIFO (Data)                                                                                               |    |

| 3.1.3 Data Separator                                                                                            | 24 |

| 3.1.4 Write Precompensation                                                           | 25 |

|---------------------------------------------------------------------------------------|----|

| 3.1.5 Perpendicular Recording Mode                                                    | 25 |

| 3.1.6 FDC Core                                                                        | 25 |

| 3.1.7 FDC Commands                                                                    | 25 |

| 3.2 REGISTER DESCRIPTIONS                                                             | 36 |

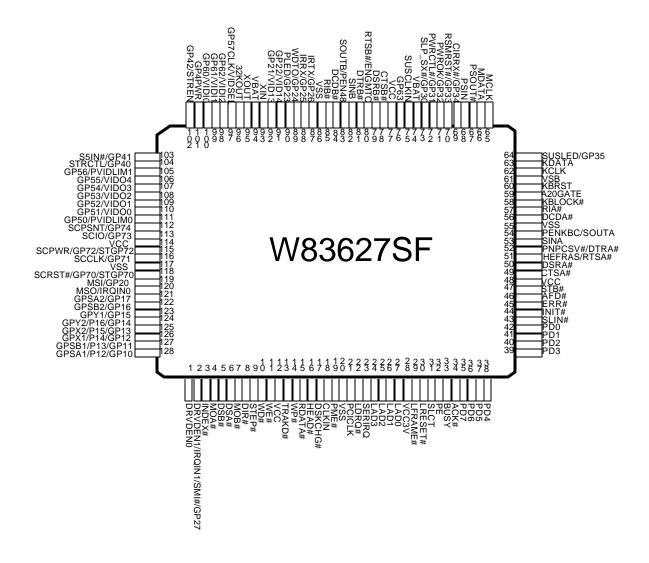

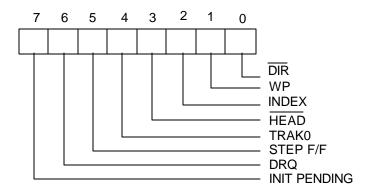

| 3.2.1 Status Register A (SA Register) (Read base address + 0)                         | 36 |

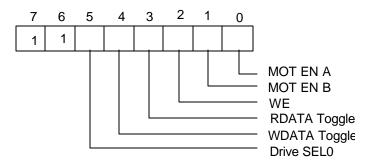

| 3.2.2 Status Register B (SB Register) (Read base address + 1)                         |    |

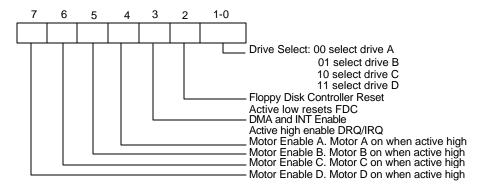

| 3.2.3 Digital Output Register (DO Register) (Write base address + 2)                  |    |

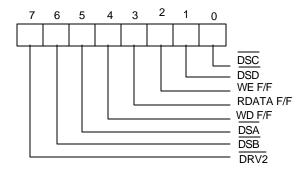

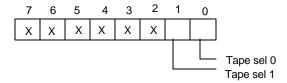

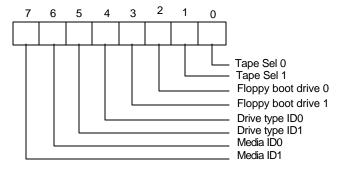

| 3.2.4 Tape Drive Register (TD Register) (Read base address + 3)                       |    |

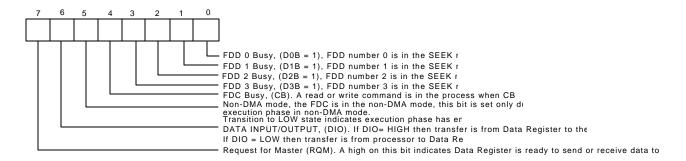

| 3.2.5 Main Status Register (MS Register) (Read base address + 4)                      |    |

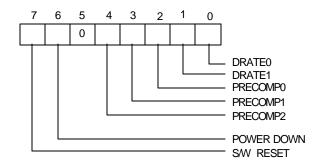

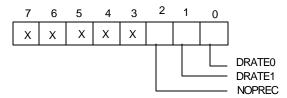

| 3.2.6 Data Rate Register (DR Register) (Write base address + 4)                       | 41 |

| 3.2.7 FIFO Register (R/W base address + 5)                                            |    |

| 3.2.8 Digital Input Register (DI Register) (Read base address + 7)                    | 45 |

| 3.2.9 Configuration Control Register (CC Register) (Write base address + 7)           | 46 |

| 4. UART PORT                                                                          | 47 |

| 4.1 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART A, UART B)                      | 47 |

| 4.2 REGISTER ADDRESS                                                                  | 47 |

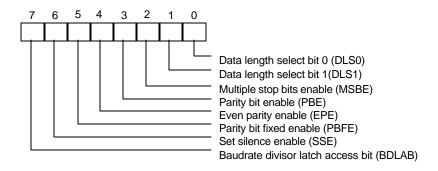

| 4.2.1 UART Control Register (UCR) (Read/Write)                                        | 47 |

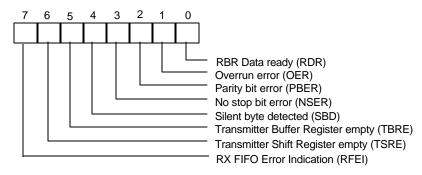

| 4.2.2 UART Status Register (USR) (Read/Write)                                         |    |

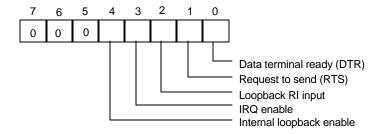

| 4.2.3 Handshake Control Register (HCR) (Read/Write)                                   |    |

| 4.2.4 Handshake Status Register (HSR) (Read/Write)                                    | 52 |

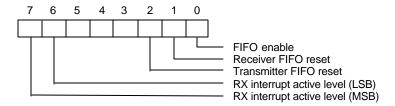

| 4.2.5 UART FIFO Control Register (UFR) (Write only)                                   |    |

| 4.2.6 Interrupt Status Register (ISR) (Read only)                                     |    |

| 4.2.7 Interrupt Control Register (ICR) (Read/Write)                                   | 55 |

| 4.2.8 Programmable Baud Generator (BLL/BHL) (Read/Write)                              |    |

| 4.2.9 User-defined Register (UDR) (Read/Write)                                        | 56 |

| 5. CIR RECEIVER PORT                                                                  | 57 |

| 5.1 CIR REGISTERS                                                                     | 57 |

| 5.1.1 Bank0.Reg0 - Receiver Buffer Registers (RBR) (Read)                             | 57 |

| 5.1.2 Bank0.Reg1 - Interrupt Control Register (ICR)                                   | 57 |

| 5.1.3 Bank0.Reg2 - Interrupt Status Register (ISR)                                    |    |

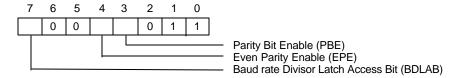

| 5.1.4 Bank0~3.Reg3 - CIR Control Register 0/Bank Select Register (CTR0/BSR) (BANK0~3) |    |

| 5.1.5 Bank0.Reg4 - CIR Control Register (CTR)                                         |    |

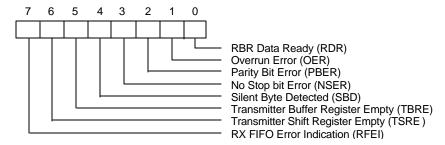

| 5.1.6 Bank0.Reg5 - UART Line Status Register (USR)                                    | 59 |

| 5.1.7 Bank0.Reg6 - Remote Infrared Config Register (RIR_CFG)                          |    |

# W83627SF

#### PRELIMINARY

| 5.1.8 Bank0.Reg7 - User Defined Register (UDR/AUDR)                                    | 61 |

|----------------------------------------------------------------------------------------|----|

| 5.1.9 Bank1.Reg0~1 - Baud Rate Divisor Latch (BLL/BHL)                                 | 62 |

| 5.1.10 Bank1.Reg2 - Version ID Regiister I (VID)                                       | 63 |

| 5.1.11 Bank0~3.Reg3 - CIR Control Register 0/Bank Select Register (CTR0/BSR) (BANK0~3) | 63 |

| 5.1.12 Bank1.Reg4 - Timer Low Byte Register (TMRL)                                     | 63 |

| 5.1.13 Bank1.Reg5 - Timer High Byte Register (TMRH)                                    | 63 |

| 6. PARALLEL PORT                                                                       | 64 |

| 6.1 PRINTER INTERFACE LOGIC                                                            | 64 |

| 6.2 ENHANCED PARALLEL PORT (EPP)                                                       | 65 |

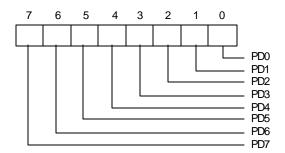

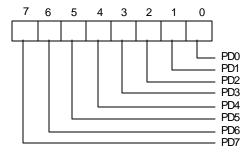

| 6.2.1 Data Swapper                                                                     | 66 |

| 6.2.2 Printer Status Buffer                                                            | 66 |

| 6.2.3 Printer Control Latch and Printer Control Swapper                                | 67 |

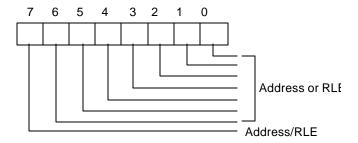

| 6.2.4 EPP Address Port                                                                 | 67 |

| 6.2.5 EPP Data Port 0-3                                                                | 68 |

| 6.2.6 Bit Map of Parallel Port and EPP Registers                                       | 68 |

| 6.2.7 EPP Pin Descriptions                                                             | 69 |

| 6.2.8 EPP Operation                                                                    | 69 |

| 6.3 EXTENDED CAPABILITIES PARALLEL (ECP) PORT                                          | 70 |

| 6.3.1 ECP Register and Mode Definitions                                                | 70 |

| 6.3.2 Data and ecpAFifo Port                                                           |    |

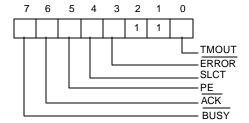

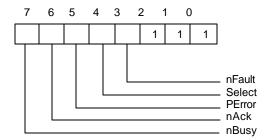

| 6.3.3 Device Status Register (DSR)                                                     | 71 |

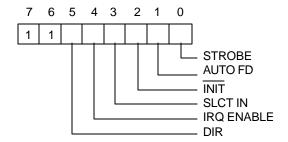

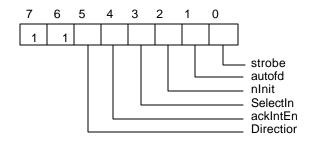

| 6.3.4 Device Control Register (DCR)                                                    | 72 |

| 6.3.5 cFifo (Parallel Port Data FIFO) Mode = 010                                       | 73 |

| 6.3.6 ecpDFifo (ECP Data FIFO) Mode = 011                                              | 73 |

| 6.3.7 tFifo (Test FIFO Mode) Mode = 110                                                |    |

| 6.3.8 cnfgA (Configuration Register A) Mode = 111                                      | 73 |

| 6.3.9 cnfgB (Configuration Register B) Mode = 111                                      | 73 |

| 6.3.10 ecr (Extended Control Register) Mode = all                                      | 74 |

| 6.3.11 Bit Map of ECP Port Registers                                                   | 75 |

| 6.3.12 ECP Pin Descriptions                                                            | 76 |

| 6.3.13 ECP Operation                                                                   | 77 |

| 6.3.14 FIFO Operation                                                                  | 77 |

| 6.3.15 DMA Transfers                                                                   | 78 |

| 6.3.16 Programmed I/O (NON-DMA) Mode                                                   | 78 |

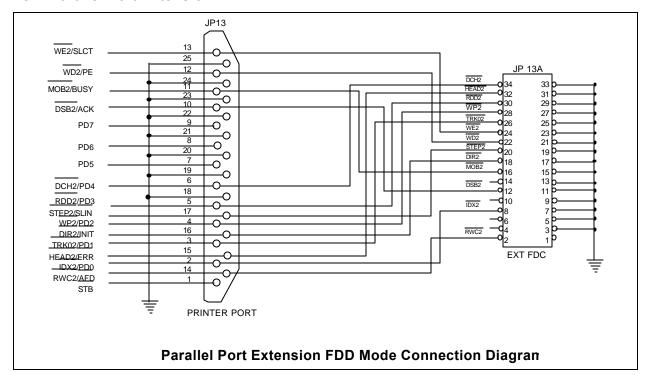

| 6.4 EXTENSION FDD MODE (EXTFDD)                                                        | 78 |

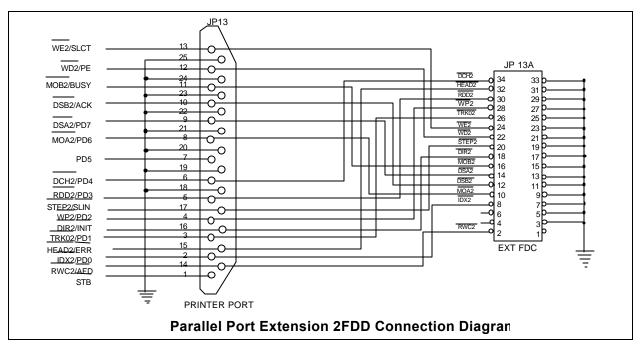

| 6.5 EXTENSION 2FDD MODE (EXT2FDD)                                                        | 79          |

|------------------------------------------------------------------------------------------|-------------|

| 7. KEYBOARD CONTROLLER                                                                   | 80          |

| 7.1 OUTPUT BUFFER                                                                        | 81          |

| 7.2 INPUT BUFFER                                                                         | 81          |

| 7.3 STATUS REGISTER                                                                      | 81          |

| 7.4 COMMANDS                                                                             | 82          |

| 7.5 HARDWARE GATEA20/KEYBOARD RESET CONTROL LOGIC                                        | 84          |

| 7.5.1 KB Control Register (Logic Device 5, CR-F0)                                        | 84          |

| 7.5.2 Port 92 Control Register (Default Value = 0x24)                                    | 84          |

| 8. GENERAL PURPOSE I/O                                                                   | 85          |

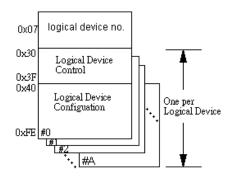

| 9. PLUG AND PLAY CONFIGURATION                                                           | 89          |

| 9.1 COMPATIBLE PNP                                                                       | 89          |

| 9.1.1 Extended Function Registers                                                        | 89          |

| 9.1.2 Extended Functions Enable Registers (EFERs)                                        | 90          |

| 9.1.3 Extended Function Index Registers (EFIRs), Extended Function Data Registers(EFDRs) | 90          |

| 9.2 CONFIGURATION SEQUENCE                                                               | 90          |

| 9.2.1 Enter the extended function mode                                                   | 90          |

| 9.2.2 Configurate the configuration registers                                            | 91          |

| 9.2.3 Exit the extended function mode                                                    |             |

| 9.2.4 Software programming example                                                       | 91          |

| 10. ACPI REGISTERS FEATURES                                                              | 93          |

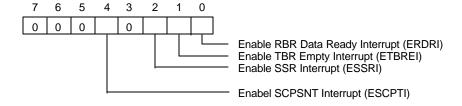

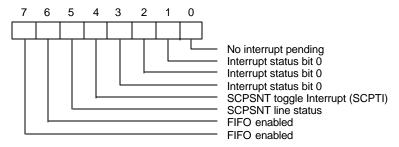

| 11. SMART CARD INTERFACE                                                                 | <b> 9</b> 4 |

| 11.1 RECEIVER BUFFER REGISTER (RBR, READ ONLY AT "BASE ADDRESS + 0" WHEN BDLAB = 0)      | 94          |

| 11.2 TRANSMITTER BUFFER REGISTER (TBR, WRITE ONLY AT "BASE ADDRESS + 0" WHEN BDLAB = 0   | ) 94        |

| 11.3 INTERRUPT CONTROL REGISTER (ICR, AT "BASE ADDRESS + 1" WHEN BDLAB = 0)              | 94          |

| 11.4 INTERRUPT STATUS REGISTER (ISR, READ ONLY AT "BASE ADDRESS + 2")                    | 95          |

| 11.5 SMART CARD FIFO CONTROL REGISTER (SCFR, WRITE ONLY AT "BASE ADDRESS + 2")           | 96          |

| 11.6 SMART CARD CONTROL REGISTER (SCCR, WRITE ONLY AT "BASE ADDRESS + 3")                | 97          |

| 11.7 INTERRUPT ENABLE REGISTER (IER, AT "BASE ADDRESS + 4")                              |             |

| 11.8 SMART CARD STATUS REGISTER (SCSR, AT "BASE ADDRESS + 5")                            |             |

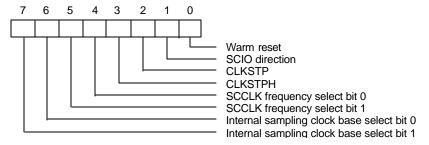

| 11.9 EXTENDED CONTROL REGISTER (ECR, AT "BASE ADDRESS + 7")                              | 99          |

| 11.10 BAUD RATE DIVISOR LATCH HIGH AND BAUD RATE DIVISOR LATCH LOW (BHL AND BLL "BASE ADDRESS + 1" AND "BASE ADDRESS + 0" RESPECTIVELY WHEN BDLAB = 1) |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 12. SERIAL IRQ                                                                                                                                         | 102 |

| 12.1 START FRAME                                                                                                                                       | 102 |

| 12.2 IRQ/DATA FRAME                                                                                                                                    | 102 |

| 12.3 STOP FRAME                                                                                                                                        | 103 |

| 13. CONFIGURATION REGISTER                                                                                                                             | 104 |

| 13.1 CHIP (GLOBAL) CONTROL REGISTER                                                                                                                    | 104 |

| 13.2 LOGICAL DEVICE 0 (FDC)                                                                                                                            | 110 |

| 13.3 LOGICAL DEVICE 1 (PARALLEL PORT)                                                                                                                  | 114 |

| 13.4 LOGICAL DEVICE 2 (UART A)                                                                                                                         | 115 |

| 13.5 LOGICAL DEVICE 3 (UART B)                                                                                                                         | 115 |

| 13.6 LOGICAL DEVICE 5 (KBC)                                                                                                                            | 117 |

| 13.7 LOGICAL DEVICE 6 (CIR)                                                                                                                            | 118 |

| 13.8 LOGICAL DEVICE 7 (GAME PORT AND MIDI PORT AND GPIO PORT 1)                                                                                        | 119 |

| 13.9 LOGICAL DEVICE 8 (GPIO PORT 2)                                                                                                                    | 120 |

| 13.10 LOGICAL DEVICE 9 (GPIO PORT 3,4 ARE POWERED BY STANDBY SOURCE VSB)                                                                               | 122 |

| 13.11 LOGICAL DEVICE A (ACPI)                                                                                                                          | 123 |

| 13.12 LOGICAL DEVICE B (SMART CARD INTERFACE)                                                                                                          | 131 |

| 13.13 LOGICAL DEVICE C (GPIO PORT 5,6,7 THIS POWER OF THE PORTS IS SOURCE VCC)                                                                         | 131 |

| 14. SPECIFICATIONS                                                                                                                                     | 134 |

| 14.1 ABSOLUTE MAXIMUM RATINGS                                                                                                                          | 134 |

| 14.2 DC CHARACTERISTICS                                                                                                                                | 134 |

| 15. APPLICATION CIRCUITS                                                                                                                               | 137 |

| 15.1 PARALLEL PORT EXTENSION FDD                                                                                                                       | 137 |

| 15.2 PARALLEL PORT EXTENSION 2FDD                                                                                                                      | 138 |

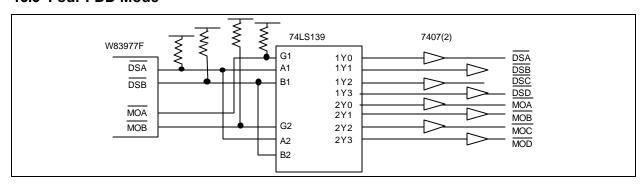

| 15.3 FOUR FDD MODE                                                                                                                                     | 138 |

| 16. ORDERING INSTRUCTION————————————————————————————————————                                                                                           | 139 |

| 17. HOW TO READ THE TOP MARKING                                                                                                                        | 139 |

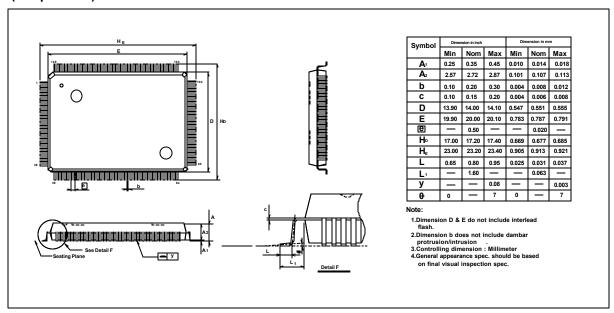

| 18. PACKAGE DIMENSIONS                                                                                                                                 | 140 |

#### GENERAL DESCRIPTION

The W83627SF is the new generation of Winbond's LPC I/O products. It features a whole new interface, namely LPC (Low Pin Count) interface, which is supported in mainstream Intel chip-set. This interface as its name suggests is to provide an economical implementation of I/O's interface with lower pin count and still maintains equivalent performance as its ISA interface counterpart. Approximately 40 pins are saved in LPC I/O comparing to ISA implementation. With this additional freedom, we can implement more devices on a single chip as demonstrated in W83627SF's integration of Game Port and MIDI Port. It is fully transparent in terms of software which means no BIOS or device driver update is needed except chip-specific configuration.

As Smart Card application is gaining more and more attention, W83627SF also implements a smart card reader interface featuring Smart wake-up function. This smart card reader interface fully meets the ISO7816 and PC/SC (Personal Computer/Smart Card Workgroup) standards. W83627SF provides a minimum external components and lowest cost soultion for smart card applications.

The disk drive adapter functions of W83627SF include a floppy disk drive controller compatible with the industry standard 82077/765, data separator, write pre-compensation circuit, decode logic, data rate selection, clock generator, drive interface control logic, and interrupt and DMA logic. The wide range of functions integrated onto the W83627SF greatly reduces the number of components required for interfacing with floppy disk drives. The W83627SF supports four 360K, 720K, 1.2M, 1.44M, or 2.88M disk drives and data transfer rates of 250 Kb/s, 300 Kb/s, 500 Kb/s,1 Mb/s, and 2 Mb/s.

The W83627SF provides two high-speed serial communication ports (UARTs), one of which supports serial Infrared communication. Each UART includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete modem control capability, and a processor interrupt system. Both UARTs provide legacy speed with baud rate up to 115.2k bps and also advanced speed with baud rates of 230k, or 921k bps which support higher speed modems. In addition, the W83627SF provides IR functions: IrDA 1.0 (SIR for 1.152K bps) and TV remote IR (Consumer IR, supporting NEC, RC-5, extended RC-5, and RECS-80 protocols).

The W83627SF supports one PC-compatible printer port (SPP), Bi-directional Printer port (BPP) and also Enhanced Parallel Port (EPP) and Extended Capabilities Port (ECP). Through the printer port interface pins, also available are: Extension FDD Mode and Extension 2FDD Mode allowing one or two external floppy disk drives to be connected.

The configuration registers support mode selection, function enable/disable, and power down function selection. Furthermore, the configurable PnP features are compatible with the plug-and-play feature demand of Windows 95/98<sup>TM</sup>, which makes system resource allocation more efficient than ever.

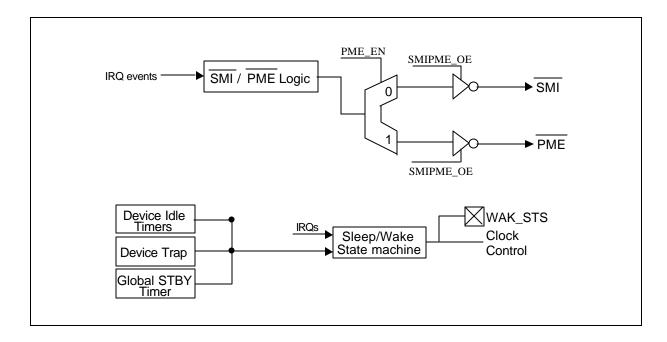

The W83627SF provides functions that complies with **ACPI** (*Advanced Configuration and Power Interface*), which includes support of legacy and ACPI power management through **PME#** or **PSOUT#** function pins. For OnNow keyboard Wake-Up, OnNow mouse Wake-Up, and OnNow CIR Wake-Up. The W83627SF also has auto power management to reduce the power consumption.

The keyboard controller is based on 8042 compatible instruction set with a 2K Byte programmable ROM and a 256-Byte RAM bank. Keyboard BIOS firmware are available with optional AMIKEY<sup>TM</sup> -2, Phoenix MultiKev/42<sup>TM</sup>, or customer code.

The W83627SF provides a set of flexible I/O control functions to the system designer through a set of General Purpose I/O ports. These GPIO ports may serve as simple I/O or may be individually configured to provide a predefined alternate function.

The W83627SF is made to fully comply with **Microsoft PC98 and PC99 Hardware Design Guide**. Moreover, W83627SF is made to meet the specification of PC2000/PC2001's requirement in the power management: **ACPI** and **DPM** (Device Power Management).

The W83627SF contains a game port and a MIDI port. The game port is designed to support 2 joysticks and can be applied to all standard PC game control devices. They are very important for a entertainment or consumer computer.

#### **FEATURES**

#### General

- Meet LPC Spec. 1.01

- Support LDRQ#(LPC DMA), SERIRQ (serial IRQ)

- Compliant with Microsoft PC2000/PC2001 Hardware Design Guide

- Support DPM (Device Power Management), ACPI

- · Programmable configuration settings

- Single 24 or 48 MHz clock input

#### FDC

- Compatible with IBM PC AT disk drive systems

- Variable write pre-compensation with track selectable capability

- Support vertical recording format

- DMA enable logic

- 16-byte data FIFOs

- Support floppy disk drives and tape drives

- Detects all overrun and underrun conditions

- Built-in address mark detection circuit to simplify the read electronics

- FDD anti-virus functions with software write protect and FDD write enable signal (write data signal was forced to be inactive)

- Support up to four 3.5-inch or 5.25-inch floppy disk drives

- Completely compatible with industry standard 82077

- 360K/720K/1.2M/1.44M/2.88M format; 250K, 300K, 500K, 1M, 2M bps data transfer rate

- Support 3-mode FDD, and its Win95/98 driver

#### **UART**

- Two high-speed 16550 compatible UARTs with 16-byte send/receive FIFOs

- MIDI compatible

- Fully programmable serial-interface characteristics:

- --- 5, 6, 7 or 8-bit characters

- --- Even, odd or no parity bit generation/detection

- --- 1, 1.5 or 2 stop bits generation

- Internal diagnostic capabilities:

- --- Loop-back controls for communications link fault isolation

- --- Break, parity, overrun, framing error simulation

- Programmable baud generator allows division of 1.8461 MHz and 24 MHz by 1 to (2<sup>16</sup>-1)

- Maximum baud rate up to 921k bps for 14.769 MHz and 1.5M bps for 24 MHz

#### Infrared

- Support IrDA version 1.0 SIR protocol with maximum baud rate up to 115.2K bps

- Support SHARP ASK-IR protocol with maximum baud rate up to 57,600 bps

- Support Consumer IR

#### **Parallel Port**

- Compatible with IBM parallel port

- Support PS/2 compatible bi-directional parallel port

- Support Enhanced Parallel Port (EPP) Compatible with IEEE 1284 specification

- Support Extended Capabilities Port (ECP) Compatible with IEEE 1284 specification

- Extension FDD mode supports disk drive B; and Extension 2FDD mode supports disk drives A and B through parallel port

- Enhanced printer port back-drive current protection

#### **Keyboard Controller**

- 8042 based with optional F/W from AMIKKEY<sup>TM</sup>-2, Phoenix MultiKey/42<sup>TM</sup> or customer code with 2K bytes of programmable ROM, and 256 bytes of RAM

- Asynchronous Access to Two Data Registers and One status Register

- Software compatibility with the 8042

- Support PS/2 mouse

- Support port 92

- Support both interrupt and polling modes

- Fast Gate A20 and Hardware Keyboard Reset

- 8 Bit Timer/ Counter

- Support binary and BCD arithmetic

• 6 MHz, 8 MHz, 12 MHz, or 16 MHz operating frequency

#### **Game Port**

- Support two separate Joysticks

- Support every Joystick two axis (X,Y) and two button (A,B) controllers

#### **MIDI Port**

- The baud rate is 31.25 Kbaud

- 16-byte input FIFO

- 16-byte output FIFO

#### **General Purpose I/O Ports**

- 40 programmable general purpose I/O ports

- General purpose I/O ports can serve as simple I/O ports, interrupt steering inputs, ,watching

dog timer output, power LED output, infrared I/O pins, KBC control I/O pins, suspend LED

output, RSMRST# signal, PWROK signal, STR(suspend to DRAM) function, VID control

function.

#### **OnNow Functions**

- Keyboard Wake-Up by programmable keys

- Mouse Wake-Up by programmable buttons

- CIR Wake-Up by programmable keys

- SMART Card Wake-up by SCPSNT

- On Now Wake-Up from all of the ACPI sleeping states (S1-S5)

#### **Smart Card Reader Interface**

- PC/SC T=0, T=1 compliant

- ISO7816 protocol compliant

- With 16-byte send/receive FIFOs

- Programmable baud generator

#### **Package**

• 128-pin PQFP

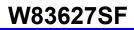

#### **PIN CONFIGURATION FOR W83627SF**

#### 1. PIN DESCRIPTION

Note: Please refer to Section 13.2 DC CHARACTERISTICS for details.

$\rm I/O_{8t}$  - TTL level bi-directional pin with 8 mA source-sink capability  $\rm I/O_{12t}$  - TTL level bi-directional pin with 12 mA source-sink capability

I/O<sub>12tp3</sub>

I/OD<sub>12t</sub>

I/OD<sub>16t</sub>

I/OD<sub>24</sub>

TTL level bi-directional pin open drain output with 12 mA sink capability

TTL level bi-directional pin open drain output with 16 mA sink capability

TTL level bi-directional pin open drain output with 24A sink capability

IN<sub>cs</sub> - CMOS level Schmitt-trigger input pin

IN, - TTL level input pin

IN<sub>td</sub> - TTL level input pin with internal pull down resistor

$IN_{ts}$  - TTL level Schmitt-trigger input pin  $IN_{tso3}$  - 3.3V TTL level Schmitt-trigger input pin

#### 1.1 LPC Interface

| SYMBOL   | PIN   | I/O                  | FUNCTION                                                          |

|----------|-------|----------------------|-------------------------------------------------------------------|

| CLKIN    | 18    | IN <sub>t</sub>      | System clock input. According to the input frequency 24MHz or     |

|          |       |                      | 48MHz, it is selectable through register. Default is 24MHz input. |

| PME#     | 19    | OD <sub>12</sub>     | Generated PME event.                                              |

| PCICLK   | 21    | IN <sub>tsp3</sub>   | PCI clock input.                                                  |

| LDRQ#    | 22    | O <sub>12tp3</sub>   | Encoded DMA Request signal.                                       |

| SERIRQ   | 23    | I/OD12t              | Serial IRQ input/Output.                                          |

| LAD[3:0] | 24-27 | I/O <sub>12tp3</sub> | These signal lines communicate address, control, and data         |

|          |       | ·                    | information over the LPC bus between a host and a peripheral.     |

| LFRAME#  | 29    | IN <sub>tsp3</sub>   | Indicates start of a new cycle or termination of a broken cycle.  |

| LRESET#  | 30    | IN <sub>tsp3</sub>   | Reset signal. It can connect to PCIRST# signal on the host.       |

| SUSCLKIN | 75    | INts                 | 32khz clock input , for CIR only.                                 |

#### 1.2 FDC Interface

| SYMBOL  | PIN | I/O                 | FUNCTION                                                                                                                                                                                                                                                                          |

|---------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRVDEN0 | 1   | OD <sub>24</sub>    | Drive Density Select bit 0.                                                                                                                                                                                                                                                       |

| DRVDEN1 | 2   | OD <sub>12</sub>    | Drive Density Select bit 1. (Default)                                                                                                                                                                                                                                             |

| SMI#    |     | OD <sub>12</sub>    | System Management Interrupt.                                                                                                                                                                                                                                                      |

| IRQIN1  |     | INt                 | Interrupt channel input.                                                                                                                                                                                                                                                          |

| GP27    |     | I/OD <sub>12t</sub> | General purpose I/O port 2 bit 7.                                                                                                                                                                                                                                                 |

| INDEX#  | 3   | IN <sub>cs</sub>    | This Schmitt-triggered input from the disk drive is active low when the head is positioned over the beginning of a track marked by an index hole. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |

| MOA#    | 4   | OD <sub>24</sub>    | Motor A On. When set to 0, this pin enables disk drive 0. This is an open drain output.                                                                                                                                                                                           |

| DSB#    | 5   | OD <sub>24</sub>    | Drive Select B. When set to 0, this pin enables disk drive B. This is an open drain output.                                                                                                                                                                                       |

| DSA#    | 6   | OD <sub>24</sub>    | Drive Select A. When set to 0, this pin enables disk drive A. This is an open drain output.                                                                                                                                                                                       |

| MOB#    | 7   | OD <sub>24</sub>    | Motor B On. When set to 0, this pin enables disk drive 1. This is an open drain output.                                                                                                                                                                                           |

| DIR#    | 8   | OD <sub>24</sub>    | Direction of the head step motor. An open drain output.                                                                                                                                                                                                                           |

|         |     |                     | Logic 1 = outward motion                                                                                                                                                                                                                                                          |

|         |     |                     | Logic 0 = inward motion                                                                                                                                                                                                                                                           |

| STEP#   | 9   | OD <sub>24</sub>    | Step output pulses. This active low open drain output produces a pulse to move the head to another track.                                                                                                                                                                         |

| WD#     | 10  | OD <sub>24</sub>    | Write data. This logic low open drain writes pre-compensation serial data to the selected FDD. An open drain output.                                                                                                                                                              |

| WE#     | 11  | OD <sub>24</sub>    | Write enable. An open drain output.                                                                                                                                                                                                                                               |

| TRAK0#  | 13  | IN <sub>cs</sub>    | Track 0. This Schmitt-triggered input from the disk drive is active low when the head is positioned over the outermost track. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                     |

#### 1.2 FDC Interface, continued

| SYMBOL  | PIN | I/O              | FUNCTION                                                                                                                                                                                                            |

|---------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WP#     | 14  | IN <sub>cs</sub> | Write protected. This active low Schmitt input from the disk drive                                                                                                                                                  |

|         |     |                  | indicates that the diskette is write-protected. This input pin is                                                                                                                                                   |

|         |     |                  | pulled up internally by a 1 $\mbox{K}\Omega$ resistor. The resistor can be                                                                                                                                          |

|         |     |                  | disabled by bit 7 of L0-CRF0 (FIPURDWN).                                                                                                                                                                            |

| RDATA#  | 15  | IN <sub>cs</sub> | The read data input signal from the FDD. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                                            |

| HEAD#   | 16  | OD <sub>24</sub> | Head select. This open drain output determines which disk drive head is active.  Logic 1 = side 0                                                                                                                   |

|         |     |                  | Logic 0 = side 1                                                                                                                                                                                                    |

| DSKCHG# | 17  | IN <sub>cs</sub> | Diskette change. This signal is active low at power on and whenever the diskette is removed. This input pin is pulled up internally by a 1 K resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |

#### 1.3 Multi-Mode Parallel Port

| SYMBOL | PIN | I/O              | FUNCTION                                                                                                                                                                                                                  |

|--------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLCT   | 31  | IN <sub>t</sub>  | PRINTER MODE:                                                                                                                                                                                                             |

|        |     |                  | An active high input on this pin indicates that the printer is selected. Refer to the description of the parallel port for definition of this pin in ECP and EPP mode.                                                    |

|        |     | OD <sub>12</sub> | EXTENSION FDD MODE: WE2#                                                                                                                                                                                                  |

|        |     |                  | This pin is for Extension FDD B; its function is the same as the WE# pin of FDC.                                                                                                                                          |

|        |     | OD <sub>12</sub> | EXTENSION 2FDD MODE: WE2#                                                                                                                                                                                                 |

|        |     |                  | This pin is for Extension FDD A and B; its function is the same as the WE# pin of FDC.                                                                                                                                    |

| PE     | 32  | IN <sub>t</sub>  | PRINTER MODE:                                                                                                                                                                                                             |

|        |     | OD <sub>12</sub> | An active high input on this pin indicates that the printer has detected the end of the paper. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode. EXTENSION FDD MODE: WD2# |

|        |     | 0012             | This pin is for Extension FDD B; its function is the same as the WD# pin of FDC.                                                                                                                                          |

|        |     | OD <sub>12</sub> | EXTENSION 2FDD MODE: WD2#                                                                                                                                                                                                 |

|        |     |                  | This pin is for Extension FDD A and B; its function is the same as the WD# pin of FDC.                                                                                                                                    |

1.3 Multi-Mode Parallel Port, continued

| SYMBOL | PIN | I/O                 | FUNCTION                                                                                                                                                                                                         |

|--------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSY   | 33  | IN <sub>t</sub>     | PRINTER MODE:                                                                                                                                                                                                    |

|        |     |                     | An active high input indicates that the printer is not ready to receive data. Refer to the description of the parallel port for definition of this pin in ECP and EPP mode.                                      |

|        |     | OD <sub>12</sub>    | EXTENSION FDD MODE: MOB2#                                                                                                                                                                                        |

|        |     |                     | This pin is for Extension FDD B; its function is the same as the MOB# pin of FDC.                                                                                                                                |

|        |     | OD <sub>12</sub>    | EXTENSION 2FDD MODE: MOB2#                                                                                                                                                                                       |

|        |     |                     | This pin is for Extension FDD A and B; its function is the same as the MOB# pin of FDC.                                                                                                                          |

| ACK#   | 34  | IN <sub>t</sub>     | PRINTER MODE: ACK#                                                                                                                                                                                               |

|        |     |                     | An active low input on this pin indicates that the printer has received data and is ready to accept more data. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode. |

|        |     | OD <sub>12</sub>    | EXTENSION FDD MODE: DSB2#                                                                                                                                                                                        |

|        |     |                     | This pin is for the Extension FDD B; its functions is the same as the DSB# pin of FDC.                                                                                                                           |

|        |     | OD <sub>12</sub>    | EXTENSION 2FDD MODE: DSB2#                                                                                                                                                                                       |

|        |     |                     | This pin is for Extension FDD A and B; its function is the same as the DSB# pin of FDC.                                                                                                                          |

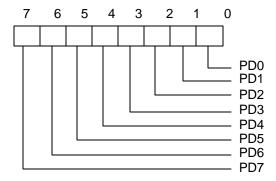

| PD7    | 35  | I/OD <sub>12t</sub> | PRINTER MODE: PD7                                                                                                                                                                                                |

|        |     |                     | Parallel port data bus bit 7. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                                                                                  |

|        |     | -                   | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                              |

|        |     | OD <sub>12</sub>    | EXTENSION 2FDD MODE: DSA2#                                                                                                                                                                                       |

|        |     |                     | This pin is for Extension FDD A; its function is the same as the DSA# pin of FDC.                                                                                                                                |

| PD6    | 36  | I/OD <sub>12t</sub> | PRINTER MODE: PD6                                                                                                                                                                                                |

|        |     |                     | Parallel port data bus bit 6. Refer to the description of the parallel                                                                                                                                           |

|        |     | -                   | port for the definition of this pin in ECP and EPP mode.                                                                                                                                                         |

|        |     |                     | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                              |

|        |     | OD <sub>12</sub>    | EXTENSION. 2FDD MODE: MOA2#                                                                                                                                                                                      |

|        |     |                     | This pin is for Extension FDD A; its function is the same as the MOA# pin of FDC.                                                                                                                                |

| PD5    | 37  | I/O <sub>12t</sub>  | PRINTER MODE: PD5                                                                                                                                                                                                |

|        |     |                     | Parallel port data bus bit 5. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                                                                                  |

|        |     | -                   | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                              |

|        |     | -                   | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                                                                                                             |

#### 1.3 Multi-Mode Parallel Port, continued

| SYMBOL | PIN | I/O                | FUNCTION                                                                                                                        |

|--------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

| PD4    | 38  | I/O <sub>12t</sub> | PRINTER MODE: PD4                                                                                                               |

|        |     |                    | Parallel port data bus bit 4. Refer to the description of the parallel                                                          |

|        |     |                    | port for the definition of this pin in ECP and EPP mode.                                                                        |

|        |     | IN <sub>t</sub>    | EXTENSION FDD MODE: DSKCHG2#                                                                                                    |

|        |     |                    | This pin is for Extension FDD B; the function of this pin is the                                                                |

|        |     |                    | same as the DSKCHG# pin of FDC. It is pulled high internally.                                                                   |

|        |     | IN <sub>t</sub>    | EXTENSION 2FDD MODE: DSKCHG2#                                                                                                   |

|        |     | ,                  | This pin is for Extension FDD A and B; this function of this pin is                                                             |

| DD2    | 20  | 1/0                | the same as the DSKCHG# pin of FDC. It is pulled high internally.                                                               |

| PD3    | 39  | I/O <sub>12t</sub> | PRINTER MODE: PD3                                                                                                               |

|        |     |                    | Parallel port data bus bit 3. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode. |

|        |     | IN <sub>t</sub>    | EXTENSION FDD MODE: RDATA2#                                                                                                     |

|        |     | l "Vt              | This pin is for Extension FDD B; its function is the same as the                                                                |

|        |     |                    | RDATA# pin of FDC. It is pulled high internally.                                                                                |

|        |     | IN <sub>t</sub>    | EXTENSION 2FDD MODE: RDATA2#                                                                                                    |

|        |     | 4                  | This pin is for Extension FDD A and B; its function is the same as                                                              |

|        |     |                    | the RDATA# pin of FDC. It is pulled high internally.                                                                            |

| PD2    | 40  | I/O <sub>12t</sub> | PRINTER MODE: PD2                                                                                                               |

|        |     |                    | Parallel port data bus bit 2. Refer to the description of the parallel                                                          |

|        |     |                    | port for the definition of this pin in ECP and EPP mode.                                                                        |

|        |     | IN <sub>t</sub>    | EXTENSION FDD MODE: WP2#                                                                                                        |

|        |     |                    | This pin is for Extension FDD B; its function is the same as the                                                                |

|        |     |                    | WP# pin of FDC. It is pulled high internally.  EXTENSION. 2FDD MODE: WP2#                                                       |

|        |     | IN <sub>t</sub>    | This pin is for Extension FDD A and B; its function is the same as                                                              |

|        |     |                    | the WP# pin of FDC. It is pulled high internally.                                                                               |

| PD1    | 41  | I/O <sub>12t</sub> | PRINTER MODE: PD1                                                                                                               |

|        | *'  | '' <b>∪</b> 12t    | Parallel port data bus bit 1. Refer to the description of the parallel                                                          |

|        |     |                    | port for the definition of this pin in ECP and EPP mode.                                                                        |

|        |     | IN <sub>t</sub>    | EXTENSION FDD MODE: TRAK02#                                                                                                     |

|        |     | ٠,                 | This pin is for Extension FDD B; its function is the same as the                                                                |

|        |     |                    | TRAK0# pin of FDC. It is pulled high internally.                                                                                |

|        |     | IN <sub>t</sub>    | EXTENSION. 2FDD MODE: TRAK02#                                                                                                   |

|        |     | ,                  | This pin is for Extension FDD A and B; its function is the same as                                                              |

|        |     |                    | the TRAK0# pin of FDC. It is pulled high internally.                                                                            |

#### 1.3 Multi-Mode Parallel Port, continued

| SYMBOL | PIN | I/O                | FUNCTION                                                                                                                |

|--------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------|

| PD0    | 42  | I/O <sub>12t</sub> | PRINTER MODE: PD0                                                                                                       |

|        |     |                    | Parallel port data bus bit 0. Refer to the description of the parallel                                                  |

|        |     |                    | port for the definition of this pin in ECP and EPP mode.                                                                |

|        |     | IN <sub>t</sub>    | EXTENSION FDD MODE: INDEX2#                                                                                             |

|        |     |                    | This pin is for Extension FDD B; its function is the same as the                                                        |

|        |     | 15.1               | INDEX# pin of FDC. It is pulled high internally.                                                                        |

|        |     | IN <sub>t</sub>    | EXTENSION 2FDD MODE: INDEX2#                                                                                            |

|        |     |                    | This pin is for Extension FDD A and B; its function is the same as the INDEX# pin of FDC. It is pulled high internally. |

| SLIN#  | 43  | OD <sub>12</sub>   | PRINTER MODE: SLIN#                                                                                                     |

|        |     |                    | Output line for detection of printer selection. Refer to the                                                            |

|        |     |                    | description of the parallel port for the definition of this pin in ECP                                                  |

|        |     |                    | and EPP mode.                                                                                                           |

|        |     | OD <sub>12</sub>   | EXTENSION FDD MODE: STEP2#                                                                                              |

|        |     |                    | This pin is for Extension FDD B; its function is the same as the STEP# pin of FDC.                                      |

|        |     | 0.0                | EXTENSION 2FDD MODE: STEP2#                                                                                             |

|        |     | OD <sub>12</sub>   | This pin is for Extension FDD A and B; its function is the same as                                                      |

|        |     |                    | the STEP# pin of FDC.                                                                                                   |

| INIT#  | 44  | OD <sub>12</sub>   | PRINTER MODE: INIT#                                                                                                     |

|        |     |                    | Output line for the printer initialization. Refer to the description of                                                 |

|        |     |                    | the parallel port for the definition of this pin in ECP and EPP mode.                                                   |

|        |     |                    | EXTENSION FDD MODE: DIR2#                                                                                               |

|        |     | OD <sub>12</sub>   | This pin is for Extension FDD B; its function is the same as the                                                        |

|        |     |                    | DIR# pin of FDC.  EXTENSION 2FDD MODE: DIR2#                                                                            |

|        |     |                    | This pin is for Extension FDD A and B; its function is the same as                                                      |

|        |     | OD <sub>12</sub>   | the DIR# pin of FDC.                                                                                                    |

| ERR#   | 45  | $IN_t$             | PRINTER MODE: ERR#                                                                                                      |

|        |     |                    | An active low input on this pin indicates that the printer has                                                          |

|        |     |                    | encountered an error condition. Refer to the description of the                                                         |

|        |     |                    | parallel port for the definition of this pin in ECP and EPP mode.  EXTENSION FDD MODE: HEAD2#                           |

|        |     | OD <sub>12</sub>   | This pin is for Extension FDD B; its function is the same as the                                                        |

|        |     | OD <sub>12</sub>   | HEAD#pin of FDC.                                                                                                        |

|        |     | OD <sub>12</sub>   | EXTENSION 2FDD MODE: HEAD2#                                                                                             |

|        |     | 12                 | This pin is for Extension FDD A and B; its function is the same as                                                      |

|        |     |                    | the HEAD# pin of FDC.                                                                                                   |

#### 1.3 Multi-Mode Parallel Port, continued

| SYMBOL | PIN | I/O              | FUNCTION                                                                                                                                                                                                                          |

|--------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AFD#   | 46  | OD <sub>12</sub> | PRINTER MODE: AFD#                                                                                                                                                                                                                |

|        |     |                  | An active low output from this pin causes the printer to auto feed a line after a line is printed. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.  EXTENSION FDD MODE: DRVDEN0 |

|        |     | OD <sub>12</sub> | This pin is for Extension FDD B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                                                              |

|        |     |                  | EXTENSION 2FDD MODE: DRVDEN0                                                                                                                                                                                                      |

|        |     | OD <sub>12</sub> | This pin is for Extension FDD A and B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                                                        |

| STB#   | 47  | OD <sub>12</sub> | PRINTER MODE: STB#                                                                                                                                                                                                                |

|        |     |                  | An active low output is used to latch the parallel data into the printer. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                                                       |

|        |     | -                | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                                               |

|        |     | -                | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                                                                                                                              |

#### 1.4 Serial Port Interface

| SYMBOL | PIN | I/O               | FUNCTION                                                                                                                                                                                              |

|--------|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTSA#  | 49  | IN <sub>t</sub>   | Clear To Send. It is the modem control input.                                                                                                                                                         |

| CTSB#  | 78  |                   | The function of these pins can be tested by reading bit 4 of the handshake status register.                                                                                                           |

| DSRA#  | 50  | IN <sub>t</sub>   | Data Set Ready. An active low signal indicates the modem or data                                                                                                                                      |

| DSRB#  | 79  |                   | set is ready to establish a communication link and transfer data to the UART.                                                                                                                         |

| RTSA#  | 51  | I/O <sub>8t</sub> | UART A Request To Send. An active low signal informs the modem or data set that the controller is ready to send data.                                                                                 |

| HEFRAS |     |                   | During power-on reset, this pin is pulled down internally and is defined as HEFRAS, which provides the power-on value for CR26 bit 6 (HEFRAS). A 4.7 k $\Omega$ is recommended if intends to pull up. |

|        |     |                   | (select 4EH as configuration I/O port's address)                                                                                                                                                      |

#### 1.4 Serial Port Interface, continued

| SYMBOL         | PIN      | I/O               | FUNCTION                                                                                                                                                                                                                                                                 |

|----------------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTSB#          | 80       | I/O <sub>8t</sub> | UART B Request To Send. An active low signal informs the modem or data set that the controller is ready to send data.                                                                                                                                                    |

| ENGMTO         |          |                   | Power on setting pin for enabling Watch Dog timer and its countdown. This pin is pulled down internally and provides the power-on value for bit 0 of CR30 and a count value of 0x0A for CRF6 in logical device 8. A 4.7 k $\Omega$ is recommended if intends to pull up. |

| DTRA#          | 52       | I/O <sub>8t</sub> | UART A Data Terminal Ready. An active low signal informs the modem or data set that the controller is ready to communicate.                                                                                                                                              |

| PNPCSV#        |          |                   | During power-on reset, this pin is pulled down internally and is defined as PNPCSV#, which provides the power-on value for CR24                                                                                                                                          |

|                |          |                   | bit 0 (PNPCSV#). A 4.7 k $\Omega$ is recommended if intends to pull up. (clear the default value of FDC, UARTs, PRT, Game port and MIDI port)                                                                                                                            |

| DTRB#          | 81       | I/O <sub>8t</sub> | UART B Data Terminal Ready. An active low signal informs the modem or data set that controller is ready to communicate.                                                                                                                                                  |

| SINA<br>SINB   | 53<br>82 | IN <sub>t</sub>   | Serial Input. It is used to receive serial data through the communication link.                                                                                                                                                                                          |

| SOUTA          | 54       | I/O <sub>8t</sub> | UART A Serial Output. It is used to transmit serial data out to the communication link.                                                                                                                                                                                  |

| PENKBC         |          |                   | During power-on reset, this pin is pulled down internally and is defined as PENKBC, which provides the power-on value for CR24 bit 2 (ENKBC). A 4.7 k $\Omega$ resistor is recommended if intends to pull up. (enable KBC)                                               |

| SOUTB          | 83       | I/O <sub>8t</sub> | UART B Serial Output.                                                                                                                                                                                                                                                    |

| PEN48          |          |                   | During power-on reset, this pin is pulled down internally and is defined as PEN48, which provides the power-on value for CR24 bit 6 (EN48). A 4.7 k $\Omega$ resistor is recommended if intends to pull up.                                                              |

| DCDA#<br>DCDB# | 56<br>84 | IN <sub>t</sub>   | Data Carrier Detect. An active low signal indicates the modem or data set has detected a data carrier.                                                                                                                                                                   |

| RIA#<br>RIB#   | 57<br>85 | IN <sub>t</sub>   | Ring Indicator. An active low signal indicates that a ring signal is being received from the modem or data set.                                                                                                                                                          |

#### 1.5 KBC Interface

| SYMBOL  | PIN | I/O                 | FUNCTION                                                                                      |

|---------|-----|---------------------|-----------------------------------------------------------------------------------------------|

| KBLOCK# | 58  | INt                 | Keyboard inhibit control input. This pin is after system reset. Internal pull high. (KBC P17) |

| A20GATE | 59  | OUT <sub>12</sub>   | Gate A20 output. This pin is high after system reset. (KBC P21)                               |

| KBRST   | 60  | OUT <sub>12</sub>   | Keyboard reset. This pin is high after system reset. (KBC P20)                                |

| KCLK    | 62  | I/OD <sub>16t</sub> | Keyboard Clock.                                                                               |

| KDATA   | 63  | I/OD <sub>16t</sub> | Keyboard Data.                                                                                |

| MCLK    | 65  | I/OD <sub>16t</sub> | PS2 Mouse Clock.                                                                              |

| MDATA   | 66  | I/OD <sub>16t</sub> | PS2 Mouse Data.                                                                               |

#### 1.6 ACPI Interface

| SYMBOL | PIN | I/O              | FUNCTION                                                                                                                         |

|--------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| PSOUT# | 67  | OD <sub>12</sub> | Panel Switch Output. This signal is used for Wake-Up system from S5 <sub>cold</sub> state. This pin is pulse output, active low. |

| PSIN   | 68  | IN <sub>td</sub> | Panel Switch Input. This pin is high active with an internal pull down resistor.                                                 |

| VBAT   | 74  | PWR              | Battery voltage input.                                                                                                           |

#### 1.7 Game Port & MIDI Port

| SYMBOL | PIN | I/O                 | FUNCTION                                                               |

|--------|-----|---------------------|------------------------------------------------------------------------|

| MSI    | 119 | INt                 | MIDI serial data input.                                                |

| GP20   |     | I/OD <sub>12t</sub> | General purpose I/O port 2 bit 0.                                      |

| MSO    | 120 | OUT12               | MIDI serial data output. (Default)                                     |

| IRQIN0 |     | INt                 | Alternate Function input: Interrupt channel input.                     |

| GPSA2  | 121 | INcs                | Active-low, Joystick I switch input 2. This pin has an internal pull-  |

|        |     |                     | up resistor. (Default)                                                 |

| GP17   |     | I/OD <sub>12t</sub> | General purpose I/O port 1 bit 7.                                      |

| GPSB2  | 122 | INcs                | Active-low, Joystick II switch input 2. This pin has an internal pull- |

|        |     |                     | up resistor. (Default)                                                 |

| GP16   |     | I/OD <sub>12</sub>  | General purpose I/O port 1 bit 6.                                      |

| GPY1   | 123 | I/OD <sub>12</sub>  | Joystick I timer pin. this pin connect to Y positioning variable       |

|        |     |                     | resistors for the Josystick. (Default)                                 |

| GP15   |     | I/OD12t             | General purpose I/O port 1 bit 5.                                      |

| GPY2   | 124 | I/OD <sub>12</sub>  | Joystick II timer pin. this pin connect to Y positioning variable      |

|        |     |                     | resistors for the Josystick. (Default)                                 |

| GP14   |     | I/OD <sub>12t</sub> | General purpose I/O port 1 bit 4.                                      |

| P16    |     | I/OD12t             | Alternate Function Output:KBC P16 I/O port.                            |

| GPX2   | 125 | I/OD <sub>12</sub>  | Joystick II timer pin. this pin connect to X positioning variable      |

|        |     | · <del>-</del>      | resistors for the Josystick. (Default)                                 |

| GP13   |     | I/OD <sub>12t</sub> | General purpose I/O port 1 bit 3.                                      |

| P15    |     | I/OD12t             | Alternate Function Output:KBC P15 I/O port.                            |

#### 1.7 Game Port & MIDI Port, continued

| SYMBOL | PIN | I/O                 | FUNCTION                                                         |

|--------|-----|---------------------|------------------------------------------------------------------|

| GPX1   | 126 | I/OD12              | Joystick I timer pin. this pin connect to X positioning variable |

|        |     |                     | resistors for the Josystick. (Default)                           |

| GP12   |     | I/OD <sub>12t</sub> | General purpose I/O port 1 bit 2.                                |

| P14    |     | I/OD12t             | Alternate Function Output:KBC P14 I/O port.                      |

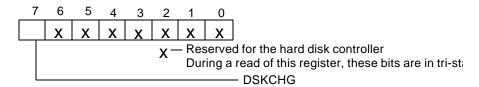

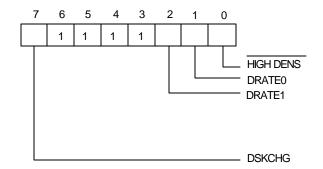

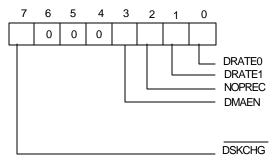

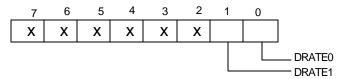

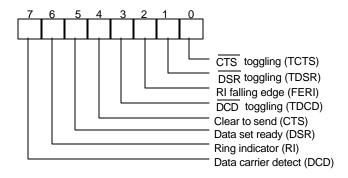

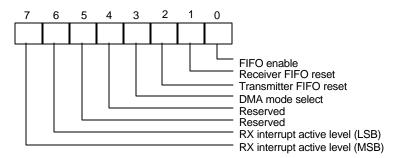

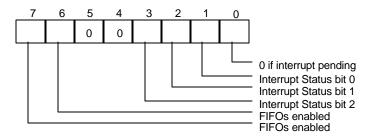

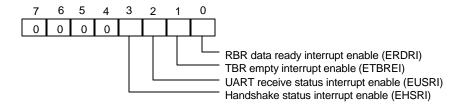

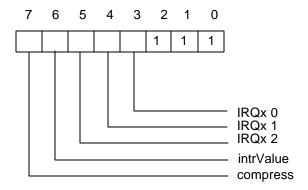

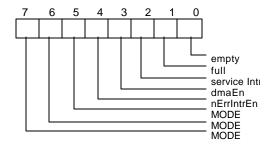

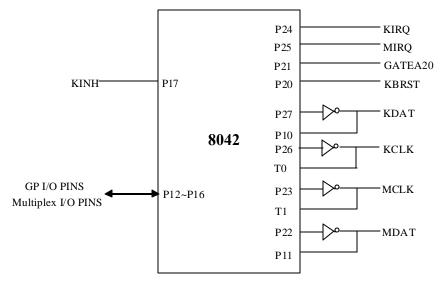

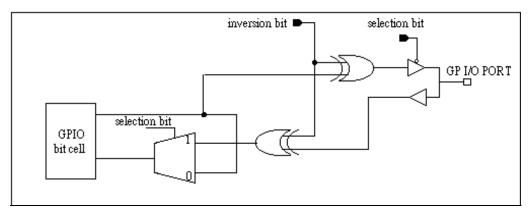

| GPSB1  | 127 | INcs                | Active-low, Joystick II switch input 1. (Default)                |