VMEbus DATA ADDRESS REGISTER FILE (DARF)

- Complete VMEbus address and data interface, except buffers

- Decoupling of CPU and VMEbus

LALMM

- Sustained 25-30 Megabyte/second VMEbus

transfer rate

- Selectable atomic or decoupled mode

- Programmable A32 and A24 slave image bases and sizes

- Programmable access protection

- Integral DMA for local RAM to VMEbus transfers

- Location monitor with 31-longword deep data FIFO

- Low power CMOS implementation

- 224 Pin Grid Array package

- Available in MIL-STD 883C Class B version

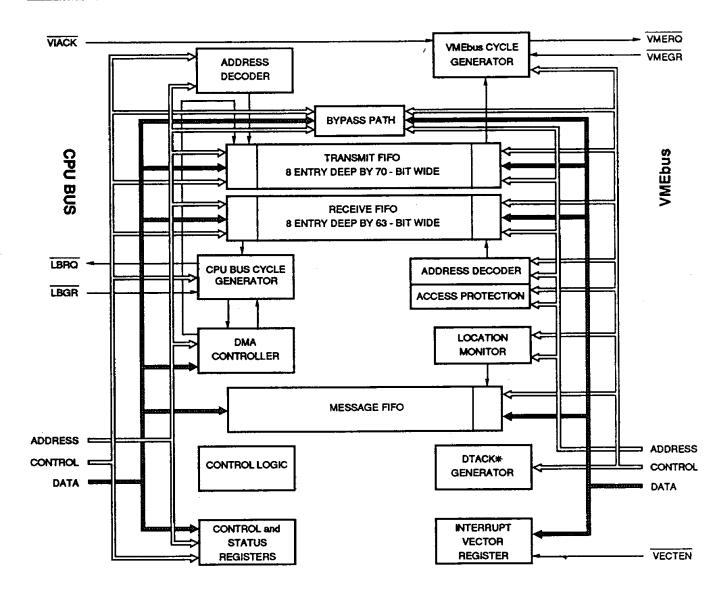

The CA91C015 Data Address Register File (DARF) is one member of the AVICS (Advanced VMEbus Interface Chip Set); the other member being the CA91C014 Advanced System Architecture Control Circuit (ACC). This chip set integrates all the functions commonly required to interface an intelligent card to the VMEbus, while adding features that provide major architectural improvements. The ACC and DARF, while optimized for use together, may also be used individually where appropriate in the system design.

The DARF provides a decoupled address and data path between the VMEbus and the local CPU and memory, and also contains a Location Monitor with an associated message queue.

© Copyright 1990, Newbridge Microsystems, All Rights Reserved

Figure 1 : CA91C015 DARF BLOCK DIAGRAM

1.1

|                    |                    |                    |                     |                    | ·                  |                      |                    |                    |                    |                    |                      |                      |                      |                    |                    |                    |    |

|--------------------|--------------------|--------------------|---------------------|--------------------|--------------------|----------------------|--------------------|--------------------|--------------------|--------------------|----------------------|----------------------|----------------------|--------------------|--------------------|--------------------|----|

| VDATA<br><19>      | VDATA<br><225      | VDATA<br><245      | VDAT/<br><26>       | VDATA<br><31>      | •<br>KADDF<br><02> | R GND                | RESET              | KADOR<br><07>      | ●<br>KADOF<br><095 | •<br>KADOF<br><13> | R KADDI<br><14>      | R KADDI<br><17>      | ●<br>R KADOA<br><21> | R KADDR            | KADDR<br><27>      | KADDR              | `` |

| VDATA<br><15>      | VDD                | VDD                | ♥<br>VDAT/<br><25>  | VDATA              | KADDR<br><005      | ●<br>I KADDR<br><05> | €<br>KADDR<br><05> | TEST<br>MODE       | KADDR<br><11>      | €<br>KADOF<br><18> | ●<br>R KADOF<br><16> | •<br>• KADDF<br><19> | ●<br>KADOK<br><285   | a GND              | ∳<br>VDD           | VDD                | E  |

| VDATA<br><10>      | VDATA<br><17>      | VDATA<br><23 >     | •<br>VDAT/<br>< 30> | VDD                | KADDR<br><01>      | KADDR<br><04>        | KADDR<br><08>      | €<br>KADDR<br><12> | VDD                | KADDF<br><205      | KADDF<br><25>        | KADDF                | •<br>KADDA<br><31>   | ●<br>KFC<br>≪3>    | ●<br>KFC<br>≪⊅     | ●<br>KFC<br><1>    | 0  |

| ♥<br>VDATA<br><08> | VDATA<br><11>      | VDATA<br><205      | VDATA<br><21>       | VDATA<br><27>      | GND                | KADOR<br><035        | VDD                | €<br>KADDR<br><10> | GND                | VDD                | KADDF<br><225        | •<br>KADDF<br><305   | GND                  | VMEINT             | DAINT              | KDATA<br><285      |    |

| VDATA<br><04>      | VDATA<br><14>      | ●<br>VDATA<br><16> | VDATA<br><185       |                    |                    | ●<br>VDATA<br><28>   | ●<br>GND           | GND                | ●<br>KADDR<br><15⊳ | KADDR              |                      | e<br>Key<br>Pin      | VDD                  | €<br>KDATA<br><27> | ●<br>KDATA<br><255 | ●<br>KDATA<br><28> | E  |

| VDD                | VDATA<br><06>      | GND                | ♥<br>VDATA<br><1\$> |                    |                    |                      |                    |                    |                    |                    |                      |                      | ●<br>KDATA<br><31>   | GND                | ●<br>KDATA<br><28> | •<br>KDATA<br><24> | F  |

| ●<br>VDATA<br><01> | ●<br>VDATA<br><09> | ♥<br>VDATA<br><07> | VDATA<br><125       |                    |                    |                      |                    |                    |                    |                    |                      | -                    | ●<br>KDATA<br><30>   | ●<br>KDATA<br><22> | •<br>VDD           | ●<br>KDATA<br><23> | G  |

| VDST               | KWR                | VDATA<br><025      | VDATA<br><035       | ●<br>VDATA<br><05> |                    | <b>C A (</b>         | 040                | 04 5               |                    | DE                 |                      | e<br>GND             | ♦<br>KDATA<br><19>   | 0<br>KDATA<br><17> | ♦<br>KDATA<br><21> | ●<br>KDATA<br><205 | н  |

| AOUT               | ADLY               | VDATA<br><00>      | VDS0                | GND                |                    | CA                   |                    |                    |                    | KF                 |                      | e<br>GND             | ●<br>KDATA<br><15>   | VDD                | KHALT              | e<br>KDATA<br><18> | J  |

|                    | VOTKOLY            | BDLY               | ●<br>TUCB           | GND                |                    |                      | BOTI               | OMIN               | /16₩               |                    |                      | GND                  | ●<br>KDATA<br><10>   | •<br>KDATA<br><125 | ●<br>KDATA<br><14> | ¢<br>KDATA<br><165 | ĸ  |

| VDD                | NOS .              | VMEGR              | end<br>GND          |                    |                    |                      |                    |                    | ,                  |                    |                      |                      | KDATA                | ♦<br>KDATA<br><07> | VDD                | KDATA              | L  |

| MERQ               | VAS                | LBGR               | VIACK               |                    |                    |                      |                    |                    |                    |                    |                      |                      | ●<br>KDATA<br>≪035   | NDATA              | ●<br>KDATA<br>≪08> | KDATA              | м  |

| WORD               | VBERRI             | VIACKRO            | VDTACKI             |                    |                    | ●<br>VADOR<br>⊲01>   | VADOR<br><10>      | GND                | e<br>GND           | e<br>GND           | -                    |                      | DARFSEL              | VOSOLY             | GND                | KDATA              | N  |

| RMC                | •<br>VAM<br><05>   | WR                 | ●<br>VAN<br><04>    | VECTEN             | e<br>GND           | ●<br>VADDR<br><035   | VOD                | KAS                | ●<br>VADDR<br><195 | VADOR<br><25>      | BIMODE               | VSBSEL               | VBERRO               | VUTACKO            | KDATA              | KDATA              | P  |

| ●<br>/AM<br>:03>   | •<br>VAN<br><01>   | ●<br>VAM<br><02>   | ●<br>VAM<br><00>    | VSTRB<br>OUT       | VDATA<br>OUT       | VADDR<br><05>        | VADDR<br><12>      | VADOR<br><14>      | ♥<br>VADOR<br><17> | VADOR              | VADOR<br><27>        | •<br>VDD             | VADOR<br><30>        | KDSACK1            | RAMSEL             | •                  | ٩  |

| 00                 | VDD                |                    | LIARO               | VADDR<br><06>      | ●<br>VADOR<br><09> | VADDR<br><07>        | ●<br>VADDR<br><15> | ●<br>VADDR<br><16> | ●<br>VADDR<br><22> | ●<br>VADDR<br><21> | ●<br>VADOR<br><285   | ●<br>VADOR<br><31>   | ●<br>KSIZE<br><1>    | •<br>VDD           | VDD                | KDATA              | R  |

| REL 1              | KBERR              | VADDR<br><02>      | VADDR<br><045       | VADDR<br><08>      | VADOR<br><11>      | VADOR<br><13>        | KCLK               | ●<br>VADDR<br><18> | VADOR<br><20>      | VADDR<br><24>      | ●<br>VADDR<br>≪26⇒   | VADDR                | •                    | KDSACKO            | VMEOUT             | VASOLY             | s  |

| 17                 | 16                 | 15                 | 14                  | 13                 | 12                 | 11                   | 10                 | 9                  | 8                  | 7                  | 6                    | 5                    | 4                    | 3                  | 2                  |                    | İ  |

Figure 2 : PIN CONFIGURATION for 224-PIN PGA PACKAGE

.

----

4

# Table 1 : DARF PGA PINOUT

| Pin | Signal          | Signal Group        | Pin       | Signal          | Signal Group        |

|-----|-----------------|---------------------|-----------|-----------------|---------------------|

| A1  | KADDR 29        | Local Bus           | C10       | KADDR 08        | Local Bus           |

| A2  | KADDR 27        | Local Bus           | C11       | KADDR 04        | Local Bus           |

| A3  | KADDR 24        | Local Bus           | C12       | KADDR 01        | Local Bus           |

| A4  | KADDR 21        | Local Bus           | C13       | V <sub>DD</sub> |                     |

| A5  | KADDR 17        | Local Bus           | C14       | VDATA 30        | VMEbus              |

| A6  | KADDR 14        | Local Bus           | C15       | VDATA 23        | VMEbus              |

| A7  | KADDR 13        | Local Bus           | C16 .     | VDATA 17        | VMEbus              |

| A8  | KADDR 09        | Local Bus           | C17       | VDATA 10        | VMEbus              |

| A9  | KADDR 07        | Local Bus           | D1        | KDATA 29        | Local Bus           |

| A10 | RESET           | Reset, Clock & Mode | D2        | LMINT           | Reset, Clock & Mode |

| A11 | V <sub>ss</sub> |                     | D3        | VMEINT          | Reset, Clock & Mode |

| A12 | KADDR 02        | Local Bus           | D4        | V <sub>ss</sub> |                     |

| A13 | VDATA 31        | VMEbus              | D5        | KADDR 30        | Local Bus           |

| A14 | VDATA 26        | VMEbus              | D6        | KADDR 22        | Local Bus           |

| A15 | VDATA 24        | VMEbus              | D7        | V <sub>DD</sub> |                     |

| A16 | VDATA 22        | VMEbus              | D8        | V <sub>ss</sub> |                     |

| A17 | VDATA 19        | VMEbus              | D9        | KADDR 10        | Local Bus           |

| B1  | V <sub>DD</sub> |                     | D10       | V <sub>DD</sub> |                     |

| B2  | V <sub>DD</sub> |                     | D11       | KADDR 03        | Local Bus           |

| B3  | V <sub>ss</sub> |                     | D12       | V <sub>ss</sub> |                     |

| B4  | KADDR 28        | Local Bus           | D13       | VDATA 27        | VMEbus              |

| B5  | KADDR 19        | Local Bus           | D14       | VDATA 21        | VMEbus              |

| B6  | KADDR 16        | Local Bus           | D15       | VDATA 20        | VMEbus              |

| B7  | KADDR 18        | Local Bus           | D16       | VDATA 11        | VMEbus              |

| B8  | KADDR 11        | Local Bus           | D17       | VDATA 08        | VMEbus              |

| B9  | TESTMODE        | Reset, Clock & Mode | E1        | KDATA 28        | Local Bus           |

| B10 | KADDR 05        | Local Bus           | E2        | KDATA 25        | Local Bus           |

| B11 | KADDR 06        | Local Bus           | E3        | KDATA 27        | Local Bus           |

| B12 | KADDR 00        | Local Bus           | E4        | V <sub>DD</sub> |                     |

| B13 | VDATA 29        | VMEbus              | E5        | N/C             | (Keying Pin)        |

| B14 | VDATA 25        | VMEbus              | E7        | KADDR 23        | Local Bus           |

| B15 | V <sub>DD</sub> |                     | E8        | KADDR 15        | Local Bus           |

| B16 | V <sub>DD</sub> |                     | E9        | V <sub>ss</sub> |                     |

| B17 | VDATA 15        | VMEbus              | E10       | V <sub>SS</sub> |                     |

| C1  | KFC1            | Local Bus           | E11       | VDATA 28        | VMEbus              |

| C2  | KFC0            | Local Bus           | E14       | VDATA 18        | VMEbus              |

| СЗ  | KFC2            | Local Bus           | E15       | VDATA 16        | VMEbus              |

| C4  | KADDR 31        | Local Bus           | E16       | VDATA 14        | VMEbus              |

| C5  | KADDR 26        | Local Bus           | E17       | VDATA 04        | VMEbus              |

| C6  | KADDR 25        | Local Bus           | F1        | KDATA 24        | Local Bus           |

| C7  | KADDR 20        | Local Bus           | F2        | KDATA 26        | Local Bus           |

| C8  | V <sub>DD</sub> |                     | F3        | V <sub>SS</sub> | Land Dire           |

| C9  | KADDR 12        | Local Bus           | <b>F4</b> | KDATA 31        | Local Bus           |

.

# Table 1 : DARF PGA PINOUT CON'T

| Pin | Signal          | Signal Group        | Pin        | Signal          | Signal Group        |

|-----|-----------------|---------------------|------------|-----------------|---------------------|

| F14 | VDATA 13        | VMEbus              | 12         | V <sub>DO</sub> |                     |

| F15 | V <sub>ss</sub> |                     | L3         | KDATA 07        | Local Bus           |

| F16 | VDATA 06        | VMEbus              | 14         | KDATA 02        | Local Bus           |

| F17 | V <sub>DD</sub> |                     | L14        | V <sub>SS</sub> |                     |

| G1  | KDATA 23        | Local Bus           | L15        | VMEGR           | VMEbus              |

| G2  | V <sub>DD</sub> |                     | L16        | KDS             | Local Bus           |

| G3  | KDATA 22        | Local Bus           | L17        | V <sub>DD</sub> |                     |

| G4  | KDATA 30        | Local Bus           | Mt         | KDATA 11        | Local Bus           |

| G14 | VDATA 12        | VMEbus              | M2         | KDATA 08        | Local Bus           |

| G15 | VDATA 07        | VMEbus              | M3         | KDATA 04        | Local Bus           |

| G16 | VDATA 09        | VMEbus              | M4         | KDATA 03        | Local Bus           |

| G17 | VDATA 01        | VMEbus              | M14        | VIACK           | VMEbus              |

| H1  | KDATA 20        | Local Bus           | M15        | LBGR            | Local Bus           |

| H2  | KDATA 21        | Local Bus           | M16        | VAS             | VMEbus              |

| НЗ  | KDATA 17        | Local Bus           | M17        | VMERQ           | VMEbus              |

| H4  | KDATA 19        | Local Bus           | N1         | KDATA 09        | Local Bus           |

| H5  | V <sub>ss</sub> |                     | N2         | V <sub>ss</sub> |                     |

| H13 | VDATA 05        | VMEbus              | N3         | VDSDLY          | VMEbus              |

| H14 | VDATA 03        | VMEbus              | N4         | DARFCS          | Local Bus           |

| H15 | VDATA 02        | VMEbus              | N7         | v <sub>ss</sub> |                     |

| H16 | KWR             | Local Bus           | N8         | v <sub>ss</sub> |                     |

| H17 | VDS1            | VMEbus              | N9         | V <sub>SS</sub> |                     |

| J1  | KDATA 18        | Local Bus           | N10        | VADDR 10        | VMEbus              |

| J2  | KHALT           | Local Bus           | N11        | VADDR 01        | VMEbus              |

| J3  | V <sub>DD</sub> |                     | N14        | VDTACKI         | VMEbus              |

| J4  | KDATA 15        | Local Bus           | N15        | VIACKRO         | VMEbus              |

| J5  | V <sub>ss</sub> |                     | N16        | VBERRI          | VMEbus              |

| J13 | V <sub>SS</sub> |                     | N17        | VLWORD          | VMEbus              |

| J14 | VDS0            | VMEbus              | P1         | KDATA 06        | Local Bus           |

| J15 | VDATA 00        | VMEbus              | . P2       | KDATA 01        | Local Bus           |

| J16 | ADLY            | Reset, Clock & Mode | P3         | VDTACKO         | VMEbus              |

| J17 | AOUT            | Reset, Clock & Mode | P <b>4</b> | VBERRO          | VMEbus              |

| K1  | KDATA 16        | Local Bus           | P5         | VSBSEL          | VMEbus              |

| K2  | KDATA 14        | Local Bus           | P6         | BIMODE          | Reset, Clock & Mode |

| K3  | KDATA 12        | Local Bus           | P7         | VADDR 25        | VMEbus              |

| K4  | KDATA 10        | Local Bus           | P8         | VADDR 19        | VMEbus              |

| K5  | V <sub>ss</sub> |                     | P9         | KAS             | Local Bus           |

| K13 | V <sub>SS</sub> |                     | P10        | V <sub>DD</sub> |                     |

| K14 | BOUT            | Reset, Clock & Mode | P11        | VADDR 03        | VMEbus              |

| K15 | BDLY            | Reset, Clock & Mode | P12        | V <sub>ss</sub> | 1                   |

| K16 | VDTKDLY         | VMEbus              | P13        | VECTEN          | VMEbus              |

| K17 | KRMC            | Local Bus           | P14        | VAM 04          | VMEbus              |

| L1  | KDATA 13        | Local Bus           | P15        | VWR             | VMEbus              |

4 - 60

\_\_\_\_

# Table 1 : DARF PGA PINOUT CON'T

| Pin | Signal          | Signal Group | Pin  | Signal          | Signal Group        |

|-----|-----------------|--------------|------|-----------------|---------------------|

| P16 | VAM 05          | VMEbus       | R9   | VADDR 16        | VMEbus              |

| P17 | VRMC            | VMEbus       | R10  | VADDR 15        | VMEbus              |

| Q1  | KDATA 05        | Local Bus    | R11  | VADDR 07        | VMEbus              |

| 02  | RAMSEL          | Local Bus    | R12  | VADDR 09        | VMEbus              |

| 03  | KDSACK1         | Local Bus    | R13  | VADDR 06        | VMEbus              |

| Q4  | VADDR 30        | VMEbus       | R14  | LBRQ            | Local Bus           |

| Q5  | V <sub>DD</sub> |              | R15  | VADDROUT        | VMEbus              |

| Q6  | VADDR 27        | VMEbus       | R16  | V <sub>DD</sub> |                     |

| Q7  | VADDR 23        | VMEbus       | R17  | V <sub>DD</sub> |                     |

| Q8  | VADDR 17        | VMEbus       | S1   | VASULY          | VMEbus              |

| Q9  | VADDR 14        | VMEbus       | S2   | VMEOUT          | VMEbus              |

| Q10 | VADDR 12        | VMEbus       | S3   | KDSACKO         | Local Bus           |

| Q11 | VADDR 05        | VMEbus       | S4   | KSIZE0          | Local Bus           |

| Q12 | VDATAOUT        | VMEbus       | S5   | VADDR 29        | VMEbus              |

| Q13 | VSTRBOUT        | VMEbus       | S6   | VADDR 26        | VMEbus              |

| Q14 | VAM 00          | VMEbus       | S7   | VADDR 24        | VMEbus              |

| Q15 | VAM 02          | VMEbus       | S8   | VADDR 20        | VMEbus              |

| Q16 | VAM 01          | VMEbus       | S9   | VADDR 18        | VMEbus              |

| Q17 | VAM 03          | VMEbus       | S10  | KCLK            | Reset, Clock & Mode |

| R1  | KDATA 00        | Local Bus    | S11  | VADDR 13        | VMEbus              |

| R2  | V <sub>DD</sub> |              | S12  | VADDR 11        | VMEbus              |

| R3  | V <sub>DO</sub> |              | S13  | VADDR 08        | VMEbus              |

| R4  | KSIZE1          | Local Bus    | S14. | VADDR 04        | VMEbus              |

| R5  | VADDR 31        | VMEbus       | S15  | VADDR 02        | VMEbus              |

| R6  | VADDR 28        | VMEbus       | S16  | KBERR           | Local Bus           |

| R7  | VADDR 21        | VMEbus       | S17  | BIREL           | Reset, Clock & Mode |

| R8  | VADDR 22        | VMEbus       |      |                 | *                   |

#### Table 2a : LOCAL BUS SIGNALS

The local bus signals are those used to gain access to, or perform data transfers on the local CPU bus. The DARF is designed for parallel connection with a 68020 or 68030 CPU.

| Symbol               | Pin(s)                                                                                                                                                   | Туре | Name and Function                            |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------|

| DARFCS               | N4                                                                                                                                                       | I    | DARF internal registers chip select, input   |

| KADDR 31 - 00        | C4, D5, A1, B4,<br>A2, C5, C6, A3, E7,<br>D6, A4, C7, B5, B7,<br>A5, B6, E8, A6, A7,<br>C9, B8, D9, A8, C10,<br>A9, B11, B10, C11,<br>D11, A12, C12, B12 | VO   | Address bus bits 31 through 00, input/output |

| KAS                  | P9                                                                                                                                                       | vo   | Address strobe, input/output                 |

| KBERR                | S16                                                                                                                                                      | vo   | Data transfer failure, input/output          |

| KDATA 31 00          | F4, G4, D1, E1, E3,<br>F2, E2, F1, G1, G3,<br>H2, H1, H4, J1, H3,<br>K1, J4, K2, L1, K3,<br>M1, K4, N1, M2, L3,<br>P1, Q1, M3, M4, L4,<br>P2, R1         | VO   | Data bus bits 31 through 00, input/output    |

| KDS                  | L16                                                                                                                                                      | VO   | Data strobe, input/output                    |

| KDSACK1 –<br>KDSACK0 | Q3, S3                                                                                                                                                   | VO   | Transfer and size acknowledge, input/output  |

| KFC2 - KFC0          | C3, C1, C2                                                                                                                                               | vo   | Function code indicator bits, input/output   |

| KHALT                | J2                                                                                                                                                       | vo   | CPU halt or retry, input/output              |

| KRMC                 | K17                                                                                                                                                      | vo   | Read-modify-write lock signal, input/output  |

| KSIZE1 - KSIZE0      | R4, S4                                                                                                                                                   | VO   | Data transfer size bits, input/output        |

| KWR                  | H16                                                                                                                                                      | ٧O   | Write signal, input/output                   |

| LBGR                 | M15                                                                                                                                                      | I    | Local bus grant, input                       |

| LBRQ                 | R14                                                                                                                                                      | 0    | Local bus request, output                    |

| RAMSEL               | Q2                                                                                                                                                       | ο    | Local memory enable signal, output           |

### Table 2b : VMEbus SIGNALS

The VMEbus signals are those involved in gaining access to and using the VMEbus. The DARF does not connect directly to the VMEbus; rather, external buffers and transceivers are used for VMEbus control signals and addresses.

| Symbol          | Pin(s)                                                                                                                                                                     | Туре     | Name and Function                             |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------|

| VADDR 31 - 01   | R5, Q4, S5, R6, Q6, S6<br>P7, S7, Q7, R8, R7, S8<br>P8, S9, Q8, R9, R10, Q9<br>S11, Q10, S12, N10<br>R12, S13, R11, R13<br>Q11, S14, P11, S15, N11                         | VO       | Address bits                                  |

| VADDROUT        | , R15                                                                                                                                                                      | 0        | Address transciever direction control         |

| VAM 05 - VAM 00 | P16, P14, Q17,<br>Q15, Q16, Q14                                                                                                                                            | VO       | Address modifier bits                         |

| VAS             | M16                                                                                                                                                                        | VO       | Address strobe                                |

| VASDLY          | S1                                                                                                                                                                         | <u> </u> | Delayed address strobe                        |

| VBERRI          | N16                                                                                                                                                                        | 1        | BERR*                                         |

| VBERRO          | P4                                                                                                                                                                         | 0        | BERR*                                         |

| VDATA 31 00     | A13, C14, B13, E11, D13<br>A14, B14, A15, C15, A16<br>D14, D15, A17, E14, C16<br>E15, B17, E16, F14, G14<br>D16, C17, G16, D17, G15<br>F16, H13, E17, H14; H15<br>G17, J15 | vo       | Data bits                                     |

| VDATAOUT        | Q12                                                                                                                                                                        | 0        | Data transceiver direction control            |

| VDS1 - VDS0     | H17, J14                                                                                                                                                                   | vo       | Data strobes                                  |

| VDSDLY          | N3                                                                                                                                                                         | 1        | Delayed data strobe                           |

| VDTACKI         | N14                                                                                                                                                                        | l        | DTACK*                                        |

| VDTACKO         | P3                                                                                                                                                                         | 0        | DTACK*                                        |

| VDTKDLY         | K16                                                                                                                                                                        | 1        | Delayed DTACK*                                |

| VECTEN          | P13                                                                                                                                                                        | I        | Respond to VMEbus IACK cycle request          |

| VIACK           | M14                                                                                                                                                                        | vo       | IACK* signal                                  |

| VIACKRO         | N15                                                                                                                                                                        | 1        | VMEbus IACK cycle request to DARF             |

| VLWORD          | N17                                                                                                                                                                        | vo       | Long-word signal                              |

| VMEGR           | L15                                                                                                                                                                        | 1        | VMEbus grant input from the ACC               |

| VMEOUT          | S2                                                                                                                                                                         | l        | Off-card data transfer bus select             |

| VMERQ           | M17                                                                                                                                                                        | 0        | VMEbus request output to the ACC              |

| VRMC            | P17                                                                                                                                                                        | vo       | Read-modify-write signal                      |

| VSBSEL          | P5                                                                                                                                                                         | 0        | Auxilliary data transfer bus select           |

| VSTRBOUT        | Q13                                                                                                                                                                        | 0        | Address and data strobe transceiver direction |

| VWR             | P15                                                                                                                                                                        | VO       | Write signal                                  |

| Symbol   | Pin(s) | Туре | Name and Function                               |

|----------|--------|------|-------------------------------------------------|

| ADLY     | J16    | 1    | Delay circuit A input from delay line           |

| AOUT     | J17    | 0    | Delay circuit A output to delay line            |

| BDLY     | K15    |      | Delay circuit B input from delay line           |

| BIMODE   | P6     | 1    | Bl-mode™ signal                                 |

| BIREL    | S17    | 0    | Bi-mode™ release                                |

| BOUT     | K14    | 0    | Delay circuit B output to delay line            |

| KCLK     | S10    | 1    | Clock input, same as the CPU clock              |

| LMINT    | D2     | 0    | Location Monitor FIFO interrupt                 |

| RESET    | A10    |      | Reset input                                     |

| TESTMODE | B9     | 1    | Chip test mode input; for chip fabrication only |

| VMEINT   | D3     | 0    | VMEbus related events interrupt                 |

#### Table 2c : RESET, CLOCK and MODE SIGNALS

#### TERMINOLOGY

Signals on the VMEbus and those within the circuit card may be active high or active low. Active low signals are defined as being true or asserted when they are at a low voltage, and conversely for active high signals. VMEbus active low signals are indicated by the \* suffix, while oncard active low signals that do not connect directly to the VMEbus are indicated with OVERBARS.

Where there is a need to clarify whether a signal is a VMEbus or local signal, a V may be prefixed for VMEbus signals, an L for general local signals, or a K for signals only connecting to the local CPU.

The output type abbreviations used in Tables 3 and 9 are defined in this section. They have both a letter code and a number suffix which indicates their current rating.

For example, the VDATA 31-00 signals are shown as input type CTTL, which are CMOS inputs with normal TTL voltage thresholds, and output type TS4 SR, which are tristateable 4 mA sink and source current outputs with slew rate limiting.

- TP Totem pole output

- TS Tristate totem pole output

- OD Open drain output

- SR Slew rate limited output

- CTTL CMOS input with TTL thresholds

- CTTL PD CMOS input, TTL thresholds, integral pull down

- CTTL PU CMOS input, TTL thresholds, integral pull up

\_\_\_\_\_

| Signal            | Input   | Output | Signal          | Input | Output |

|-------------------|---------|--------|-----------------|-------|--------|

| ADLY              | CTTL    |        | TESTMODE        | CTTL  |        |

| AOUT              |         | TP4    | VADDR 31-01     | CTTL  | TS4 SR |

| BDLY              | CTTL    |        | VADDROUT        | CTTL  | TS4    |

| BIMODE            | CTTL    |        | VAM 05 - VAM 00 | CTTL  | TS4    |

| BIREL             |         | TP2    | VAS             | CTTL  | TS4    |

| BOUT              |         | TP4    | VASDLY          | CTTL  |        |

| DARFCS            | CTTL    |        | VBERRI          | CTTL  |        |

| DTACKDLY          | CTTL    |        | VBERRO          |       | TP4    |

| KADDR 31 - 00     | CTTL    | TS6    | VDATA 31 - 00   | CTTL  | TS4 SR |

| KAS               | CTTL    | TS8    | VDATAOUT        |       | TP4    |

| KBERR             | CTTL    | OD8    | VDS1 - VDS0     | CTTL  | TS4    |

| KCLK              | CTTL    |        | VDSDLY          | CTTL  |        |

| KDATA 31 - 00     | CTTL PU | TS6    | VDTACKI         | CTTL  |        |

| KDS               |         | TS8    | VDTACKO         |       | TP4    |

| KDSACK1 - KDSACKO | CTTL    | TS8    | VECTEN          | CTTL  |        |

| KFC 1             |         | TS6    | VIACK           | CTTL  | TS4    |

| KFC 2,0           | CTTL    | TS6    | VIACKRQ         | CTTL  |        |

| KHALT             |         | OD12   | VLWORD          | CTTL  | TS4    |

| KRMC              | CTTL    | TS8    | VMEGR           | CTTL  |        |

| KSIZE1 - KSIZE0   | CTTL    | TS8    | VMEINT          |       | TP2    |

| KWR               | CTTL    | TS8    | VMEOUT          | CTTL  |        |

| LBGR              | CTTL    |        | VMERQ           |       | TP2    |

| LBRQ              |         | TP2    | VRMC            | CTTL  | TS4    |

| LMINT             |         | TP2    | VSBSEL          |       | TP4    |

| RAMSEL            |         | TP4    | VSTRBOUT        |       | TP4    |

| RESET             | CTTL    |        | VWR             | CTTL  | TS4    |

# Table 3 : Input and Output Type General Classification

4

|                  |                                            |       |       | Limits  |    |      |  |

|------------------|--------------------------------------------|-------|-------|---------|----|------|--|

| Symbol           | Description                                | Cik   | Min   | Max     |    | Unit |  |

|                  |                                            | Count |       | Com Mil |    |      |  |

|                  | Clock frequency                            | -     | -     | 25      | 20 | MHz  |  |

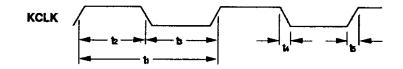

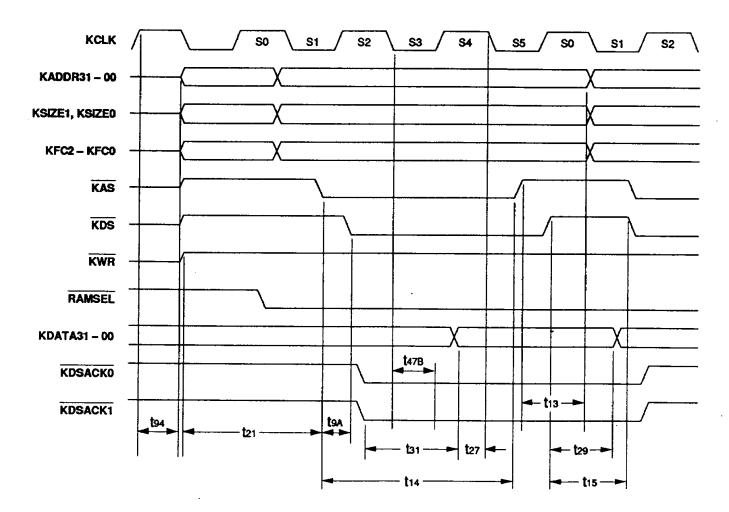

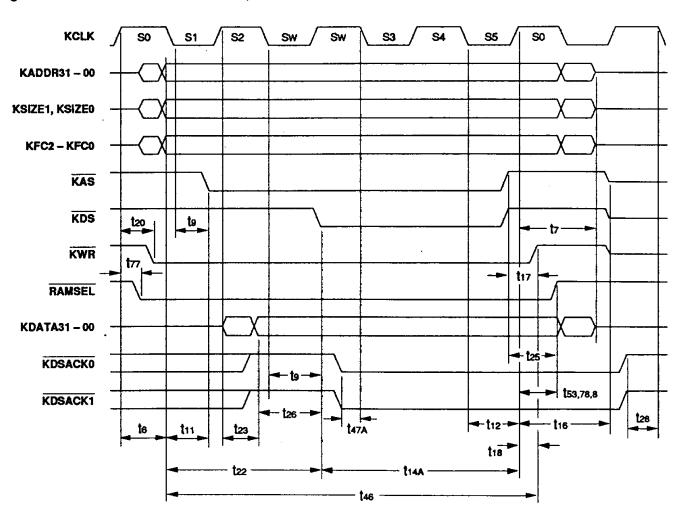

| <b>t</b> ,       | KCLK cycle time                            | •     | 40/50 |         |    | ns   |  |

| t <sub>2</sub>   | KCLK pulse width low                       | •     | 17/22 | •       | •  | ns   |  |

| t <sub>3</sub>   | KCLK pulse width high                      | •     | 17/22 | •       | •  | ns   |  |

| t <sub>4,5</sub> | KCLK rise and fall times                   | •     | •     | 5       | 5  | ns   |  |

| t <sub>e</sub>   | KCLK high to address valid                 | -     | 5     | 40      | 47 | ns   |  |

| t <sub>7</sub>   | KCLK high to address tri-state             | -     | 5     | 30      | 35 | ns   |  |

| t <sub>8</sub>   | KCLK high to address invalid               | -     | 5     | -       | -  | ns   |  |

| t <sub>9</sub>   | KCLK low to KAS, KDS asserted              | •     | 4     | 25      | 30 | ns   |  |

| t <sub>9A</sub>  | KAS to KDS skew (read) (Note 1)            | •     | -15   | 10      | 15 | ns   |  |

| t <sub>11</sub>  | Address valid to KAS asserted              |       | 4     |         | -  | ns   |  |

| t <sub>12</sub>  | KCLK low to KAS, KDS negated               | •     | 4     | 25      | 30 | ns   |  |

| t <sub>13</sub>  | KAS negated to address invalid (Note 3)    | 0.5   | 0     | -       | -  | ns   |  |

| t <sub>14</sub>  | KAS width asserted (Note 3)                | 2.0   | -5    | -       | -  | ns   |  |

| t <sub>i4A</sub> | KDS width asserted (write) (Note 3)        | 1.0   | -5    | -       | -  | ns   |  |

| t <sub>15</sub>  | KAS & KDS width negated (Note 3)           | 1.0   | 0     | •       | •  | ns   |  |

| t <sub>16</sub>  | KCLK high to KAS tri-state                 | -     | 4     | 25      | 30 | ns   |  |

| t <sub>17</sub>  | KAS, KDS high to KWR invalid (Note 3)      | 0.5   | -2    | -       | -  | ns   |  |

| t <sub>18</sub>  | KCLK high to KWR high                      |       | 4     | 25      | 30 | ns   |  |

| t <sub>20</sub>  | KCLK high to KWR low                       | -     | 4     | 30      | 35 | ns   |  |

| t <sub>21</sub>  | KWR high to KAS asserted (Note 3)          | 0.5   | -5    | -       | -  | ns   |  |

| t <sub>22</sub>  | KWR low to KDS asserted (Notes 3 & 6)      | 1.5   | 0     | -       | •  | ns   |  |

| t <sub>23</sub>  | KCLK high to data out valid                | -     | 5     | 30      | 36 | ns   |  |

| t <sub>25</sub>  | KDS high to data out invalid (Notes 3 & 6) | 0.5   | 0     | •       | -  | ns   |  |

| t <sub>26</sub>  | Data out valid to KDS low (Notes 3 & 6)    | 0.5   | -7    | •       | -  | ns   |  |

| t <sub>27</sub>  | Data in valid to KCLK low                  |       | 5     | •       | -  | ns   |  |

| t_27A            | Late KBERR to KCLK high (Notes 5)          | ++    | 5     | -       | -  | ns   |  |

| t <sub>28</sub>  | KDSACK high to next S2 low                 |       | 5     | -       | -  | ns   |  |

| t <sub>29</sub>  | KDS high to data hold time                 |       | 0     | -       | -  | ns   |  |

| t <sub>31</sub>  | KDSACK low to data in valid (Notes 2 & 3)  | 1.0   | -     | 2       | 5  | ns   |  |

| t46              | KWR width low (Notes 3)                    | 4.0   | 5     | -       | -  | ns   |  |

# Table 4 : AC CHARACTERISTICS (DARF LOCAL BUS MASTERSHIP)

# Table 4 :AC CHARACTERISTICS (DARF LOCAL BUS MASTERSHIP)CONT(Commercial $T_A = 0^\circ$ to +70°C, $V_{DD} = 5V \pm 5\%$ , Military $T_A = -55^\circ$ to +125°C, $V_{DD} = 5V \pm 10\%$ )

| Symbol           | Description                               | Cik   | Min | M   | Unit |    |

|------------------|-------------------------------------------|-------|-----|-----|------|----|

|                  |                                           | Count |     | Com | Mil  |    |

| t <sub>47A</sub> | Asynchronous input setup time (Notes 5)   | -     | 5   | -   | -    | ns |

| t <sub>478</sub> | Asynchronous input hold time              | -     | 5   | •   | -    | ns |

| t <sub>48</sub>  | KDSACK asserted to KBERR low (Notes 3, 4) | 2.5   | •   | 0   | 0    | ns |

| t <sub>53</sub>  | Data out hold from KCLK high              | •     | 5   | -   |      | ns |

#### Notes:

1. This number can be reduced to 2 ns if strobes have equal loads.

- If the asynchronous setup time (t<sub>47</sub>) requirements are met, the KDSACKn low to data setup time (t<sub>31</sub>) can be ignored. The data must only satisfy the data-in to clock low setup time (t<sub>27</sub>) for the following clock cycle, KBERR must only satisfy the later KBERR/ low to clock high setup time (t<sub>27A</sub>) for the following clock cycle.

- 3. This timing parameter is the sum of the number listed and the product of the CLK COUNT times the period of the CPU clock.

eg:  $t_{21} = -5 + (0.5 \times t_{KCLK})$  ns

- 4. This specification applies to the first KDSACKn signal asserted. In the absence of KDSACKn, KBERR is an asynchronous input using the asynchronous input setup time  $(t_{47})$ . Timing paramter  $t_{27A}$  must also be met for a late KBERR.

- 5. This timing parameter applies for all asynchronous inputs: KDSACK0, KDSACK1, KBERR, LBGR and VMEGR.

- 6. Actual value depends on the clock input waveform.

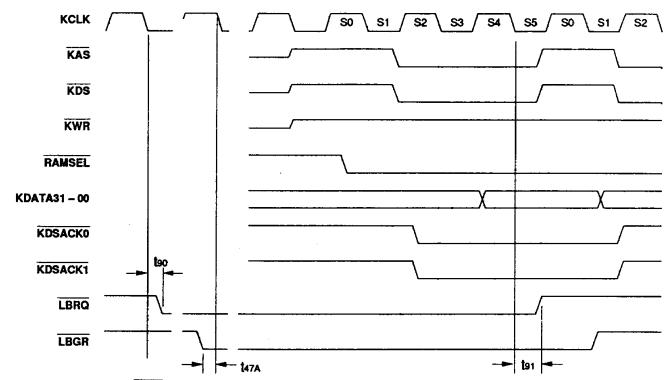

# Table 5 :AC CHARACTERISTICS (DARF BUS ARBITRATION)<br/>(Commercial $T_A = 0^\circ$ to +70°C, $V_{DD} = 5V \pm 5\%$ , Military $T_A = -55^\circ$ to +125°C, $V_{DD} = 5V \pm 10\%$ )

|                 |                                             |         |     | *   | Unit |                   |  |

|-----------------|---------------------------------------------|---------|-----|-----|------|-------------------|--|

| Symbol          | Description                                 | Cik     | Min | M   |      |                   |  |

|                 |                                             | Count   |     | Com | Mii  | <u> </u>          |  |

| t <sub>90</sub> | KCLK low to LBRO asserted                   | -       | 3   | 20  | 25   | ns                |  |

| t <sub>91</sub> | KCLK low to LBRQ negated                    | -       | 3   | 20  | 25   | ns                |  |

| t <sub>92</sub> | KCLK low to VMERQ asserted                  | •       | 3   | 20  | 25   | ns                |  |

| t <sub>93</sub> | KCLK low to VMERQ negated                   | •       | 3   | 20  | 25   | ns                |  |

| <sup>t</sup> 94 | KCLK high to KADDR, KFC, KSIZE buses driven | -       | 5   | -   | -    | ns                |  |

| t <sub>95</sub> | LBGR low to DARF S0 (Note 1)                | 3.5/4.5 | •   | •   | •    | t <sub>kCLK</sub> |  |

Notes:

1. This timing parameter is the sum of the number listed and product of the CLK COUNT times the period of the CPU clock.

eg: t<sub>21</sub> = -5 + (0.5 x t<sub>KCLK</sub>) ns

# Figure 3 : INPUT CLOCK WAVEFORM TIMING

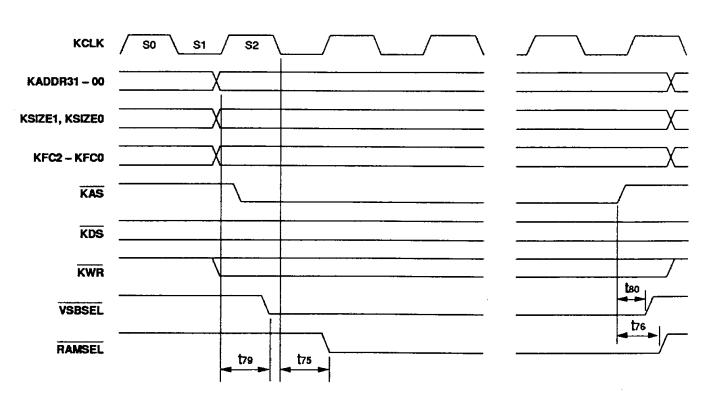

# Figure 4a : DARF MASTER INTERFACE, MEMORY READ

### Figure 4b : DARF MASTER INTERFACE, MEMORY WRITE

CA91C015

#### Figure 5 : DARF BUS ARBITRATION, CPU BUS REQUEST

Note: LBRQ is only released if another cycle is not pending. If LBRQ is released early, it is done 2 clocks after KAS is asserted.

| Symbol           | Description                             | Cik   | Min | M   | ax   | Unit |

|------------------|-----------------------------------------|-------|-----|-----|------|------|

|                  |                                         | Count |     | Com | Mil  | ]    |

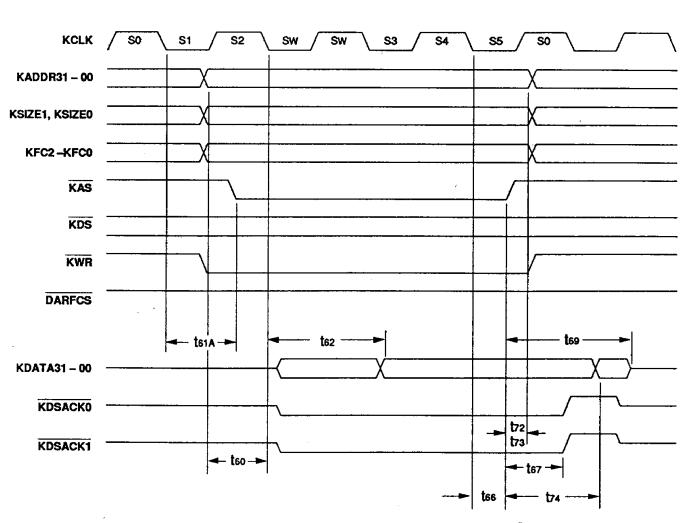

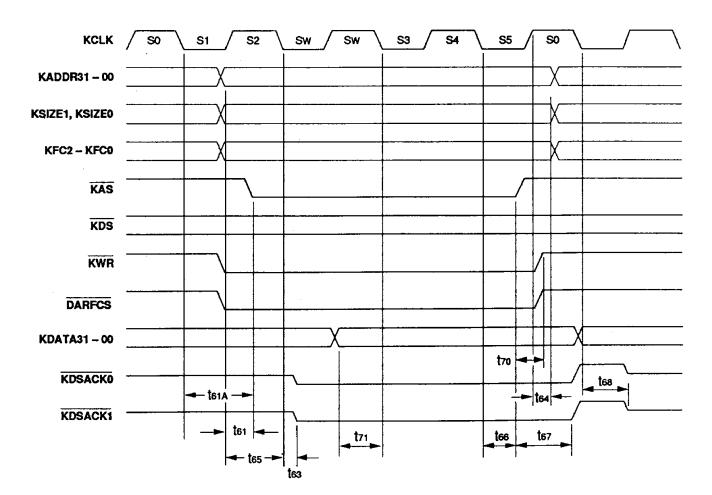

| t <sub>60</sub>  | KWR, etc valid to S3 low (Note 1)       |       | -   | 26  | 40   | ns   |

| t <sub>61</sub>  | KAS setup to S3 low                     |       | 5   | -   | -    | ns   |

| t <sub>61A</sub> | KAS delay from S1 low                   |       | 2   | •   | -    | ns   |

| t <sub>62</sub>  | KCLK low to data valid (read)           | -     | 5   | 40  | 80   | ns   |

| t <sub>63</sub>  | S3 low to KDSACKn asserted              | -     | 5   | 30  | 40   | ns   |

| t <sub>64</sub>  | S0 high to address invalid              | -     | 0   | -   |      | ns   |

| t <sub>65</sub>  | Address valid to S3 low (Note 1)        | •     | -   | 26  | 40   | ns   |

| t <sub>66</sub>  | S5 low to KAS high                      |       | 0   | •   | -    | ns   |

| t <sub>67</sub>  | KAS high to KDSACKn high                | -     | 3   | 20  | 30   | ns   |

| t <sub>68</sub>  | S0 low to KDSACKn tri-state             | -     | 4   | 25  | 35   | ns   |

| t <sub>69</sub>  | KAS high to data tri-state (read)       |       | 5   | 35  | 40   | ns   |

| t <sub>70</sub>  | KAS high to KWR invalid (Note 1)        | -     | -   | 10  | 12   | ns   |

| <b>Ļ</b> 1       | Data setup time to S4 low               | •     | 5   | -   | -    | ns   |

| t <sub>72</sub>  | KAS high to KFC[2-0] invalid            |       | 0   | -   | -    | ns   |

| t <sub>73</sub>  | KAS high to KSIZE[1-0] invalid (Note 1) | •     | -   | 10  | 12   | ns   |

| t <sub>74</sub>  | KAS high to data invalid (read)         |       | 4   | 20  | 25   | ns   |

| t <sub>75</sub>  | KCLK low to RAMSEL low, VMEout          | •     | 4   | 25  | 30   | ns   |

| t <sub>76</sub>  | KAS high to RAMSEL high, VMEout         |       | 3   | 20  | 25   | ns   |

| t <sub>77</sub>  | KCLK high to RAMSEL low, VMEin          | -     | 4   | 21  | 25 . | ns   |

| t <sub>78</sub>  | KCLK high to RAMSEL high, VMEin         | -     | 3   | 20  | 25   | ns   |

| t <sub>79</sub>  | Address valid to VSBSEL low             |       | 23  | 40  | 55   | ns   |

| t <sub>80</sub>  | KAS high to VSBSEL high                 |       | 2   | 15  | 20   | ns   |

| t <sub>81</sub>  | KCLK low to LMINT low                   | •     | 7   | 35  | 45   | ns   |

| t <sub>82</sub>  | KCLK low to BIREL low                   | -     | 4   | 25  | 30   | ns   |

| t <sub>83</sub>  | KCLK low to BIREL high                  |       | 3   | 20  | 25   | ns   |

# Table 6 :AC CHARACTERISTICS (DARF LOCAL BUS SLAVE INTERFACE)<br/>(Commercial $T_A = 0^{\circ}$ to +70°C, $V_{DD} = 5V \pm 5\%$ , Military $T_A = -55^{\circ}$ to +125°C, $V_{DD} = 5V \pm 10\%$ )

Note:

1. This timing parameter is actually a *minimum* time which must be provided for the given operation condition.

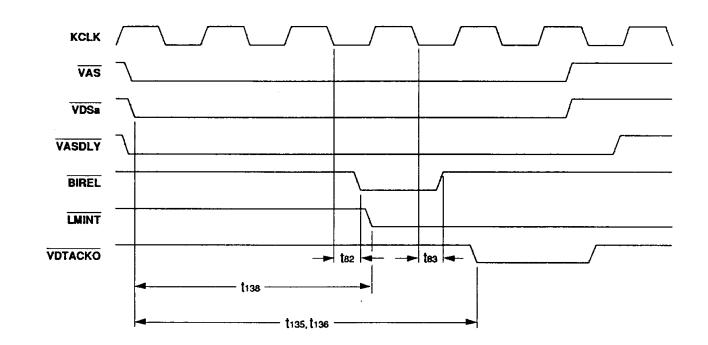

# Figure 7a : DARF SLAVE INTERFACE, CPU REGISTER READ

### Figure 7B : DARF SLAVE INTERFACE, CPU REGISTER WRITE

ž

### Figure 8 : DARF SLAVE INTERFACE, VSB and DVA DECODING

Note: DVA and VSBSEL will not be asserted on the same cycle. Both are shown here for illustration only.

#### KCLK S0 S2 SW SW SW SW S3 **S4 S**5 S0 **S**1 KADDR31 - 00 KSIZE1, KSIZE0 KFC2 - KFC0 KAS KDS KWR DARFCS KDATA31 - 00 LMINT **t**82 BIREL - **t**81-• te3-4 KDSACK0 KDSACK1

#### Figure 9 : DARF SLAVE INTERFACE, CPU LOCATION MONITOR WRITE

Note:

This diagram assumes that the CPU is allowed access to the Location Monitor without waiting for the VMEbus to finish a write cycle.

If the VMEbus is writing to the FIFO, a minimum of two wait states are added, depending on the DSB\* release time of the VME master.

If the LM FIFO is full, wait states are added indefinitely.

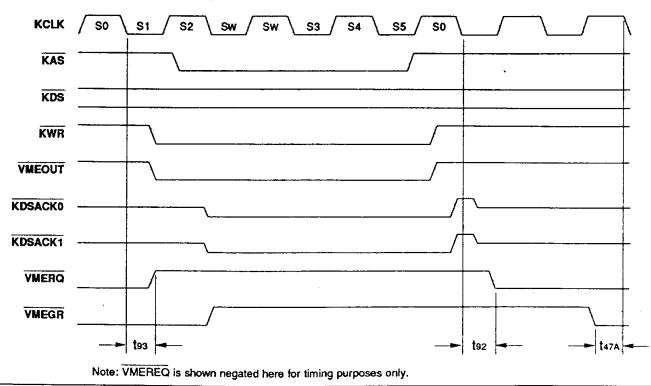

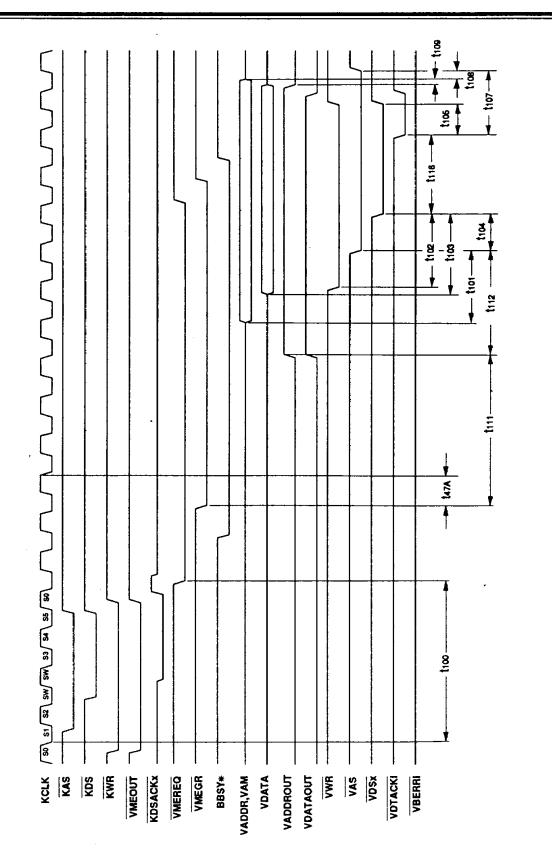

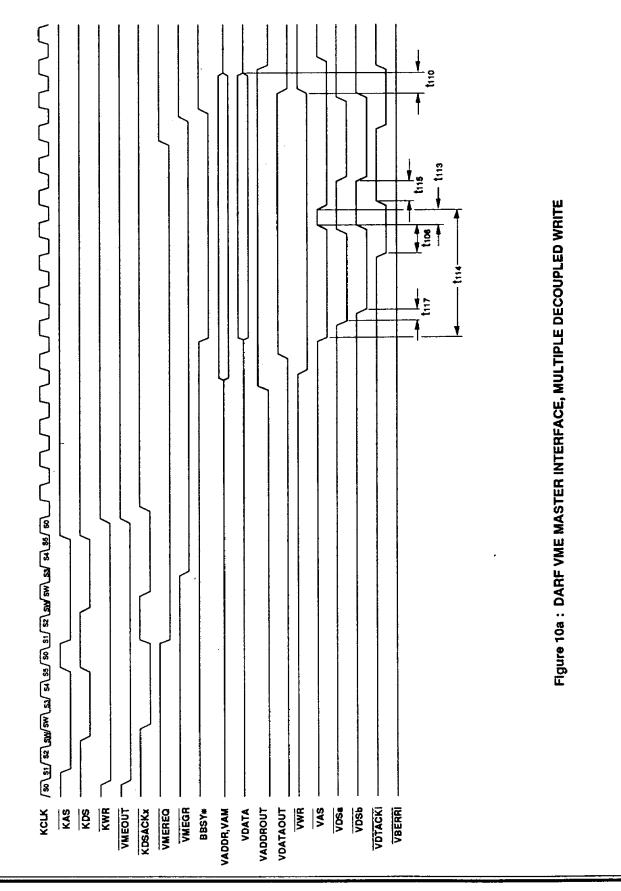

# Table 7 : AC CHARACTERISTICS (DARF VMEbus MASTERSHIP)

(Commercial  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$ )

| Symbol            | Description                                                               | Cik<br>Count | Limits |     |     |      |

|-------------------|---------------------------------------------------------------------------|--------------|--------|-----|-----|------|

|                   |                                                                           |              | Min    | Max |     | Unit |

|                   |                                                                           |              |        | Com | Mil |      |

| t <sub>100</sub>  | S1 clock low to VMERQ asserted (Note 3)                                   | 4            | 3      | 20  | 25  | ns   |

| t <sub>101</sub>  | VADDR, VAM valid to VAS asserted                                          | -            | 38     | -   | -   | ns   |

| t <sub>102</sub>  | VWR valid to VDSa asserted (Note 3)                                       | 1            | 30     | -   | -   | ns   |

| t <sub>103</sub>  | VDATA valid to VDSa asserted                                              | -            | 40     | -   | -   | ns   |

| t <sub>104</sub>  | VAS asserted to VDSa asserted                                             | -            | 2      | •   | -   | ns   |

| t <sub>105</sub>  | VDTACKI low to VDSb negated,<br>Decoupled VME access                      | -            | 5      | 30  | 35  | ns   |

| t <sub>105A</sub> | VDTACKI low to VDSb negated,<br>Atomic VME access (Note 4)                | •            | 45     | 70  | 75  | ns   |

| t <sub>106</sub>  | VDTACKI low to VAS negated,<br>Decoupled VME access with cycle pending    | -            | 5      | 35  | 40  | ns   |

| t <sub>107</sub>  | VDTACKI low to VAS negated,<br>Decoupled VME access without cycle pending | -            | 15     | 85  | 100 | ns   |

| t <sub>107A</sub> | VDTACKI low to VAS negated,<br>Atomic VME access (Note 4, 5 & 6)          | -            | 55     | 125 |     | ns   |

| t <sub>108</sub>  | VME buffers tri-state to VAS negated                                      | -            | 3      | 20  | 25  | ns   |

| t <sub>109</sub>  | VADDROUT low to VME buffers tri-state                                     | -            | 0      | 5   | 6   | ns   |

| t <sub>110</sub>  | VDATAOUT low to VDATA tri-state                                           | -            | 1      | 7   | 9   | ns   |

| t <sub>111</sub>  | VMEGR low to VADDROUT,<br>VDATAOUT asserted (Note 3)                      | 2/3          | 4      | 25  | 30  | ns   |

| t <sub>112</sub>  | VADDROUT asserted to VAS low (Note 3)                                     | 1            | 45     | 75  | 85  | ns   |

| t <sub>113</sub>  | VAS, VDSn minimum high time (Note 4)                                      | -            | 45     | -   | · · | ns   |

| t <sub>114</sub>  | VME cycle time, VAS to VAS (Note 1)                                       | •            | 101    | 173 | 194 | ns   |

| t <sub>115</sub>  | VDTACKI high to VDSa asserted                                             | <b>_</b> ·   | 5      | -   | -   | ns   |

| t <sub>116</sub>  | VDSa low to VDTACKI asserted                                              | -            | 20     | -   | •   | ns   |

| t <sub>117</sub>  | VDSa low to VDSb low (Note 7)                                             | •            | 0      | 5   | 7   | ns   |

| t <sub>118</sub>  | VDTACKI low to KDSACKn asserted (Note 2, 4)                               | -            | 45     | 75  | 80  | ns   |

| t <sub>119</sub>  | VMEGR low to VAS asserted (Note 3, 4 & 8)                                 | 3/4          | 50     | 100 | 115 | ns   |

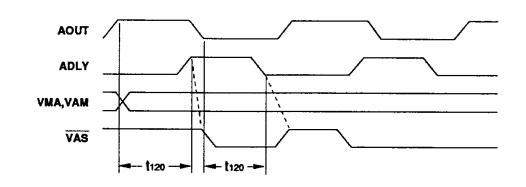

| t <sub>120</sub>  | AOUT edge to ADLY edge                                                    | -            | 37     | 43  | 43  | ns   |

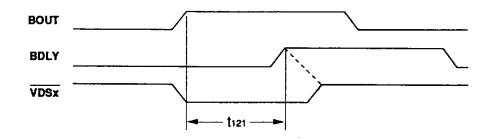

| t <sub>121</sub>  | BOUT high to BDLY high                                                    | -            | 37     | 43  | 43  | ns   |

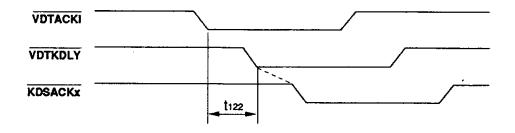

| t <sub>122</sub>  | VDTACKI low to VDTKDLY low                                                | •            | 35     | 45  | 45  | ns   |

Notes: see next page //

Notes:

- 1. This cycle time applies only to the DARF operating in loopback mode. This time represents the maximum obtainable transfer rate under *ideal* conditions.

- 2. This parameter applies to Atomic VME accesses only.

- 3. This timing parameter is the sum of the number listed and product of the CLK COUNT times the period of the CPU clock. eg:  $t_{21} = -5 + (0.5 \times t_{KCLK})$  ns

- 4. This parameter assumes that a 40ns delay line is used to generate ADLY, BDLY, VDSDLY, and VDTKDLY.

- 5. In the case of RMW cycles, the release time of KRMC controls the release of VAS when the TASCON bit is set. The release of KRMC controls the release of VADDR, VAM, and VRMC regardless of the state of the TASCON bit.

- 6. The minimum low time for VAS is (3 x t<sub>KCLK</sub> 5ns) and may override this parameter, depending on the Slave Response time.

- 7. If the loading on the two outputs is equal, the skew can be reduced to 2ns.

- 8. This parameter assumes that previous VMEbus cycle is complete and that VMEbus ownership can be taken without further delay.

Downloaded from Elcodis.com electronic components distributor

4 - 80

4 - 81

### Figure 13 : DARF DELAY LINE TIMING, VMEbus MASTER CYCLES

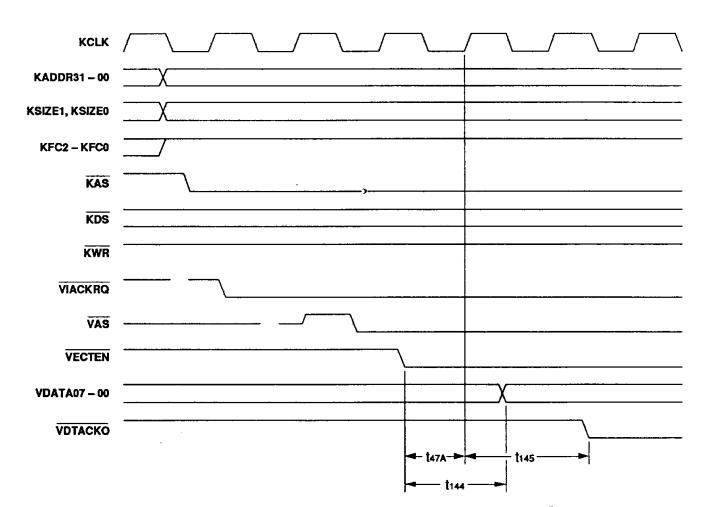

# Figure 14 : DARF MASTER INTERFACE, VMEbus Iack CYCLE

# Table 8 : AC CHARACTERISTICS (DARF VMEbus SLAVE INTERFACE) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2) (2)</td

(Commercial  $T_A = 0^{\circ}$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^{\circ}$  to +125°C,  $V_{DD} = 5V \pm 10\%$ )

| Symboi            | Description                                                         | Cik<br>Count |     |                  |                  |      |

|-------------------|---------------------------------------------------------------------|--------------|-----|------------------|------------------|------|

|                   |                                                                     |              | Min | Max              |                  | Unit |

|                   |                                                                     |              |     | Com              | Mil              | ]    |

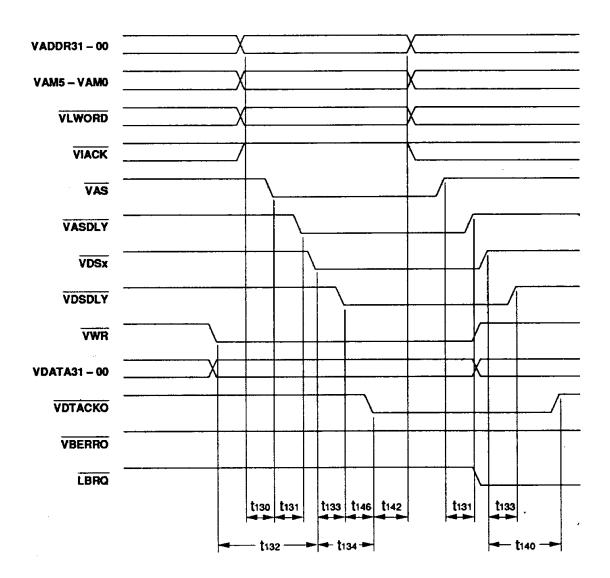

| t <sub>130</sub>  | VADDR, VAM, VLWORD, VIACK<br>setup to VAS low                       | -            | 5   | -                | -                | ns   |

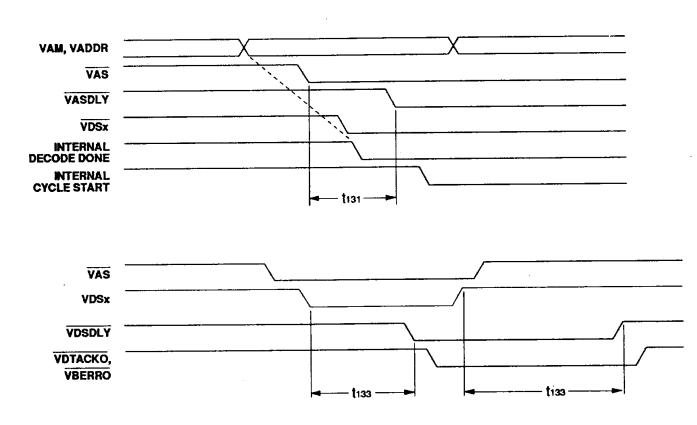

| t <sub>131</sub>  | VAS low to VASDLY low                                               | -            | 15  | 25               | 25               | ns   |

| t <sub>132</sub>  | VDATA, VWR setup to VDSa low                                        | -            | 5   | -                | •                | ns   |

| t <sub>133</sub>  | VDSn edge to VDSDLY edge                                            | -            | 35  | 45               | 45               | ns   |

| t <sub>134</sub>  | SR, RXFIFO write without holdoff (Note 1 & 4)                       | -            | 45  | 65               | 70               | ns   |

| t <sub>135</sub>  | SR, LM write without holdoff (Note 1 & 4)                           | 3/4          | 50  | 75               | 80               | ns   |

| t <sub>136</sub>  | SR, LM write with CPU holdoff (Note 1 & 4)                          | 6/7          | 50  | 75               | 80               | ns   |

| t <sub>137</sub>  | SR, Atomic (minimum) (Note 5)                                       | 11.5/12.5    | 4   | 35               | 40               | ns   |

| t <sub>138</sub>  | VDSa low to LMINT asserted (Note 1 & 4)                             | 1.5/2.5      | 50  | 85               | 90               | ns   |

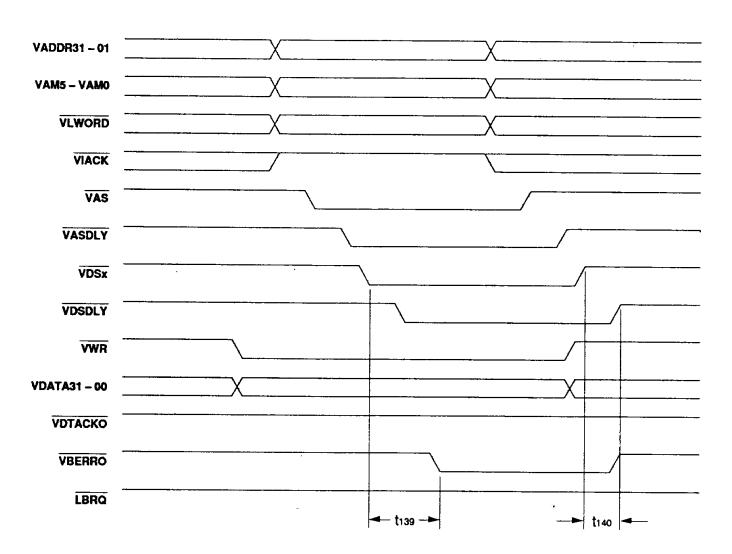

| t <sub>139</sub>  | VDSa low to VBERRO asserted,<br>illegal VMEin cycle (Note 2, 4 & 6) | -            | 45  | 65               | 70               | ns   |

| t <sub>140</sub>  | VDSb high to VDTACKO negated,<br>VMEbus write cycle to DARF         | -            | 5   | 30               | 35               | ns   |

| t <sub>140A</sub> | VDSb high to VDTACKO negated,<br>VMEbus read cycle to DARF (Note 4) | -            | 45  | 70               | 75               | ns   |

| t <sub>141</sub>  | VDATAOUT negated to VDTACKO negated                                 | -            | -1  | 0                | 1                | ns   |

| t <sub>142</sub>  | VADDR, VAM, VLWORD, VIACK<br>hold time from VDTACKO low             | -            | 0   | •                | -                | ns   |

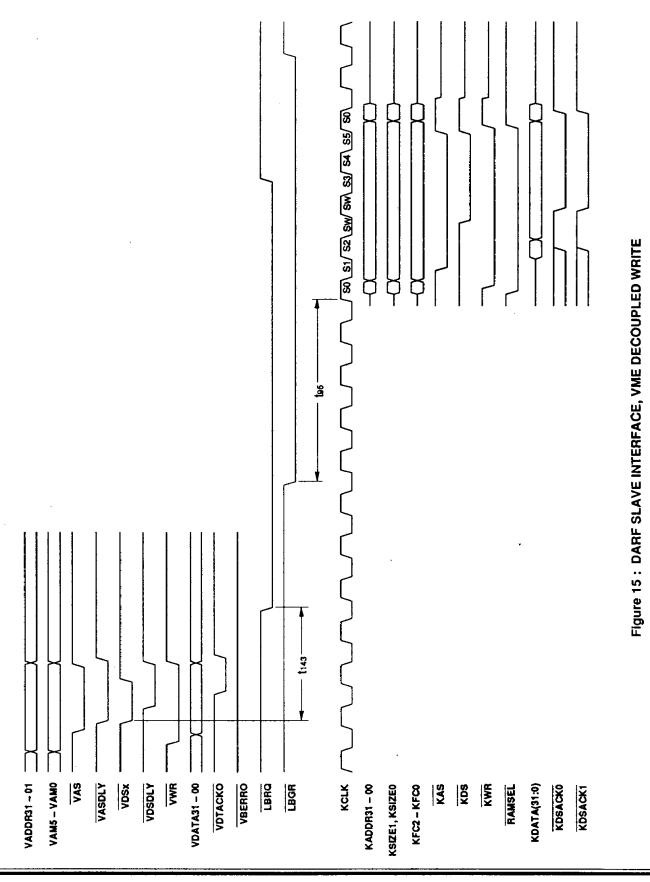

| t <sub>143</sub>  | VDSn low to LBRQ asserted,<br>Atomic VMEin cycle                    | 2/3          | 3   | 20               | 25               | ns   |

| t <sub>144</sub>  | VECTEN low to VDATA asserted (Note 3)                               | 0.5/1.5      | 5   | 35               | 40               | ns   |

| t <sub>145</sub>  | VECTEN low to VDTACKO asserted (Note 3)                             | 2/3          | 3   | 20               | 25               | ns   |

| t <sub>146</sub>  | VDSDLY low to VDTACKO asserted,<br>Decoupled VMEin cycle (Note 1)   | -            | 4   | 25               | 30               | ns   |

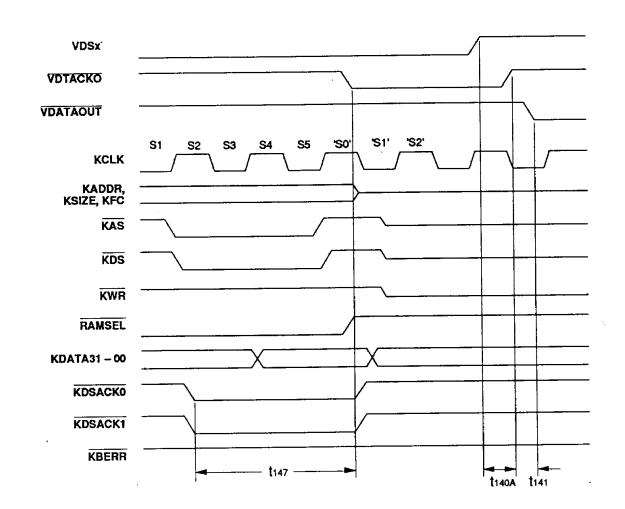

| t <sub>147</sub>  | KDSACKn low to VDTACKO asserted<br>BERRCHK = 0 (Note 3)             | 1.5/2.5      | 5   | 35               | 40               | ns   |

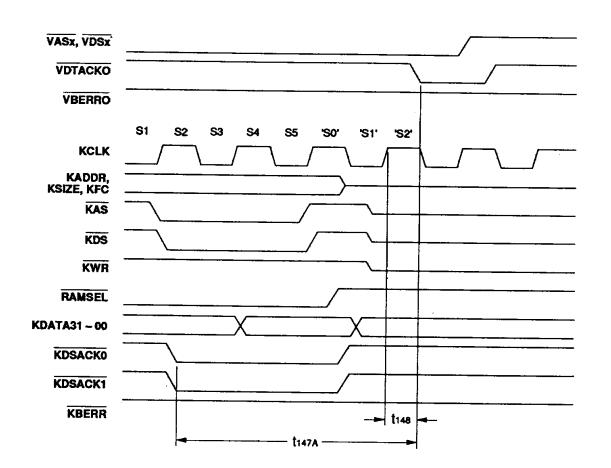

| t <sub>147A</sub> | KDSACKn low to VDTACKO asserted<br>BERRCHK = 1 (Note 3)             | 2.5/3.5      | 5   | 35               | 40               | ns   |

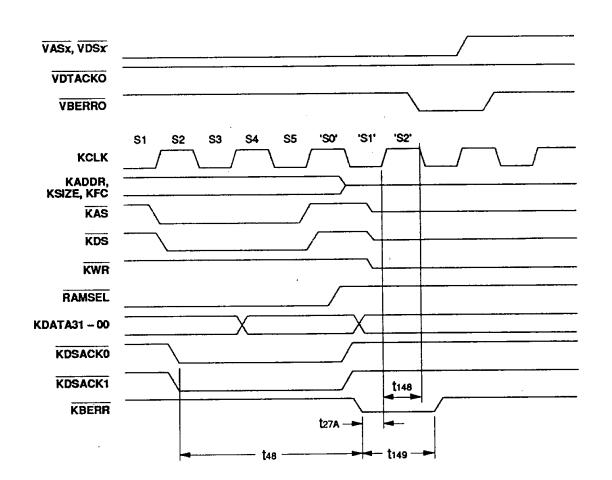

| t <sub>148</sub>  | KCLK high to VBERRO or VDTACKO<br>asserted, Atomic VMEin cycle      | -            | 5   | 35               | 40               | ns   |

| t <sub>149</sub>  | Pulse width, late KBERR width (Note 7)                              |              | 10  | <sup>t</sup> ськ | t <sub>clk</sub> | ns   |

Notes: see next page

Notes:

- 1. This parameter assumes that there is space in the Message/Receive FIFO to receive the data.

- 2. This parameter applies only to accesses to protected memory and Message FIFO read cycles.

- 3. This timing parameter is the sum of the number listed and product of the CLK COUNT times the period of the CPU clock.

eg:  $t_{21} = -5 + (0.5 \times t_{KCLK})$  ns

- 4. This parameter assumes that a 40ns delay line is used to generate ADLY, BDLY, VDSDLY, and VDTKDLY.

- 5. This slave response parameter assumes that the LBGR is returned in time to be sampled on the next falling edge of KCLK after LBRa is asserted. Additional clocks will have to be added to account for bus arbitration time.

- 6. This parameter applies when an illegal access to the DARF is attempted by the VMEbus, i.e, read access to the location monitor or illegal access to protected memory.

- 7. When KBERR is received late, it is latched internally for the DARF's use. KBERR needs to be negated before the next local bus cycle starts.

.

-6

#### Note:

,

The Slave Response time for Location Monitor writes is extended an additional 3 clocks if the CPU is writing to the FIFO when the VMEin cycle occurs.

,

# Figure 18a : DARF SLAVE INTERFACE, MEMORY READ with BERRCHK CLEARED

# Figure 18b : DARF SLAVE INTERFACE, MEMORY READ with BERRCHK SET

# Figure 18b : DARF SLAVE INTERFACE, MEMORY READ with LATE KBERR

# Figure 20 : DARF VME SLAVE INTERFACE, ILLEGAL ACCESS

Note:

This timing applies to VMEbus attempts to read the Location Monitor or to illegally access protected memory.

# Figure 21 : DARF DELAY LINE TIMING, VMEbus SLAVE CYCLES

Note:

On VMEbus write cycles to the DARF, VDTACK0 is negated with VDSB instead of VDSDLY.

÷

.

# Table 9 : DC CHARACTERISTICS

(Commercial  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$ )

| Symbol          | Parameter                        | Test                              |      | Unit    |      |            |

|-----------------|----------------------------------|-----------------------------------|------|---------|------|------------|

|                 |                                  | Conditions                        | Min  | Min Typ |      |            |

| I <sub>H</sub>  | Input HIGH Current               | V <sub>IN</sub> = V <sub>DD</sub> |      |         |      |            |

|                 | CTTL                             |                                   |      | 1       | 10   | μA         |

|                 | CTTL PU                          |                                   | •    | -       | 40   | μΑ         |

| I               | Input LOW Current                | V <sub>IN</sub> =V <sub>SS</sub>  |      |         |      |            |

|                 | CTTL                             |                                   |      | -1      | -10  | μ <b>A</b> |

|                 | CTTL PU                          |                                   | -8   | -30     | -100 | μA         |

| l <sub>oz</sub> | Tri-state Output Leakage Current |                                   | -10  | ±1      | 10   | μA         |

| V <sub>IL</sub> | Input LOW Voitage                |                                   |      |         |      |            |

|                 | CTTL                             |                                   | -    |         | 0.8  | v          |

|                 | CTTL PU                          |                                   | · -  | -       | 0.8  | v          |

| V <sub>IH</sub> | Input HIGH voltage               |                                   |      |         |      |            |

|                 | CTTL                             | 0° to 70°C                        | 2.0  | -       | -    | v          |

|                 | CTTL PU                          | 0° to 70°C                        | 2.0  | -       | -    | v          |

|                 | CTTL                             | -55° to +125°C                    | 2.25 |         | -    | v          |

|                 | CTTL PU                          | -55° to +125°C                    | 2.25 | •       | -    | v          |

| V <sub>OH</sub> | Voltage Output HIGH              | 0° to 70°C                        |      |         |      |            |

|                 | TP2                              | I <sub>он</sub> = –2 mA           | 2.4  | 4.5     | -    | v          |

|                 | TP4                              | I <sub>OH</sub> ≖ –4 mA           | 2.4  | 4.5     | -    | v          |

|                 | TS4                              | I <sub>он</sub> = -4 mA           | 2.4  | 4.5     | -    | v          |

|                 | TS4 SR                           | I <sub>OH</sub> =4 mA             | 2.4  | 4.5     | -    | v          |

|                 | TS6                              | I <sub>OH</sub> = -6 mA           | 2.4  | 4.5     | -    | v          |

|                 | TS8                              | l <sub>он</sub> = -8 mA           | 2.4  | 4.5     | -    | v          |

| V <sub>OH</sub> | Voltage Output HIGH              | -55° to 125°C                     |      |         |      |            |

|                 | TP2                              | l <sub>OH</sub> = -1.6 mA         | 2.4  | 4.5     | -    | ν          |

|                 | TP4                              | l <sub>OH</sub> =3.2 mA           | 2.4  | 4.5     | -    | v          |

|                 | TS4                              | l <sub>OH</sub> = -3.2 mA         | 2.4  | 4.5     | -    | ٧          |

| ĺ               | TS4 SR                           | i <sub>OH</sub> = -3.2 mA         | 2.4  | 4.5     | -    | ٧          |

|                 | TS6                              | I <sub>OH</sub> = -4.8 mA         | 2.4  | 4.5     | -    | V          |

| ĺ               | TS8                              | $l_{OH} = -6.4 \text{ mA}$        | 2.4  | 4.5     | -    | v          |

# Table 9: DC CHARACTERISTICS CONT

(Commercial T<sub>A</sub> = 0° to +70°C, V<sub>DD</sub> = 5V ± 5%, Military T<sub>A</sub> = -55° to +125°C, V<sub>DD</sub> = 5V ± 10%)

| Symbol | Parameter          | Test                     |     | Limits |     | Unit |

|--------|--------------------|--------------------------|-----|--------|-----|------|

|        |                    | Conditions               | Min | Тур    | Max |      |

| VOL    | Voltage Output LOW | 0° to 70°C               |     |        |     |      |

|        | TP2                | I <sub>OL</sub> = 2 mA   | -   | 0.2    | 0.4 | v    |

|        | TP4                | I <sub>OL</sub> = 4 mA   | -   | 0.2    | 0.4 | v    |

|        | TS4                | I <sub>OH</sub> = 4 mA   | · - | 0.2    | 0.4 | v    |

|        | TS4 SR             | l <sub>OH</sub> = 4 mA   | -   | 0.2    | 0.4 | v    |

|        | TS6                | I <sub>OL</sub> = 6 mA   | -   | 0.2    | 0.4 | v    |

|        | TS8                | I <sub>OL</sub> = 8 mA   | -   | 0.2    | 0.4 | V    |

|        | OD8                | l <sub>oL</sub> = 8 mA   | -   | 0.2    | 0.4 | v    |

|        | OD12               | I <sub>OL</sub> = 12 mA  | -   | 0.2    | 0.4 | v    |

| VoL    | Voltage Output LOW | -55° to 125°C            |     |        |     |      |

|        | TP2                | l <sub>OL</sub> = 1.6 mA | -   | 0.2    | 0.4 | v    |

|        | TP4                | l <sub>OL</sub> = 3.2 mA | •   | 0.2    | 0.4 | V    |

| -      | TS4                | l <sub>OH</sub> = 3.2 mA | -   | 0.2    | 0.4 | v    |

|        | TS4 SR             | l <sub>OH</sub> = 3.2 mA | •   | 0.2    | 0.4 | V    |

|        | TS6                | l <sub>OL</sub> = 4.8 mA | -   | 0.2    | 0.4 | v    |

|        | TS8                | I <sub>OL</sub> = 6.4 mA | •   | 0.2    | 0.4 | v    |

|        | OD8                | I <sub>OL</sub> = 6.4 mA | -   | 0.2    | 0.4 | V    |

|        | OD8                | I <sub>OL</sub> = 6.4 mA | -   | 0.2    | 0.4 | V    |

|        | OD12               | I <sub>OL</sub> = 9.6 mA | •   | 0.2    | 0.4 | v    |

Note that the type abbreviations used above have a number suffix which indicates the current rating. The letter prefixes are defined in the Terminology section, just before Table 3.

# Table 10 : CAPACITIVE LOADING

| Symbol          | Parameter                                                    | Test       |     | Unit |     |    |

|-----------------|--------------------------------------------------------------|------------|-----|------|-----|----|

|                 |                                                              | Conditions | Min | Тур  | Max |    |

| C <sub>∥N</sub> | Input Pin Capacitance                                        |            |     | 10   | •   | рF |

| с <sub>ю</sub>  | Bidirectional Pin Capacitance<br>TS4, TS4 SR, TS6, TS8, OD12 |            | -   | 14   | -   | ρF |

| Cour            | Output Pin Capacitance<br>TP2, TP4, OD8                      |            | -   | 13   | -   | pF |

Note that the maximum capacitive loads under recommended operating conditions for outputs driving the local bus, that is, all signals beginning with K, is 1300pF. The maximum capacitive load for all outputs is 85pF.

# Table 16 : RECOMMENDED OPERATING CONDITIONS

| DC Supply Voltage (V <sub>DD</sub> )                      | +4.5 V to +5.5 V |  |  |

|-----------------------------------------------------------|------------------|--|--|

| Power Dissipation (P <sub>DD</sub> )                      | 1 W              |  |  |

| Ambient Operating Temperature (T <sub>A</sub> Commercial) | 0° to +70°C      |  |  |

| Ambient Operating Temperature (T <sub>A</sub> Military)   | -55° to +125°C   |  |  |

The power dissipation figure is based on typical internal logic dissipation plus the worst case set of outputs simultaneously active with maximum rated loads.

# Table 17 : ABSOLUTE MAXIMUM RATINGS

| DC Supply Voltage (V <sub>DD</sub> )             | –0.3 to +7.0 V                |

|--------------------------------------------------|-------------------------------|

| Input Voltage (V <sub>IN</sub> )                 | 0.3 to V <sub>D0</sub> +0.3 V |

| DC Input Current (I <sub>IN</sub> )              | -10 to +10 mA                 |

| Storage Temperature, ceramic (T <sub>STG</sub> ) | -65° to +150°C                |

| Storage Temperature, plastic (T <sub>STG</sub> ) | -40° to +125°C                |

Stresses beyond those listed above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## **FUNCTIONAL DESCRIPTION**

The DARF provides an address and data path to link a CPU to a VMEbus, including the logic required to perform data transfers as a master or a slave on local or VMEbus. Transmit and receive paths of the DARF each run in one of two operating modes: atomic or decoupled. In atomic mode, a cycle initiated on one port of the DARF does not finish until the DARF has initiated and completed that cycle on its other port. The decoupled mode allows cycles on one port to be completed and queued within the DARF for later dispatch to the other port. The decoupled mode has inherently higher transfer rates than the atomic mode.

#### **Memory Map**

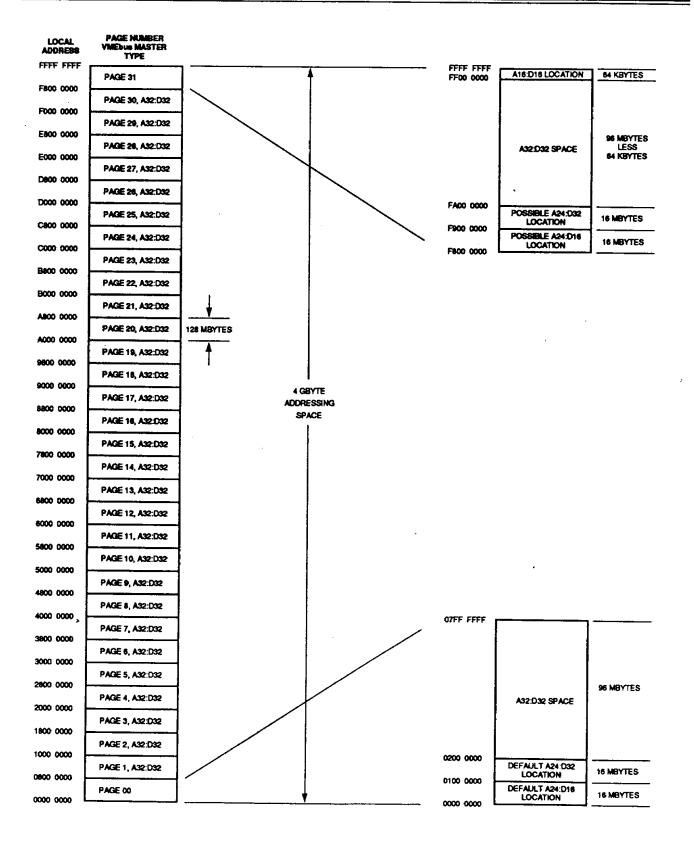

The DARF is a two port device with 32-bit addressing and 32-bit data on each port. The 4 Gbyte memory maps are different for each port. A cycle that is generated to select the VMEbus port of the DARF from a VMEbus master is generated on the local bus as a 68020-like bus cycle, with the data shifted to the byte lanes appropriate for the data size indicated in the VMEbus transfer.

A cycle generated by the local CPU for the VMEbus is signalled to the DARF by having the local logic assert the VMEOUT (device wants bus) input. This cycle is interpreted according to the memory map of Figure 22 to generate the appropriate cycle on the DARF VMEbus port.

The DARF treats the 4 Gbyte space viewed from the local port as 32 – 128 Mbyte pages numbered 0 through 31, starting from address 0. Accesses to VMEbus A24:D16 space are through the lowest 16 Mbytes of page 0 (default) or page 31 as determined by register selection. The same is true of A24:D32 transfers through the second 16 Mbytes of page 0 (default) or page 31. A24 can also be disabled entirely, causing these locations to generate A32:D32 VMEbus cycles in those address ranges.

The upper 64 Kbytes of page 31 causes A16:D16 cycles to be generated, if A16 mode is enabled (default). Otherwise, this area causes A32:D32 cycles.

The BUSSEL register within the DARF allows each of the 32 pages to be individually forced to generate a  $\overrightarrow{VSBSEL}$  signal instead of a VMEbus access. This is useful whenever a major peripheral bus, like a VME Subsystem Bus (VSB), is present. The default setting is for all pages to generate VMEbus accesses.

Aside from the areas mentioned above, accesses with VMEOUT asserted generate A32:D32 VMEbus cycles.

#### **Bus Master Operation**

Bus master operation implies that the DARF is generating a cycle on its VMEbus port. If the logic within the DARF indicates that the cycle should not be generated on the VMEbus (BUSSEL register), the DARF asserts the VSBSEL signal until the local cycle is terminated. The DARF does not decouple these cycles, and they proceed regardless of the DARF BI-mode<sup>™</sup> status.

#### VMEbus Requesting

Accesses to the VMEbus may be requested by the DARF for any of the following:

- A local read cycle to the VMEbus

- An atomic mode write cycle from the local bus to the VMEbus

- VIACKRQ signal is requesting a VMEbus interrupt acknowledge cycle

- · Cycles are queued in the transmit FIFO

- A local cycle with KRMC asserted accesses the VMEbus

## Deadlocks

If, while requesting the VMEbus for the first three cases above, an incoming atomic cycle is received from the VMEbus, then the DARF asserts KBERR and KHALT to instruct the local device to relinquish the local bus then retry its cycle. The incoming VMEbus cycle then finishes normally, before the CPU is allowed to retry it's cycle. If an incoming atomic cycle occurs during the last case above, the DARF issues only KBERR locally. This is required to terminate local KRMC cycles which will not otherwise relinquish the local bus.

#### **Transactions Performed**

When generating VMEbus cycles in A24 or A16 mode, the DARF sets all unused address lines to logic 1. The address modifier codes generated by the DARF during VMEbus cycles indicate the addressing mode (A32, A24 or A16) and the access type (user/supervisor program/ data). Interrupt acknowledge cycles generated by the DARF use AM code 2E if A16 mode is enabled, or code 0E otherwise.

The DARF uses the KDSACK0 and KDSACK1 signals to indicate to the CPU the size of data being transfered in

4 – 98

any given transaction. Accesses to D32 space result in both  $\overline{\text{KDSACK0}}$  and  $\overline{\text{KDSACK1}}$  being asserted if the access is aligned (A01 = A00 = 0). All other VMEbus cycles requested by the CPU result in the assertion of  $\overline{\text{KDSACK1}}$ only. The DARF supports unaligned transfers as generated by Motorola 68020/030 microprocessors.

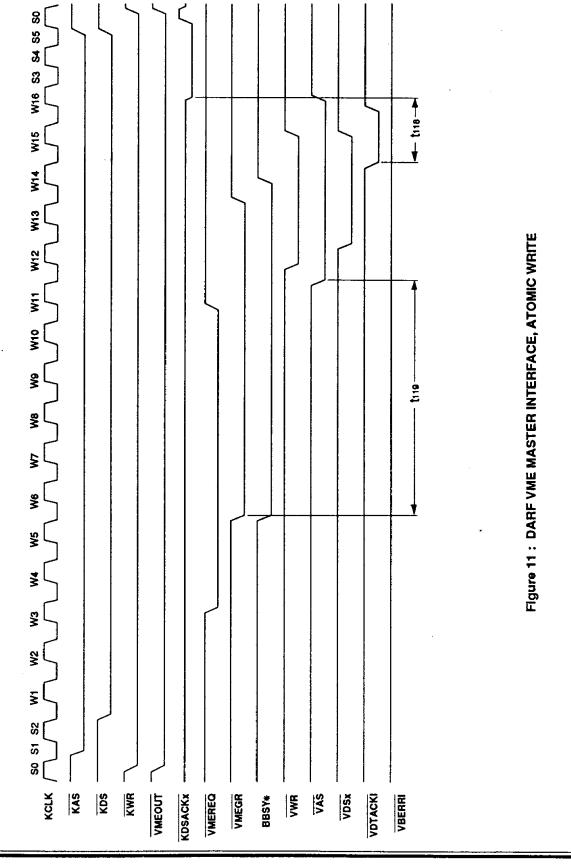

#### **Locked Transactions**

Two classes of locked transactions concern the DARF; single address locked transactions and multi-address locked transactions. These classes correspond to the 68020 TAS and CAS2 instructions respectively.

During cycles where KRMC is asserted (locked cycles) on the local bus, the DARF retains control of the VMEbus, until all cycles making up the locked transaction are complete. Note that this is insufficient to guarantee the indivisibility of a locked transaction, since it may not prevent access by other devices to the memory on the slave module during the locked transaction (though it does if the slave is another DARF).

For single address locked transactions, the VMEbus specification allows AS\* to remain asserted for all cycles of the transaction. To enable this feature, the TASCON control bit must be set within the DARF. *Caution:* the use of the TASCON mode with multi-address locked transactions may cause the failure of those transactions.

During all types of locked transactions, the DARF asserts its VRMC output. This output may be routed to the VMEbus P2 Reserved pin for transmission to a similarly equipped slave. It is recommended that this connection be made through a jumper block in case a different use is envisaged for this VMEbus pin. If the slave module(s) participating in the locked transaction are capable of responding to the VRMC/ signal (eg: DARF equipped module), all locked transactions can be made indivisible.

During a locked transaction to the VMEbus, an incoming transaction causes the attempted locked transaction to be terminated, with a bus error, when bus control has not been acquired.

#### Atomic Mode

In atomic mode accesses, the CPU transfer is *not* queued by the transmit FIFO; the CPU becomes directly linked to the VMEbus once ownership is established. The CPU enters wait states until a DTACK\* or BERR\* is generated by the VMEbus slave and passed back through the DARF. Only then can the CPU terminate the local cycle and proceed to the next.

If a BERR\* is received during a VMEbus transaction, the VBERR flag will be set in the DARF and the VMEINT output asserted. The DARF does not initiate any further cycles on the VMEbus until the VBERR flag is cleared. The VMEINT output remains asserted as long as the VBERR flag is asserted.

Read, locked and interrupt acknowledge cycles are always atomic. Write cycles are atomic if the transmit FIFO is in atomic mode. Atomic cycles are blocked, if cycles are queued in the transmit FIFO, until the FIFO has cleared. This is required to ensure data integrity.

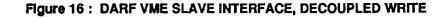

#### **Decoupled Mode**

When the CPU writes to the VMEbus with the transmit FIFO in decoupled mode, the local cycle finishes in one wait state. The transmit FIFO is 7 stages deep and contains all queued decoupled writes and DMA writes. When the FIFO becomes non-empty, it causes a request for the VMEbus.