# **Features**

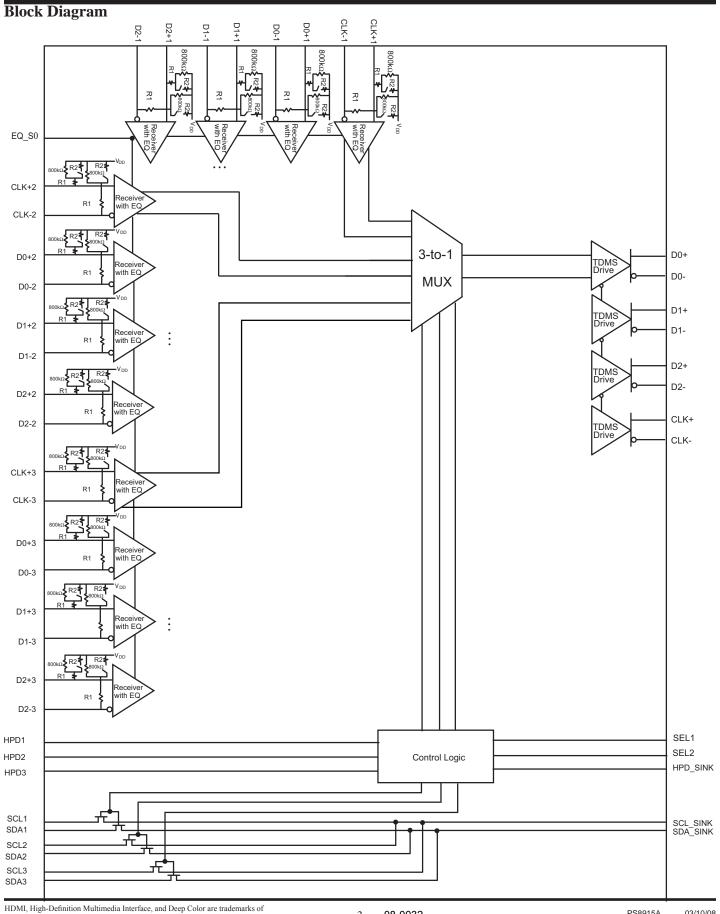

- 3 digital video inputs can be switched to a single output

- Each input can be AC coupled video or DC coupled, while the output will maintain its DC coupled, current-steering, TMDS compliance

- TMDS pixel clock support up to 250MHz max

- Deep Color<sup>TM</sup> support up to 36bits max per link

- Integrated DDC switch to connect DDC path from HDMI™ input connectors to HDCP block in the HDMI<sup>TM</sup> Receiver.

- Can support Clock Stretching on DDC path

- HDCP reset circuitry for quick communication when switching from one port to another

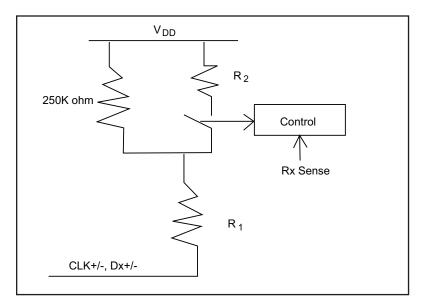

- Automatic Termination turn-off circuitry when port is deselected

- Clock Detection: Will disable output TMDS channels when no TMDS pixel clock is present

- Flexible termination;

- when TMDS channel is off, 50ohm termination is changed to 800Kohm

- Integrated ESD on all data input channels

- 8kV contact per IEC61000-4-2

- Optimized Equalization with support for up to 20 meter input cable lengths

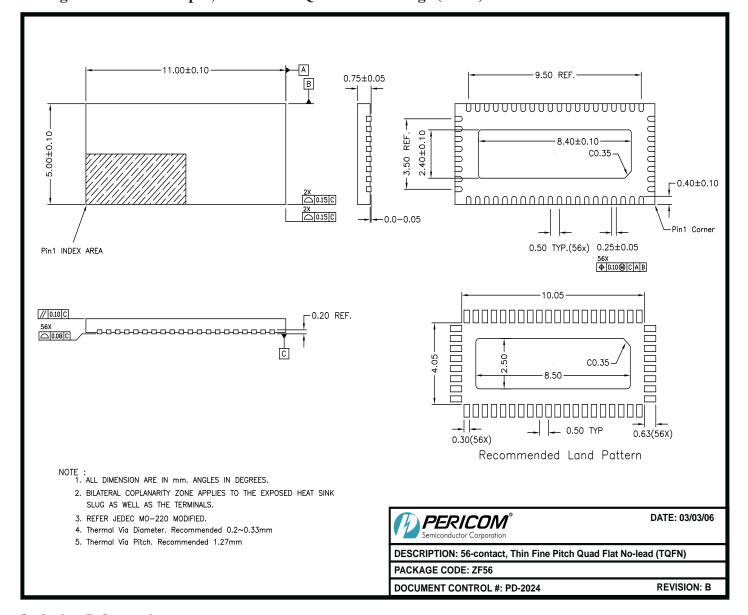

- Packaging (Pb-free and Green)

- 56 contact TQFN (ZFE)

# 3:1 Active EYE HDMI<sup>TM</sup> switch with Electrical Idle Detect

## **Description**

08-0032

Fully compatible HDMI<sup>™</sup> signal support with backward compatibility to the DVI 1.0 standard, Pericom's new "Active EYE" switch technology is all you need to connect multiple, unknown sources, to a single display. Without any affect on HDCP, these switches can be used almost anywhere. In addition to supporting DC coupled HDMI<sup>™</sup> and DVI inputs, Pericom's PI3HDMI231-A can also level shift an AC coupled HDMI<sup>™</sup> or Dual Mode DP signal to a DC coupled HDMI™ output.

Pericom's HDMI™ product family has been designed specifically to support color depths of up to 12bits per channel, as specified in the HDMI<sup>™</sup> revision 1.3 standard. We have integrated the entire interface solution so the TV designer doesn't have to think about it. This includes, integrated DDC switching.

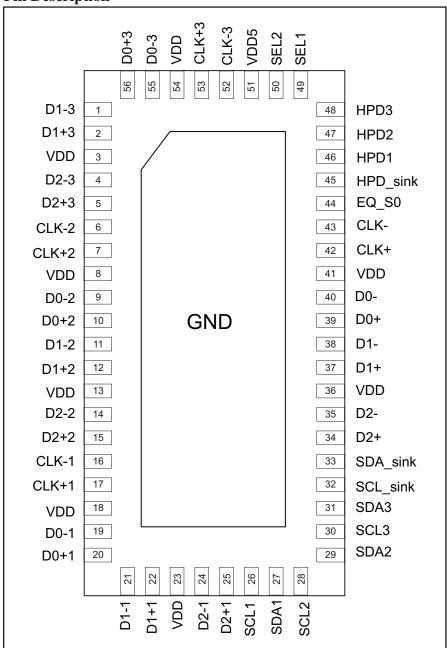

## **Pin Description**

PS8915A

#### Receiver Block

The HDMI™/DVI receive ports are terminated separately as follows:

### **Truth Table**

| EQ_S0 <sup>(1)</sup> | EQ value on TMDS data channels |

|----------------------|--------------------------------|

| 0                    | 6dB @ 825MHz                   |

| 1                    | 12dB @ 825MHz                  |

Notes:

Each input has integrated equalization that can eliminate deterministic jitter caused by 20meter 24AWG cables. The Rx block is designed to receive all relevant signals directly from the HDMI™ connector without any additional circuitry, 3 High speed TMDS data, 1 pixel clock, and DDC signals (R1 + R2 = 50 ohm).

### **Transmitter Block**

The transmitter block transmits the HDMI™/DVI data according to HDMI™ revision 1.3 transmitter spec.

## **Source Selection Look-up Table**

| Contro | l Bits | I/O S                                                                      | elected                                                 | Hot      | Plug Detect St | atus     |

|--------|--------|----------------------------------------------------------------------------|---------------------------------------------------------|----------|----------------|----------|

| SEL2   | SEL1   | TMDS output                                                                | SCL_SINK/SDA_SINK                                       | HPD1     | HPD2           | HPD3     |

| Н      | Н      | TMDS Port 1 is active and port 2 and 3 have 50ohm termination disconnected | SCL1/SDA1                                               | HPD_SINK | L              | L        |

| Н      | L      | TMDS Port 2 is active and port 1 and 3 have 50ohm termination disconnected | SCL2/SDA2                                               | L        | HPD_SINK       | L        |

| L      | L      | TMDS Port 3 is active and port 1 and 2 have 50ohm termination disconnected | SCL3/SDA3                                               | L        | L              | HPD_SINK |

| L      | Н      | NONE(Z)<br>All terminations are disconnected                               | NONE(Z) Are pulled HIGH by external pull-up termination | HPD_SINK | HPD_SINK       | HPD_SINK |

08-0032

<sup>1)</sup> Internal 100K-ohm pull down resistor

## **Electrical Specifications**

## **Absolute Maximum Conditions**

| Symbol              | Parameter                                         | Min  | Тур | Max     | Units | Note |

|---------------------|---------------------------------------------------|------|-----|---------|-------|------|

| $V_{\mathrm{DD}}$   | TMDS Supply Voltage                               | -0.3 |     | 4.0     | V     | 1, 2 |

| $V_{\rm I}$         | Input Voltage                                     | -0.3 |     | VDD+0.3 | V     | 1, 2 |

| $V_{O}$             | Output Voltage                                    | -0.3 |     | VDD+0.3 | V     | 1, 2 |

| $V_{\mathrm{DD}}$ 5 | +5V power supply used during power down situation | -0.3 |     | 6.0     | V     |      |

### **Notes:**

- 1. Permanent device damage can occur if absolute maximum conditions are exceeded.

- 2. Functional operation should be restricted to the conditions described under Normal Operating Conditions.

## **Electrical Specifications**

## **Normal Operating Conditions**

| Symbol            | Parameter                                                     | Min   | Тур | Max   | Units |

|-------------------|---------------------------------------------------------------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$ | TMDS Analog Supply Voltage                                    | 3.135 | 3.3 | 3.465 | V     |

| V <sub>DD</sub> 5 | +5V power supply used during power down (from HDMI connector) | 4.5   |     | 5.5   | V     |

| T <sub>A</sub>    | Ambient Temperature (with power applied)                      | 0     | 25  | 70    | °C    |

PS8915A

# **Electrical Characteristics Over Recommended Operating Conditions** (unless otherwise noted)

| Symbol          | Description   | Test Co              | nditions                                        | Min | Тур | Max | Units |

|-----------------|---------------|----------------------|-------------------------------------------------|-----|-----|-----|-------|

| I <sub>CC</sub> | Supply        | SEL1/SEL2 = LOW/LOW  | $V_{IH} = V_{DD},$                              |     |     | 120 | mA    |

|                 | current       | LOW/HIGH             | $V_{\rm IL} = V_{\rm DD}$ -0.6V                 |     |     |     |       |

|                 |               | HIGH/HIGH            | RT= $50\Omega$ , $V_{DD}=3.3V$                  |     |     |     |       |

|                 |               | SEL1/SEL2 = HIGH/LOW | TMDS data inputs = 2.5Gbps<br>HDMI data pattern |     |     | 35  |       |

| $I_{DD}$        | 5V power supp | oly current          | TMDS clock input = 250MHz                       |     |     | 5   | mA    |

## **Electrical Characteristics Over Recommended Operating Conditions** (unless otherwise noted)

| Symbol               | Parameter                                                                                                    | Test Conditions                               | Min.                 | <b>Typ.</b> <sup>(1)</sup> | Max.                     | Units      |

|----------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------|----------------------------|--------------------------|------------|

| TMDS Differ          | rential pins                                                                                                 |                                               |                      |                            |                          |            |

| V <sub>OH</sub>      | Single-ended high level output voltage                                                                       |                                               | V <sub>DD</sub> -10  |                            | V <sub>DD</sub> +10      | mV         |

| $V_{OL}$             | Single-ended low level output voltage                                                                        |                                               | V <sub>DD</sub> -600 |                            | V <sub>DD</sub> -<br>400 | mV         |

| V <sub>swing</sub>   | Single-ended output swing voltage                                                                            | $V_{DD} = 3.3 \text{V}, \text{RT} = 50\Omega$ | 400                  |                            | 600                      | mV         |

| V <sub>OD(O)</sub>   | Overshoot of output differential voltage                                                                     |                                               |                      |                            | 15%                      | 2 x Vswing |

| V <sub>OD(U)</sub>   | Undershoot of output differential voltage                                                                    |                                               |                      |                            | 25%                      | 2 x Vswing |

| $\Delta V_{OC(SS)}$  | Change in steady-state common-mode output voltage between logic states                                       |                                               |                      |                            | 5                        | mV         |

| $I_{OS}$             | Short Circuit output current                                                                                 |                                               | -12                  |                            | 12                       | mA         |

| V <sub>I(open)</sub> | Single-ended input voltage under high impedance input or open input                                          | $I_{\rm I} = 10 { m uA}$                      | V <sub>DD</sub> -10  |                            | V <sub>DD</sub> +10      | mV         |

| R <sub>INT</sub>     | Input termination resistance                                                                                 | $V_{\rm IN} = 2.9 V$                          | 45                   | 50                         | 55                       | Ω          |

| CLK_Detect           | TMDS clock detection for                                                                                     | Frequency                                     | 15                   |                            | 340                      | MHz        |

| l                    | normal operation. Outputs are<br>Hi-Z if CLK signal detected is<br>outside of this Normal<br>operating range | Differential Voltage Swing                    | 140                  |                            |                          | mV         |

| I <sub>OZ</sub>      | Leakage current with Hi-Z I/O                                                                                | $V_{DD} = 3.6V, V_{DD}5 = 5.5V$               |                      |                            | 5                        | uA         |

| I <sub>OFF</sub>     | Leakage current when V <sub>DD</sub> is not present                                                          | $V_{DD} = 0V$ or open, $V_{DD}5$<br>= 5.5V    |                      |                            | 10                       | uA         |

(Continued)

## Switching Characteristics (over recommended operating conditions unless otherwise noted)

| TMDS D               | oifferential Pins                                |                                           |      |                            |      |       |

|----------------------|--------------------------------------------------|-------------------------------------------|------|----------------------------|------|-------|

| Symbol               | Parameter                                        | Test Conditions                           | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |

| tpd                  | Propagation delay                                |                                           |      |                            | 2000 |       |

| t <sub>r</sub>       | Differential output signal rise time (20% - 80%) |                                           |      | 140                        |      |       |

| $t_{\mathrm{f}}$     | Differential output signal fall time (20% - 80%) | $V_{DD} = 3.3V, R_T = 50$ -ohm            |      | 140                        |      |       |

| t <sub>sk(p)</sub>   | Pulse skew                                       |                                           |      | 10                         | 50   |       |

| t <sub>sk(D)</sub>   | Intra-pair differential skew                     |                                           |      | 23                         | 50   | ps    |

| t <sub>sk(o)</sub>   | Inter-pair differential skew                     |                                           |      |                            | 100  |       |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter CLK residual jitter   | Data Input = 1.65 Gbps HDMI <sup>TM</sup> |      | 15                         | 30   |       |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter DATA residual jitter  | data pattern CLK Input = 165 MHz clock    |      | 18                         | 50   |       |

| $t_{SX}$             | Select to switch output                          |                                           |      |                            | 10   |       |

| t <sub>en</sub>      | Enable time                                      |                                           |      |                            | 600  | ns    |

| t <sub>dis</sub>     | Disable time                                     |                                           |      |                            | 10   |       |

| DDC I/O I            | DDC I/O Pins (SCL, SCL_SINK, SDA, SDA_SINK)                                     |                 |      |                            |      |       |  |  |

|----------------------|---------------------------------------------------------------------------------|-----------------|------|----------------------------|------|-------|--|--|

| Symbol               | Parameter                                                                       | Test Conditions | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |  |  |

| t <sub>pd(DDC)</sub> | Propagation delay from SCLn to SCL_SINK or SDAn to SDA_SINK or SDA_SINK to SDAn | $C_L = 10 pF$   |      | 0.4                        | 2.5  | ns    |  |  |

| Control a            | Control and Status Pins (OC_SX, EQ_SX, S, HPD_SINK, HPD)         |                 |      |                            |      |       |  |  |

|----------------------|------------------------------------------------------------------|-----------------|------|----------------------------|------|-------|--|--|

| Symbol               | Parameter                                                        | Test Conditions | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |  |  |

| t <sub>pd(HPD)</sub> | Propagation delay (from HPD_SINK to the active port of HPD)      |                 |      | 2                          | 6.0  |       |  |  |

| t <sub>sx(HPD)</sub> | Switch time (from port select to the latest valid status of HPD) | $C_L = 10 pF$   |      | 3                          | 6.5  | ns    |  |  |

| Control Pi        | Control Pins                        |                                  |      |                            |                |       |  |  |

|-------------------|-------------------------------------|----------------------------------|------|----------------------------|----------------|-------|--|--|

| Symbol            | Parameter                           | Test Conditions                  | Min. | <b>Typ.</b> <sup>(1)</sup> | Max.           | Units |  |  |

| $I_{IH}$          | High level digital input current(1) | $V_{IH} = 2V \text{ or } V_{DD}$ | -10  |                            | 10             | μΑ    |  |  |

| $I_{IL}$          | Low level digital input current(1)  | $V_{IL}$ = GND or 0.8V           | -10  |                            | 10             | μΑ    |  |  |

| $V_{\mathrm{IH}}$ | High Level Digital input Voltage    |                                  | 2.0  |                            | $V_{\rm DD}$ 5 | V     |  |  |

| $V_{\rm IL}$      | low level digital input voltage     |                                  | 0    |                            | 0.8            | V     |  |  |

(Continued)

| DDC I/O Pins    |                          |                                                       |     |    |    |    |

|-----------------|--------------------------|-------------------------------------------------------|-----|----|----|----|

| $I_{LK}$        | Input leakage current    | $V_I = 0.1 V_{DD}$ to $V_{DD}$ to isolated DDC inputs | -10 |    | 10 | μΑ |

| C <sub>IO</sub> | Input/Output capacitance | V <sub>I</sub> peak-peak = 1V, 100 KHz                |     |    | 10 | pF |

| R <sub>ON</sub> | Switch resistance        | $I_{O} = 3mA, V_{O} = 0.4V$                           |     | 25 | 50 | Ω  |

| <b>HPD Path</b> | HPD Path                               |                           |     |  |                   |    |  |

|-----------------|----------------------------------------|---------------------------|-----|--|-------------------|----|--|

| $I_{IH}$        | High level digital input current       | $V_{IH} = 2V$ or $V_{DD}$ | -10 |  | 10                | μΑ |  |

| $I_{IL}$        | Low level digital input current        | $V_{IL}$ = GND or 0.8V    | -10 |  | 10                | μΑ |  |

| V <sub>OH</sub> | Single-ended high level output voltage | $I_{OH} = -100 \mu A$     | 2.4 |  | $V_{\mathrm{DD}}$ | V  |  |

| V <sub>OL</sub> | Single-ended low level output voltage  | $I_{OL} = 100 \mu A$      | GND |  | 0.4               | V  |  |

08-0032

## Package Mechanical: 56-pin, Low Profile Quad Flat Package (ZF56)

### **Ordering Information**

| Ordering Code   | Package Code | Package Description          |

|-----------------|--------------|------------------------------|

| PI3HDMI231-AZFE | ZFE          | 56-pin, Pb-free & Green TQFN |

#### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding an X Suffix = Tape/Reel

- HDMI & Deep Color are trademarks of Silicon Image

### Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com

#### Disclaimer

HDMI Licensing, LLC, a wholly owned subsidiary of Silicon Image, Inc., is the agent responsible for licensing the HDMI Specification, promoting the HDMI standard and providing education on the benefits of HDMI to retailers and consumers. The HDMI Specification was developed by Sony, Hitachi, Thomson (RCA), Philips, Matsushita (Panasonic), Toshiba and Silicon Image as the digital interface standard for the consumer electronics market. The HDMI specification combines uncompressed high-definition video and multi-channel audio in a single digital interface to provide crystal-clear digital quality over a single cable. For more information about HDMI, please visit www.hdmi.org

08-0032