# **HDMI**<sup>TM</sup> Switch with non-blocking EQ Circuitry

#### **Features**

- Differential channel 3:1 Mux/DeMux for TDMS signals

- 3:1 Mux/DeMux for DDC signals

- non-EQ blocking circuitry to utilize ideal EQ found in main receiver chipset

- Low power consumption to support Energy Star Compliance

- Data rate support up to 3.4Gbps (16bit color depth per channel)

- 2 pin control for port selection

- 3.3V power and 5V standby power

- ESD protection on all I/O pins

- $\rightarrow \pm 8kV$  contact per IEC61000-4-2

- $\rightarrow$  7kV HBM per JESD22

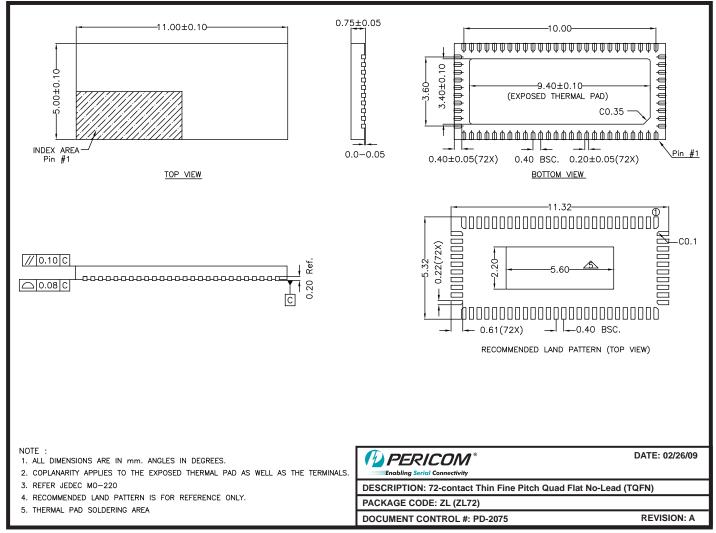

- Packaging (Pb-free & Green): 72 Contact TQFN

# **Description**

Pericom Semiconductor's PI3HDMI<sup>TM</sup> series of switch circuits are targeted for high-resolution video networks that are based on DVI/HDMI standards. The PI3HDMI1310-A is a 3-to-1 HDMI Mux/DeMux Switch. It is designed for low bit-to-bit skew and high channel-to-channel noise isolation. The maximum DVI/HDMI data rate of 3.4Gbps provides the resolution required by next generation HDTV and PC graphics. Three differential channels are used for data (video signals for DVI or audio/video signals for HDMI), and one differential channel is used for Clock for decoding the TMDS signals at the outputs.

PI3HDMI1310-A was designed specifically to meet ATC-Sink requirements. Therefore, Pericom recommends locating this switch at the sink to switch between multiple sources.

All input pins are protected with Pericom's ESD protection circuits, supporting protection against ESD damage as high as ±8kV contact per IEC6000-4-2 spec.

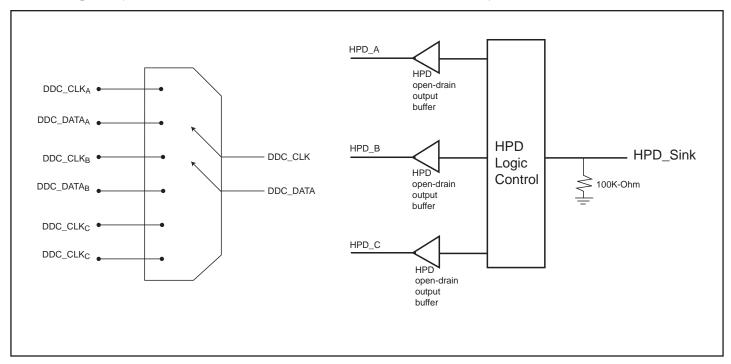

# **Block Diagram** (AUX/DDC Switch Channels and HPD Control Channels)

09-0073 10/08/09

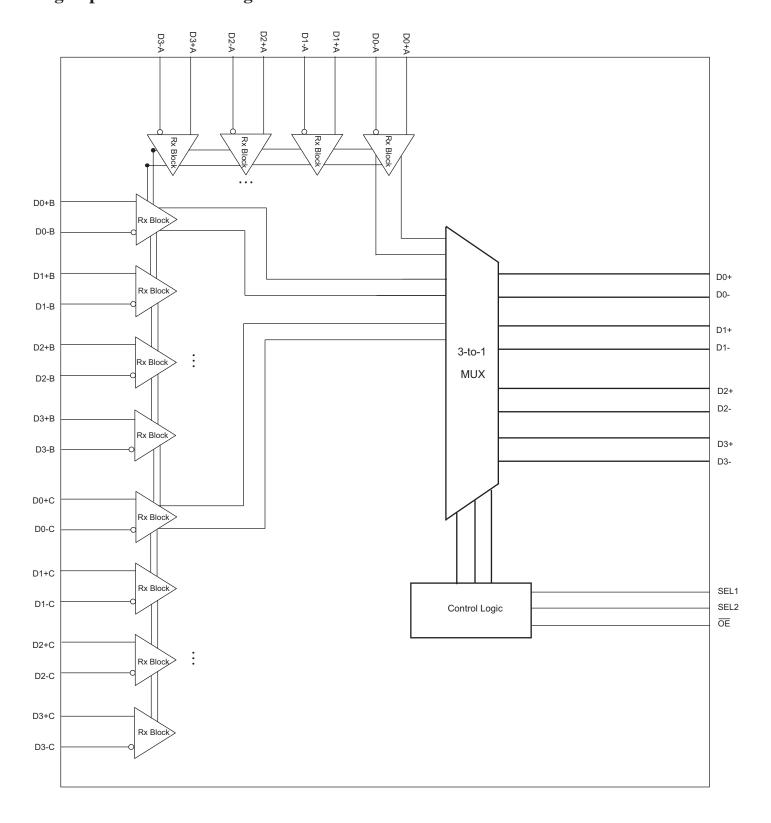

# **High Speed Differential Signal Switch Block**

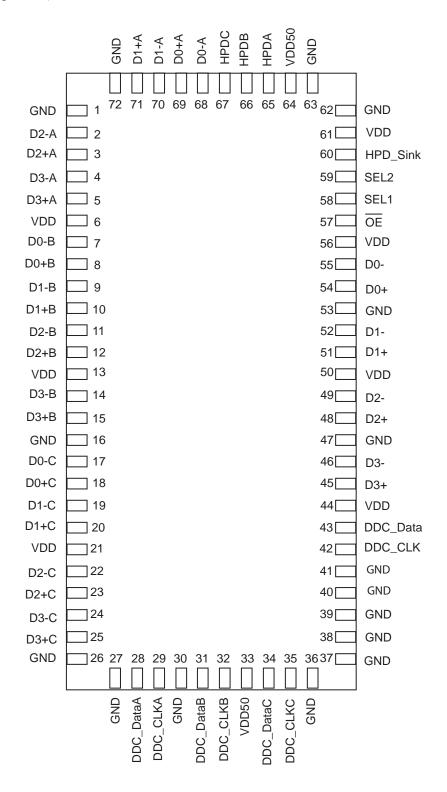

**Pin Configuration** (Top View)

# **Pin Description**

| Pin #                                                              | Pin Name                   | Pin Type | Description                                                                                                                                             |      |             |  |

|--------------------------------------------------------------------|----------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|--|

| 69, 68, 71, 70,<br>3, 2, 5, 4,                                     | $Dx\pm A (X = 0, 1, 2, 3)$ | I/O      | Port A High Speed inputs                                                                                                                                |      |             |  |

| 8, 7, 10, 9, 12,<br>11, 15, 14                                     | $Dx\pm B (X = 0, 1, 2, 3)$ | I/O      | Port B High Speed inputs                                                                                                                                |      |             |  |

| 18, 17, 20, 19,<br>23, 22, 25, 24                                  | $Dx\pm C (X = 0, 1, 2, 3)$ | I/O      | Port C High Speed inputs                                                                                                                                |      |             |  |

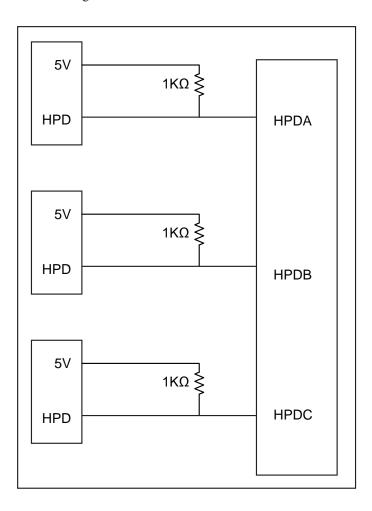

| 65, 66, 67                                                         | HPDA, HPDB, HPDC           | Output   | HPD open-drain outputs for each port. Logic will follow truth table on page 7. External 1Kohm pull-up to 5V is required                                 |      |             |  |

| 33, 64                                                             | VDD50                      | Power    | 5.0V voltage rail from HDMI/DVI connector. Used during standby-mode.                                                                                    |      |             |  |

| 60                                                                 | HPD_Sink                   | Input    | GP I/O pin from SCALAR. Internal 100Kohm pull-down.                                                                                                     |      |             |  |

| 29, 28, 32, 31,<br>35, 34, 42, 43                                  | DDC_CLKx, DDC_Datax        | I/O      | I <sup>2</sup> C signals for DDC communication on TMDS ports                                                                                            |      |             |  |

| 55, 54, 53, 52,<br>51, 49, 48, 46,<br>45                           | $DX \pm (x = 0, 1, 2, 3)$  | I/O      | 4-differential high speed Output signals                                                                                                                |      |             |  |

|                                                                    |                            | Inputs   | SEL1                                                                                                                                                    | SEL2 | Output Port |  |

|                                                                    | SEL1, SEL2                 |          | 0                                                                                                                                                       | 0    | Port A      |  |

| 58, 59                                                             |                            |          | 0                                                                                                                                                       | 1    | Port B      |  |

|                                                                    |                            |          | 1                                                                                                                                                       | 0    | Port C      |  |

|                                                                    |                            |          | 1                                                                                                                                                       | 1    | Hi-Z        |  |

| 6, 13, 21, 44,<br>50, 56, 61                                       | $V_{ m DD}$                | Power    | 3.3V Power Supply                                                                                                                                       |      |             |  |

| 1, 16, 26, 27,<br>30, 36, 37, 38,<br>39, 40, 41, 53,<br>62, 63, 72 | GND                        | Power    | Ground.                                                                                                                                                 |      |             |  |

| 57                                                                 | ŌĒ                         | Input    | Output enable (Active LOW). When HIGH, all outputs are Hi-Z and chip is placed into Standby Mode. Under Standby Mode, the current supply is from VDD50. |      |             |  |

# **BLOCK DIAGRAM EXPLANATION**

### **DDC Switch Block**

Passive NMOS based 3:1 mux for DDC channels from each HDMI/DVI input connector. This section can remain active even when 3.3V supply is gone, as long as 5.0V from TMDS connector is connects to the PI3HDMI1310-A IC.

# 3:1 High speed Differential Channel Block

4-differential channels per port. 3 channels are targeted for high speed data channels (250Mbps to 3.4Gbps) and 1 channel is targeted for high speed clock signal (25MHz to 340MHz).

### **HPD Control Channels Block**

Drives each HPD channels through the input pin, HPD\_Sink.

This signal will need to drive external pull-down transistor circuit before connecting to the HDMI/DVI connector. The external pull down circuit will look like the following:

09-0073 5 PS9077 10/08/09

# Truth table for HPDx signals

| Control Pins |      |      | Hot      | Plug Detect Sta | atus  |       |

|--------------|------|------|----------|-----------------|-------|-------|

| ŌĒ           | SEL1 | SEL2 | HPD_Sink | HPD A           | HPD B | HPD C |

| x            | L    | L    | L        | Hi-Z            | Hi-Z  | Hi-Z  |

| x            | L    | L    | H        | L               | Hi-Z  | Hi-Z  |

| X            | L    | H    | L        | Hi-Z            | Hi-Z  | Hi-Z  |

| X            | L    | H    | H        | Hi-Z            | L     | Hi-Z  |

| X            | H    | L    | L        | Hi-Z            | Hi-Z  | Hi-Z  |

| X            | H    | L    | H        | Hi-Z            | Hi-Z  | L     |

| X            | H    | H    | L        | Hi-Z            | Hi-Z  | Hi-Z  |

| X            | H    | H    | H        | Hi-Z            | Hi-Z  | Hi-Z  |

<sup>\*</sup>All Hi-Z will become H if external pull-up connected at the output.

# **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | 65°C to +150°C |

|------------------------------------|----------------|

| Supply Voltage to Ground Potential | 0.5V to +3.6V  |

| DC Input Voltage                   | -0.5V to 3.6V  |

| DC Output Current                  | 120mA          |

| Power Dissipation                  | 0.5W           |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **DC** Electrical Characteristics for Switching over Operating Range $(T_A = -40^{\circ}\text{C to} + 85^{\circ}\text{C}, V_{DD} = 3.3\text{V} \pm 10\%)$

| Parameter           | Description              | Test Conditions <sup>(1)</sup>   | Min  | Typ <sup>(2)</sup> | Max  | Units |  |

|---------------------|--------------------------|----------------------------------|------|--------------------|------|-------|--|

| V <sub>IH</sub>     | Input HIGH Voltage       | Guaranteed HIGH level            | 1.5  |                    |      |       |  |

| $v_{IL}$            | Input LOW Voltage        | Guaranteed LOW level             | -0.5 |                    | 0.65 | V     |  |

| V <sub>IK</sub> (1) | Clamp Diode Voltage      | $V_{DD} = Max., I_{IN} = -18mA$  |      | -0.7               | -1.2 |       |  |

| IIH                 | Input HIGH Current       | $V_{DD} = Max., V_{IN} = V_{DD}$ |      |                    | ±5   |       |  |

| III                 | Input LOW Current        | $V_{DD} = Max., V_{IN} = GND$    |      |                    | ±5   | μΑ    |  |

| I <sub>OFF</sub>    | Off Leakage Current      | $V_{DD} = 0V$                    |      |                    | 10   | 7     |  |

| Status Pins (H      | IPD_SINK)                |                                  |      |                    |      |       |  |

| V <sub>IH</sub>     | LVTTL Input HIGH Voltage |                                  | 2    |                    | 5.3  | 1,7   |  |

| $V_{\mathrm{IL}}$   | LVTTL Input LOW Voltage  |                                  | GND  |                    | 0.8  | V     |  |

| Rp                  | Pull-down Resistance     | $V_{DD}50 = 5.0V$                |      | 100K               |      | Ohm   |  |

<sup>1.</sup> Substrate diode voltage drop. For testing reference.

09-0073 6 PS9077 10/08/09

**Power Supply Characteristics**

| Parameters       | Description                    | Test Conditions <sup>(1)</sup>                     | Min. | Typ. (2) | Max. | Units |

|------------------|--------------------------------|----------------------------------------------------|------|----------|------|-------|

| $I_{DD}$         | Operating Power Supply Current | $V_{DD} = Max., V_{SELx} = GND \text{ or } V_{DD}$ |      | 6        | 10   | mA    |

| I <sub>DDQ</sub> | Standby Supply Current         | OE - High                                          |      | 3        | 5    |       |

# **Dynamic Electrical Characteristics Over the Operating Range** (T<sub>A</sub>= -40° to +85°C, V<sub>DD</sub> = 3.3V ±10%, GND=0V)

| Parameter                                       | Description                                                          | <b>Test Conditions</b>                                                         |             | Min | Typ. (2)                                 | Max | Units |

|-------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------|-----|------------------------------------------|-----|-------|

| X <sub>TALK</sub> Crosstalk on High Speed Chann |                                                                      | See Fig. 3 for                                                                 | f= 1.13 GHz |     | -34                                      |     |       |

|                                                 | Crosstalk on High Speed Channels                                     | Measurement<br>Setup                                                           | f = 825 MHz |     | -36                                      |     | ] ,,, |

|                                                 | OFF Isolation on High Speed                                          | See Fig. 2 for                                                                 | f= 1.13 GHz |     | -28                                      |     | dB    |

| O <sub>IRR</sub>                                | OIRR Channels Measureme Setup                                        | Measurement<br>Setup                                                           | f = 825 MHz |     | -32                                      |     |       |

| $I_{LOSS}$                                      | Differential Insertion Loss on High<br>Speed Channels (see figure 1) | DR = 1.54Gbps<br>DR = 2.0Gbps<br>DR = 2.25Gbps<br>DR = 3.0Gbps<br>DR = 3.4Gbps |             |     | -1.5<br>-1.73<br>-1.82<br>-1.99<br>-2.08 |     | dB    |

| BW                                              | -3dB BW for TMDS channels                                            |                                                                                |             |     | 3.0                                      |     | GHz   |

| <b>Status Pins</b>                              | Status Pins (HPD) - open drain output buffer                         |                                                                                |             |     |                                          |     |       |

| V <sub>OL(TTL)</sub>                            | TTL Low-level output voltage                                         | $I_{OL} = 4mA$                                                                 |             |     |                                          | 0.4 | V     |

#### **Notes:**

7 PS9077 10/08/09 09-0073

For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

Typical values are at  $V_{DD} = 3.3V$ ,  $T_A = 25$ °C ambient and maximum loading.

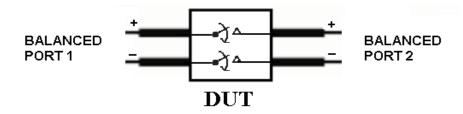

Fig.1 Differential Insertion Loss and Return Loss Test Circuit

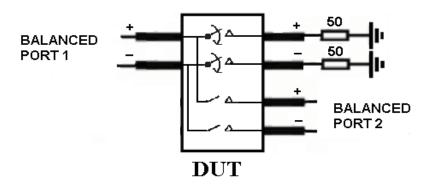

Fig.2 Differential Off Isolation Test Circuit

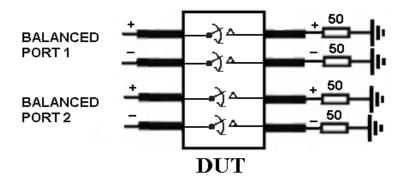

Fig.3 Differential Near End Crosstalk Test Circuit

09-0073 8 PS9077 10/08/09

# **Switching Characteristics** ( $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}, V_{DD} = 3.3\text{V} \pm 10\%$ )

| Parameter        | Description                                       | Min. | Max. | Units       |

|------------------|---------------------------------------------------|------|------|-------------|

| tpzh, tpzl       | Line Enable Time                                  | 0.5  | 25   | <b>10</b> G |

| tpHZ, tPLZ       | Line Disable Time                                 | 0.5  | 25   | ns          |

| t <sub>b-b</sub> | Bit-to-bit skew within the same differential pair | 15   |      | <b>12</b> G |

| tch-ch           | Channel-to-channel skew                           |      | 35   | ps          |

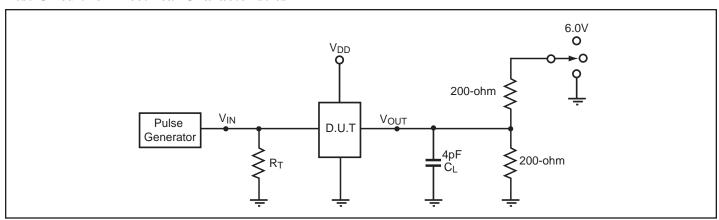

# **Test Circuit for Electrical Characteristics**(1-5)

#### Notes

- 1.  $C_L = Load$  capacitance: includes jig and probe capacitance.

- 2.  $R_T$  = Termination resistance: should be equal to  $Z_{OUT}$  of the Pulse Generator

- 3. Output 1 is for an output with internal conditions such that the output is low except when disabled by the output control. output 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- 4. All input impulses are supplied by generators having the following characteristics:  $PRR \le MHz$ ,  $Z_O = 50\Omega$ ,  $t_R \le 2.5$ ns,  $t_F \le 2.5$ ns.

- 5. The outputs are measured one at a time with one transition per measurement.

### **Switch Positions**

| Test                                                   | Switch |

|--------------------------------------------------------|--------|

| t <sub>PLZ</sub> , t <sub>PZL</sub> (output on B-side) | 6.0V   |

| t <sub>PHZ</sub> , t <sub>PZH</sub> (output on B-side) | GND    |

| Prop Delay                                             | Open   |

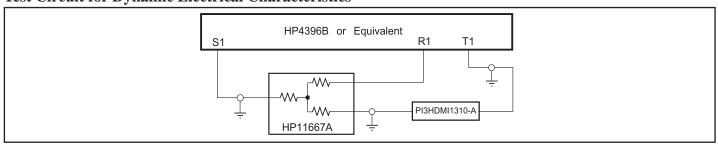

# **Test Circuit for Dynamic Electrical Characteristics**

9 PS9077 10/08/09

# Packaging Mechanical: 72-Contact TQFN

09-0134

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

# **Ordering Information**

| Ordering Code    | Package Code | Package Description               |

|------------------|--------------|-----------------------------------|

| PI3HDMI1310-AZLE | ZL           | Pb-free and Green 72-contact TQFN |

10

#### **Notes:**

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- "E" denotes Pb-free and Green

- Adding an "X" at the end of the ordering code denotes tape and reel packaging