# **PI3PCIE2612-A**

# High Bandwidth, 6-Differential Channel 1:2 DP/PCIe Gen2 Display Mux, ATX Pinout

## Features

- 6 Differential Channel, 1 to 2 demux that will support 5.0Gbps PCIexpress Gen2 signals on one path, and DP 1.1 signals on the second path

- Insertion Loss for high speed channels @ 5.0 Gbps: -5.0dB

- Low Bit-to-Bit Skew, 7ps max (between '+' and '-' bits)

- Latched Mux Select

- Matched paths for all PCIe signals

- Low Crosstalk for high speed channels: -35dB@2.5 GHz

- Low Off Isolation for high speed channels: -35dB@2.5 GHz

- V<sub>DD</sub> Operating Range:  $3.3V \pm 10\%$

- ESD Tolerance: 8kV contact on Display Port Path output 4kV HBM on PCI-Express path output

- Low channel-to-channel skew, 35ps max

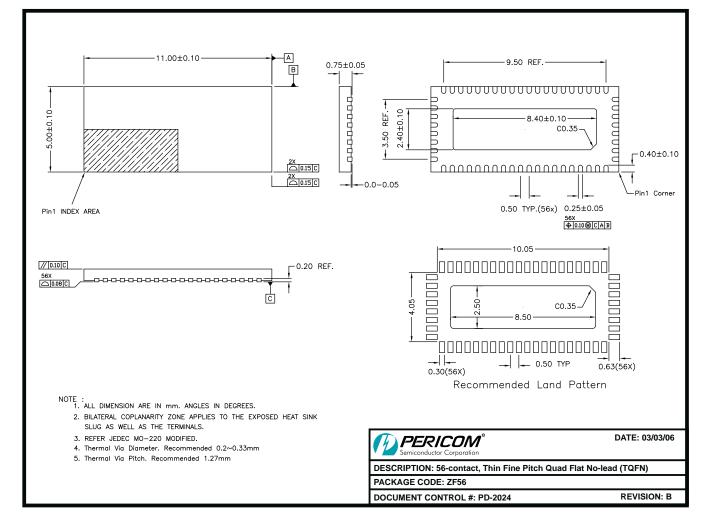

- Packaging (Pb-free & Green): - 56 TQFN (ZFE)

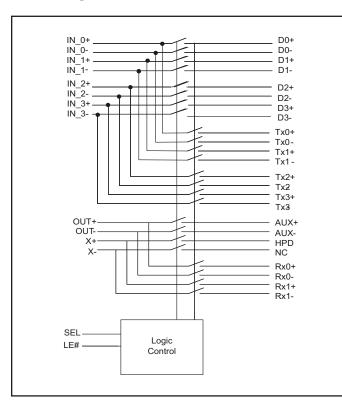

## **Block Diagram**

•

### Truth Table (SEL control)

Downloaded from Elcodis.com electronic components distributor

| Function                             | SEL |

|--------------------------------------|-----|

| PCI-Express Gen2 path is active (Tx) | L   |

| Digital Video Port is active (Dx)    | Н   |

## Description

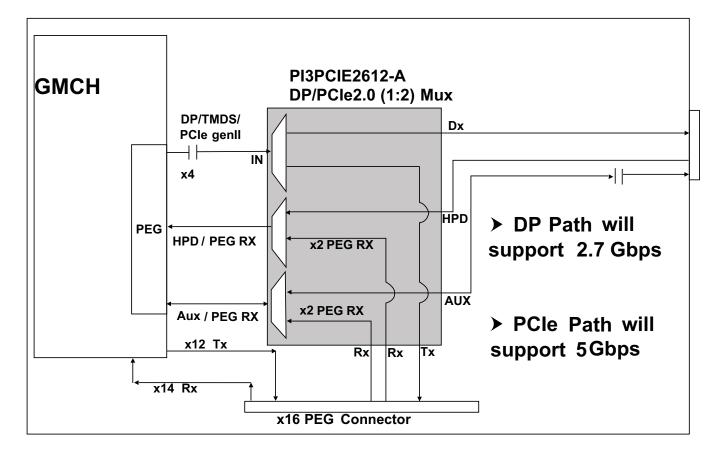

Pericom Semiconductor's PI3PCIE2612-A one to two Mux/ Demux is targeted for next generation systems that combine PCI-Express gen-II signals with Display Port Signals.

### Application

Routing DP and PCIExpress Gen1 or Gen2 signals with low signal attenuation.

## Pin Diagram (top-side view)

|       |    | <b>UND</b> | DQ/ | 1×0+ | Tx0- | 7+<br>7  | <u>7</u> | DQ/ | SND |    |      |

|-------|----|------------|-----|------|------|----------|----------|-----|-----|----|------|

|       |    | $\square$  |     |      |      |          |          |     |     |    |      |

|       |    | 56         | 55  | 54   | 53   | 52       | 51       | 50  | 49  |    |      |

| GND   | 1  |            |     |      |      |          |          |     |     | 48 | GND  |

| IN_0+ | 2  |            |     |      |      |          |          |     |     | 47 | Tx2+ |

| IN_0- | 3  |            |     |      |      |          |          |     |     | 46 | Tx2- |

| IN_1+ | 4  |            |     |      |      |          |          |     |     | 45 | Tx3+ |

| IN_1- | 5  |            |     |      |      |          |          |     |     | 44 | Tx3- |

| VDD   | 6  |            |     |      |      |          |          |     |     | 43 | D0+  |

| IN_2+ | 7  |            |     |      |      |          |          |     |     | 42 | D0-  |

| IN_2- | 8  |            |     |      |      |          |          |     |     | 41 | D1+  |

| IN_3+ | 9  |            |     |      |      |          |          |     |     | 40 | D1-  |

| IN_3- | 10 |            |     |      |      |          |          |     |     | 39 | D2+  |

| GND   | 11 |            |     |      |      |          |          |     |     | 38 | D2-  |

| OUT+  | 12 |            |     |      |      |          |          |     |     | 37 | D3+  |

| OUT-  | 13 |            |     |      |      |          |          |     |     | 36 | D3-  |

| X+    | 14 |            |     |      |      |          |          |     |     | 35 | GND  |

| X-    | 15 |            |     |      |      |          |          |     |     | 34 | VDD  |

| GND   | 16 |            |     |      |      |          |          |     |     | 33 | Rx0+ |

| VDD   | 17 |            |     |      |      |          |          |     |     | 32 | Rx0- |

| SEL   | 18 |            |     |      |      |          |          |     |     | 31 | Rx1+ |

| LE#   | 19 |            |     |      |      |          |          |     |     | 30 | Rx1- |

| GND   | 20 |            |     |      |      |          |          |     |     | 29 | GND  |

|       |    | 21         | 22  | 23   | 24   | 25       | 26       | 27  | 28  |    |      |

| I     |    |            |     |      |      | <u> </u> | +        |     |     |    |      |

|       |    | GND        | VDD | NC   | ΠРΟ  | AUX      | +XUA     | VDD | GND |    |      |

|       |    |            |     |      |      |          |          |     |     |    |      |

### Truth Table (Latch control)

| LE# | Internal mux select       |

|-----|---------------------------|

| 0   | Respond to changes on SEL |

| 1   | Latched                   |

## Application Example

### **Pin Description**

| Pin Number | Pin Name | Туре | Description                                                                                                                                       |

|------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 26         | AUX+     | 0    | Differential input from HDMI/DP connector. AUX+ makes a dif-<br>ferential pair with AUX AUX+ is passed through to the OUT+<br>pin when SEL = 1.   |

| 25         | AUX-     | 0    | Differential input from HDMI/DP connector. AUX- makes a dif-<br>ferential pair with AUX+. AUX- is passed through to the OUT-<br>pin when SEL = 1. |

| 43, 42     | D0+, D0- | 0    | Analog "pass through" output#1 corresponding to IN_0+ and IN_0-, when SEL = 1.                                                                    |

| 41, 40     | D1+, D1- | 0    | Analog "pass through" output#1 corresponding to IN_1+ and IN_1-, when SEL = 1.                                                                    |

| 39, 38     | D2+, D2- | 0    | Analog "pass through" output#1 corresponding to IN_2+ and IN_2-, when SEL = 1.                                                                    |

| 37, 36     | D3+, D3- | 0    | Analog "pass through" output#1 corresponding to IN_3+ and IN_3-, when SEL = 1.                                                                    |

| Pin Number      | Pin Name | Туре    | Description                                                              |

|-----------------|----------|---------|--------------------------------------------------------------------------|

| 1, 11, 20, 21,  | GND      | Power - |                                                                          |

| 28, 29, 35, 48, |          | Ground. |                                                                          |

| 49, 56          |          |         |                                                                          |

| 24              | HPD      | Ι       | The HPD signal comes from the HDMI or DP connector. This is              |

|                 |          |         | a low frequency, 0V to 5V (HDMI) or 3.6V (DP) input signal at            |

|                 |          |         | the connector.                                                           |

|                 |          |         | The HPD input at the mux is 3.6V max, so HDMI HPD must be                |

|                 |          |         | shifted down from 5V before it is passed to the mux.                     |

| 2               | IN_0+    | Ι       | Differential input from GMCH PCIE outputs. IN_0+ makes a                 |

|                 |          |         | differential pair with IN_0                                              |

| 3               | IN_0-    | Ι       | Differential input from GMCH PCIE outputs. IN_0- makes a dif-            |

|                 |          |         | ferential pair with IN_0+.                                               |

| 4               | IN_1+    | Ι       | Differential input from GMCH PCIE outputs. IN_1+ makes a                 |

|                 |          |         | differential pair with IN_1                                              |

| 5               | IN_1-    | Ι       | Differential input from GMCH PCIE outputs. IN_1- makes a dif-            |

|                 |          |         | ferential pair with IN_1+.                                               |

| 7               | IN_2+    | Ι       | Differential input from GMCH PCIE outputs. IN_2+ makes a                 |

|                 | _        |         | differential pair with IN_2                                              |

| 8               | IN_2-    | Ι       | Differential input from GMCH PCIE outputs. IN_2- makes a dif-            |

|                 | _        |         | ferential pair with IN_2+.                                               |

| 9               | IN_3+    | Ι       | Differential input from GMCH PCIE outputs. IN 3+ makes a                 |

|                 | _        |         | differential pair with IN_3                                              |

| 10              | IN_3-    | Ι       | Differential input from GMCH PCIE outputs. IN_3- makes a dif-            |

|                 | _        |         | ferential pair with IN_3+.                                               |

| 19              | LE#      | Ι       | The latch gate is controlled by LE. 3.6V tolerant, low-voltage,          |

|                 |          |         | single-ended input.                                                      |

| 23              | NC       | Do Not  |                                                                          |

|                 |          | Connect |                                                                          |

| 12              | OUT+     | 0       | Pass-through output from AUX+ input when SEL = 1. Pass-                  |

|                 |          |         | through output from $Rx0+$ input when $SEL = 0$ .                        |

| 13              | OUT-     | 0       | Pass-through output from AUX- input when SEL = 1. Pass-                  |

| -               |          | -       | through output from Rx0- input when $SEL = 0$ .                          |

| 33              | Rx0+     | I/O     | Differential input from PCIE connector or device. Rx0+ makes a           |

|                 | 1010     | 1,0     | differential pair with $Rx0-$ . $Rx0+$ is passed through to the OUT+     |

|                 |          |         | pin when $SEL = 0$ .                                                     |

| 32              | Rx0-     | I/O     | Differential input from PCIE connector or device. Rx0- makes a           |

|                 | 1010     | 1,0     | differential pair with $Rx0+$ . $Rx0-$ is passed through to the OUT-     |

|                 |          |         | pin when $SEL = 0$ .                                                     |

| 31              | Rx1+     | Ι       | Differential input from PCIE connector or device. Rx1+ makes a           |

|                 |          |         | differential pair with $Rx1-$ . $Rx1+$ is passed through to the $X+$ pin |

|                 |          |         | when $SEL = 0$ .                                                         |

|                 | 1        | 1       | (Continued)                                                              |

| Pin Number                   | Pin Name   | Туре  | Description                                                                                                                                                                                                                            |

|------------------------------|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30                           | Rx1-       | Ι     | Differential input from PCIE connector or device. Rx1- makes a differential pair with Rx1+. Rx1- is passed through to the X- pin on a path that matches the Rx1+ to X+ path.                                                           |

| 18                           | SEL        | Ι     | SEL controls the mux through a flow-through latch. 3.6V toller-<br>ant low-voltage single-ended output<br>SEL = 0 for PCIE Mode<br>SEL = 1 for DP Mode                                                                                 |

| 54, 53                       | Tx0+,Tx0-  | 0     | Analog "pass through" output#2 corresponding to IN_0+ and IN_0-, when SEL = 0.                                                                                                                                                         |

| 52, 51                       | Tx1+, Tx1- | 0     | Analog "pass through" output#2 corresponding to IN_1+ and IN_1-, when SEL = 0.                                                                                                                                                         |

| 47, 46                       | Tx2+, Tx2- | 0     | Analog "pass through" output#2 corresponding to $IN_2$ + and $IN_2$ -, when $SEL = 0$ .                                                                                                                                                |

| 45, 44                       | Tx3+, Tx3- | 0     | Analog "pass through" output#2 corresponding to $IN_3$ + and $IN_3$ -, when $SEL = 0$ .                                                                                                                                                |

| 6, 17, 22, 27,<br>34, 50, 55 | VDD        | Power | 3.3V DC Supply, 3.3V +/- 10%                                                                                                                                                                                                           |

| 14                           | X+         | I/O   | HPD: Low frequency, 0V to 5V/3.3V (nominal) input signal at the connector. This signal comes from the HDMI/DP connector. X+: Analog "pass through" output corresponding to Rx1+.                                                       |

| 15                           | X-         | Ι     | X- is an analog "pass-through" output corresponding to the Rx1-<br>input. The path from Rx1- to X- must be matched with the path<br>from Rx1+ to X+. X+ and X- form a differential pair when the<br>pass-through mux mode is selected. |

### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | 65°C to +150°C          |

|------------------------------------|-------------------------|

| Supply Voltage to Ground Potential | 0.5V to +4.6V           |

| DC Input Voltage                   | 0.5V to V <sub>DD</sub> |

| DC Output Current                  | 120mA                   |

| Power Dissipation                  | 0.5W                    |

|                                    |                         |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Electrical Characteristics**

**Recommended Operating Conditions**

| Symbol | Parameter                                               | Conditions | Min | Тур | Max | Units   |

|--------|---------------------------------------------------------|------------|-----|-----|-----|---------|

| VDD    | 3.3V Power Supply                                       |            | 3.0 | 3.3 | 3.6 | V       |

| IDD    | Total current from<br>VDD 3.3V supply                   |            | 0   |     | 2.5 | mA      |

| TCASE  | Case temperature<br>range for operation<br>within spec. |            | -40 |     | 85  | Celcius |

### **DC Electrical Characteristics** ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , $V_{DD} = 3.3V \pm 10\%$ )

| Parameter                         | Description            | Test Conditions                                  | Min | Typ <sup>(1)</sup> | Max | Units |

|-----------------------------------|------------------------|--------------------------------------------------|-----|--------------------|-----|-------|

| V <sub>IH-EN</sub> <sup>(2)</sup> | Input high level       |                                                  | 2.0 |                    | 3.6 | V     |

| V <sub>IL-EN</sub> <sup>(2)</sup> | Input Low Level        |                                                  | 0   |                    | 0.8 | V     |

| I <sub>IN_EN<sup>(2)</sup></sub>  | Input Leakage Current  | Measured with input at VIH-EN max and VIL-EN min | -10 |                    | 10  | uA    |

| R <sub>ON</sub>                   | On Resistance          | $V_{DD} = Min., V_{IN} = 1.3V, I_{IN} = 40mA$    |     |                    | 10  | Ohm   |

| C <sub>ON</sub>                   | On Channel Capacitance | $V_{IN} = 0, V_{DD} = 3.3V$                      |     | 3.0                |     | pF    |

Note:

1. Typical values are at  $V_{DD}$  = 3.3V,  $T_A$  = 25°C ambient and maximum loading.

2. For SEL and LE# inputs

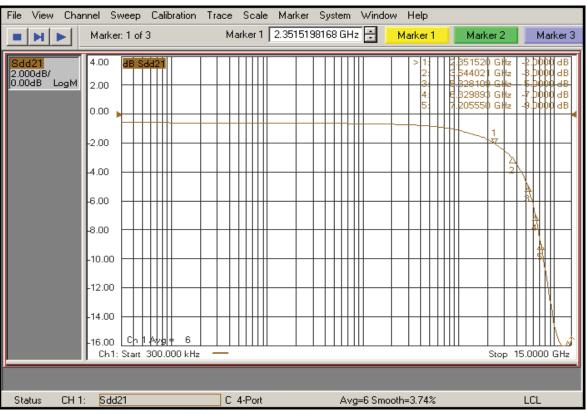

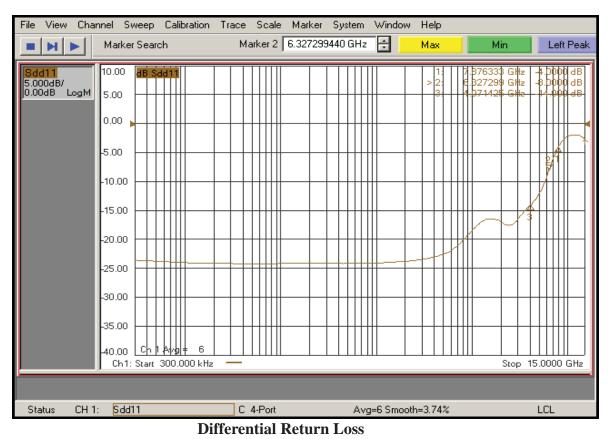

## Dynamic Electrical Characteristics for IN\_x+/-, Rxy+/-, and Txy+/-

| Parameter           | Description                 | Test Conditions                                        | Min. | <b>Typ.</b> <sup>(1)</sup>   | Max. | Units |

|---------------------|-----------------------------|--------------------------------------------------------|------|------------------------------|------|-------|

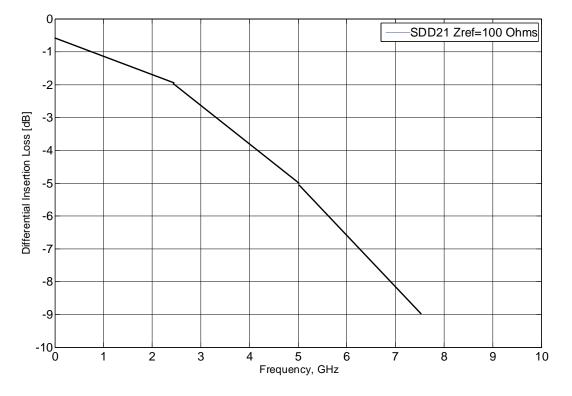

| DDIL                | Differential Insertion Loss | f=1.2GHz<br>f=2.5GHz<br>f=5.0GHz<br>f=7.5GHz           |      | -1.5<br>-2.0<br>-5.0<br>-9.0 |      |       |

| DDIL <sub>OFF</sub> | Differential Off Isolation  | f= 0 to 3.0GHz<br>f= 5.0GHz                            |      | -23.0<br>-20.0               |      | dB    |

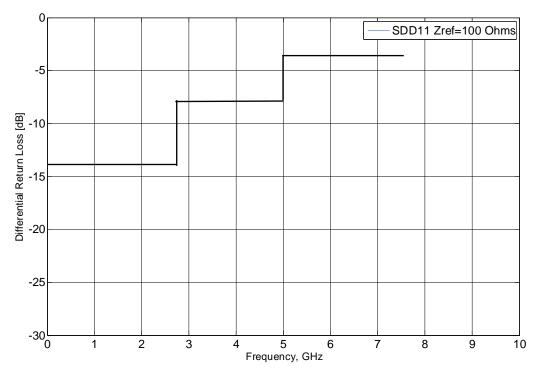

| DDRL                | Differential Return Loss    | f= 0 to 2.8GHz<br>f= 2.8 to 5.0GHz<br>f= 5.0 to 7.5GHz |      | -14.0<br>-8.0<br>-4.0        |      | uБ    |

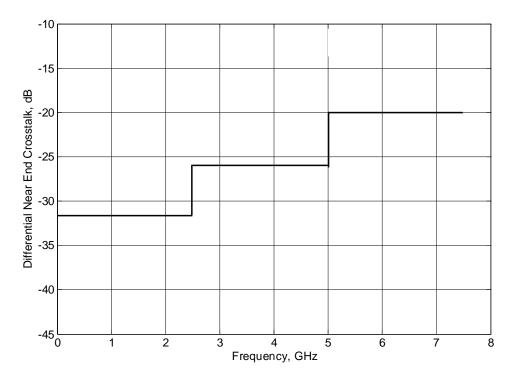

| DDNEXT              | Near End Crosstalk          | f= 0 to 2.5GHz<br>f= 2.5 to 5.0GHz<br>f= 5.0 to 7.5GHz |      | -32.0<br>-26.0<br>-20.0      |      |       |

## Dynamic Electrical Characteristics for Dx+/-

| Parameter          | Description                              | Test Conditions                      | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |

|--------------------|------------------------------------------|--------------------------------------|------|----------------------------|------|-------|

| DDIL <sub>DP</sub> | Display Port Differential Insertion Loss | f= 0 to 1.35GHz<br>f= 1.35 to 2.7GHz |      | -1.5<br>-4.5               |      |       |

| DDRL <sub>DP</sub> | Display Port Differential Return Loss    | f= 0 to 2.7GHz                       |      | -14                        |      | dB    |

| DDNEXT-<br>DP      | Display Port Near End Crosstalk          | f= 0 to 2.7GHz                       |      | -32.0                      |      |       |

## Switching Characteristics ( $T_A$ = -40° to +85°C, $V_{DD}$ = 3.3V±10%)

| Parameter          | Description                                                                          | Test Conditions                                      | Min. | Тур. | Max. | Units |

|--------------------|--------------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|-------|

| tpZH, tpZL         | Line Enable Time - SEL to $D_X \pm$ , $T_{XY} \pm$ , $R_{XY} \pm$ , $AUX \pm$ , HPD  | See "Test Circuit for<br>Electrical Chatacteristics" | 0.5  |      | 12.0 | ns    |

| tpHZ, tPLZ         | Line Disable Time - SEL to $D_X \pm$ , $T_{XY} \pm$ , $R_{XY} \pm$ , $AUX \pm$ , HPD | See "Test Circuit for<br>Electrical Chatacteristics" | 0.5  |      | 12.0 | ns    |

| t <sub>b-b</sub>   | Bit-to-bit skew within the same differential pair                                    | See "Test Circuit for<br>Electrical Chatacteristics" |      |      | 7    | ps    |

| t <sub>ch-ch</sub> | Channel-to-channel skew                                                              | See "Test Circuit for<br>Electrical Chatacteristics" |      |      | 35   | ps    |

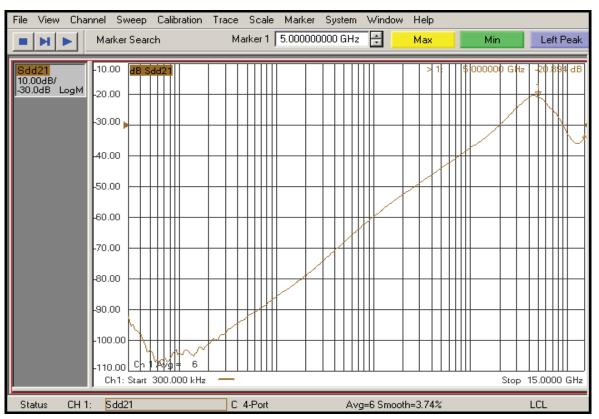

### **Differential Insertion Loss**

#### 07-0261

### **Off Isolation**

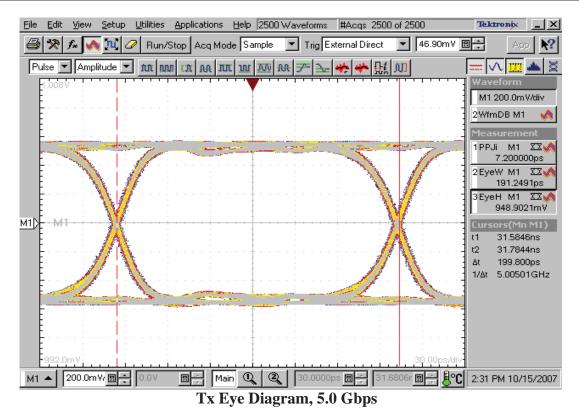

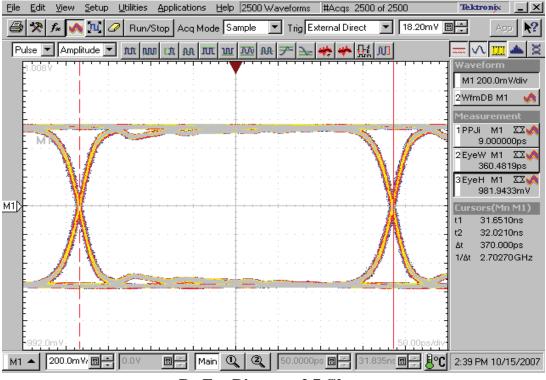

Dx Eye Diagram, 2.7 Gbps

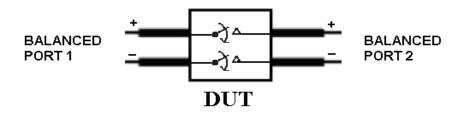

### Differential Insertion Loss and Return Loss Test Circuit

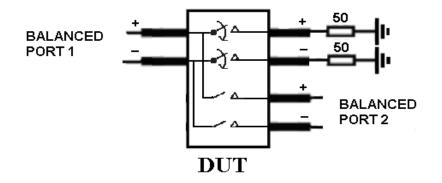

**Differential Off Isolation Test Circuit**

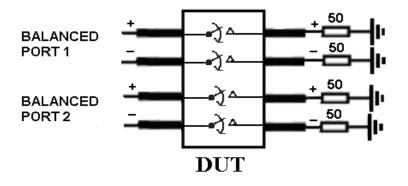

### Differential Near End Crosstalk Test Circuit

## PI3PCIE2612-A High Bandwidth, 6-Differential Channel 1:2 DP/PCIe Gen2 Display Mux. ATX Pinout

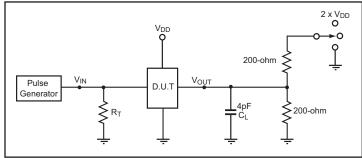

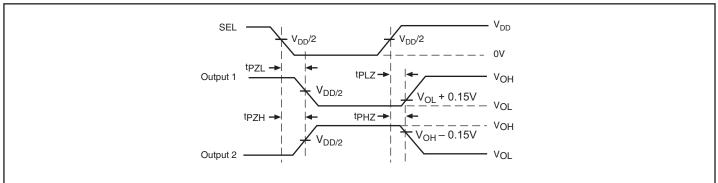

# <u>Test Circuit for Electrical Characteristics</u><sup>(1-5)</sup>

### **Switch Positions**

| Test                                | Switch              |

|-------------------------------------|---------------------|

| t <sub>PLZ</sub> , t <sub>PZL</sub> | 2 x V <sub>DD</sub> |

| t <sub>PHZ</sub> , t <sub>PZH</sub> | GND                 |

| Prop Delay                          | Open                |

### Notes:

- 1.  $C_L$  = Load capacitance: includes jig and probe capacitance.

- 2.  $R_T$  = Termination resistance: should be equal to  $Z_{OUT}$  of the Pulse Generator

- 3. Output 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

- output 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- 4. All input impulses are supplied by generators having the following characteristics:  $PRR \le MHz$ ,  $Z_0 = 50\Omega$ ,  $t_R \le 2.5ns$ ,  $t_F \le 2.5ns$ .

- 5. The outputs are measured one at a time with one transition per measurement.

### **Switching Waveforms**

### **Voltage Waveforms Enable and Disable Times**

# **Applications Information**

Differential Input Characteristics for IN\_x+/- and Rxx+/- signals.

| Symbol                     | Parameter                                         | Min                                                                                                                                                                                                                                                                                                                                                                                     | Nom    | Max    | Units | Comments                                                                                                                                                    |

|----------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tbit                       | Unit Interval                                     | 199.94                                                                                                                                                                                                                                                                                                                                                                                  | 200.00 | 200.06 | Ps    | Defined by Gen2 spec.                                                                                                                                       |

| V <sub>RX</sub> -Diffp-p   | Differential Input Peak<br>to Peak Voltage        | 0.175                                                                                                                                                                                                                                                                                                                                                                                   |        | 1.200  | V     | VRX-DIFFp-p = 2* VRX-<br>D+ - VRX-D- . Applies to<br>IN_D and RX_IN signals.                                                                                |

| T <sub>RX-EYE</sub>        | Minimum Eye Width at IN_D input pair.             | TBD                                                                                                                                                                                                                                                                                                                                                                                     |        |        | Tbit  |                                                                                                                                                             |

| V <sub>CM</sub> -AC-pp     | AC Peak Common-<br>Mode Input Voltage             |                                                                                                                                                                                                                                                                                                                                                                                         |        | 100    | mV    | VCM-AC-pp =<br> VRX-D+ + VRX-D- /2<br>- VRX-CM-DC.<br>VRX-CM-DC =<br>DC(avg) of  VRX-D++<br>VRX-D- /2<br>VCM-AC-pp includes all<br>frequencies above 30kHz. |

| Z <sub>RX</sub> -DIFF-DC   | DC Differential Input<br>Impedance                | 80                                                                                                                                                                                                                                                                                                                                                                                      | 100    | 120    | Ω     | Rx DC Differential Mode impedance.                                                                                                                          |

| Z <sub>RX-DC</sub>         | DC Input Impedance                                | 40                                                                                                                                                                                                                                                                                                                                                                                      | 50     | 60     | Ω     | Required IN_D+ as well<br>as IN_D- DC impedance<br>(50 $\Omega$ +/- 20% tolerance).<br>Includes mux resistance.                                             |

| V <sub>RX-Bias</sub>       | Rx input termination voltage                      | 0                                                                                                                                                                                                                                                                                                                                                                                       |        | 2.0    | V     | Intended to limit power-<br>up stress on PCIE output<br>buffers.                                                                                            |

| DDIL                       | Differential Insertion<br>Loss                    | $ \ge -[0.6^*(f)+0.5] \text{ dB up to } 2.5 \\ \text{GHz (for example, } \ge -2 \text{ dB at } f \\ = 2.5 \text{ GHz}); \\ \ge -[1.2^*(f-2.5)+2] \text{ dB for } 2.5 \\ \text{GHz} < f \le 5 \text{ GHz (for example, } 2.5 \\ \text{GHz} < f \le 5 \text{ GHz (for example, } 2.5 \\ = -[1.6^*(f-5)+5] \text{ dB for } 5 \text{ GHz}; \\ \ge -9 \text{ dB at } f = 7.5 \text{ GHz}); $ |        |        | dB    |                                                                                                                                                             |

| DDRL                       | Differential Return<br>Loss                       | $\leq$ -14 dB up to 2.8 GHz; $\leq$ -8 dB up to 5 GHz; $\leq$ -4 dB up to 7.5 GHz.                                                                                                                                                                                                                                                                                                      |        |        | dB    |                                                                                                                                                             |

| DDNEXT                     | Near End Crosstalk                                | -32 dB max up to 2.5 GHz; -<br>26 dB max up to 5.0 GHz; -20<br>dB max up to 7.5 GHz;                                                                                                                                                                                                                                                                                                    |        |        | dB    |                                                                                                                                                             |

| DDIL when<br>switch is off | Differential Insertion<br>Loss when switch is off | $\leq$ -20 dB up to 3 GHz;                                                                                                                                                                                                                                                                                                                                                              |        |        | dB    |                                                                                                                                                             |

## **PCIe Gen2 Output Characteristics**

| Symbol                  | Parameter                                         | Min                                                                                                                                                                                                                                                                   | Nom       | Max | Units | Comments                                                                                                               |

|-------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-------|------------------------------------------------------------------------------------------------------------------------|

| Z <sub>RX-DIFF-DC</sub> | DC Differential Input<br>Impedance                | 80                                                                                                                                                                                                                                                                    | 100       | 120 | Ω     | Rx DC Differential<br>Mode impedance.                                                                                  |

| Z <sub>RX-DC</sub>      | DC Input Impedance                                | 40                                                                                                                                                                                                                                                                    | 50        | 60  | Ω     | Required IN_D+ as well<br>as IN_D- DC imped-<br>ance ( $50\Omega$ +/- 20% tol-<br>erance). Includes mux<br>resistance. |

| V <sub>RX-Bias</sub>    | Rx input termination voltage                      | 0                                                                                                                                                                                                                                                                     |           | 2.0 | V     | Intended to limit pow-<br>er-up stress on PCIE<br>output buffers.                                                      |

| DDIL                    | Differential Insertion<br>Loss                    | ≥-[0.6*(f)+0.5] dB up to 2.5<br>GHz (for example, ≥-2 dB at<br>f = 2.5 GHz);<br>≥-[1.2*(f-2.5)+2] dB for 2.5<br>GHz < f ≤ 5 GHz (for exam-<br>ple, ≥-5 dB at f = 5 GHz);<br>≥-[1.6*(f-5)+5] dB for 5<br>GHz < f ≤ 7.5 GHz (for<br>example, ≥-9 dB at f = 7.5<br>GHz); |           |     | dB    |                                                                                                                        |

| DDRL                    | Differential Return Loss                          | $ \leq -14 \text{ dB up to } 2.8 \text{ GHz}; \leq -8 \\ \text{dB up to } 5 \text{ GHz}; \leq -4 \text{ dB up} \\ \text{to } 7.5 \text{ GHz}. $                                                                                                                       |           |     | dB    |                                                                                                                        |

| DDNEXT                  | Near End Crosstalk                                | -32 dB max up to 2.5 GHz;<br>-26 dB max up to 5.0 GHz;<br>-20 dB max up to 7.5 GHz;                                                                                                                                                                                   |           |     | dB    |                                                                                                                        |

| DDIL when switch is off | Differential Insertion<br>Loss when switch is off | $\leq$ -20 dB                                                                                                                                                                                                                                                         | up to 3 G | Hz; | dB    |                                                                                                                        |

Downloaded from Elcodis.com electronic components distributor

## **Display Port Output Characteristics**

| Symbol                   | Parameter                                  | Min                                                                                                              | Nom        | Max    | Units                                                                                           | Comments                                                                                                                |

|--------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------|--------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Tbit                     | Unit Interval                              | 333                                                                                                              |            |        | ps                                                                                              | Normal Tbit at 2.7Gb/<br>s=370ps. 333ps=370ps-<br>10%                                                                   |

| V <sub>RX</sub> -Diffp-p | Differential Input Peak to<br>Peak Voltage | 0.340                                                                                                            |            | 1.38   | V                                                                                               | VRX-DIFFp-p =<br>2* VRX-D+ - VRX-D-<br> . Applies to IN_D and<br>RX_IN signals.                                         |

| T <sub>JIT</sub>         | Jitter added to high-speed<br>signals      |                                                                                                                  |            | 7.4    | ps                                                                                              | Jitter budget for high-<br>speed signals as they<br>pass through the display<br>mux.<br>7.4ps = 0.02 Tbit at<br>2.7Gb/s |

| DDIL                     | Differential Insertion<br>Loss             | $\geq$ -[0.75*(f)+0.5] dB up to<br>1.35 GHz;<br>$\geq$ -[2.2*(f-1.35)+1.5] dB for<br>1.35 GHz < f $\leq$ 2.7 GHz |            | dB     | For example, $\geq$ -1.5 dB<br>at f = 1.35 GHz<br>For example, $\geq$ -4.5 dB<br>at f = 2.7 GHz |                                                                                                                         |

| DDRL                     | Differential Return Loss                   | $\leq$ -14 dB up to 2.7 GHz                                                                                      |            |        | dB                                                                                              |                                                                                                                         |

| DDNEXT                   | Near End Crosstalk                         | -32 dB m                                                                                                         | ax up to 2 | .7 GHz | dB                                                                                              |                                                                                                                         |

## **HPD Input Characteristics**

| Symbol              | Parameter                             | Min | Nom | Max | Units | Comments                                                                                       |

|---------------------|---------------------------------------|-----|-----|-----|-------|------------------------------------------------------------------------------------------------|

| V <sub>IH-HPD</sub> | Input high level                      |     |     | 3.6 | V     | Low-speed input chang-<br>es state on cable plug/<br>unplug.                                   |

| V <sub>IL-HPD</sub> | HPD Input Low Level                   | 0   |     |     |       | V                                                                                              |

| I <sub>IN_HPD</sub> | HPD input leakage cur-<br>rent        |     |     | 10  | uA    | Measured with HPD<br>at VIH-HPD max and<br>VIL-HPD min                                         |

| T <sub>HPD</sub>    | HPD_IN to HPD propa-<br>gation delay. |     |     | 200 | ns    | Time from HPD_IN<br>changing state to HPD<br>changing state. Includes<br>HPD rise/fall time.   |

| T <sub>RF-HPD</sub> | HPD rise/fall time.                   | 1   |     | 20  | ns    | Time required to transi-<br>tion from VOH-HPD to<br>VOL-HPD or from<br>VOL-HPD to VOH-<br>HPD. |

## **Termination Resistors**

| Symbol           | Parameter                      | Min  | Nom  | Max  | Units | Comments                                          |

|------------------|--------------------------------|------|------|------|-------|---------------------------------------------------|

| R <sub>DDC</sub> | DDC Termination Resis-<br>tors | 1.3K | 1.5k | 2.2k |       | Applies to both 3.3V<br>and 5V pull up resistors. |

### Switch Signal Integrity Requirements and Test Procedures for 5.0 Gb/s

Signal integrity requirements for 5.0 Gb/s applications of the switch are specified. Also included are the requirements of the test fixture for switch S-parameter measurements.

### **Signal Integrity Requirements**

The procedures outlined in ANSI Electronics Industry Alliance (EIA) standards documents shall be followed:

• EIA 364-101 – Attenuation Test Procedure for Electrical Connectors, Sockets, Cable Assemblies or Interconnection Systems

• EIA 364-90 – Crosstalk Ratio Test Procedure for Electrical Connectors, Sockets, Cable Assemblies or Interconnection Systems

• EIA 364-108- Impedance, Reflection Coefficient, Return Loss, and VSWR Measured in the Time and Frequency Domain Test Procedure for Electrical Connectors, Sockets, Cable Assemblies or Interconnection Systems

| Parameter                                                                          | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                  | Requirements                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential<br>Insertion Loss<br>(DDIL)                                           | <ul> <li>EIA 364-101</li> <li>The EIA standard shall be used with the following considerations:</li> <li>1. The measured differential S parameter shall be referenced to a 100 ohms differential impedance.</li> <li>2. The test fixture shall meet the test fixture requirement defined in Section 1.12.</li> <li>3. The test fixture effect shall be removed from the measured S parameters. Refer to Note 1.</li> </ul> | $\geq$ -[0.6*(f)+0.5] dB up to 2.5 GHz (for<br>example, $\geq$ -2 dB at f = 2.5 GHz);<br>$\geq$ -[1.2*(f-2.5)+2] dB for 2.5 GHz < f $\leq$ 5<br>GHz (for example, $\geq$ -5 dB at f = 5 GHz);<br>$\geq$ -[1.6*(f-5)+5] dB for 5 GHz < f $\leq$ 7.5<br>GHz (for example, $\geq$ -9 dB at f = 7.5<br>GHz);<br>Refer to Figure 1. |

| Differential<br>Return Loss<br>(DDRL)                                              | <ul> <li>EIA 364-108</li> <li>The EIA standard shall be used with the following considerations:</li> <li>1. The measured differential S parameter shall be referenced to a 100 ohms differential impedance.</li> <li>2. The test fixture shall meet the test fixture requirement in Section 1.12.</li> <li>3. The test fixture effect shall be removed. Refer to Note 1.</li> </ul>                                        | $\leq$ -14 dB up to 2.8 GHz; $\leq$ -8 dB up to 5 GHz; $\leq$ -4 dB up to 7.5 GHz.<br>Refer to Figure 2.                                                                                                                                                                                                                       |

| Intra-pair Skew                                                                    | Intra-pair skew must be achieved by design; measurement not required.                                                                                                                                                                                                                                                                                                                                                      | 5 ps max                                                                                                                                                                                                                                                                                                                       |

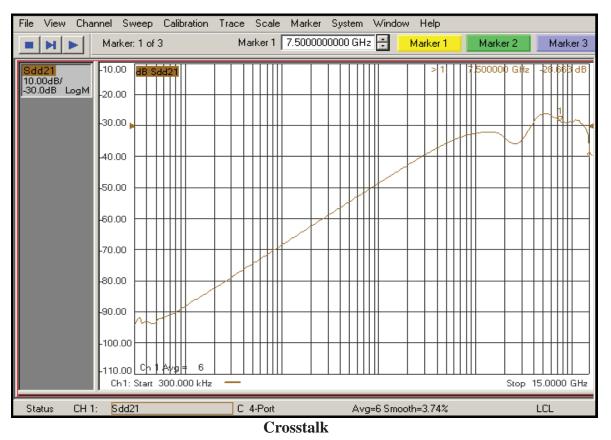

| Differential Near<br>End Crosstalk<br>(DDNEXT)                                     | EIA 364-90<br>The EIA standard must be used with the following considerations:<br>1. The crosstalk requirement is with respect to all the adjacent dif-<br>ferential pairs                                                                                                                                                                                                                                                 | -32 dB max up to 2.5 GHz;<br>-26 dB max up to 5.0 GHz;<br>-20 dB max up to 7.5 GHz;<br>See Figure 3.                                                                                                                                                                                                                           |

| Differential<br>Insertion Loss<br>(DDIL) when<br>switch is turned<br>off<br>Notes: | EIA 364-101                                                                                                                                                                                                                                                                                                                                                                                                                | $\leq$ -20 dB up to 3 GHz;                                                                                                                                                                                                                                                                                                     |

### Signal Integrity Requirements and Test Procedures for 5.0 Gb/s

Notes:

1. The specified S parameters requirements are for switch component only, not including the test fixture effect. While the TRL calibration method is recommended, other calibration methods are allowed.

Figure 1: Illustration of differential insertion loss requirement.

# Figure 3: Illustration of different ial near end crosstalk requirement.

## Switch Test Fixture Requirements

The test fixture for switch S-parameter measurement shall be designed and built to specific requirements, as described below, to ensure good measurement quality and consistency:

- The test fixture shall be a FR4-based PCB of the microstrip structure; the dielectric thickness or stackup shall be about 4 mils.

- The total thickness of the test fixture PCB shall be 1.57 mm (0.62").

- The measurement signals shall be launched into the switch from the top of the test fixture, capturing the through-hole stub effect.

- Traces between the DUT and measurement ports (SMA or microprobe) should be uncoupled from each other, as much as possible. Therefore, the traces should be routed in such a way that traces will diverge from each other exiting from the switch pin field.

- The trace lengths between the DUT and measurement port shall be minimized. The maximum trace length shall not exceed 1000 mils. The trace lengths between the DUT and measurement port shall be equal.

- All of the traces on the test board and add-in card must be held to a characteristic impedance of 50 Ohms with a tolerance of +/- 7%.

- SMA connector is recommended for ease of use. The SMA launch structure shall be designed to minimize the connection discontinuity from SMA to the trace. The impedance range of the SMA seen from a TDR with a 60 ps rise time should be within 50+/-7 ohms.

### PI3PCIE2612-A High Bandwidth, 6-Differential Channel 1:2 DP/PCIe Gen2 Display Mux. ATX Pinout

## Packaging Mechanical: 56-Contact TQFN (ZFE)

### **Ordering Information**

| Ordering Code    | Package Code | Package Description              |

|------------------|--------------|----------------------------------|

| PI3PCIE2612-AZFE | ZF           | Pb-free & Green, 56-contact TQFN |

### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- "E" denotes Pb-free and Green

- Adding an "X" at the end of the ordering code denotes tape and reel packaging

### Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com