# LMP7312

# Precision SPI-Programmable AFE with Differential/Single-Ended Input/Output

## **General Description**

The LMP7312 is a digitally programmable variable gain amplifier/attenuator. Its wide input voltage range and superior precision make it a prime choice for applications requiring high accuracy such as data acquisition systems for IO modules in programmable logic control (PLC). The LMP7312 provides a differential output to maximize dynamic range and signal to noise ratio, thereby reducing the overall system error. It can also be configured to handle single ended input data converters by means of the  $V_{\mbox{\scriptsize OCM}}$  pin (see application section for details). The inputs of LMP7312 can be configured in attenuation mode to handle large input signals of up to +/- 15V, as well as in amplification mode to handle current loops of 0-20mA and 4-20mA. The LMP7312 is equipped with a null switch to evaluate the offset of the internal amplifier. A guaranteed 0.035% maximum gain error (for all gains) and a maximum gain drift of 5ppm over the extended industrial temperature range (-40° to 125°C) make the LMP7312 very attractive for high precision systems even under harsh conditions. A low input offset voltage of 100µV and low voltage noise of 3µVpp give the LMP7312 a superior performance. The LMP7312 is fully specified from -40° to 125°C and is available in SOIC-14 package.

#### **Features**

Typical Values, T<sub>A</sub> = 25°C, V+=5V, V-=0V.

Gain bandwidth 1 MHz Input voltage range (G= 0.096 V/V) -15V to +15V Core op-amp input offset voltage 100 μV (max) Supply current 2 mA (max) Gain (Attenuation Mode) 0.096 V/V, 0.192 V/V 0.384 V/V, 0.768 V/V Gain (AmplificationMode) 1 V/V, 2 V/V Gain Error 0.035% (max) Core op-amp PSRR 90 dB (min) **CMRR** 80 dB (min) 1V to 4V Adjustable output common mode -40 to 125°C Temperature range Package 14-Pin SOIC

### **Applications**

- Signal conditioning AFE ±10V; ±5V; 0-5V; 0-10V; 0-20mA; 4-20mA

- Data Acquisition systems

- Motor control

- Instrument and process control

- Remote sensing

- Programmable automation control

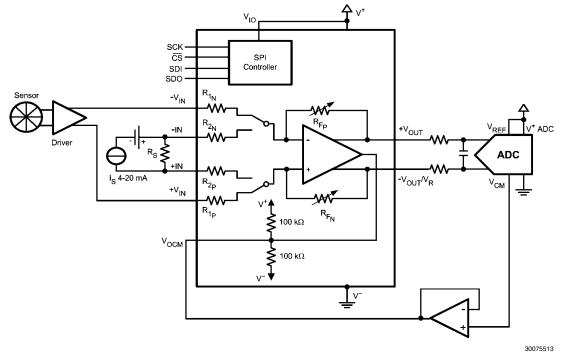

# **Typical Application**

LMP™ is a trademark of National Semiconductor Corporation.

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Rating (Note 2) Human Body Model 2000V Machine Body Model 150V Charge device Model 1000V Analog Supply Voltage  $(V_S = V^+ - V^-)$ 6V Digital Supply Voltage (V<sub>DIO</sub>=V<sub>IO</sub>-V-) 6V Attenuation pins - $V_{IN}$ , + $V_{IN}$  referred to  $V^{-}$ ±17.5V

Amplification pins -IN, +IN referred to V-±10V Voltage at all other pins referred to V-

Storage Temperature Range -65°C to 150°C For soldering specification:

see product folder at www.national.com and www.national.com/ms/MS/MS-SOLDERING.pdf

Junction Temperature

150°C

# **Operating Ratings** (Note 1)

Analog Supply Voltage  $(V_S = V^+ - V^-), V^-$

4.5V to 5.5V

Digital Supply Voltage  $(V_{DIO} = V_{IO} - V^{-})$ ,

V-=0V 2.7V to 5.5V

Attenuation pins -V<sub>IN</sub>, +V<sub>IN</sub> referred to V--15V to 15V Amplification pins -IN, +IN referred to V--2.35V to 7.35V

Temperature Range (Note 3) -40°C to 125°C

Package Thermal Resistance (Note 3)

SOIC-14 145°C/W

# **5V Electrical Characteristics** (Note 4)

Unless otherwise specified, all limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ , G = 0.192 V/V,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2, \ V_{CM\_AMP} = (+IN + (-IN))/2. \ Differential \ output \ configuration. \ SE = Single \ Ended \ Output,$ DE = Differential Output. **Boldface** limits apply at the temperature extremes.

| Symbol                                              | Parameter                                                                                                          | Conditions                                                                                                         |                          | Typ<br>( <i>Note 5</i> ) | Max<br>( <i>Note 6</i> ) | Units            |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------------------|

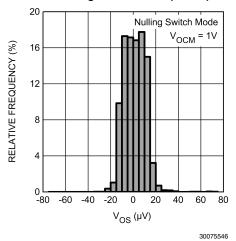

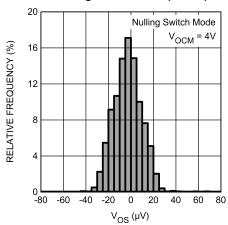

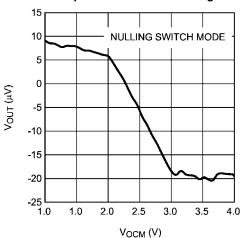

| V <sub>OS</sub>                                     | Core op-amp Input<br>Offset Voltage                                                                                | Nulling Switch Mode, DE, V <sub>OCM</sub> = 1V;<br>Nulling switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 1V | -100<br><b>-250</b>      |                          | 100<br><b>250</b>        | /                |

|                                                     | Nulling Switch Mode, DE, V <sub>OCM</sub> = 4V;<br>Nulling Switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 4V |                                                                                                                    | -100<br><b>-250</b>      |                          | 100<br><b>250</b>        | μV               |

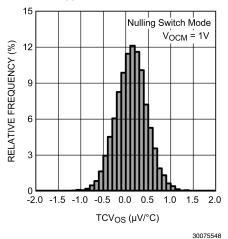

| TCV <sub>OS</sub>                                   | Core op-amp Input<br>Offset Voltage                                                                                | Nulling Switch Mode, DE, V <sub>OCM</sub> = 1V;<br>Nulling Switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 1V | -3                       | ±1.5                     | 3                        |                  |

|                                                     | (Note 7)                                                                                                           | Nulling Switch Mode, DE, V <sub>OCM</sub> = 4V;<br>Nulling Switch Mode, SE, -V <sub>OUT</sub> /V <sub>R</sub> = 4V | -3                       | ±1.5                     | 3                        | μV/°C            |

| Av                                                  | Gain Error                                                                                                         | All gains, $R_L = 10 \text{ k}\Omega$ , $C_L = 50 \text{pF}$ , SE / DE                                             | -0.035<br>- <b>0.045</b> |                          | 0.035<br><b>0.045</b>    | %                |

|                                                     | Gain Drift                                                                                                         | SE / DE                                                                                                            | -5                       | ±1                       | 5                        | ppm/°C           |

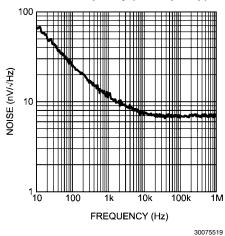

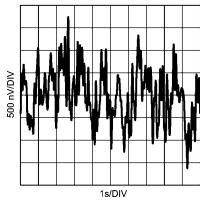

| e <sub>n</sub> Core op-amp Voltage<br>Noise Density |                                                                                                                    | RTI, Nulling Switch Mode, f = 10 kHz                                                                               |                          | 7.25                     |                          | nV/√Hz           |

|                                                     | Core op-amp Peak to<br>Peak Voltage Noise                                                                          | RTI, Nulling Switch Mode, f= 0.1Hz to 10Hz                                                                         |                          | 3                        |                          | μV <sub>PP</sub> |

| I <sub>VA</sub>                                     | Analog Supply Current                                                                                              | $+V_{IN} = -V_{IN} = V_{OCM}$                                                                                      |                          |                          | 2                        | mA               |

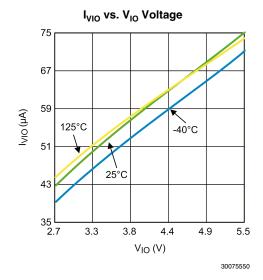

| I <sub>VIO</sub>                                    | Digital Supply Current                                                                                             | Without any load connected to SDO pin                                                                              |                          |                          | 120                      | μΑ               |

| R <sub>IN_CM</sub>                                  | CM Input Resistance                                                                                                | G= 0.192 V/V                                                                                                       |                          | 62.08                    |                          | kΩ               |

|                                                     |                                                                                                                    | G= 1 V/V                                                                                                           |                          | 40                       |                          |                  |

| R <sub>IN_DIFF</sub>                                | Differential Input                                                                                                 | G= 0.192 V/V                                                                                                       |                          | 248.3                    |                          | kΩ               |

|                                                     | Resistance                                                                                                         | G= 1 V/V                                                                                                           |                          | 160                      |                          |                  |

|                                                     |                                                                                                                    | G= 0.096V/V, -15V < V <sub>CM_ATT</sub> < 15V, SE / DE                                                             | _                        |                          |                          |                  |

|                                                     |                                                                                                                    | G= 0.192V/V, -11.4V < V <sub>CM_ATT</sub> < 15V, SE / DE                                                           |                          |                          |                          |                  |

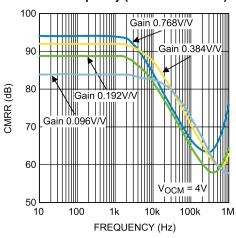

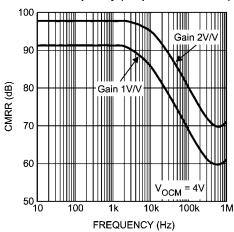

| CMRR                                                | DC Common Mode                                                                                                     | G= 0.384V/V, -6V < V <sub>CM_ATT</sub> < 11V, SE / DE                                                              | 80                       |                          |                          | dB               |

| CIVINN                                              | Rejection Ratio                                                                                                    | G= 0.768V/V, -3V < V <sub>CM_ATT</sub> < 8V, SE / DE                                                               | 77                       |                          |                          | ub               |

|                                                     |                                                                                                                    | G= 1V/V, -2.3V < V <sub>CM_AMP</sub> < 7.3V, SE / DE                                                               |                          |                          |                          |                  |

|                                                     |                                                                                                                    | G= 2V/V, -1.15V < V <sub>CM_AMP</sub> < 6.15V, SE / DE.                                                            |                          |                          |                          |                  |

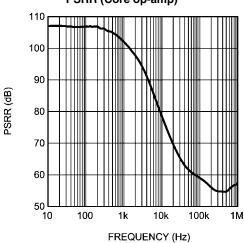

| PSRR                                                | Core op-amp DC<br>Power Supply<br>Rejection Ratio                                                                  | Nulling Switch Mode, 4.5V <v+ <5.5v<="" td=""><td>90</td><td></td><td></td><td>dB</td></v+>                        | 90                       |                          |                          | dB               |

| Symbol              |                                                  |                                                                                                                 | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units  |

|---------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--------|

| V <sub>OCM_OS</sub> | V <sub>OCM</sub> Output Offset ( <i>Note 8</i> ) | V <sub>OCM</sub> = 2.5 V                                                                                        | -20             |                 | 20              | mV     |

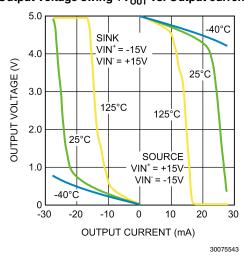

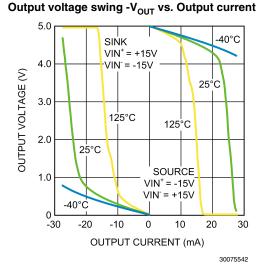

| V <sub>OUT</sub>    | Positive Output<br>Voltage Swing                 | $R_L = 10 \text{ k}\Omega, C_L = 50 \text{ pF},$<br>+ $V_{IN} = 15V, -V_{IN} = -15V$                            |                 |                 | V+-0.2          | V      |

|                     | Negative Output<br>Voltage Swing                 | $R_L$ = 10 kΩ, $C_L$ = 50 pF,<br>+ $V_{IN}$ = -15V, - $V_{IN}$ = 15V                                            | V-+0.2          |                 |                 | V      |

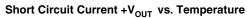

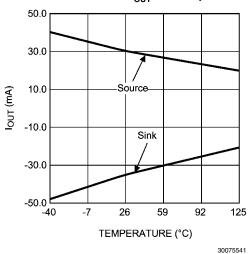

| I <sub>OUT</sub>    | Short circuit current                            | $+V_{IN}$ = $-V_{IN}$ = 2.5V, $+V_{OUT}$ , $-V_{OUT}$ /V <sub>R</sub> connected individually to either V+ or V- | 10              |                 |                 | mA     |

|                     | Current limitation                               | Internal current limiter                                                                                        |                 |                 | 55              |        |

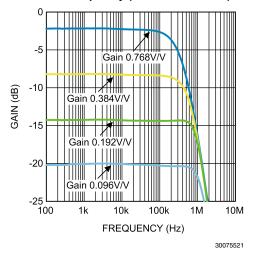

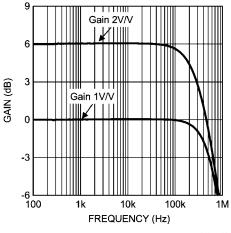

|                     | Bandwidth                                        | Attenuation Mode, G = 0.096 V/V, $R_L$ =10 k $\Omega$ , $C_L$ = 50 pF                                           |                 | 1.2             |                 | MHz    |

|                     |                                                  | Attenuation Mode, G = 0.192 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                          |                 | 1.0             |                 | 171112 |

| ODW                 |                                                  | Attenuation Mode, G = 0.384 V/V, R <sub>L</sub> = 10 k $\Omega$ , C <sub>L</sub> = 50 pF                        |                 | 560             |                 | 1.11_  |

| GBW                 |                                                  | Attenuation Mode, G = 0.768 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                          |                 | 310             |                 | kHz    |

|                     |                                                  | Amplification Mode, G = 1 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                            |                 | 530             |                 | 1.11=  |

|                     |                                                  | Amplification Mode, G = 2 V/V, $R_L$ = 10 k $\Omega$ , $C_L$ = 50 pF                                            |                 | 280             |                 | − kHz  |

| SR                  | Slew Rate                                        | $R_L = 10 \text{ k}\Omega, C_L = 50 \text{ pF}$ 1.4 ( <i>Note 9</i> )                                           |                 |                 | V/µsec          |        |

| THD+N               | Total Harmonic Distorsion + Noise                | Vout = 4.096 Vpp, f = 1KHz, 0.0026 $R_1 = 10 \text{ k}\Omega$                                                   |                 |                 | %               |        |

# Electrical Characteristics (Serial Interface) (Note 4)

Unless otherwise specified. All limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $2.7V < V_{IO} < 5.5V$

| Symbol                         | Parameter                                                       | Conditions               | Min<br>( <i>Note 6</i> ) | Typ<br>( <i>Note 5</i> ) | Max<br>( <i>Note 6</i> ) | Units |

|--------------------------------|-----------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-------|

| VIL                            | Input Logic Low Threshold                                       |                          |                          |                          | 0.8                      | V     |

| VIH                            | Input Logic High Threshold (SDO pin)                            |                          | 2                        |                          |                          | V     |

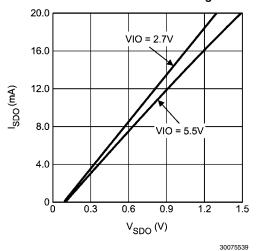

| VOL                            | Output logic Low Threshold (SDO pin)                            | I <sub>SDO</sub> = 100μA |                          |                          | 0.2                      | V     |

|                                |                                                                 | I <sub>SDO</sub> = 2mA   |                          |                          | 0.4                      | V     |

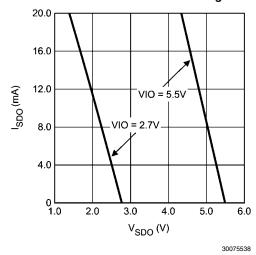

| VOH                            | Output logic High Threshold                                     | I <sub>SDO</sub> = 100μA | V <sub>IO</sub> -0.2     |                          |                          |       |

|                                |                                                                 | I <sub>SDO</sub> = 2mA   | V <sub>IO</sub> -0.6     |                          |                          | V     |

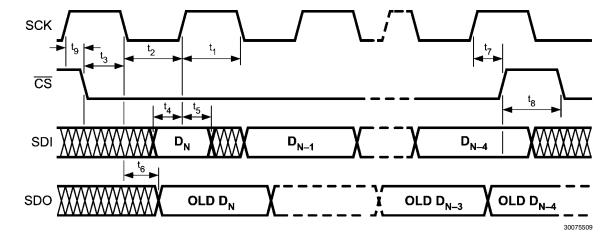

| t <sub>1</sub>                 | High Period, SCK                                                | (Note 10)                | 100                      |                          |                          | ns    |

| t <sub>2</sub>                 | Low Period, SCK                                                 | (Note 10)                | 100                      |                          |                          | ns    |

| t <sub>3</sub>                 | Set Up Time, CS to SCK                                          | (Note 10)                | 50                       |                          |                          | ns    |

|                                | Set Up Time, SDI to SCK                                         | (Note 10)                | 30                       |                          |                          | ns    |

| t <sub>5</sub>                 | Hold Time, SCK to SDI                                           | (Note 10)                | 10                       |                          |                          | ns    |

| t <sub>6</sub>                 | Prop. Delay, SCK to SDO                                         | (Note 10)                |                          |                          | 60                       | ns    |

| t <sub>7</sub>                 | Hold Time, SCK Transition to $\overline{\text{CS}}$ Rising Edge | (Note 10)                | 50                       |                          |                          | ns    |

| t <sub>8</sub>                 | CS Inactive                                                     | (Note 10)                | 100                      |                          |                          | ns    |

| t <sub>9</sub>                 | Hold Time, SCK Transition to CS Falling Edge                    | (Note 10)                | 10                       |                          |                          | ns    |

| t <sub>R</sub> /t <sub>F</sub> | Signal Rise and Fall Times                                      | (Note 10)                | 1.5                      |                          | 5                        | ns    |

3

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but for which specific performance is not guaranteed. For guaranteed specifications and the test conditions, see Electrical Characteristics.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22–A115–A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22–C101–C (ESD FICDM std. of JEDEC).

Note 3: The maximum power dissipation is a function of TJ(max),  $\theta JA$ . The maximum allowable power dissipation at any ambient temperature is:  $PD(max) = (TJ(max) - TA)/\theta JA$ . All numbers apply for packages soldered directly onto a PC Board.

Note 4: Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

Note 5: Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 6: All limits are guaranteed by testing, design, or statistical analysis.

Note 7: Offset voltage temperature drift is determined by dividing the change in V<sub>OS</sub> at the temperature extremes by the total temperature change.

$\textbf{Note 8: } V_{\text{OCM\_OS}} \text{ is the difference between the Output Common mode voltage } (+V_{\text{OUT}} + (-V_{\text{OUT}} / V_{\text{R}}))/2 \text{ and the Voltage on the } V_{\text{OCM}} \text{ pin.} \\$

Note 9: The number specified is the average of rising and falling slew rates and is measured at 90% to 10%.

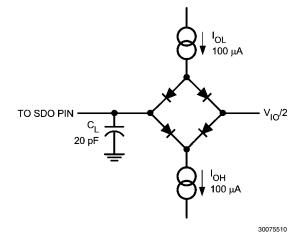

Note 10: Load for these tests is shown in the Test Circuit Diagram.

# **Test Circuit Diagram**

# **Timing Diagram**

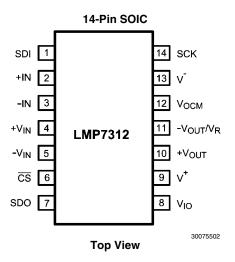

# **Connection Diagram**

# **Pin Descriptions**

| Pin | Name                              | Description                                                                                  |  |

|-----|-----------------------------------|----------------------------------------------------------------------------------------------|--|

| 1   | SDI                               | SPI data IN                                                                                  |  |

| 2   | +IN                               | Non-inverting input of Amplification pair                                                    |  |

| 3   | -IN                               | Inverting input of Amplification pair                                                        |  |

| 4   | +V <sub>IN</sub>                  | Non-inverting input of Attenuation pair                                                      |  |

| 5   | -V <sub>IN</sub>                  | Inverting input of Attenuation pair                                                          |  |

| 6   | CS                                | SPI chip select                                                                              |  |

| 7   | SDO                               | SPI data OUT                                                                                 |  |

| 8   | V <sub>IO</sub>                   | SPI supply voltage                                                                           |  |

| 9   | V+                                | Positive supply voltage                                                                      |  |

| 10  | +V <sub>OUT</sub>                 | Non-inverting output                                                                         |  |

| 11  | -V <sub>OUT</sub> /V <sub>R</sub> | Inverting output in differential output mode, reference input in single-ended operation mode |  |

| 12  | V <sub>OCM</sub>                  | Output common mode voltage in DE                                                             |  |

| 13  | V-                                | Negative supply voltage, reference for both Analog and Digital supplies                      |  |

| 14  | SCK                               | SPI Clock                                                                                    |  |

# **Ordering Information**

| Package      | Part Number | Package Marking | Transport Media          | NSC Drawing |  |

|--------------|-------------|-----------------|--------------------------|-------------|--|

| 14-Pin SOIC  | LMP7312MA   | LMD7010MA       | 95 Units/Rail            | N44 4 A     |  |

| 14-2111 3010 | LMP7312MAX  | LMP7312MA       | 2.5k units Tape and Reel | M14A        |  |

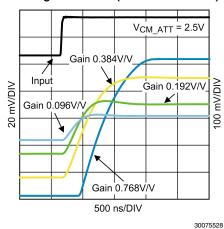

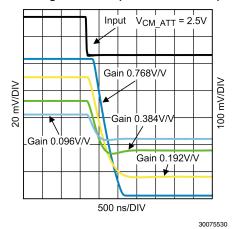

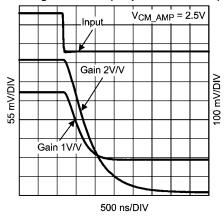

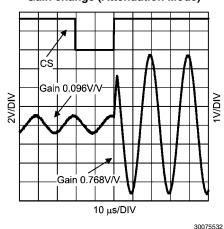

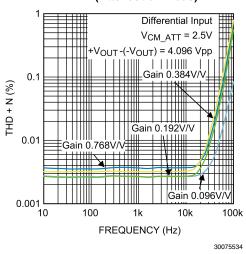

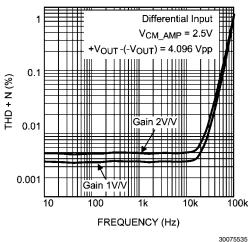

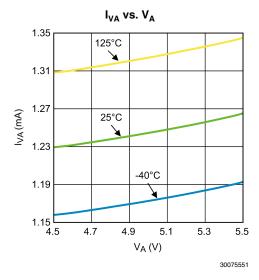

# **Typical Performance Characteristics**

Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V_{IO} = 5V$ ,  $V^- = 0V$ ,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$ ,  $V_{CM\_AMP} = (+IN + (-IN))/2$ .  $R_L = 10k\Omega$ ,  $C_L = 50pF$ , Differential output configuration.

#### Offset Voltage distribution (PMOS)

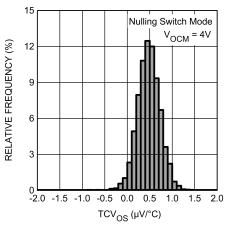

### TCV<sub>OS</sub> distribution (PMOS)

#### Noise vs. Frequency (Core op-amp)

#### Offset Voltage distribution (NMOS)

#### 30075547

### TCV<sub>OS</sub> distribution (NMOS)

#### 30075549

#### 0.1Hz to 10Hz Noise (Core op-amp)

30075520

#### Gain vs. Frequency (Attenuation Mode)

#### CMRR vs. Frequency (Attenuation Mode)

PSRR (Core op-amp)

30075536

30075523

#### Gain vs. Frequency (Amplification Mode)

30075522

### CMRR vs. Frequency (Amplification Mode)

30075537

#### Vos vs. Input Common Mode Voltage

30075545

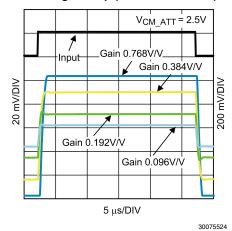

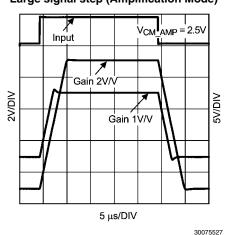

#### Small signal step (Attenuation Mode)

### Small signal step (Amplification Mode)

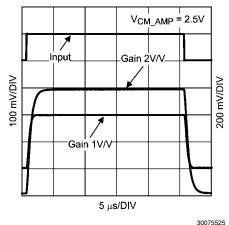

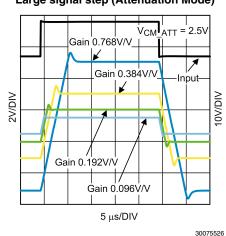

# Large signal step (Attenuation Mode)

### Large signal step (Amplification Mode)

#### **Settling time – Rise (Attenuation Mode)**

#### Settling time - Rise (Amplification Mode)

30075529

#### Settling time - Fall (Attenuation Mode)

#### Settling time - Fall (Amplification Mode)

30075531

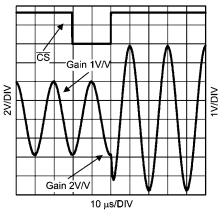

#### Gain change (Attenuation Mode)

#### **Gain change (Amplification Mode)**

30075533

#### THD + N (Attenuation Mode)

### THD + N (Amplification Mode)

30075535

# Output voltage swing $+V_{OUT}$ vs. Output current

#### SDO sink current vs. SDO Voltage

### SDO source current vs. SDO Voltage

www.national.com

12

# **Application Section**

#### **GENERAL DESCRIPTION**

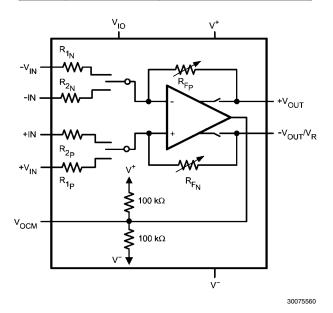

The LMP7312 is a single supply programmable gain difference amplifier with two input pairs: Attenuation pair (- $V_{IN}$ , + $V_{IN}$ ) and Amplification pair (-IN, +IN). The output can be configured in both single-ended and differential modes with the output common mode voltage set by the user. The input selection, the gains and the mode of operation of the LMP7312 are controlled through a 4- wire SPI interface (SCK,  $\overline{CS}$ , SDI, SDO). These features combined make the LMP7312 a very easy interface between the analog high voltage industrial buses and the low voltage digital converters.

#### **OUTPUT MODE CONFIGURATION**

The LMP7312 is able to work in both single ended and differential output mode. The selection of the mode is made through the  $V_{\rm OCM}$  (output common mode voltage) pin.

#### **Differential Output**

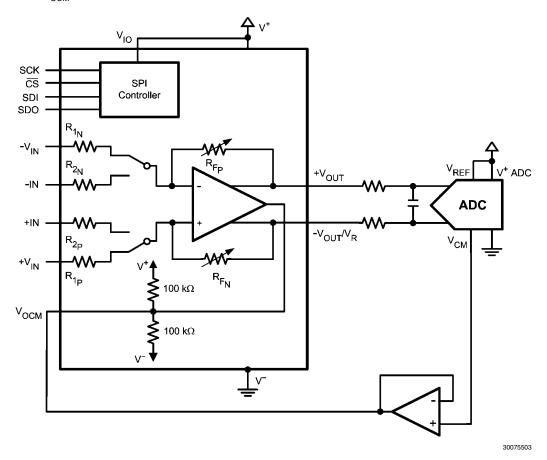

This mode of operation is enabled when the output common mode voltage pin ( $V_{\rm OCM}$ ) is connected to a voltage higher than

1V, for instance the common mode voltage supplied by an ADC, (*Figure 1*) or a voltage reference. If the  $V_{OCM}$  pin is floating an internal voltage divider biases it at the half supply voltage. In this configuration the output signals are set on the  $V_{OCM}$  voltage level.

#### **Single-Ended Output**

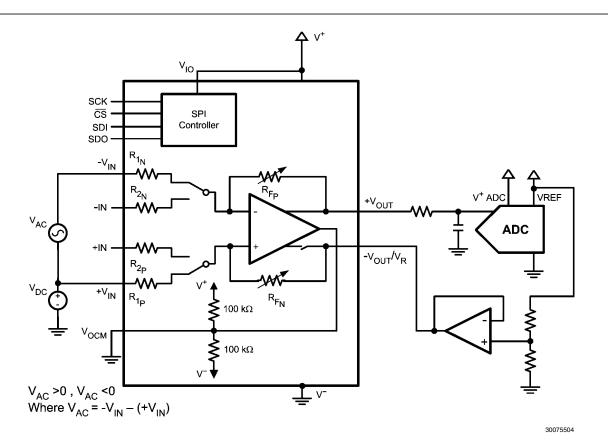

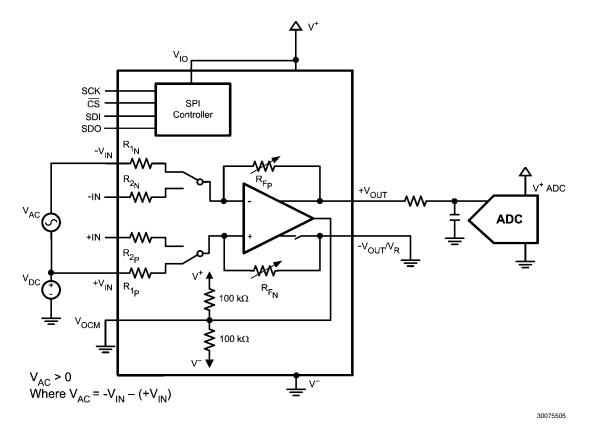

This mode of operation is enabled when the  $V_{\rm OCM}$  pin is tied to a voltage less than 0.5 V, for example to ground. In this mode of operation the LMP7312 behaves as a difference amplifier, where the + $V_{\rm OUT}$  pin is the single-ended output while the - $V_{\rm OUT}$ /V<sub>R</sub> is the reference voltage.

- In the case of bipolar input signal the non inverting output will be connected to an external reference through a buffer (Figure 2).

- 2. In the case of unipolar input signal the non inverting output will be connected to ground (*Figure 3*).

In both cases the inverting output pin is configured as an input pin.

FIGURE 1. Differential ADC Interfacing with  $\rm V_{CM}$  provided by the ADC

FIGURE 2. Bipolar Input Signal to Single-Ended ADC Interface

FIGURE 3. Unipolar Input Signal to Single-Ended ADC Interface

#### **INPUT VOLTAGE RANGE**

The LMP7312 has an internal OpAmp with rail-to-rail input voltage range capability. The requirement to stay within the V- and V+ rail at the OpAmp input translates in an Input Voltage Range specification as explained in this application section.

#### **Differential Output**

Considering a single positive supply (V- = GND, V+ = V<sub>S</sub>) the Input Common mode voltage,  $V_{CM\_ATT} = (+V_{IN} + (-V_{IN}))/2$  for the Attenuation inputs and  $V_{CM\_AMP} = (+I_{IN} + (-I_{IN}))/2$  for the Amplification inputs, has to stay between the MIN and MAX values determined by these formulas:

$$CM_{MAX} = V_S + 1/K_V^*(V_S - V_{OCM})$$

$CM_{MIN} = -1/K_V^*V_{OCM}$

K<sub>v</sub> is a function of the Gain according to the table below:

| Gain           | 0.096 V/<br>V | 0.192 V/<br>V | 0.384 V/<br>V | 0.768 V/<br>V | 1 V/V | 2 V/V |

|----------------|---------------|---------------|---------------|---------------|-------|-------|

| K <sub>V</sub> | 0.12          | 0.218         | 0.414         | 0.806         | 1.065 | 2.096 |

Regardless to the values derived by the formula, the voltage on each input pin must never exceed the specified Absolute Maximum Ratings.

Below are some typical values:

Differential Input, Differential Output,  $V_S = 5V$ ,  $V_{OCM} = 2.5V$

|           | V <sub>CM_ATT</sub> |        | V <sub>CM</sub> | I_AMP  |

|-----------|---------------------|--------|-----------------|--------|

| Gain      | Min                 | Max    | Min             | Max    |

| 0.096 V/V | -15 V*              | +15 V* |                 |        |

| 0.192 V/V | -11.5 V             | +15 V  |                 |        |

| 0.384 V/V | -6 V                | +11 V  |                 |        |

| 0.768 V/V | -3.1 V              | +8.1 V |                 |        |

| 1 V/V     |                     | -      | -2.3 V          | +7.3 V |

| 2 V/V     |                     |        | -1.2 V          | +6.2 V |

<sup>\*</sup> Limited by the operating ratings on input pins

In the case of a single ended input referred to ground (- $V_{IN}$  = GND, -IN = GND) the table below summarizes the voltage range allowed on the + $VI_N$  and + $I_{IN}$  inputs.

Single Ended Input, Differential Output,  $V_S = 5V$ ,  $V_{OCM} = 2.5V$ ,  $-V_{IN} = GND$ ,  $-I_{IN} = GND$

|           | +V <sub>IN</sub> |         | +IN      |          |

|-----------|------------------|---------|----------|----------|

| Gain      | Min              | Max     | Min      | Max      |

| 0.096 V/V | -15 V*           | +15 V*  |          | -        |

| 0.192 V/V | -15 V*           | +15 V*  |          |          |

| 0.384 V/V | -12 V**          | +12 V** |          |          |

| 0.768 V/V | -6 V**           | +6 V**  |          |          |

| 1 V/V     |                  |         | -4.6 V** | +4.6 V** |

| 2 V/V     |                  |         | -2.3 V** | +2.3 V** |

<sup>\*</sup> Limited by the operating ratings on input pins

#### **Single Ended Output**

In this mode the LMP7312 behaves as a Difference Amplifier, with -V $_{\rm OUT}$ /V $_{\rm R}$  being the reference output voltage when a zero volt differential input signal is applied. The voltages at the OpAmp inputs are determined by +V $_{\rm IN}$  and -V $_{\rm OUT}$ /V $_{\rm R}$  voltages. The voltage range of +V $_{\rm IN}$  and +I $_{\rm IN}$  inputs is as follows:

$$V_{MAX} = V_{S} + 1/K_{V} * (V_{S} - (-V_{OUT}/V_{R}))$$

$$V_{MIN} = -1/K_V * (-V_{OUT}/V_R)$$

Regardless of the values derived by the formula, the voltage on each input pin must never exceed the specified Absolute Maximum Ratings.

Below are some typical values:

Differential Input, Single Ended Output,  $V_S = 5V$ ,  $V_{OCM} = GND$ , and  $-V_{OUT}/V_B = 2.5V$

|           | +V <sub>IN</sub> |        | +      | I <sub>IN</sub> |

|-----------|------------------|--------|--------|-----------------|

| Gain      | Min              | Max    | Min    | Max             |

| 0.096 V/V | -15 V*           | +15 V* |        | -               |

| 0.192 V/V | -11.5 V*         | +15 V  |        |                 |

| 0.384 V/V | -6 V             | +11 V  |        |                 |

| 0.768 V/V | -3.1 V           | +8.1 V |        |                 |

| 1 V/V     |                  |        | -2.3 V | +7.3 V          |

| 2 V/V     |                  |        | -1.2 V | +6.2 V          |

<sup>\*</sup> Limited by the operating ratings on input pins

In the case of a single ended input referred to ground (- $V_{IN}$  = GND, -IN = GND) this table summarize the voltage ranges allowed on the + $V_{IN}$  and + $I_{IN}$  inputs.

Single Ended Input, Single Ended Output,  $V_S = 5V$ ,  $V_{OCM} = GND$ ,  $-V_{OLIT}/V_B = 2.5V$ ,  $-V_{IN} = GND$ ,  $-I_{IN} = GND$

|           | +V <sub>IN</sub> |         | +I <sub>IN</sub> |          |

|-----------|------------------|---------|------------------|----------|

| Gain      | Min              | Max     | Min              | Max      |

| 0.096 V/V | -15 V*           | +15 V*  |                  |          |

| 0.192 V/V | -11.5 V          | +12 V** |                  |          |

| 0.384 V/V | -6 V**           | +6 V**  |                  |          |

| 0.768 V/V | -3 V**           | +3 V**  |                  |          |

| 1 V/V     |                  |         | -2.3 V**         | +2.3 V** |

| 2 V/V     |                  |         | -1.1 V**         | +1.1 V** |

<sup>\*</sup> Limited by the operating ratings on input pins

#### **SERIAL INTERFACE CONTROL OPERATION**

The serial interface control of the LMP7312 can be supplied with a voltage between 2.7V and 5.5V through the V<sub>IO</sub> pin for compatibility with different logic families present in the market. The LMP7312 Attenuation, Amplification, Null switch and HiZ modes are controlled by a register. Data to be written into the control register is first loaded into the LMP7312 via the serial interface. The serial interface employs a 5-bit shift register. Data is loaded through the serial data input, SDI. Data passing through the shift register is obtained through the serial data output, SDO. The serial clock, SCK controls the serial loading process. All five data bits are required to correctly program the device. The falling edge of  $\overline{\text{CS}}$  enables the shift register to receive data. The SCK signal must be high during the falling edge of CS. Each data bit is clocked into the shift register on the rising edge of SCK. Data is transferred from the shift register to the holding register on the rising edge of CS. Operation is shown in the timing diagram.

#### **SPI Registers**

| MSB    |        |       |         | LSB  |

|--------|--------|-------|---------|------|

| Gain_1 | Gain_0 | EN_CL | Null_SW | Hi_Z |

<sup>\*\*</sup> Limited by the output voltage swing (0.2V to  $V_S$ -0.2V on both +  $V_{OUT}$  and  $V_{OUT}$ )

<sup>\*\*</sup> Limited by the output voltage swing (0.2V to V<sub>S</sub>-0.2V on +V<sub>OUT</sub>)

Gain\_0, Gain\_1 bit: Gain Values

Different gains are available in Attenuation Mode or Amplification Mode according to the following Gain Table.

| Gain_1 | Gain_0 | EN_CL | Gain Value (V/V) |

|--------|--------|-------|------------------|

| 0      | 0      | 0     | 0.096            |

| 0      | 1      | 0     | 0.192            |

| 1      | 0      | 0     | 0.384            |

| 1      | 1      | 0     | 0.768            |

| 1      | 0      | 1     | 1                |

| 1      | 1      | 1     | 2                |

EN\_CL bit: Enable Amplification Mode

This register selects which input pair is processed.

| EN_CL | Mode                  | Description                                                               |  |  |  |  |

|-------|-----------------------|---------------------------------------------------------------------------|--|--|--|--|

| 0     | Attenuation<br>Mode   | ±V <sub>IN</sub> inputs are processed through the 104.16k input resistors |  |  |  |  |

| 1     | Amplification<br>Mode | ±IN inputs are processed through the 40k input resistors                  |  |  |  |  |

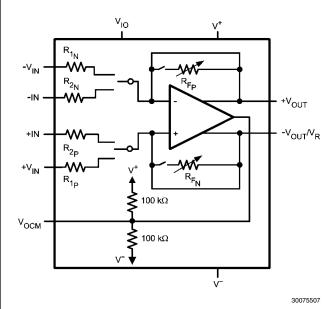

#### NULL\_SW bit: Input Offset Nulling Switch Mode

This register selects a mode in which the amplifier is not processing any input but it is configured in unity gain to allow system level amplifier offset calibration. The Nulling Switch mode is available in both single ended and fully differential output mode. The LMP7312 in Nulling Switch and fully differential mode has he following configuration.

| NULL_SW | Mode           | Description                         |

|---------|----------------|-------------------------------------|

| 0       | Normal         | ±V <sub>IN</sub> and ±IN inputs are |

|         | Operation      | processed depending on              |

|         | Mode           | EN_CL register setting.             |

| 1       | Nulling Switch | Enables to evaluate the offset      |

|         | Mode           | of the internal amplifier for       |

|         |                | system level calibration            |

FIGURE 4. LMP7312 in Nulling Switch Mode

In this condition at the Output pins is possible to measure the input voltage offset of the op-amp:

| Output Mode  | +V <sub>out</sub>                                 | -V <sub>OUT</sub> /V <sub>R</sub> |  |  |

|--------------|---------------------------------------------------|-----------------------------------|--|--|

| Differential | $V_{CM_{out}} + V_{OS}/2$ $V_{CM_{out}} - V_{OS}$ |                                   |  |  |

| Single-Ended | $V_R + V_{OS}$                                    | $V_R$                             |  |  |

#### Hi\_Z bit: High Impedance

In this mode both outputs  $+V_{OUT}$  and  $-V_{OUT}/V_{R}$  of the LMP7312 are in tri-state Figure 5.

| HI_Z | Mode           | Description                   |

|------|----------------|-------------------------------|

| 0    | Normal         | The LMP7312 is configured     |

|      | Operation Mode | according to value of the     |

|      |                | other 4 bits of the register. |

| 1    | High Impedance | The LMP7312 output is in      |

|      | Mode           | high impedance                |

FIGURE 5. LMP7312 in High Impedance Mode

In each case the SPI registers require 5 bits. The table below is a summary of all allowed configurations.

| MSB    |        |       |         | LSB  |                     |                       |

|--------|--------|-------|---------|------|---------------------|-----------------------|

| Gain_1 | Gain_0 | EN_CL | Null_SW | Hi_Z | Gain Value<br>(V/V) | Mode of Operation     |

| 0      | 0      | 0     | 0       | 0    | 0.096               | Attenuation Mode      |

| 0      | 1      | 0     | 0       | 0    | 0.192               | Attenuation Mode      |

| 1      | 0      | 0     | 0       | 0    | 0.384               | Attenuation Mode      |

| 1      | 1      | 0     | 0       | 0    | 0.768               | Attenuation Mode      |

| 1      | 0      | 1     | 0       | 0    | 1                   | Amplification Mode    |

| 1      | 1      | 1     | 0       | 0    | 2                   | Amplification Mode    |

| х      | х      | х     | х       | 1    | _                   | High Impedance Output |

| Х      | х      | х     | 1       | 0    | 1                   | Null Switch Mode      |

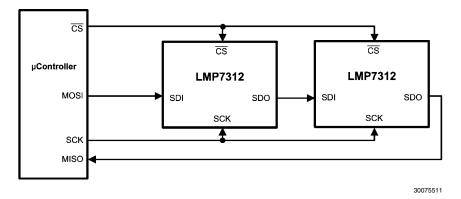

#### **Daisy Chain**

The LMP7312 supports daisy chaining of the serial data stream between multiple chips. To use this feature serial data is clocked into the first chip SDI pin, and the next chip SDI pin is connected to the SDO pin of the first chip. Both chips may share a chip select signal, or the second chip can be enabled

separately. When the chip select pin goes low on both chips and 5 bits have been clocked into the first chip the next 5 clock cycle begins moving new configuration data into the second chip. With a full 10 clock cycles both chips have valid data and the chip select pin of both chips should be brought high to prevent the data from overshooting.

FIGURE 6. Daisy chain

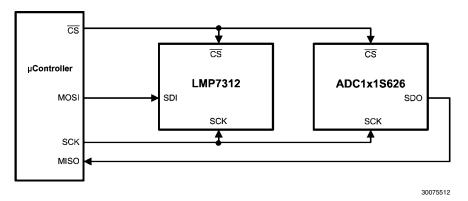

#### **Shared 4-wire SPI with ADC**

The LMP7312 is a good choice when interfacing to differential analog to digital converters ADC141S626 and ADC161S626 of PowerWise® Family. Its SPI interface has been designed to enable sharing CSB with the ADC. LMP7312 register access happens only when CSB is asserted low while SCK is high. However, the ADC starts conversion under any of the following conditions: (1) CSB goes low while SCK is high, (2)

CSB goes low while SCK is low, (3) CSB and SCK both going low. Therefore, if a system uses timing condition #2 above, LMP7312 and ADC1x1S626 can share CSB and SCK as shown in *Figure 7*. The only side-effect would be that writing to LMP7312 triggers an ADC conversion, but then the result can be ignored. At other times, the LMP7312 is not affected by the CSB assertions used to initiate normal ADC conversions.

FIGURE 7. 4-wire SPI with ADC interface

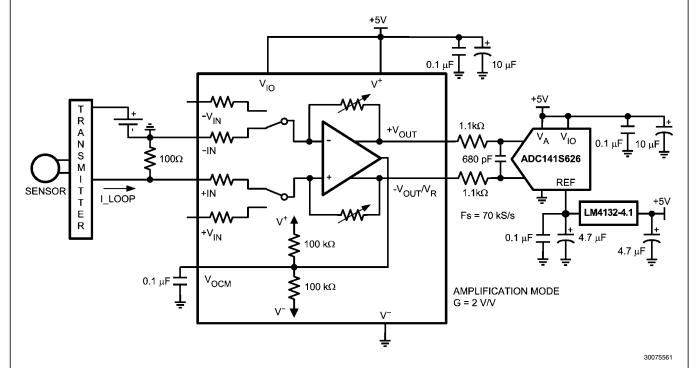

#### LMP7312 IN 4-20mA CURRENT LOOP APPLICATION

The 4-20mA current loop shown in Figure 8 is a common method of transmitting sensor information in many industrial process-monitoring applications. Transmitting sensor information via a current loop is particularly useful when the information has to be sent to a remote location over long distances (1000 feet, or more). The loop's operation is straightforward: a sensor's output voltage is first converted to a proportional current, with 4mA normally representing the sensor's zerolevel output, and 20mA representing the sensor's full-scale output. Then, a receiver at the remote end converts the 4-20mA current back into a voltage which in turn can be further processed by a computer or display module. A typical 4-20mA current-loop circuit is made up of four individual elements: a sensor/transducer; a voltage-to-current converter (commonly referred to as a transmitter and/or signal conditioner); a loop power supply; and a receiver/monitor. In loop powered applications, all four elements are connected in a closed, series circuit, loop configuration (Figure 8). Sensors provide an output voltage whose value represents the physical parameter being measured. The transmitter amplifies and conditions the sensor's output, and then converts this voltage to a proportional 4-20mA dc-current that circulates within the closed series-loop. The loop power-supply generally provides all operating power to the transmitter and receiver, and any other loop components that require a well-regulated dc voltage. In loop-powered applications, the power supply's internal elements also furnish a path for closing the series loop. The receiver/monitor, normally a subsection of a panel meter or data acquisition system, converts the 4-20mA current back into a voltage which can be further processed and/or displayed. The high DC performance of the LMP7312 makes this difference amplifier an ideal choice for use in current loop AFE receiver. The LMP7312 has a low input offset voltage and low input offset voltage drift when configured in amplification mode. In the circuit shown in Figure 8 the LMP7312 is in amplification mode with a gain of 2V/V and differential output in order to well match the input stage of the ADC141S626 (SAR ADC with differential input). The shunt resistor is 100ohm in order to have a max voltage drop of 2V when 20mA flows in the loop. The first order filter between the LMP7312 and the ADC141S626 reduces the noise bandwidth and allows handling input signal up to 2kHz. That frequency has been calculated taking in account the roll off of the filter and ensuring a gain error less than 1LSB of the ADC141S626. In order to utilize the maximum number of bits of the ADC141S626 in this configuration, a 4.1V reference voltage is used. With this system, the current of the 4-20mA loop is accurately gained to the full scale of the ADC and then digitized for further processing.

FIGURE 8. LMP7312 in 4-20mA Current Loop application

18

#### LAYOUT CONSIDERATIONS

#### Power supply bypassing

In order to preserve the gain accuracy of the LMP7312, power supply stability requires particular attention. The LMP7312 guarantees minimum PSRR of 90dB (or 31.62  $\mu V/V$ ). However, the dynamic range, the gain accuracy and the inherent low-noise of the amplifier can be compromised by introducing and amplifying power supply noise. To decouple the LMP7312 from supply line AC noise, a 0.1  $\mu F$  ceramic capacitor should be located on the supply line, close to the

LMP7312. Adding a 10  $\mu$ F tantalum capacitor in parallel with the 0.1  $\mu$ F ceramic capacitor will reduce the noise introduced to the LMP7312 even further by providing an AC path to ground for most frequency ranges.

#### **APPENDIX**

#### Offset Voltage and Offset Voltage Drift calculation

Listed in the table below are the calculated values for Offset Voltage and Offset Voltage Drift based on the max specifications of these parameters for the core op-amp (for all gain configurations).

| Parameter                                      | Unit  |       | Val   |       |       |      |      |

|------------------------------------------------|-------|-------|-------|-------|-------|------|------|

| Gain                                           | V/V   | 0.096 | 0.192 | 0.384 | 0.768 | 1    | 2    |

| Total Offset Input Referred (MAX)              | μV    | ±1141 | ±620  | ±360  | ±230  | ±200 | ±150 |

| Total Offset Output Referred (MAX)             | μV    | ±109  | ±119  | ±138  | ±176  | ±200 | ±300 |

| TCV <sub>OS</sub> Input Referred @ 25°C (MAX)  | μV/°C | ±32.3 | ±18.6 | ±10.8 | ±6.9  | ±6   | ±4.5 |

| TCV <sub>OS</sub> Output Referred @ 25°C (MAX) | μV/°C | ±3.3  | ±3.6  | ±4.1  | ±5.3  | ±6   | ±9   |

#### **Noise calculation**

Listed in the table below are the calculated values for Voltage Noise based on the spectral density of the core op-amp at 10kHz (for all gain configurations).

| Parameter                      | Unit   |       | Va    |       |       |    |    |

|--------------------------------|--------|-------|-------|-------|-------|----|----|

| Gain                           | V/V    | 0.096 | 0.192 | 0.384 | 0.768 | 1  | 2  |

| Total Noise Referred to Input  | nV/√Hz | 211   | 150   | 112   | 89    | 53 | 46 |

| Total Noise Referred to Output | nV/√Hz | 20    | 29    | 43    | 68    | 53 | 92 |

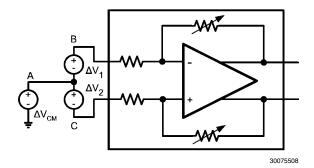

#### Input resistance calculation

The common mode input resistance is the resistance seen from node "A" when  $\Delta V1 = \Delta V2 = 0$  and a common mode voltage  $\Delta VCM$  is applied to both inputs of the LMP7312. The

differential input resistance is the resistance seen from the nodes "B" and "C" when  $\Delta VCM=0$  and a differential voltage  $\Delta V1=\Delta V2=V/2$  is applied to the inputs of the LMP7312.

FIGURE 9. Circuit for Input Resistance calculation

| Mode of Operation  |                         | Unit | Gains     |        |        |        |

|--------------------|-------------------------|------|-----------|--------|--------|--------|

| Attenuation Mode   |                         |      | 0.096     | 0.192  | 0.384  | 0.768  |

|                    | Common Mode Resistance  | kΩ   | 57.08     | 62.08  | 72.08  | 92.08  |

|                    | Differential Resistance | kΩ   | 228.30    | 248.30 | 288.30 | 368.30 |

| Amplification Mode |                         |      | 1 2       |        | 2      |        |

|                    | Common Mode Resistance  | kΩ   | 40.0 60.0 |        | 0.0    |        |

|                    | Differential Resistance | kΩ   | 16        | 0.0    | 24     | 0.0    |

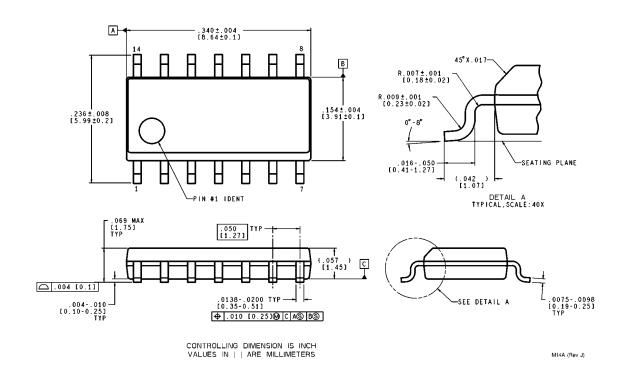

# Physical Dimensions inches (millimeters) unless otherwise noted

14-Pin SOIC NS Package Number M14A

# **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Desi                            | gn Support                     |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com