## QT1100A-ISG 10 Key QTouch™ Sensor IC

- 10 independent touch sensing fields

- 100% autocal for life no adjustments required

- SPI and UART serial interfaces

- Scanport output simulates a membrane keypad

- Simple external per channel passive circuit

- User-defined setups of operating parameters

- 3.3V~5.0V single supply operation

- AKS<sup>™</sup> Adjacent Key Suppression for tight key layouts

- Sleep mode for low power operation

- Spread spectrum modulated bursts superior noise rejection

- Sync pin for superior mains frequency noise rejection

- FMEA compliant design features self detects faults

- Lower per key cost than many mechanical switches

- Lead-free package

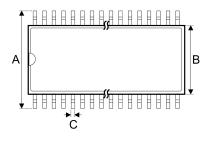

#### Actual Size

#### **APPLICATIONS**

- PC peripherals

- Television controls

- Instrument panels

- Appliance controls

- Pointing devices

- Gaming machines

QT1100A charge-transfer ("QT") QTouch ICs are self-contained digital controllers capable of detecting near-proximity or touch on up to 10 electrodes. This device allows each electrode to project an independent sense field through glass or plastic. These devices require only a few inexpensive passive components per sensing channel. The devices are designed specifically for human interfaces, such as control panels, appliances, gaming devices, lighting controls, or anywhere a mechanical switch may be found.

Each key channel operates independently, and can be tuned to a unique sensitivity level by simply changing setup values in an EEPROM or via a serial interface. An external EEPROM can store the setups permanently for standalone applications, for example when using the scanport, or, the EEPROM can be omitted if the serial port is used to send setup information after each power-up.

Included is patent pending AKS™ Adjacent Key Suppression which suppresses touch from weakly responding keys and allows only a dominant key to detect, to solve the problem of large fingers on tightly spaced keys. Modulated burst technology provides superior noise rejection. 'Fast-DI' operation works to further suppress false activations due to noise.

These devices also have a Sync pin to suppress some forms of external interference. A Sleep mode is also available for very low power standby operation.

The QT1100A is designed specifically to assist in creating FMEA compliant designs, allowing it to be used in applications such as appliance controls.

Using the charge transfer principle, these devices deliver a level of performance which is clearly superior to older technologies yet extremely cost-effective.

#### **AVAILABLE OPTIONS**

| T <sub>A</sub> | SSOP-48     | LEAD-FREE |

|----------------|-------------|-----------|

| -40°C to +85°C | QT1100A-ISG | Yes       |

## **Contents**

| 1 Overview                                    | 3  | 3.5.3 Detect Integrator for Key 'k' - 0x6k        | 19         |

|-----------------------------------------------|----|---------------------------------------------------|------------|

| Table 1.1 Scanport / UART Pinlist             |    | 3.5.4 Status for Key 'k' - 0x8k                   | 19         |

| Table 1.2 Standalone Pinlist                  | 5  |                                                   | 20         |

| Table 1.3 Standalone Pinlist                  | 6  | 3.5.6 Report All Keys - 0xC1                      | 20         |

| Table 1.4 SPI Pinlist                         |    | 3.5.7 Device Status - 0xC2                        |            |

| Table 1.5 Pin Descriptions                    |    | 0.5.0.5555504.05000                               | 20         |

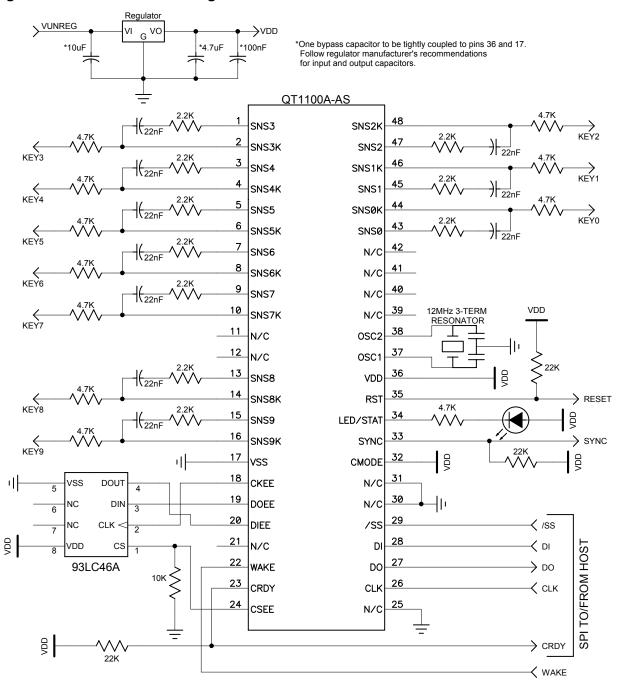

| Figure 1.1 SPI Connection Diagram             |    | 3.5.9 RAM CRC - 0xC4                              | 20         |

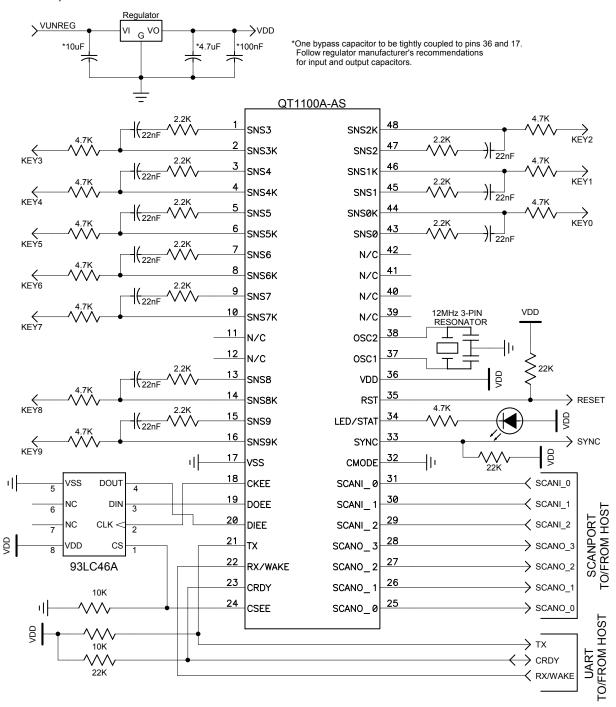

| Figure 1.2 UART / Scanport Connection Diagram |    |                                                   | <u>-</u> 0 |

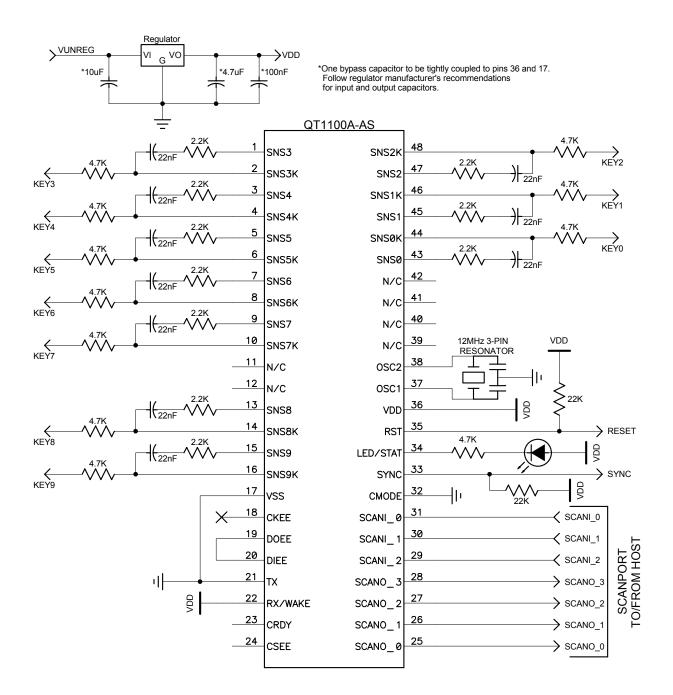

| Figure 1.3 Scanport Only Connection Diagram+  |    | 0.5.44.14                                         | 21         |

| 2 Device Control & Wiring                     |    | 0.5.40 But and out 0.007                          | 21         |

| 2.1 Oscillator                                |    | 0.5.40.0                                          | 21         |

| 2.2 Spread Spectrum Modulation                |    |                                                   | 21         |

| 2.3 Cs Sample Capacitors                      |    | 3.6 Command Sequencing                            |            |

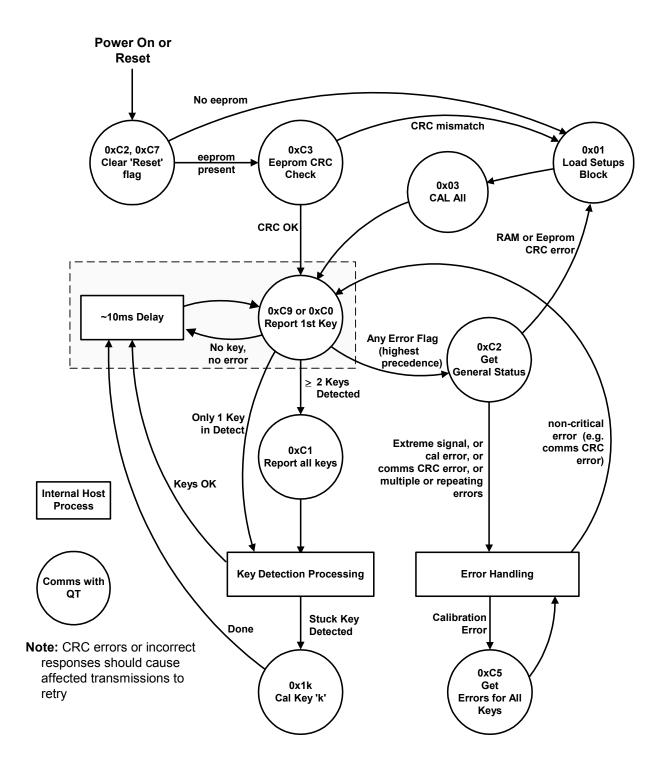

| 2.4 Sensitivity                               |    | Figure 3-1 Suggested Serial Flow                  |            |

| 2.5 Sensitivity Balance                       |    | Table 3-1 Control Commands                        |            |

| 2.6 Power Supply                              |    | T.I. 0.001 / 0                                    | 24         |

| 2.7 PCB Layout and Construction               |    | 4 Setup Block Functions                           | 25         |

| 2.8 ESD Protection                            |    | 4.1 NTHR - Negative Threshold Bits                |            |

| 2.9 Noise Issues                              |    | 4.2 NHYS - Negative Hysteresis Bits               |            |

| 2.9.1 LED Traces and Other Switching Signals  |    | 4.3 NDCR / PDCR - Drift Comp Bits                 |            |

| 2.9.2 External Fields                         |    | 4.4 NRD - Negative Recal Delay Bits               |            |

| 2.10 Start-up Time                            |    | 4.5 PRD - Positive Recal Delay Bits               |            |

| 2.11 Operating Parameter Setups               |    | 4.6 AKS - Adjacent Key Suppression Bits           |            |

| 2.12 Standalone Operation, No EEPROM          |    | 4.7 EK - Error Key Control Bits                   |            |

| 2.13 EEPROM Functionality                     |    | 4.8 K2L / LEDP / KEYO Control Bits                |            |

| 2.14 Scanport Interface                       |    | 4.9 NDIL, FDIL - Detect Integrator Bits           |            |

| 2.15 Start-up Sequencing                      |    | 1.10 DTUD D 33 TI 1.10 D3                         | 21<br>28   |

| 2.16 Error Detection and Reporting            |    |                                                   | 20<br>28   |

| 3 Serial Operation                            |    | 1.10.05.00410.0 1.107                             | 20<br>28   |

| 3.1 UART Interface                            |    | 4.13 LBLL - Lower Burst Length Limit              |            |

| 3.1.1 TX Pin                                  |    | 4.14 BS - Burst Spacing Control Bits              |            |

| 3.1.2 Sleep/Wake Operation in UART Mode       |    | 4.15 BR - Baud Rate Control Bits                  |            |

| 3.1.3 CRDY Operation in UART Mode             |    |                                                   | 29         |

| 3.2 SPI Operation                             |    | Table 4-1 Serial / EEPROM Setups Block            |            |

| 3.2.1 Multi-Drop SPI Capability               |    | 4.17 Timing Tables                                |            |

| 3.2.2 Sleep/Wake Operation in SPI Mode        |    | 5 - Specifications                                |            |

| 3.2.3 CRDY Operation in SPI Mode              |    |                                                   | 36         |

| 3.3 Communication Error Handling              |    | 5.2 Recommended Operating Conditions              |            |

| 3.4 Control Commands                          |    | 5.3 AC Specifications                             |            |

| 3.4.1 Null Command - 0x00                     |    | 5.4 DC Specifications                             |            |

| 3.4.2 Enter Setups Load Mode - 0x01           |    | 5.5 Burst / Sync Timing                           |            |

| 3.4.3 Enter Run Mode - 0x02                   |    | 5.6 SPI Timing Diagram                            |            |

| 3.4.4 Enter Cal Mode - 0x03                   |    | 5.7 QT1100A Timing Parameters - with Fosc = 12MHz |            |

| 3.4.5 Force Reset - 0x04                      |    | 5.8 Current vs Vdd                                |            |

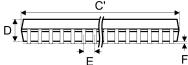

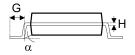

| 3.4.6 Sleep - 0x05                            |    | 5.9 Mechanical                                    |            |

| 3.4.7 Cal Key 'k' - 0x1k                      |    | F 40.44 1.                                        |            |

| 3.5 Status Commands                           |    | 6 Appendix A - 8-Bit CRC C Algorithm              |            |

| 3.5.1 Signal for 1 Key - 0x2k                 |    | TAPPOINT A - 0-Dit Ofto O Algorithm               | 41         |

| 3.5.2 Reference for Key 'k' - 0x4k            |    |                                                   |            |

|                                               | 19 |                                                   |            |

#### 1 Overview

The QT1100A is a 10 touch-key sensor IC based on Quantum's patented charge-transfer principles for robust operation and ease of design. This device has many advanced features which provide for reliable, trouble-free operation over the life of the product. It can operate in either a standalone mode or under host control via a serial interface. Output options include UART and SPI serial types and parallel scanport. In any interface mode, a low-cost optional EEPROM can be used to determine the device configuration using a stored Setup block.

**FMEA self-testing:** This part has been designed specifically for demanding appliance applications requiring FMEA certification. The part has many advanced features that check for and report failures, to allow the designer to create a safer product. It also features two robust serial interfaces with sophisticated CRC error checking to permit validation of commands and responses in real time.

**Burst mode:** The device operates in 'burst mode'. Each key is acquired using a burst of charge-transfer sensing pulses whose count can vary tremendously depending on the value of the reference capacitor Cs and the load capacitance Cx. The keys (also called 'channels') are acquired time sequentially within fixed timeslots whose width can be controlled by user-defined Setups.

**Self-calibration:** On power-up, all keys are self-calibrated within a few hundred milliseconds to provide reliable operation under almost any set of conditions.

**Auto-recalibration**: The device can time out and recalibrate each key independently after a fixed interval of continuous detection, so that the keys can never become 'stuck on' due to foreign objects or sudden influences. After recalibration the key will continue to function normally.

**Drift compensation** operates to correct the reference level of each key slowly but automatically over time, to suppress false detections caused by changes such as temperature, humidity, dirt and other environmental effects.

**Spread Spectrum operation:** The bursts operate over a spread of frequencies, so that external fields will have minimal effect on key operation and emissions are very weak. Spread-spectrum operation works with the 'detect integrator' (DI) mechanism to dramatically reduce the probability of false detection due to noise.

**Detection confirmation** occurs by means of a 'detect integrator' mechanism that requires multiple confirmations of detection over a number of key bursts. The bursts operate at alternating frequencies, so that external fields will have a minimal effect on key operation. This spread-spectrum mode of operation also reduces RF noise emissions.

The device also features the ability to acquire and lock onto touch signals very rapidly, greatly improving response time through the use of the 'fast detect integration' or 'Fast-DI' feature.

**Sync Mode:** The QT1100A features a Sync mode to allow the device to slave to an external signal source, such as a mains signal (50/60Hz), to limit interference effects. This is performed using a special Sync pin.

Low Power Sleep Mode: The device features a low power Sleep mode for microamp levels of current drain when not in use. The part can be put into sleep for a certain percentage of the time, so that it can still respond to touch but with lower levels of current drain.

AKS™ Adjacent Key Suppression works to prevent multiple keys responding to a single touch, a common complaint of capacitive touch panels. This system operates by comparing signal strengths from keys within a defined group to suppress touch detections from those with a weaker signal change than the dominant key. The QT1100A allows any AKS grouping of two or more keys, under user control.

Unique to this device is the ability for the designer to treat each key as an individual sensor for configuration purposes. Each key can be programmed separately for sensitivity, drift compensation, recalibration timeouts, adjacent key suppression, and the like.

The device is designed to support FMEA-qualified applications using a variety of checks and redundancies. Among other checks the component uses CRC codes in all critical communication transfers, and can also output error condition codes via redundant signaling paths.

## **Table 1.1 Scanport / UART Pinlist**

With or without EEPROM; either UART or Scanport or both may be used

| Pin | Name     | Type    | Function     | Notes                                  | If Unused         |

|-----|----------|---------|--------------|----------------------------------------|-------------------|

| 1   | SNS3     | I/O     | Sense pin    | To CS3                                 | Open              |

| 2   | SNS3K    | I/O     | Sense pin    | To CS3 + Key                           | Vss or open       |

| 3   | SNS4     | I/O     | Sense pin    | To CS4                                 | Open              |

| 4   | SNS4K    | I/O     | Sense pin    | To CS4 + Key                           | Vss or open       |

| 5   | SNS5     | I/O     | Sense pin    | To CS5                                 | Open              |

| 6   | SNS5K    | I/O     | Sense pin    | To CS5 + Key                           | Vss or open       |

| 7   | SNS6     | I/O     | Sense pin    | To CS6                                 | Open              |

| 8   | SNS6K    | I/O     | Sense pin    | To CS6 + Key                           | Vss or open       |

| 9   | SNS7     | I/O     | Sense pin    | To CS7                                 | Open              |

| 10  | SNS7K    | I/O     | Sense pin    | To CS7 + Key                           | Vss or open       |

| 11  | n/c      | -       | Unused       | -                                      | =                 |

| 12  | n/c      | -       | Unused       | =                                      | -                 |

| 13  | SNS8     | I/O     | Sense pin    | To CS8                                 | Open              |

| 14  | SNS8K    | I/O     | Sense pin    | To CS8 + Key                           | Vss or open       |

| 15  | SNS9     | I/O     | Sense pin    | To CS9                                 | Open              |

| 16  | SNS9K    | I/O     | Sense pin    | To CS9 + Key                           | Vss or open       |

| 17  | Vss      | Pwr     | Ground       | 0V                                     | -                 |

| 18  | CKEE     | 0       | EEPROM       | Clock to EEPROM                        | Open              |

| 19  | DOEE     | 0       | EEPROM       | Data out to EEPROM                     | Open              |

| 20  | DIEE     | ı       | EEPROM       | Data in from EEPROM                    | Vdd               |

| 21  | TX       | OD      | UART         | Serial to host; If used, use pull-up-R | Vss               |

| 22  | RX/WAKE  | I       | UART, Wakeup | Serial in / Wake from sleep            | Vdd               |

| 23  | CRDY     | I/O, OD | Handshake    | 1 = Comms ready; use pull-up-R         | 10K ~ 220K to Vdd |

| 24  | CSEE     | 0       | EEPROM       | EEPROM chip select; use pull-down-R    | Open              |

| 25  | SCANO_0  | 0       | Scanport out | See Table 2.1                          | Open              |

| 26  | SCANO_1  | 0       | Scanport out | See Table 2.1                          | Open              |

| 27  | SCANO_2  | 0       | Scanport out | See Table 2.1                          | Open              |

| 28  | SCANO_3  | 0       | Scanport out | See Table 2.1                          | Open              |

| 29  | SCANI_2  | I       | Scanport in  | See Table 2.1                          | Vss               |

| 30  | SCANI_1  | I       | Scanport in  | See Table 2.1                          | Vss               |

| 31  | SCANI_0  | I       | Scanport in  | See Table 2.1                          | Vss               |

| 32  | CMODE    |         | Comms select | To Vss                                 |                   |

| 33  | SYNC     | I/O     | Sync in      | Always use pull-up R                   | 20K ~ 220K to Vdd |

| 34  | LED/STAT | 0       | LED & Status | -                                      | Open              |

| 35  | RST      | I       | Reset input  | Active low                             | Vdd               |

| 36  | Vdd      | Pwr     | Power        | +3.3 ~ +5V                             | -                 |

| 37  | OSC1     | I       | Resonator    | 12MHz - Can also be ext clock in       | -                 |

| 38  | OSC2     | 0       | Resonator    | -                                      | Open              |

| 39  | n/c      | -       | Unused       | -                                      | -                 |

| 40  | n/c      | -       | Unused       | -                                      | -                 |

| 41  | n/c      | -       | Unused       | -                                      | -                 |

| 42  | n/c      | -       | Unused       | -                                      | -                 |

| 43  | SNS0     | I/O     | Sense pin    | To CS0 + Key                           | Open              |

| 44  | SNS0K    | I/O     | Sense pin    | To CS0                                 | Vss or open       |

| 45  | SNS1     | I/O     | Sense pin    | To CS1 + Key                           | Open              |

| 46  | SNS1K    | I/O     | Sense pin    | To CS1                                 | Vss or open       |

| 47  | SNS2     | I/O     | Sense pin    | To CS2 + Key                           | Open              |

| 48  | SNS2K    | I/O     | Sense pin    | To CS2                                 | Vss or open       |

I CMOS input I/O CMOS I/O

#### **Table 1.2 Standalone Pinlist**

Scanport, with EEPROM; no serial interface

| Pin                                                                                                                              | Name                                                                                                                                           | Туре                                                                             | Function                                                                                                                                                                                                                                      | Notes                                                                                                                                                                                                  | If Unused                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                | SNS3                                                                                                                                           | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS3                                                                                                                                                                                                 | Open                                                                                                                 |

| 2                                                                                                                                | SNS3K                                                                                                                                          | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS3 + Key                                                                                                                                                                                           | Vss or open                                                                                                          |

| 3                                                                                                                                | SNS4                                                                                                                                           | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS4                                                                                                                                                                                                 | Open                                                                                                                 |

| 4                                                                                                                                | SNS4K                                                                                                                                          | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS4 + Key                                                                                                                                                                                           | Vss or open                                                                                                          |

| 5                                                                                                                                | SNS5                                                                                                                                           | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS5                                                                                                                                                                                                 | Open                                                                                                                 |

| 6                                                                                                                                | SNS5K                                                                                                                                          | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS5 + Key                                                                                                                                                                                           | Vss or open                                                                                                          |

| 7                                                                                                                                | SNS6                                                                                                                                           | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS6                                                                                                                                                                                                 | Open                                                                                                                 |

| 8                                                                                                                                | SNS6K                                                                                                                                          | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS6 + Key                                                                                                                                                                                           | Vss or open                                                                                                          |

| 9                                                                                                                                | SNS7                                                                                                                                           | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS7                                                                                                                                                                                                 | Open                                                                                                                 |

| 10                                                                                                                               | SNS7K                                                                                                                                          | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS7 + Key                                                                                                                                                                                           | Vss or open                                                                                                          |

| 11                                                                                                                               | n/c                                                                                                                                            | -                                                                                | Unused                                                                                                                                                                                                                                        | -                                                                                                                                                                                                      | -                                                                                                                    |

| 12                                                                                                                               | n/c                                                                                                                                            | -                                                                                | Unused                                                                                                                                                                                                                                        | -                                                                                                                                                                                                      | -                                                                                                                    |

| 13                                                                                                                               | SNS8                                                                                                                                           | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS8                                                                                                                                                                                                 | Open                                                                                                                 |

| 14                                                                                                                               | SNS8K                                                                                                                                          | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS8 + Key                                                                                                                                                                                           | Vss or open                                                                                                          |

| 15                                                                                                                               | SNS9                                                                                                                                           | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS9                                                                                                                                                                                                 | Open                                                                                                                 |

| 16                                                                                                                               | SNS9K                                                                                                                                          | I/O                                                                              | Sense pin                                                                                                                                                                                                                                     | To CS9 + Key                                                                                                                                                                                           | Vss or open                                                                                                          |

| 17                                                                                                                               | Vss                                                                                                                                            | Pwr                                                                              | Ground                                                                                                                                                                                                                                        | 0V                                                                                                                                                                                                     | -                                                                                                                    |

| 18                                                                                                                               | CKEE                                                                                                                                           | 0                                                                                | EEPROM                                                                                                                                                                                                                                        | Clock to EEPROM                                                                                                                                                                                        | -                                                                                                                    |

| 19                                                                                                                               | DOEE                                                                                                                                           | 0                                                                                | EEPROM                                                                                                                                                                                                                                        | Data out to EEPROM                                                                                                                                                                                     | -                                                                                                                    |

| 20                                                                                                                               | DIEE                                                                                                                                           | I                                                                                | EEPROM                                                                                                                                                                                                                                        | Data in from EEPROM                                                                                                                                                                                    | -                                                                                                                    |

| 21                                                                                                                               | TX                                                                                                                                             | OD                                                                               | UART                                                                                                                                                                                                                                          | To Vss                                                                                                                                                                                                 | -                                                                                                                    |

| 22                                                                                                                               | RX/WAKE                                                                                                                                        | I                                                                                | UART, Wakeup                                                                                                                                                                                                                                  | To Vdd                                                                                                                                                                                                 | -                                                                                                                    |

| 23                                                                                                                               | CRDY                                                                                                                                           | I/O, OD                                                                          | Handshake                                                                                                                                                                                                                                     | Leave open                                                                                                                                                                                             | -                                                                                                                    |

| 24                                                                                                                               | CSEE                                                                                                                                           | 0                                                                                | EEPROM                                                                                                                                                                                                                                        | EEPROM chip select                                                                                                                                                                                     | -                                                                                                                    |

| 24                                                                                                                               | CSEE                                                                                                                                           | U                                                                                | EEPROW                                                                                                                                                                                                                                        | EEFROW Chip select                                                                                                                                                                                     | -                                                                                                                    |

| 25                                                                                                                               | SCANO 0                                                                                                                                        | 0                                                                                | Scanport out                                                                                                                                                                                                                                  | See Table 2.1                                                                                                                                                                                          | -<br>Open                                                                                                            |

| 25                                                                                                                               |                                                                                                                                                |                                                                                  |                                                                                                                                                                                                                                               |                                                                                                                                                                                                        |                                                                                                                      |

|                                                                                                                                  | SCANO_0                                                                                                                                        | 0                                                                                | Scanport out                                                                                                                                                                                                                                  | See Table 2.1                                                                                                                                                                                          | Open                                                                                                                 |

| 25<br>26                                                                                                                         | SCANO_0<br>SCANO_1                                                                                                                             | 0                                                                                | Scanport out<br>Scanport out                                                                                                                                                                                                                  | See Table 2.1<br>See Table 2.1                                                                                                                                                                         | Open<br>Open                                                                                                         |

| 25<br>26<br>27                                                                                                                   | SCANO_0<br>SCANO_1<br>SCANO_2                                                                                                                  | 0 0                                                                              | Scanport out Scanport out Scanport out                                                                                                                                                                                                        | See Table 2.1 See Table 2.1 See Table 2.1                                                                                                                                                              | Open<br>Open<br>Open                                                                                                 |

| 25<br>26<br>27<br>28                                                                                                             | SCANO_0<br>SCANO_1<br>SCANO_2<br>SCANO_3                                                                                                       | 0<br>0<br>0                                                                      | Scanport out Scanport out Scanport out Scanport out                                                                                                                                                                                           | See Table 2.1 See Table 2.1 See Table 2.1 See Table 2.1                                                                                                                                                | Open<br>Open<br>Open<br>Open                                                                                         |

| 25<br>26<br>27<br>28<br>29                                                                                                       | SCANO_0<br>SCANO_1<br>SCANO_2<br>SCANO_3<br>SCANI_2                                                                                            | 0<br>0<br>0<br>0                                                                 | Scanport out Scanport out Scanport out Scanport out Scanport in                                                                                                                                                                               | See Table 2.1                                                                                                                    | Open Open Open Open Vss                                                                                              |

| 25<br>26<br>27<br>28<br>29<br>30                                                                                                 | SCANO_0<br>SCANO_1<br>SCANO_2<br>SCANO_3<br>SCANI_2<br>SCANI_1                                                                                 | 0<br>0<br>0<br>0                                                                 | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in                                                                                                                                                                   | See Table 2.1 To Vss                                                                                 | Open Open Open Open Vss Vss                                                                                          |

| 25<br>26<br>27<br>28<br>29<br>30<br>31                                                                                           | SCANO_0<br>SCANO_1<br>SCANO_2<br>SCANO_3<br>SCANI_2<br>SCANI_1<br>SCANI_0                                                                      | 0<br>0<br>0<br>0<br>1<br>1                                                       | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in                                                                                                                                                       | See Table 2.1                                                                                        | Open Open Open Open Vss Vss Vss                                                                                      |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32                                                                                     | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT                                                                    | 0<br>0<br>0<br>0<br>1<br>1                                                       | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status                                                                                                                     | See Table 2.1 To Vss                                                                                 | Open Open Open Open Vss Vss Vss -                                                                                    |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33                                                                               | SCANO_0 SCANO_1 SCANO_2 SCANO_2 SCANO_2 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC                                                                     | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1                                             | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in                                                                                                                                  | See Table 2.1 To Vss Always use pull-up R                                                            | Open Open Open Open Vss Vss Vss Vss 20K ~ 220K to Vdd                                                                |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35                                                                   | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd                                                            | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1                                             | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status                                                                                                                     | See Table 2.1 To Vss Always use pull-up R                                                            | Open Open Open Open Vss Vss Vss Open - 20K ~ 220K to Vdd Open Vdd -                                                  |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37                                                       | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1                                                       | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1/0<br>0<br>1<br>Pwr                | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator                                                                                         | See Table 2.1 To Vss Always use pull-up R                                                            | Open Open Open Open Vss Vss Vss Vss Vss Vss Vss Vss Vdd                                                              |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35                                                                   | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd                                                            | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1/0<br>0                            | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power                                                                                                   | See Table 2.1 To Vss Always use pull-up R                                                            | Open Open Open Open Vss Vss Vss Oss - 20K ~ 220K to Vdd Open Vdd -                                                   |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37                                                       | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1                                                       | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1/0<br>0<br>1<br>Pwr                | Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator                                                                                         | See Table 2.1 To Vss Always use pull-up R                                                            | Open Open Open Open Vss Vss Vss Vss Vss - 20K ~ 220K to Vdd Open Vdd                                                 |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40                                     | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c                                          | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1/0<br>0<br>1<br>Pwr<br>1           | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused                                                    | See Table 2.1 To Vss Always use pull-up R - Active low +3.3 ~ +5V  12MHz - Can also be ext clock in  | Open Open Open Open Vss Vss Vss - 20K ~ 220K to Vdd Open Vdd Open                                                    |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40                                     | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c n/c                                      | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1/0<br>0<br>1<br>Pwr<br>1           | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused Unused                                             | See Table 2.1 To Vss Always use pull-up R  Active low +3.3 ~ +5V  12MHz - Can also be ext clock in - | Open Open Open Open Vss Vss Vss  - 20K ~ 220K to Vdd Open Vdd Open                                                   |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41                               | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c n/c                                      | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1/0<br>0<br>1<br>Pwr<br>1<br>0      | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused Unused Unused                                      | See Table 2.1 To Vss Always use pull-up R - Active low +3.3 ~ +5V  12MHz - Can also be ext clock in  | Open                                                                                                                 |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43                   | SCANO_0 SCANO_1 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c n/c n/c SNS0                             | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1/0<br>0<br>1<br>Pwr<br>1<br>0<br>- | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused Unused Unused Sense pin                            | See Table 2.1  To Vss  Always use pull-up R                                                                  | Open                                                                                                                 |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43                   | SCANO_0 SCANO_1 SCANO_2 SCANO_2 SCANO_2 SCANO_2 SCANI_2 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c n/c SNS0 SNS0K                   | O O O O O O O O O O O O O O O O O O O                                            | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused Unused Sense pin Sense pin                         | See Table 2.1  To Vss  Always use pull-up R                                                   | Open                                                                                                                 |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>40<br>41<br>42<br>43<br>44<br>45             | SCANO_0 SCANO_1 SCANO_2 SCANO_2 SCANO_2 SCANO_2 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c n/c n/c SNS0 SNS0K SNS0K | O O O O O O O O O O O O O O O O O O O                                            | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused Unused Unused Sense pin Sense pin                  | See Table 2.1  To Vss  Always use pull-up R                                                   | Open                                                                                                                 |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46 | SCANO_0 SCANO_1 SCANO_2 SCANO_2 SCANO_3 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c n/c sNS0 SNS0K SNS1 SNS1K        | O O O O O O O O O O O O O O O O O O O                                            | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused Unused Unused Unused Sense pin Sense pin Sense pin | See Table 2.1 To Vss Always use pull-up R                                                            | Open Open Open Open Open Vss Vss Vss Vss - 20K ~ 220K to Vdd Open Vdd Open - Open - Open Vssor open Open Vss or open |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>40<br>41<br>42<br>43<br>44<br>45             | SCANO_0 SCANO_1 SCANO_2 SCANO_2 SCANO_2 SCANO_2 SCANI_2 SCANI_1 SCANI_0 CMODE SYNC LED/STAT RST Vdd OSC1 OSC2 n/c n/c n/c n/c SNS0 SNS0K SNS0K | O O O O O O O O O O O O O O O O O O O                                            | Scanport out Scanport out Scanport out Scanport out Scanport out Scanport in Scanport in Scanport in Comms select Sync in LED & Status Reset input Power Resonator Resonator Unused Unused Unused Unused Sense pin Sense pin                  | See Table 2.1  To Vss  Always use pull-up R                                                   | Open                                                                                                                 |

I CMOS input I/O CMOS I/O

#### **Table 1.3 Standalone Pinlist**

Scanport, without EEPROM; no serial interface

| Pin | Name     | Type    | Function     | Notes                            | If Unused         |

|-----|----------|---------|--------------|----------------------------------|-------------------|

| 1   | SNS3     | I/O     | Sense pin    | To CS3                           | Open              |

| 2   | SNS3K    | I/O     | Sense pin    | To CS3 + Key                     | Vss or open       |

| 3   | SNS4     | I/O     | Sense pin    | To CS4                           | Open              |

| 4   | SNS4K    | I/O     | Sense pin    | To CS4 + Key                     | Vss or open       |

| 5   | SNS5     | I/O     | Sense pin    | To CS5                           | Open              |

| 6   | SNS5K    | I/O     | Sense pin    | To CS5 + Key                     | Vss or open       |

| 7   | SNS6     | I/O     | Sense pin    | To CS6                           | Open              |

| 8   | SNS6K    | I/O     | Sense pin    | To CS6 + Key                     | Vss or open       |

| 9   | SNS7     | I/O     | Sense pin    | To CS7                           | Open              |

| 10  | SNS7K    | I/O     | Sense pin    | To CS7 + Key                     | Vss or open       |

| 11  | n/c      | -       | Unused       |                                  | -                 |

| 12  | n/c      | -       | Unused       | •                                | -                 |

| 13  | SNS8     | I/O     | Sense pin    | To CS8                           | Open              |

| 14  | SNS8K    | I/O     | Sense pin    | To CS8 + Key                     | Vss or open       |

| 15  | SNS9     | I/O     | Sense pin    | To CS9                           | Open              |

| 16  | SNS9K    | I/O     | Sense pin    | To CS9 + Key                     | Vss or open       |

| 17  | Vss      | Pwr     | Ground       | 0V                               | -                 |

| 18  | CKEE     | 0       | EEPROM       | Open                             | -                 |

| 19  | DOEE     | 0       | EEPROM       | Connect DOFF, DIFF together      | -                 |

| 20  | DIEE     | I       | EEPROM       | Connect DOEE, DIEE together      | -                 |

| 21  | TX       | OD      | UART         | To Vss                           | -                 |

| 22  | RX/WAKE  | ı       | UART, Wakeup | To Vdd                           | -                 |

| 23  | CRDY     | I/O, OD | Handshake    | Leave open                       | -                 |

| 24  | CSEE     | 0       | EEPROM       | Open                             | -                 |

| 25  | SCANO_0  | 0       | Scanport out | See Table 2.1                    | Open              |

| 26  | SCANO_1  | 0       | Scanport out | See Table 2.1                    | Open              |

| 27  | SCANO_2  | 0       | Scanport out | See Table 2.1                    | Open              |

| 28  | SCANO_3  | 0       | Scanport out | See Table 2.1                    | Open              |

| 29  | SCANI_2  | I       | Scanport in  | See Table 2.1                    | Vss               |

| 30  | SCANI_1  | ı       | Scanport in  | See Table 2.1                    | Vss               |

| 31  | SCANI_0  | I       | Scanport in  | See Table 2.1                    | Vss               |

| 32  | CMODE    |         | Comms select | To Vss                           | -                 |

| 33  | SYNC     | I/O     | Sync in      | Always use pull-up R             | 20K ~ 220K to Vdd |

| 34  | LED/STAT | 0       | LED & Status | ī                                | Open              |

| 35  | RST      |         | Reset input  | Active low                       | Vdd               |

| 36  | Vdd      | Pwr     | Power        | +3.3 ~ +5V                       | -                 |

| 37  | OSC1     | I       | Resonator    | 12MHz - Can also be ext clock in | -                 |

| 38  | OSC2     | 0       | Resonator    | -                                | Open              |

| 39  | n/c      | -       | Unused       | <u>-</u>                         | -                 |

| 40  | n/c      | -       | Unused       | -                                | -                 |

| 41  | n/c      | -       | Unused       | <u>-</u>                         | -                 |

| 42  | n/c      | -       | Unused       | -                                | -                 |

| 43  | SNS0     | I/O     | Sense pin    | To CS0 + Key                     | Open              |

| 44  | SNS0K    | I/O     | Sense pin    | To CS0                           | Vss or open       |

| 45  | SNS1     | I/O     | Sense pin    | To CS1 + Key                     | Open              |

| 46  | SNS1K    | I/O     | Sense pin    | To CS1                           | Vss or open       |

| 47  | SNS2     | I/O     | Sense pin    | To CS2 + Key                     | Open              |

| 48  | SNS2K    | I/O     | Sense pin    | To CS2                           | Vss or open       |

I CMOS input I/O CMOS I/O

## **Table 1.4 SPI Pinlist**

#### With or without EEPROM

| Pin                                                                                    | Name                                                                            | Type | Function                                                                                                                                                         | Notes                                                                                                                                       | If Unused                                                                   |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 1                                                                                      | SNS3                                                                            | I/O  | Sense pin                                                                                                                                                        | To CS3                                                                                                                                      | Open                                                                        |

| 2                                                                                      | SNS3K                                                                           | I/O  | Sense pin                                                                                                                                                        | To CS3 + Key                                                                                                                                | Vss or open                                                                 |

| 3                                                                                      | SNS4                                                                            | I/O  | Sense pin                                                                                                                                                        | To CS4                                                                                                                                      | Open                                                                        |

| 4                                                                                      | SNS4K                                                                           | I/O  | Sense pin                                                                                                                                                        | To CS4 + Key                                                                                                                                | Vss or open                                                                 |

| 5                                                                                      | SNS5                                                                            | I/O  | Sense pin                                                                                                                                                        | To CS5                                                                                                                                      | Open                                                                        |

| 6                                                                                      | SNS5K                                                                           | I/O  | Sense pin                                                                                                                                                        | To CS5 + Key                                                                                                                                | Vss or open                                                                 |

| 7                                                                                      | SNS6                                                                            | I/O  | Sense pin                                                                                                                                                        | To CS6                                                                                                                                      | Open                                                                        |

| 8                                                                                      | SNS6K                                                                           | I/O  | Sense pin                                                                                                                                                        | To CS6 + Key                                                                                                                                | Vss or open                                                                 |

| 9                                                                                      | SNS7                                                                            | I/O  | Sense pin                                                                                                                                                        | To CS7                                                                                                                                      | Open                                                                        |

| 10                                                                                     | SNS7K                                                                           | I/O  | Sense pin                                                                                                                                                        | To CS7 + Key                                                                                                                                | Vss or open                                                                 |

| 11                                                                                     | n/c                                                                             | -    | Unused                                                                                                                                                           | -                                                                                                                                           | -                                                                           |

| 12                                                                                     | n/c                                                                             | -    | Unused                                                                                                                                                           | -                                                                                                                                           | -                                                                           |

| 13                                                                                     | SNS8                                                                            | I/O  | Sense pin                                                                                                                                                        | To CS8                                                                                                                                      | Open                                                                        |

| 14                                                                                     | SNS8K                                                                           | I/O  | Sense pin                                                                                                                                                        | To CS8 + Key                                                                                                                                | Vss or open                                                                 |

| 15                                                                                     | SNS9                                                                            | I/O  | Sense pin                                                                                                                                                        | To CS9                                                                                                                                      | Open                                                                        |

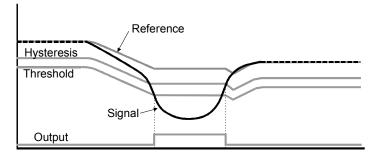

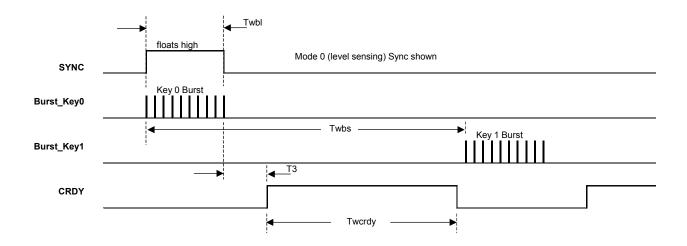

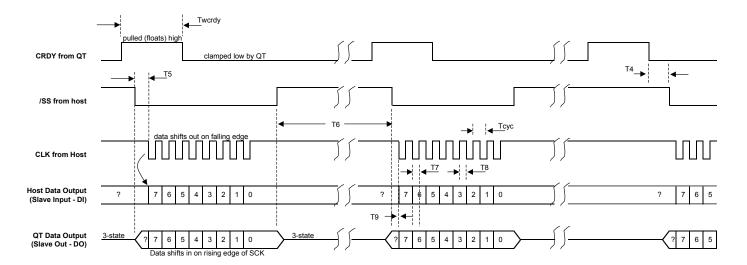

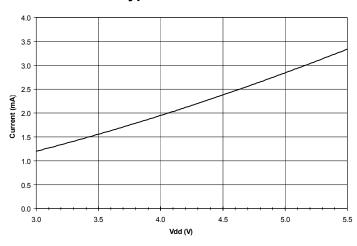

| 16                                                                                     | SNS9K                                                                           | I/O  | Sense pin                                                                                                                                                        | To CS9 + Key                                                                                                                                | Vss or open                                                                 |