### **ADVANCED COMMUNICATIONS & SENSING**

## SX1507B/SX1508B/SX1509B

### World's Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine

### **GENERAL DESCRIPTION**

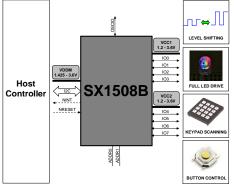

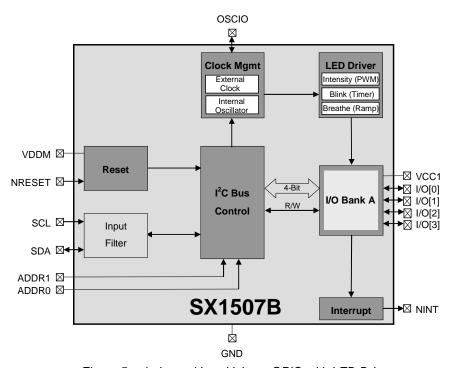

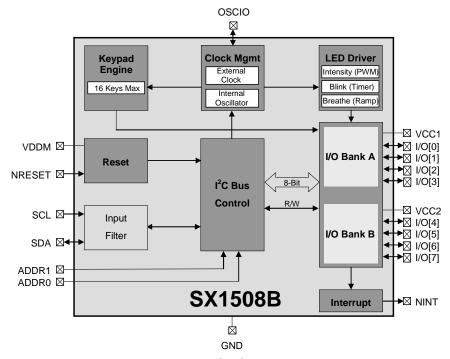

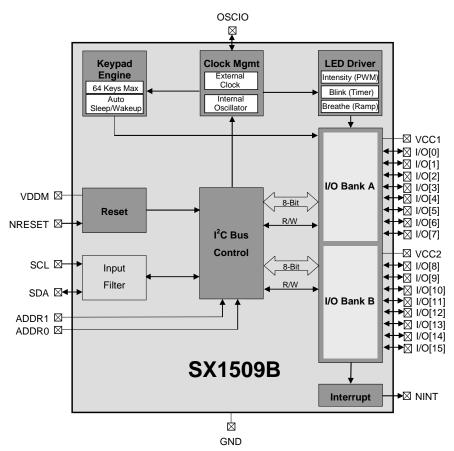

The SX1507B, SX1508B and SX1509B are complete ultra low voltage General Purpose parallel Input/Output (GPIO) expanders ideal for low power handheld battery powered equipment. This family of GPIOs comes in 4-, 8-, 16-channel configuration and allows easy serial expansion of I/O through a standard 400kHz I<sup>2</sup>C interface. GPIO devices can provide additional control and monitoring when the microcontroller or chipset has insufficient I/O ports, or in systems where serial communication and control from a remote location is advantageous.

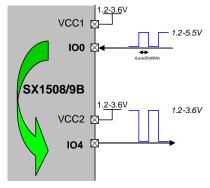

These devices can also act as a level shifter to connect a microcontroller running at one voltage level to a component running at a different voltage level, thus eliminating the need for extra level translating circuits. The core is operating as low as 1.2V (SX1507B) while the dual I/O banks can operate between 1.2V and 5.5V (SX1507B) independent of the core voltage and each other (5.5V tolerant).

The SX1507B, SX1508B and SX1509B feature a fully programmable LED Driver with internal oscillator for enhanced lighting control such as intensity (via 256-step PWM), blinking and breathing (fade in/out) make them highly versatile for a wide range of LED applications.

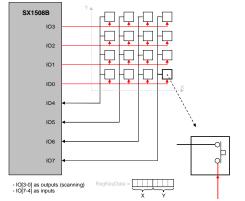

In addition, keypad applications are also supported with an on-chip scanning engine that enables continuous keypad monitoring up to 64 keys without any additional host interaction reducing bus activity.

The SX1507B, SX1508B and SX1509B have the ability to generate mask-programmable interrupts based on a falling/rising edge of any of its GPIO lines. A dedicated pin (NINT) indicates to a host controller that a state change occurred on one or more of the lines. Each GPIO is programmable via a bank of 8-bit configuration registers that include data, direction, pull-up/pull-down, interrupt mask and interrupt registers. These I/O expanders feature small footprint packages and are rated from -40℃ to +85℃ temperature range.

### ORDERING INFORMATION

| Part Number               | I/Os | Package        | Marking |

|---------------------------|------|----------------|---------|

| SX1507BXXX <sup>(1)</sup> | 4    | QFN-UT-14      | ı       |

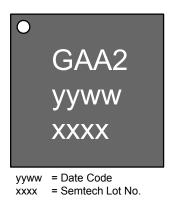

| SX1508BIULTRT             | 8    | QFN-UT-20      | GAA2    |

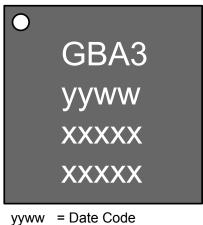

| SX1509BIULTRT             | 16   | QFN-UT-28      | GBA3    |

| SX1508BEVK                | 8    | Evaluation Kit | -       |

| SX1509BEVK                | 16   | Evaluation Kit | ı       |

<sup>(1)</sup> Future product

### **KEY PRODUCT FEATURES**

- 1.2V to 5.5V (SX1507B) Low Operating Voltage with Dual Independent I/O Rails (VCC1, VCC2)

- Enable Direct Level Shifting Between I/O Banks and Host Controller

- 5.5V Tolerant I/Os, Up to 15mA Output Sink on All I/Os (No Total Sink Current Limit)

- Integrated LED Driver for Enhanced Lighting

- Intensity Control (256-step PWM)

- Blink Control (224 On/Off values)

- Breathing Control (224 Fade In/Out values)

- On-Chip Keypad Scanning Engine

- Support Up to 8x8 Matrix (64 Keys)

- Configurable Input Debouncer

- 4/8/16 Channels of True Bi-directional Style I/O

- Programmable Pull-up/Pull-down

- Push/Pull or Open-drain outputs

- Programmable Polarity

- Open Drain Active Low Interrupt Output (NINT)

- Bit Maskable

- Programmable Edge Sensitivity

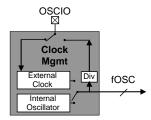

- Built-in Clock Management (Internal 2MHz Oscillator/External Clock Input, 7 clock values)

- OSCIO can be Configured as GPO

- 400kHz I<sup>2</sup>C Compatible Slave Interface

- 4 User-Selectable I<sup>2</sup>C Slave Addresses

- Power-On Reset and Reset Input (NRESET)

- Ultra Low Current Consumption: 1uA Typ

- -40℃ to +85℃ Operating Temperature Range

- Up to 2kV HBM ESD Protection

- Small Footprint Packages

- Pb & Halogen Free, RoHS/WEEE compliant

### **TYPICAL APPLICATIONS**

- · Cell phones, PDAs, MP3 players

- Digital camera, Notebooks, GPS Units

- Any battery powered equipment

# ADVANCED COMMUNICATIONS & SENSING

### **Table of Contents**

| G  | GENERAL DESCRIPTION 1 |                                                                            |                  |  |  |  |  |  |

|----|-----------------------|----------------------------------------------------------------------------|------------------|--|--|--|--|--|

| 0  | RDERING               | INFORMATION                                                                | 1                |  |  |  |  |  |

| Kı | EY PROD               | UCT FEATURES                                                               | 1                |  |  |  |  |  |

| T۱ | PICAL A               | PPLICATIONS                                                                | 1                |  |  |  |  |  |

| 1  | PIN D                 | DESCRIPTION                                                                | 4                |  |  |  |  |  |

|    | 1.1                   | SX1507B 4-channel I <sup>2</sup> C GPIO with LED Driver                    | 4                |  |  |  |  |  |

|    | 1.2                   | SX1508B 8-channel I <sup>2</sup> C GPIO with LED Driver and Keypad Engine  | Ę                |  |  |  |  |  |

|    |                       | SX1509B 16-channel I <sup>2</sup> C GPIO with LED Driver and Keypad Engine | 6                |  |  |  |  |  |

|    | 1.4 I                 | /Os Feature Summary                                                        | 7                |  |  |  |  |  |

| 2  | ELEC                  | CTRICAL CHARACTERISTICS                                                    | 8                |  |  |  |  |  |

|    | 2.1                   | Absolute Maximum Ratings                                                   | 8                |  |  |  |  |  |

|    | 2.2                   | Electrical Specifications                                                  | 8                |  |  |  |  |  |

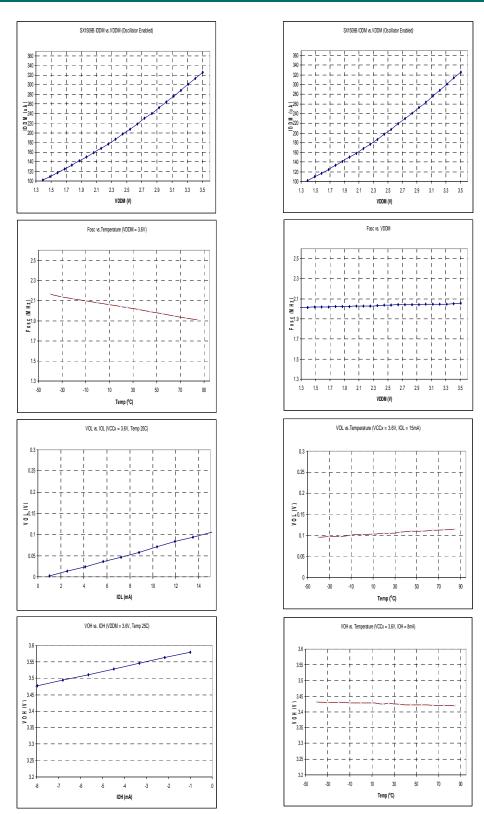

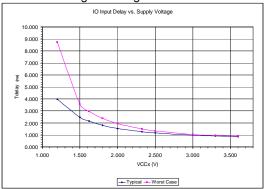

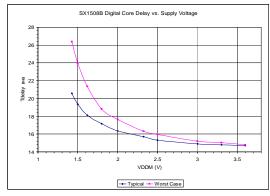

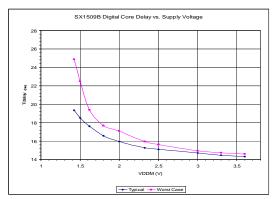

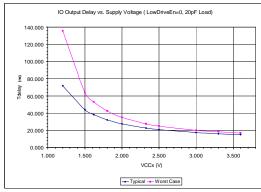

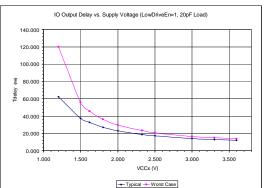

| 3  | TYPI                  | CAL OPERATING CHARACTERISTICS                                              | 11               |  |  |  |  |  |

| 4  | BLO                   | CK DETAILED DESCRIPTION                                                    | 12               |  |  |  |  |  |

|    | 4.1                   | SX1507B 4-channel I <sup>2</sup> C GPIO with LED Driver                    | 12               |  |  |  |  |  |

|    |                       | SX1508B 8-channel I <sup>2</sup> C GPIO with LED Driver and Keypad Engine  | 12               |  |  |  |  |  |

|    |                       | SX1509B 16-channel I <sup>2</sup> C GPIO with LED Driver and Keypad Engine | 13               |  |  |  |  |  |

|    | 4.4 F                 | Reset                                                                      | 13               |  |  |  |  |  |

|    | 4.4.1<br>4.4.2        | Hardware (NRESET)<br>Software (RegReset)                                   | 13<br>14         |  |  |  |  |  |

|    |                       | 2-Wire Interface (I <sup>2</sup> C)                                        | 14               |  |  |  |  |  |

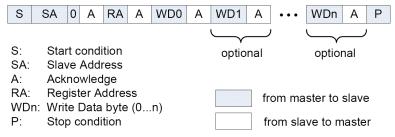

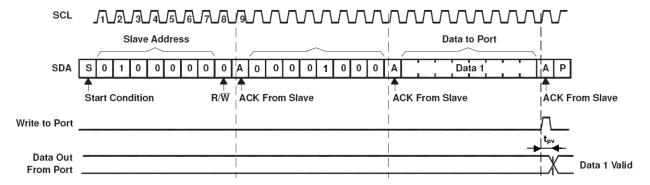

|    | 4.5.1                 | WRITE                                                                      | 14               |  |  |  |  |  |

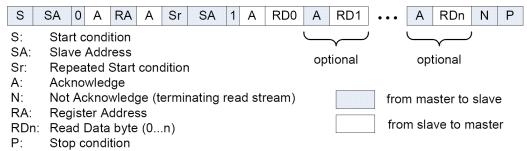

|    | 4.5.2                 | READ                                                                       | 15               |  |  |  |  |  |

|    | <b>4.6 I</b> 4.6.1    | /O Banks Input Debouncer                                                   | <b>15</b><br>15  |  |  |  |  |  |

|    | 4.6.2                 | Keypad Scanning Engine                                                     | 15               |  |  |  |  |  |

|    | 4.6.3                 | Level Shifter                                                              | 16               |  |  |  |  |  |

|    | 4.6.4                 | Polarity Inverter nterrupt (NINT)                                          | 17<br><b>1</b> 7 |  |  |  |  |  |

|    |                       | Clock Management                                                           | 18               |  |  |  |  |  |

|    |                       | LED Driver                                                                 | 18               |  |  |  |  |  |

|    | 4.9.1                 | Overview                                                                   | 18               |  |  |  |  |  |

|    | 4.9.2<br>4.9.3        | Static Mode<br>Single Shot Mode                                            | 19<br>19         |  |  |  |  |  |

|    | 4.9.4                 | Blink Mode                                                                 | 20               |  |  |  |  |  |

|    | 4.9.5                 | LED Driver Modes                                                           | 20               |  |  |  |  |  |

|    | 4.9.6<br>4.9.7        | Synchronization of LED Drivers across several ICs Tutorial                 | 21<br>21         |  |  |  |  |  |

| 5  | CON                   | FIGURATION REGISTERS                                                       | 23               |  |  |  |  |  |

|    |                       | SX1507B 4-channel GPIO with LED Driver                                     | 23               |  |  |  |  |  |

|    |                       | SX1508B 8-channel GPIO with LED Driver and Keypad Engine                   | 26               |  |  |  |  |  |

|    |                       | SX1509B 16-channel GPIO with LED Driver and Keypad Engine                  | 30               |  |  |  |  |  |

| 6  | APPL                  | ICATION INFORMATION                                                        | 36               |  |  |  |  |  |

|    | 6.1                   | Typical Application Circuit                                                | 36               |  |  |  |  |  |

|    |                       | Typical LED Connection                                                     | 36               |  |  |  |  |  |

|    |                       |                                                                            |                  |  |  |  |  |  |

World's Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine

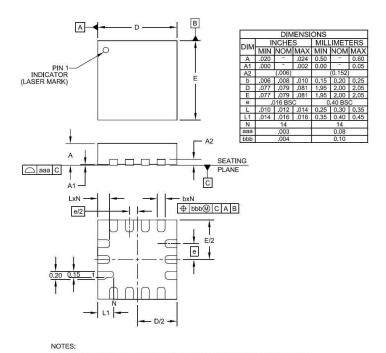

| 7 |     | PACKAGING INFORMATION         | 37 |

|---|-----|-------------------------------|----|

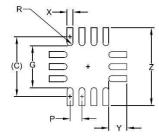

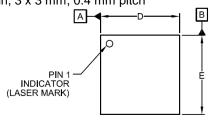

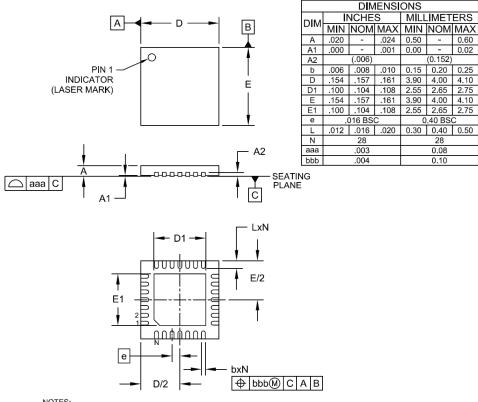

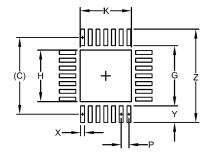

|   | 7.1 | QFN-UT 14-pin Outline Drawing | 37 |

|   | 7.2 | QFN-UT 14-pin Land Pattern    | 37 |

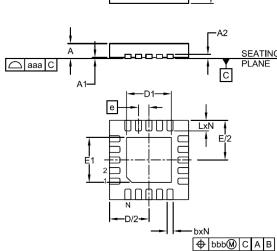

|   | 7.3 | QFN-UT 20-pin Outline Drawing | 38 |

|   | 7.4 | QFN-UT 20-pin Land Pattern    | 38 |

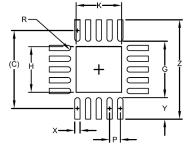

|   | 7.5 | QFN-UT 28-pin Outline Drawing | 39 |

|   | 7.6 | QFN-UT 28-pin Land Pattern    | 39 |

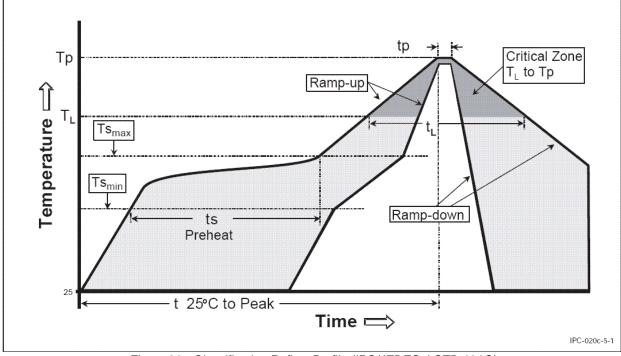

| 8 |     | SOLDERING PROFILE             | 40 |

| 9 |     | MARKING INFORMATION           | 41 |

## ADVANCED COMMUNICATIONS & SENSING

### **PIN DESCRIPTION**

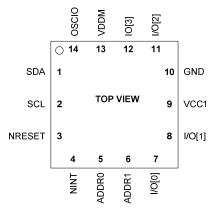

#### SX1507B 4-channel I2C GPIO with LED Driver 1.1

| Pin | Symbol | Type     | Description                                                                                                        |

|-----|--------|----------|--------------------------------------------------------------------------------------------------------------------|

| 1   | SDA    | DIO      | I <sup>2</sup> C serial data line                                                                                  |

| 2   | SCL    | DI       | I <sup>2</sup> C serial clock line                                                                                 |

| 3   | NRESET | DI       | Active low reset input                                                                                             |

| 4   | NINT   | DO       | Active low interrupt output                                                                                        |

| 5   | ADDR0  | DI       | Address input bit 0, connect to VDDM or GND                                                                        |

| 6   | ADDR1  | DI       | Address input bit 1, connect to VDDM or GND                                                                        |

| 7   | I/O[0] | DIO (*1) | I/O[0], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking                       |

| 8   | I/O[1] | DIO (*1) | I/O[1], at power-on configured as an input LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out) |

| 9   | VCC1   | Р        | I/O supply voltage                                                                                                 |

| 10  | GND    | Р        | Ground Pin                                                                                                         |

| 11  | I/O[2] | DIO (*1) | I/O[2], at power-on configured as an input LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out) |

| 12  | I/O[3] | DIO (*1) | I/O[3], at power-on configured as an input LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out) |

| 14  | OSCIO  | DIO (*1) | Oscillator input/output, can also be used as GPO                                                                   |

| 13  | VDDM   | Р        | Main supply voltage                                                                                                |

Table 1 - SX1507B Pin Description

Figure 1 - SX1507B QFN-UT-14 Pinout

D/I/O/P: Digital/Input/Output/Power

(\*1) This pin is programmable through the I<sup>2</sup>C interface

## ADVANCED COMMUNICATIONS & SENSING

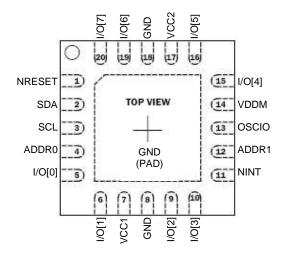

#### SX1508B 8-channel I<sup>2</sup>C GPIO with LED Driver and Keypad Engine 1.2

| Pin | Symbol | Type                | Description                                                                                                           |  |  |

|-----|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | NRESET | DI                  | Active low reset input                                                                                                |  |  |

| 2   | SDA    | DIO                 | I <sup>2</sup> C serial data line                                                                                     |  |  |

| 3   | SCL    | DI                  | I <sup>2</sup> C serial clock line                                                                                    |  |  |

| 4   | ADDR0  | DI                  | Address input bit 0, connect to VDDM or GND                                                                           |  |  |

| 5   | I/O[0] | DIO (*1)            | I/O[0], at power-on configured as an input<br>LED driver : Intensity control (PWM)                                    |  |  |

| 6   | I/O[1] | DIO (*1)            | I/O[1], at power-on configured as an input<br>LED driver : Intensity control (PWM)                                    |  |  |

| 7   | VCC1   | Р                   | Supply voltage for Bank A I/O[3-0]                                                                                    |  |  |

| 8   | GND    | Р                   | Ground Pin                                                                                                            |  |  |

| 9   | I/O[2] | DIO (*1)            | I/O[2], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking                          |  |  |

| 10  | I/O[3] | DIO (*1)            | I/O[3], at power-on configured as an input LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out)    |  |  |

| 11  | NINT   | DO                  | Active low interrupt output                                                                                           |  |  |

| 12  | ADDR1  | DI                  | Address input bit 1, connect to VDDM or GND                                                                           |  |  |

| 13  | OSCIO  | DIO (*1)            | Oscillator input/output, can also be used as GPO                                                                      |  |  |

| 14  | VDDM   | Р                   | Main supply voltage                                                                                                   |  |  |

| 15  | I/O[4] | DIO <sup>(*1)</sup> | I/O[4], at power-on configured as an input<br>LED driver : Intensity control (PWM)                                    |  |  |

| 16  | I/O[5] | DIO <sup>(*1)</sup> | I/O[5], at power-on configured as an input<br>LED driver : Intensity control (PWM)                                    |  |  |

| 17  | VCC2   | Р                   | Supply voltage for Bank B I/O[7-4]                                                                                    |  |  |

| 18  | GND    | Р                   | Ground Pin                                                                                                            |  |  |

| 19  | I/O[6] | DIO <sup>(*1)</sup> | I/O[6], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking                          |  |  |

| 20  | I/O[7] | DIO <sup>(*1)</sup> | I/O[7], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out) |  |  |

Table 2 - SX1508B Pin Description

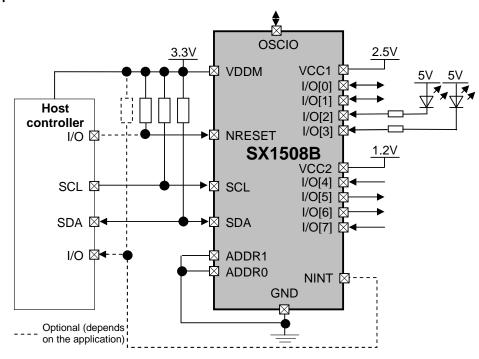

Figure 2 - SX1508B QFN-UT-20 Pinout

D/I/O/P: Digital/Input/Output/Power

(\*1) This pin is programmable through the I<sup>2</sup>C interface

## ADVANCED COMMUNICATIONS & SENSING

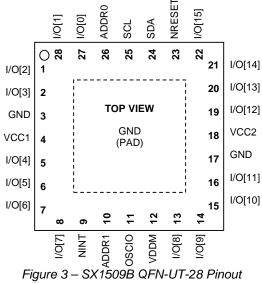

#### SX1509B 16-channel I<sup>2</sup>C GPIO with LED Driver and Keypad Engine 1.3

| Pin | Symbol  | Туре                | Description                                                                                                            |  |

|-----|---------|---------------------|------------------------------------------------------------------------------------------------------------------------|--|

| 1   | I/O[2]  | DIO (*1)            | I/O[2], at power-on configured as an input                                                                             |  |

|     | 1/0[2]  |                     | LED driver : Intensity control (PWM), Blinking                                                                         |  |

| 2   | I/O[3]  | DIO (*1)            | I/O[3], at power-on configured as an input                                                                             |  |

|     |         |                     | LED driver : Intensity control (PWM), Blinking                                                                         |  |

| 3   | GND     | P<br>P              | Ground Pin                                                                                                             |  |

| 4   | VCC1    |                     | Supply voltage for Bank A I/O[7-0]                                                                                     |  |

| 5   | I/O[4]  | DIO <sup>(*1)</sup> | I/O[4], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out)  |  |

| 6   | I/O[5]  | DIO <sup>(*1)</sup> | I/O[5], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out)  |  |

| 7   | I/O[6]  | DIO (*1)            | I/O[6], at power-on configured as an input LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out)     |  |

|     | 1/0/-1  | DIO (*1)            | I/O[7], at power-on configured as an input                                                                             |  |

| 8   | I/O[7]  | DIO                 | LED driver: Intensity control (PWM), Blinking, Breathing (Fade In/Out)                                                 |  |

| 9   | NINT    | DO                  | Active low interrupt output                                                                                            |  |

| 10  | ADDR1   | DI                  | Address input bit 1, connect to VDDM or GND                                                                            |  |

| 11  | OSCIO   | DIO (^1)            | Oscillator input/output, can also be used as GPO                                                                       |  |

| 12  | VDDM    | Р                   | Main supply voltage                                                                                                    |  |

| 13  | I/O[8]  | DIO (*1)            | I/O[8], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking                           |  |

| 14  | I/O[9]  | DIO (*1)            | I/O[9], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking                           |  |

|     |         | (*1)                | I/O[10], at power-on configured as an input                                                                            |  |

| 15  | I/O[10] | DIO <sup>(*1)</sup> | LED driver: Intensity control (PWM), Blinking                                                                          |  |

| 16  | I/O[11] | DIO (*1)            | I/O[11], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking                          |  |

| 17  | GND     | Р                   | Ground Pin                                                                                                             |  |

| 18  | VCC2    | Р                   | Supply voltage for Bank B I/O[15-8]                                                                                    |  |

| 19  | I/O[12] | DIO (*1)            | I/O[12], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out) |  |

| 20  | I/O[13] | DIO (*1)            | I/O[13], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out) |  |

| 21  | I/O[14] | DIO (*1)            | I/O[14], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking, Breathing (Fade In/Out) |  |

| 22  | I/O[15] | DIO (*1)            | I/O[15], at power-on configured as an input LED driver: Intensity control (PWM), Blinking, Breathing (Fade In/Out)     |  |

| 23  | NRESET  | DI                  | Active low reset input                                                                                                 |  |

| 24  | SDA     | DIO                 | I <sup>2</sup> C serial data line                                                                                      |  |

| 25  | SCL     | DI                  | 1 <sup>2</sup> C serial clock line                                                                                     |  |

| 26  | ADDR0   | DI                  | Address input bit 0, connect to VDDM or GND                                                                            |  |

|     |         | DIO (*1)            | I/O[0], at power-on configured as an input                                                                             |  |

| 27  | I/O[0]  | טוט ייי             | LED driver : Intensity control (PWM), Blinking                                                                         |  |

| 28  | I/O[1]  | DIO <sup>(*1)</sup> | I/O[1], at power-on configured as an input<br>LED driver : Intensity control (PWM), Blinking                           |  |

<sup>(\*1)</sup> This pin is programmable through the I<sup>2</sup>C interface

### Table 3 - SX1509B Pin Description

World's Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine

# ADVANCED COMMUNICATIONS & SENSING

### 1.4 I/Os Feature Summary

|     | 5            | X1507E   | 3        |           | S        | X1508B       |              |          |              | S        | X1509B   |          |           |

|-----|--------------|----------|----------|-----------|----------|--------------|--------------|----------|--------------|----------|----------|----------|-----------|

| I/O | LI           | ED Drive | er       | LE        | D Driv   | /er          | Key          | pad      | LE           | D Driv   | ⁄er      | Key      | /pad      |

|     | PWM          | Blink    | Breathe  | PWM       | Blink    | Breathe      | Row          | Col.     | PWM          | Blink    | Breathe  | Row      | Col.      |

| 0   | $\checkmark$ | <b>√</b> |          | $\sqrt{}$ |          |              | <b>√</b>     |          | $\checkmark$ |          |          | <b>√</b> |           |

| 1   | $\checkmark$ |          | <b>√</b> |           |          |              | $\checkmark$ |          |              | <b>√</b> |          |          |           |

| 2   |              | <b>V</b> | <b>V</b> | V         | <b>√</b> |              | <b>V</b>     |          |              | V        |          | V        |           |

| 3   |              | V        | V        | V         | V        |              | <b>V</b>     |          | V            | V        |          | V        |           |

| 4   |              |          |          | V         |          |              |              | V        | V            | V        | <b>√</b> | V        |           |

| 5   |              |          |          | V         |          |              |              | V        | V            | V        | <b>V</b> | V        |           |

| 6   |              |          |          | <b>V</b>  | <b>√</b> |              |              | <b>√</b> | <b>V</b>     | <b>V</b> | <b>V</b> | <b>V</b> |           |

| 7   |              |          |          | <b>V</b>  | <b>√</b> | $\checkmark$ |              | <b>√</b> | <b>V</b>     | <b>V</b> | <b>V</b> | <b>V</b> |           |

| 8   |              |          |          |           |          |              |              |          | V            | V        |          |          | V         |

| 9   |              |          |          |           |          |              |              |          | V            | V        |          |          | V         |

| 10  |              |          |          |           |          |              |              |          | V            | V        |          |          | V         |

| 11  |              |          |          |           |          |              |              |          | V            | V        |          |          | V         |

| 12  |              |          |          |           |          |              |              |          | <b>V</b>     | <b>√</b> | <b>√</b> |          | $\sqrt{}$ |

| 13  |              |          |          |           |          |              |              |          |              | V        | <b>√</b> |          | $\sqrt{}$ |

| 14  |              |          |          |           |          |              |              |          | <b>V</b>     | V        | <b>V</b> |          | V         |

| 15  |              |          |          |           |          |              |              |          | <b>V</b>     | <b>V</b> | <b>V</b> |          | V         |

Table 4 – I/Os Feature Summary

Please note that in addition to table above, all I/Os feature bank-to-bank and bank-to-host level shifting.

World's Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine

### ADVANCED COMMUNICATIONS & SENSING

#### 2 ELECTRICAL CHARACTERISTICS

#### 2.1 Absolute Maximum Ratings

Stress above the limits listed in the following table may cause permanent failure. Exposure to absolute ratings for extended time periods may affect device reliability. The limiting values are in accordance with the Absolute Maximum Rating System (IEC 134). All voltages are referenced to ground (GND).

| Symbol                  | Description                                                 | Min    | Max  | Unit           |

|-------------------------|-------------------------------------------------------------|--------|------|----------------|

| V                       | Main supply voltage (SX1507B)                               | - 0.4  | 6    | V              |

| $V_{max\_VDDM}$         | Main supply voltage (SX1508/9B)                             | - 0.4  | 3.7  | V              |

| V                       | Digital I/O pin supply voltage (SX1507B)                    | - 0.4  | 6    | V              |

| V <sub>max_VCC1-2</sub> | Digital I/O pin supply voltage (SX1508/9B)                  | - 0.4  | 3.7  | V              |

| W                       | Electrostatic handling HBM model <sup>(1)</sup> (SX1507/8B) | - 2000 |      | V              |

| $V_{ES\_HBM}$           | Electrostatic handling HBM model <sup>(1)</sup> (SX1509B)   | -      | 1500 | V              |

| V <sub>ES_CDM</sub>     | Electrostatic handling CDM model                            | -      | 1000 | V              |

| V                       | Electrostatic handling MM model (SX1507/8B)                 | -      | 200  | V              |

| V <sub>ES_MM</sub>      | Electrostatic handling MM model (SX1509B)                   | -      | 150  | V              |

| T <sub>A</sub>          | Operating ambient temperature range                         | -40    | +85  | C              |

| T <sub>C</sub>          | Junction temperature range                                  |        | +125 | ${\mathcal C}$ |

| T <sub>STG</sub>        | Storage temperature range                                   | -55    | +150 | ${\mathcal C}$ |

| l <sub>lat</sub>        | Latchup-free input pin current <sup>(2)</sup>               | +/-100 | -    | mΑ             |

<sup>(1)</sup> Tested according to JESD22-A114A

Table 5 - Absolute Maximum Ratings

### 2.2 Electrical Specifications

Table below assumes default registers values, unless otherwise specified. Typical values are given for  $T_A = +25$ °C, VDDM=VCC1=VCC2=3.3V.

| Symbol     | Description                                              | Conditions                      | Min            | Тур | Max                | Unit |

|------------|----------------------------------------------------------|---------------------------------|----------------|-----|--------------------|------|

| Supply     |                                                          |                                 |                |     |                    |      |

| VDDM       | Main supply voltage                                      | SX1507B                         | 1.2            | -   | 5.5                | V    |

| VDDIVI     | I wain supply voltage                                    | SX1508/9B                       | 1.425          | -   | 3.6                | 7 °  |

| VCC1,2     | I/O banks supply voltage                                 | SX1507B                         | 1.2            | 1   | 5.5                | V    |

| VCC 1,2    | 1/O banks supply voltage                                 | SX1508/9B                       | 1.2            | 1   | 3.6                | V    |

|            | Main supply current                                      | Oscillator OFF                  | -              | 1   | 5                  |      |

|            | (SX1507B, I <sup>2</sup> C inactive)                     | Internal osc. (2MHz)            | -              | TBD | TBD                | μΑ   |

|            | (SX1507B, 1 C mactive)                                   | External osc. (32kHz)           | -              | 10  | -                  |      |

|            | Main supply current                                      | Oscillator OFF                  | -              | 1   | 5                  |      |

| IDDM       | Main supply current (SX1508B, I <sup>2</sup> C inactive) | Internal osc. (2MHz)            | -              | 175 | 235                | μΑ   |

|            |                                                          | External osc. (32kHz)           | -              | 10  | -                  | 1    |

|            | Main supply current (SX1509B, I <sup>2</sup> C inactive) | Oscillator OFF                  | -              | 1   | 5                  |      |

|            |                                                          | Internal osc. (2MHz)            | -              | 365 | 460                | μΑ   |

|            | ,                                                        | External osc. (32kHz)           | -              | 10  | -                  |      |

| ICC1,2     | I/O banks supply current <sup>(1)</sup>                  |                                 | -              | 1   | 2                  | μΑ   |

| I/Os set a | as Input                                                 |                                 |                |     |                    |      |

| VIH        | High level input voltage                                 | VCC1,2 >= 2V                    | 0.7*<br>VCC1,2 | -   | 5.5 <sup>(8)</sup> | V    |

| VIII       | Trigit level iriput voltage                              | VCC1,2 < 2V                     | 0.8*<br>VCC1,2 | -   | 5.5 <sup>(8)</sup> | ] '  |

| VIL        | Low lovel input veltage                                  | VCC1,2 >= 2V                    | -0.4           | -   | 0.3*<br>VCC1,2     | V    |

| VIL        | Low level input voltage                                  | VCC1,2 < 2V                     | -0.4           | -   | 0.2*<br>VCC1,2     | ] `  |

| ILEAK      | Input leakage current                                    | Assuming no active pull-up/down | -1             | -   | 1                  | μΑ   |

| CI         | Input capacitance                                        | -                               | -              | -   | 10                 | pF   |

<sup>(2)</sup> Static latch-up values are valid at maximum temperature according to JEDEC 78 specification

World's Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine

| Symbol             | Description                               | Conditions                       | Min             | Тур    | Max                 | Unit     |

|--------------------|-------------------------------------------|----------------------------------|-----------------|--------|---------------------|----------|

| I/Os set a         | s Output                                  |                                  |                 |        |                     |          |

| VOH                | High level output voltage                 | -                                | VCC1,2<br>- 0.3 | -      | VCC1,2              | V        |

| VOL                | Low level output voltage                  | -                                | -0.4            | _      | 0.3                 | V        |

|                    | ,                                         | VCC1,2 >= 2V                     | -               | -      | 8 <sup>(2)</sup>    |          |

| IOH                | High level output source current          | VCC1,2 < 2V                      | -               | -      | 2 <sup>(2)</sup>    | mΑ       |

| 101                | Low lovel output sink oursent             | VCC1,2 >= 2V                     | -               | -      | 15 <sup>(2)</sup>   | Л        |

| IOL                | Low level output sink current             | VCC1,2 < 2V                      | -               | -      | 8 <sup>(2)</sup>    | mA       |

| t <sub>PV</sub>    | Output data valid timing                  | Cf. Figure 10                    | -               | -      | 425                 | ns       |

| NINT (Out          | tput)                                     |                                  |                 |        |                     |          |

| VOL                | Low level output voltage                  | -                                | -0.4            | -      | 0.3                 | <b>V</b> |

| IOL <sub>M</sub>   | Low level output sink current             | VDDM >= 2V                       | -               | -      | 8                   | mΑ       |

| IOLM               | •                                         | VDDM < 2V                        | -               | -      | 4                   | ША       |

| t <sub>IV</sub>    | Interrupt valid timing                    | From input data change           | -               | -      | 4                   | μs       |

| $t_{IR}$           | Interrupt reset timing                    | From RegInterruptSource clearing | -               | -      | 4                   | μs       |

| NRESET             | (Input)                                   |                                  |                 |        |                     |          |

|                    |                                           | VDDM >= 2V                       | 0.7*VDDM        | -      | VDDM <sub>max</sub> | V        |

| $VIH_{MR}$         | High level input voltage                  | VDDM < 2V                        | 0.8*VDDM        | -      | VDDM <sub>max</sub> | V        |

| \/II               |                                           | VDDM >= 2V                       | -0.4            | -      | 0.3*VDDM            | V        |

| $VIL_M$            | Low level input voltage                   | VDDM < 2V                        | -0.4            | -      | 0.2*VDDM            | V        |

| ILEAK              | Input leakage current                     | -                                | -1              | -      | 1                   | μΑ       |

| CI                 | Input capacitance                         | -                                | -               | -      | 10                  | рF       |

| VPOR               | Power-On-Reset voltage                    | Cf. Figure 8                     | -               | 0.8    | -                   | V        |

| VDROPH             | High brown-out voltage                    | Cf. Figure 8                     | -               | VDDM-1 | -                   | ٧        |

|                    | Low brown-out voltage                     | Cf. Figure 8                     | -               | 0.2    | -                   | V        |

| t <sub>RESET</sub> | Reset time                                | Cf. Figure 8                     | -               | -      | 2.5                 | ms       |

| t <sub>PULSE</sub> | Reset pulse from host uC                  | Cf. Figure 8                     | 200             | -      | -                   | ns       |

|                    | ADDR1 (Inputs)                            |                                  |                 |        |                     |          |

| VIH <sub>MA</sub>  | High lovel input voltage                  | VDDM >= 2V                       | 0.7*VDDM        | -      | VDDM+0.3            | V        |

| VIIIMA             | High level input voltage                  | VDDM < 2V                        | 0.8*VDDM        | -      | VDDM+0.3            | V        |

| $VIL_M$            | Low level input voltage                   | VDDM >= 2V                       | -0.4            | -      | 0.3*VDDM            | V        |

|                    | Low level input voltage                   | VDDM < 2V                        | -0.4            | -      | 0.2*VDDM            | >        |

| ILEAK              | Input leakage current                     | -                                | -1              | -      | 1                   | μΑ       |

| CI                 | Input capacitance                         | -                                | -               | -      | 10                  | рF       |

| OSCIO (Ir          | nput/Output)                              |                                  |                 |        |                     |          |

|                    |                                           |                                  | 0.7*VDDM        | -      | VDDM+0.3            |          |

| $VIH_{MO}$         | High level input voltage                  |                                  | 0.8*VDDM        | -      | VDDM+0.3            |          |

|                    |                                           | VDDM < 1.425V                    | 0.9*VDDM        | -      | VDDM+0.3            |          |

|                    |                                           | VDDM >= 2V                       | -0.4            | -      | 0.3*VDDM            | V        |

| $VIL_{MO}$         | Low level input voltage                   | 1.425V =< VDDM < 2V              | -0.4            | -      | 0.2*VDDM            | ٧        |

|                    |                                           | VDDM < 1.425V                    | -0.4            | -      | 0.1*VDDM            |          |

| ILEAK              | Input leakage current                     | -                                | -1              | -      | 1                   | μΑ       |

| CI                 | Input capacitance                         | -                                | -               | -      | 10                  | рF       |

| VOH <sub>M</sub>   | High level output voltage                 | -                                | VDDM-0.3        | -      | VDDM                | V        |

| VOL                | Low level output voltage                  | -                                | -0.4            | -      | 0.3                 | V        |

| $IOH_{M}$          | High level output source current          | VDDM >= 2V                       | -               | -      | 8                   | mΑ       |

| . •                | - Ing. 1515. Salpat Source Sarroll        | VDDM < 2V                        | -               | -      | 2                   | , \      |

| $IOL_{M}$          | Low level output sink current             | VDDM >= 2V                       | -               | -      | 8                   | mΑ       |

|                    | •                                         | VDDM < 2V                        | -               | -      | 4                   |          |

| SCL (INPL          | ıt) and SDA (Input/Output) <sup>(3)</sup> |                                  |                 |        |                     |          |

World's Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine

# **ADVANCED COMMUNICATIONS & SENSING**

| Symbol              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Conditions                                 | Min                                 | Тур                                             | Max                 | Unit       |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------|-------------------------------------------------|---------------------|------------|

|                     | complies with slave F/S mode I <sup>2</sup> C nuary, 2000. Please refer to that doc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                            |                                     |                                                 | ion version         | 2.1        |

|                     | <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |                                     | <del>                                    </del> | <del>-</del>        |            |

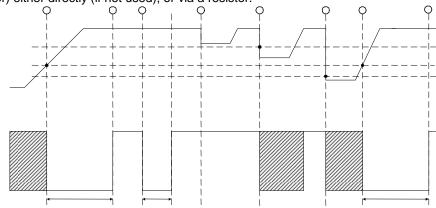

| S                   | DA tributation to the street of the street o | t <sub>f</sub>                             | -t <sub>SP</sub>                    | t <sub>r</sub> +                                |                     |            |

| s                   | CL thD;STA thD;DAT thIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>SU;STA</sub> sr                     | tsu;sto                             | P                                               | s                   |            |

| VOL                 | Low level output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                          | -0.4                                | -                                               | 0.3                 | V          |

| IOL <sub>M</sub>    | Low level output sink current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VDDM >= 2V                                 | -                                   | -                                               | 8                   | mA         |

| IOLM                | Low level output sink current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VDDM < 2V                                  | -                                   | -                                               | 4                   | ША         |

| $VIH_{MR}$          | High level input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VDDM >= 2V                                 | 0.7*VDDM                            | -                                               | $VDDM_{max}$        | V          |

| VIIIMR              | Tilgit level lilput voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VDDM < 2V                                  | 0.8*VDDM                            | -                                               | VDDM <sub>max</sub> |            |

| VIL <sub>M</sub>    | Low level input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VDDM >= 2V                                 | -0.4                                | -                                               | 0.3*VDDM            |            |

| ***                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VDDM < 2V                                  | -0.4                                | -                                               | 0.2*VDDM            | V          |

| f <sub>SCL</sub>    | SCL clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                          | -                                   | -                                               | 400                 | kHz        |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                          | 0.6                                 | -                                               | -                   | μs         |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                          | 1.3                                 | -                                               | -                   | μs         |

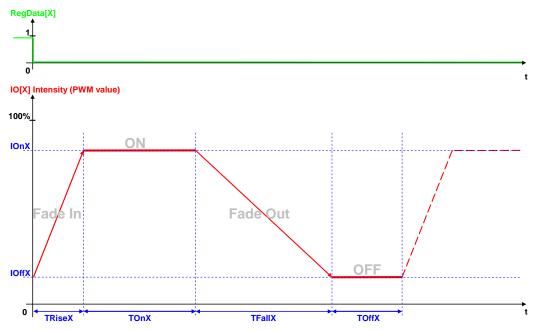

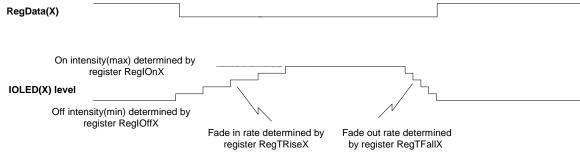

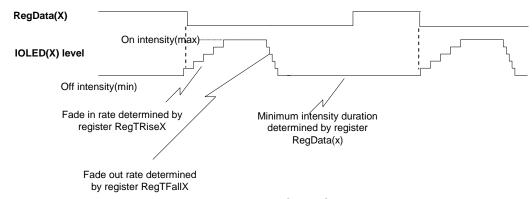

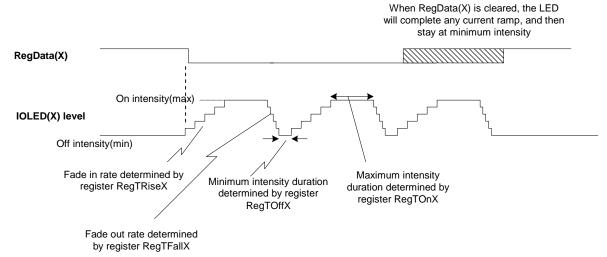

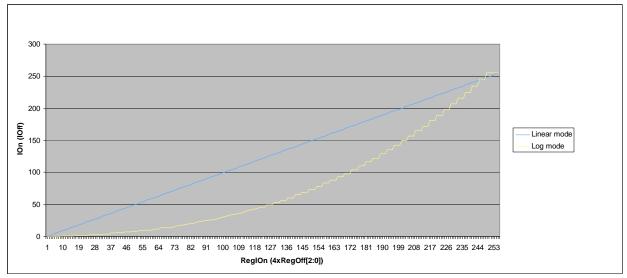

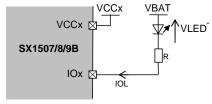

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                          | 0.6                                 | -                                               | -                   | μs         |