# DATA SHEET

| Part No.         | AN12960A          |

|------------------|-------------------|

| Package Code No. | UBGA015-W-2020AEA |

# Panasonic

# Contents

|                                                          | 3  |

|----------------------------------------------------------|----|

| ■ Features                                               | 3  |

| Applications                                             | 3  |

| ■ Package                                                | 3  |

| ■ Туре                                                   | 3  |

| ■ Application Circuit Example (Block Diagram)            | 4  |

| ■ Pin Descriptions                                       | 6  |

| ■ Absolute Maximum Ratings                               | 7  |

| Operating Supply Voltage Range                           | 7  |

| ■ Allowed Voltage Ranges                                 | 8  |

| Electrical Characteristics                               | 9  |

| Electrical Characteristics (Reference values for design) | 11 |

| Electrical Characteristics Test Procedures               | 15 |

| ■ Technical Data                                         | 16 |

| I/O block circuit diagram and pin function descriptions  | 16 |

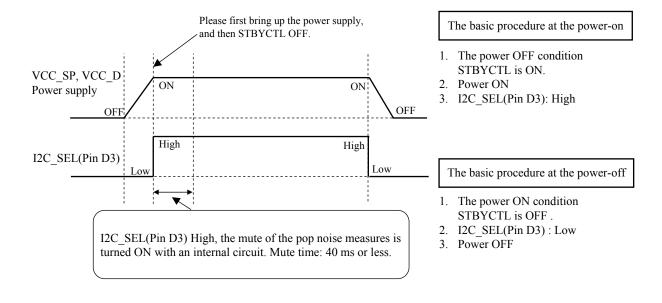

| • The power supply and logic sequence                    | 20 |

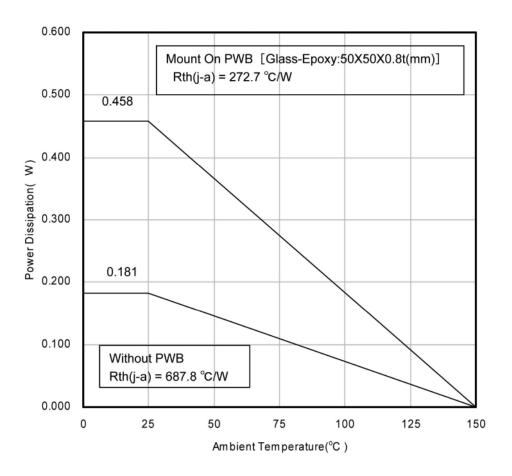

| • $P_D - T_a$ diagram                                    | 22 |

| ■ Usage Note                                             | 23 |

# AN12960A Monaural Class-D amplifier IC with built-in AGC

# Overview

AN12960A is a Class-D audio amplifier IC for mobile devices such as mobile phone and so on.

AGC circuit which prevents sound distortion due to output saturation caused by excessive input is embedded. This IC is equipped with Auto SP Save function which automatically detects non-signal input condition and stops speaker amplifier, and noise at non-signal input can be reduced.

Either I<sup>2</sup>C bus control mode or parallel control mode can be selected.

#### Features

- 1. High power efficiency by Class-D power amplifier (85%, 500 mW output power with 8  $\Omega$  load)

- The original AGC circuit makes low distortion whether AGC is active or not. 2.

- The ON level and attack/recovery time of the AGC can be selected with I<sup>2</sup>C bus control.

- 3. Auto SP Save function

In case of non-signal input, the auto SP save function automatically turns off speaker amplifier, and PWM output is stopped. When larger input signal than set detection level is input, SP Save mode is automatically deactivated and speaker amplifier starts and signal is output. The detection level and detection time for the function to be active are selectable.

- 4. EVR (Electric volume) function : 0 dB to -47 dB by 1 dB

- 5. Gain Selection

- 3-pattern of +16 dB, +19 dB, +22 dB :

- 6. I<sup>2</sup>C bus control mode and parallel control mode (changed by High/Low voltage of a pin) can be used for IC control.

## Applications

· Audio amplifier for mobile devices, such as a cellular phone

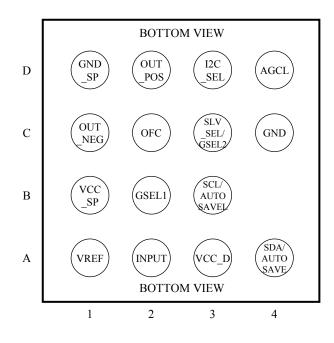

#### Package

• 15 pin wafer level chip size package (WLCSP) Size : 1.96 × 1.96 mm (0.5 mm pitch)

#### Type

• Bi-CMOS IC

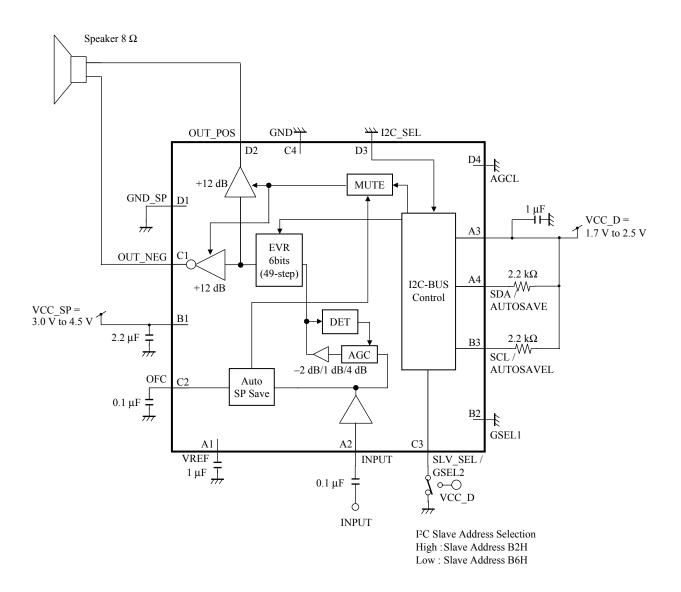

- Application Circuit Example (Block Diagram)

- I<sup>2</sup>C Control Mode

Notes) • This application circuit is shown as an example but does not guarantee the design for mass production set.

- This block diagram is for explaining functions. The part of the block diagram may be omitted, or it may be simplified.

- The threshold voltages of Pin C3 and Pin D3 depend on VCC\_D.

- Pin C3 and Pin D3 are floating condition at open, so please apply either High level or Low level voltage to them.

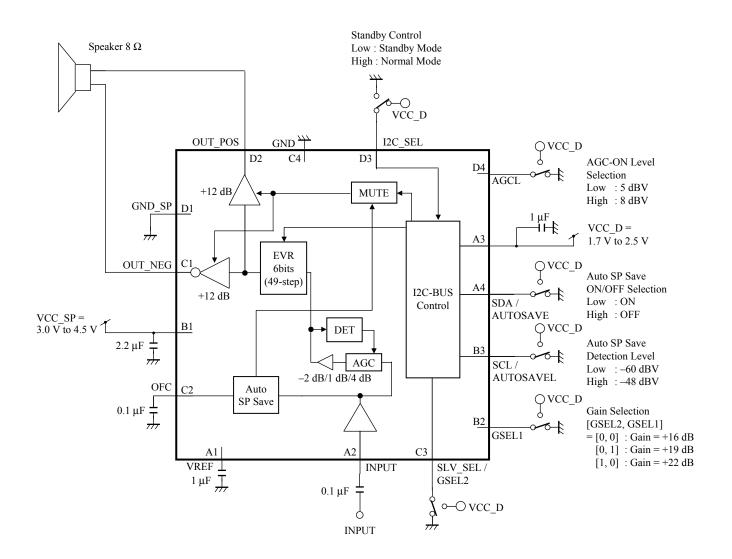

- Application Circuit Example (Block Diagram) (continued)

- Parallel Control Mode

Notes) • This application circuit is shown as an example but does not guarantee the design for mass production set.

- This block diagram is for explaining functions. The part of the block diagram may be omitted, or it may be simplified.

- The threshold voltages of Pin C3, B2, B3, A4, D4, D3 depend on VCC\_D.

- The pins C3, B2, B3, A4, D4, D3 are floating condition at open, so please apply either High level or Low level voltage to them.

## Pin Descriptions

| Pin No. | Pin name           | Туре           | Description                                                                                                                            |

|---------|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| A1      | VREF               | Output         | Reference Voltage                                                                                                                      |

| A2      | INPUT              | Input          | Signal Input                                                                                                                           |

| A3      | VCC_D              | Power Supply   | Power Supply for Logic circuit                                                                                                         |

| A4      | SDA /<br>AUTOSAVE  | Input / Output | I <sup>2</sup> C Control Mode: SDA of I <sup>2</sup> C-bus<br>Parallel Control Mode: Auto SP Save ON/OFF switch                        |

| B1      | VCC_SP             | Power Supply   | Power supply for Speaker Amplifier                                                                                                     |

| B2      | GSEL1              | Input          | I <sup>2</sup> C Control Mode: No Function (Connect to GND)<br>Parallel Control Mode: Gain Selection 1                                 |

| В3      | SCL /<br>AUTOSAVEL | Input          | I <sup>2</sup> C Control Mode: SCL of I <sup>2</sup> C-bus<br>Parallel Control Mode: Auto SP Save Non-signal Threshold Level Selection |

| C1      | OUT_NEG            | Output         | Speaker Output (Negative Phase)                                                                                                        |

| C2      | OFC                | Input / Output | Offset Cancel for Auto SP Save                                                                                                         |

| C3      | SLV_SEL /<br>GSEL2 | Input          | I <sup>2</sup> C Control Mode: I <sup>2</sup> C Slave Address Selection<br>Parallel Control Mode: Gain Selection 2                     |

| C4      | GND                | Ground         | Ground                                                                                                                                 |

| D1      | GND_SP             | Ground         | Ground for Speaker Amplifier                                                                                                           |

| D2      | OUT_POS            | Output         | Speaker Output (Positive Phase)                                                                                                        |

| D3      | I2C_SEL            | Input          | I <sup>2</sup> C Control Mode: No Function (Connect to GND)<br>Parallel Control Mode: Standby Control                                  |

| D4      | AGCL               | Input          | I <sup>2</sup> C Control Mode: No Function (Connect to GND)<br>Parallel Control Mode: AGC-ON Level Selection                           |

## Absolute Maximum Ratings

Note) Absolute maximum ratings are limit values which are not destructed, and are not the values to which operation is guaranteed.

| A No. | Parameter                                                 | Symbol Range      |             | Unit | Notes |

|-------|-----------------------------------------------------------|-------------------|-------------|------|-------|

| 1     | Supply voltage      VCC_D      3.6        VCC_SP      5.5 |                   | V           | *1   |       |

|       |                                                           |                   | 5.5         | v    | .1    |

| 2     | Supply current                                            | I <sub>cc</sub> — |             | А    |       |

| 3     | Power dissipation                                         | P <sub>D</sub>    | 80          | mW   | *2    |

| 4     | Operating ambient temperature                             | T <sub>opr</sub>  | -30 to +85  | °C   | *3    |

| 5     | Storage temperature                                       | T <sub>stg</sub>  | -55 to +150 | °C   |       |

Notes) \*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2 : The power dissipation shown is the value at  $T_a = 85^{\circ}$ C for the independent (unmounted) IC package without a heat sink.

When using this IC, refer to the  $P_D$ - $T_a$  diagram in the  $\blacksquare$  Technical Data standard and design the heat radiation with sufficient margin so that the allowable value might not be exceeded based on the conditions of power supply voltage, load, and ambient temperature.

\*3 :Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

#### Operating supply voltage range

| Parameter            | Symbol | Range      | Unit | Note |

|----------------------|--------|------------|------|------|

|                      | VCC_D  | 1.7 to 2.5 | V    | *1   |

| Supply voltage range | VCC_SP | 3.0 to 4.5 | V    | *1   |

Note) \*1 :The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

#### Allowed Voltage Ranges

Notes) • Allowable current and voltage ranges are limit ranges which are not destructed, and are not the ranges to which operation is guaranteed.

- Voltage values, unless otherwise specified, are with respect to GND. GND is voltage for GND and GND\_SP. GND = GND\_SP

- Do not apply external currents or voltages to any pin not specifically mentioned.

| Pin No. | Pin name      | Range                   | Unit | Notes |

|---------|---------------|-------------------------|------|-------|

| A1      | VREF          | - 0.3 to 2.9            | V    |       |

| A2      | INPUT         | - 0.3 to 2.9            | V    |       |

| A3      | VCC_D         | 0 to 3.6                | V    |       |

| A4      | SDA/AUTOSAVE  | - 0.5 to (VCC_D + 0.5)  | V    | *1    |

| B1      | VCC_SP        | 0 to 5.5                | V    |       |

| B2      | GSEL1         | $-0.3$ to (VCC_D + 0.3) | V    | *1    |

| B3      | SCL/AUTOSAVEL | - 0.5 to (VCC_D + 0.5)  | V    | *1    |

| C3      | SLV_SEL/GSEL2 | - 0.3 to (VCC_D + 0.3)  | V    | *1    |

| D3      | I2C_SEL       | - 0.3 to (VCC_D + 0.3)  | V    | *1    |

| D4      | AGCL          | $-0.3$ to (VCC_D + 0.3) | V    | *1    |

Note) \*1 : (VCC\_D + 0.5) V  $\leq$  3.6 V.

# Panasonic

# ■ Electrical Characteristics at VCC\_D = 1.8 V, VCC\_SP = 3.8 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

| в      | Parameter                                          | Cump al | Conditions                                                                                                 |      | Limits |     | Unit | Note |

|--------|----------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------|------|--------|-----|------|------|

| No.    | Parameter                                          | Symbol  | Conditions                                                                                                 | Min  | Тур    | Max | Unit | Note |

| Circu  | it Current                                         |         |                                                                                                            |      |        | -   |      |      |

| 1      | Circuit current 1 at non-signal (VCC_SP)           | IVCC2A  | Non-signal, STB = OFF,<br>SP = ON, AGC = ON                                                                | _    | 7      | 20  | mA   |      |

| 2      | Circuit current 2 at non-signal (VCC_D)            | IVCC3A  | Non-signal, STB = OFF,<br>SP = ON, AGC = ON                                                                | _    | 1      | 10  | μΑ   |      |

| 3      | Circuit current 1 in standby mode<br>(VCC_SP)      | IVCC2B  | Non-signal, STB = ON,<br>SP = OFF, AGC = ON                                                                | _    | 0.1    | 1.0 | μΑ   |      |

| 4      | Circuit current 2 in standby mode<br>(VCC_D)       | IVCC3B  | Non-signal, STB = ON,<br>SP = OFF, AGC = ON                                                                | _    | 0.1    | 1.0 | μΑ   |      |

| 5      | Circuit current 1 in speaker save mode<br>(VCC_SP) | IVCC2C  | Non-signal, STB = OFF,<br>SP = OFF, AGC = ON                                                               | _    | 3.5    | 5.5 | mA   |      |

| 6      | Circuit current 2 in speaker save mode<br>(VCC_D)  | IVCC3C  | Non-signal, STB = OFF,<br>SP = OFF, AGC = ON                                                               | _    | 0.1    | 10  | μΑ   |      |

| Input- | Output Characteristics                             |         |                                                                                                            |      |        |     |      |      |

| 7      | SP reference output level                          | VSPO    | Vin = -19.0  dBV, f = 1  kHz<br>RL = 8 $\Omega$ , GAIN = +19 dB                                            | -1.5 | 0.0    | 1.5 | dBV  |      |

| 8      | SP reference output distortion                     | THSPO   | Vin = $-19.0 \text{ dBV}$ , f = 1 kHz<br>RL = 8 $\Omega$ , GAIN = $+19 \text{ dB}$<br>to THD5th            |      | 0.05   | 0.5 | %    |      |

| 9      | SP output noise voltage                            | VNSPO   | Non-Signal,<br>using A curve filter<br>GAIN = +19 dB                                                       |      | -79    | -72 | dBV  |      |

| 10     | SP maximum rating output                           | VMSPO   | THD = 10%, f = 1 kHz<br>RL = 8 $\Omega$ , AGC = OFF                                                        | 500  | 900    |     | mW   |      |

| 11     | SP Output level at power save                      | VSSPO   | Vin = $-19.0 \text{ dBV}$ , f = 1 kHz<br>RL = 8 $\Omega$ , GAIN = $+19 \text{ dB}$<br>using A curve filter |      | -110   | -90 | dBV  | _    |

# Panasonic

# ■ Electrical Characteristics (continued) at VCC\_D = 1.8 V, VCC\_SP = 3.8 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

|                     | Demonster                             | O. mahaal        | O and it is an                                                                                                                      |               | Limit | S                                          | Linit | Nata |

|---------------------|---------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------------------------------------------|-------|------|

| B No.               | Parameter                             | Symbol           | mbol Conditions                                                                                                                     |               | Тур   | Max                                        | Unit  | Note |

| I <sup>2</sup> C bu | s (Internal I/O stage characteristi   | cs)              |                                                                                                                                     |               |       |                                            |       |      |

| 12                  | SCL, SDA signal input<br>Low level    | VIL              | _                                                                                                                                   | - 0.5         |       | $0.3 \times VCC_D$                         | V     | *1   |

| 13                  | SCL, SDA signal input<br>High level   | V <sub>IH</sub>  | _                                                                                                                                   | 0.7×<br>VCC_D | _     | $\frac{\text{VCC\_D}_{\text{max}}}{+ 0.5}$ | V     | *1   |

| 14                  | SDA output signal Low level           | V <sub>OL</sub>  | Open drain,<br>sink current : 3 mA                                                                                                  | 0             | _     | 0.2×<br>VCC_D                              | V     | _    |

| 15                  | SCL, SDA signal input current         | Ii               | 入力電圧:<br>0.1VCC_D <sub>max</sub> to 0.9VCC_D <sub>max</sub><br>input voltage:<br>0.1VCC_D <sub>max</sub> to 0.9VCC_D <sub>max</sub> | -10           |       | 10                                         | μΑ    |      |

| 16                  | SCL maximum frequency of signal input | f <sub>SCL</sub> |                                                                                                                                     | 0             |       | 400                                        | kHz   | _    |

# ■ Electrical Characteristics (Reference value for design) at VCC\_D = 1.8 V, VCC\_SP = 3.8 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

| в     | Deremeter                  | Currente el | Canditiana                                                                                         | Refe           | rence v | alues          | Linit | Natas |

|-------|----------------------------|-------------|----------------------------------------------------------------------------------------------------|----------------|---------|----------------|-------|-------|

| No.   | Parameter                  | Symbol      | Conditions                                                                                         | Min            | Тур     | Max            | Unit  | Notes |

| AGC   | Characteristics            |             |                                                                                                    |                |         |                |       |       |

| 17    | SP AGC output level        | VSPOA       | Vin = $-7.0 \text{ dBV}$ ,<br>f = 1 kHz<br>RL = 8 $\Omega$ ,<br>GAIN = +19 dB<br>AGC-Level = 5 dBV | 4.0            | 5.0     | 6.0            | dBV   |       |

| Contr | ol Pin Input Level         | _           |                                                                                                    |                |         |                |       |       |

| 18    | SLV_SEL input Low level    | Vslvl       | _                                                                                                  | _              |         | 0.1 ×<br>VCC_D | v     | _     |

| 19    | SLV_SEL input High level   | Vslvh       | _                                                                                                  | 0.9×<br>VCC_D  | _       |                | v     | _     |

| 20    | I2C_SEL input Low level    | VI2Cl       | —                                                                                                  |                |         | 0.1 ×<br>VCC_D | V     | —     |

| 21    | I2CSEL input High level    | VI2Ch       |                                                                                                    | 0.9 ×<br>VCC_D | _       |                | V     | _     |

| 22    | GSEL1 input Low level      | Vgs11       | I2C_SEL = High                                                                                     | _              |         | 0.1 ×<br>VCC_D | v     | _     |

| 23    | GSEL1 input High level     | Vgs1h       | I2C_SEL = High                                                                                     | 0.9×<br>VCC_D  |         |                | V     | _     |

| 24    | GSEL2 input Low level      | Vgs21       | I2C_SEL = High                                                                                     | _              |         | 0.1 ×<br>VCC_D | V     | _     |

| 25    | GSEL2 input High level     | Vgs2h       | I2C_SEL = High                                                                                     | 0.9 ×<br>VCC_D |         |                | V     |       |

| 26    | AUTOSAVE input Low level   | Vasl        | I2C_SEL = High                                                                                     | _              |         | 0.1 ×<br>VCC_D | V     | _     |

| 27    | AUTOSAVE input High level  | Vash        | I2C_SEL = High                                                                                     | 0.9×<br>VCC_D  |         |                | V     | _     |

| 28    | AUTOSAVEL input Low level  | Vasll       | I2C_SEL = High                                                                                     | _              |         | 0.1 ×<br>VCC_D | V     | _     |

| 29    | AUTOSAVEL input High level | Vaslh       | I2C_SEL = High                                                                                     | 0.9 ×<br>VCC_D |         |                | v     | _     |

| 30    | AGCL input Low level       | Vagell      | I2C_SEL = High                                                                                     | _              |         | 0.1 ×<br>VCC_D | V     | _     |

| 31    | AGCL input High level      | Vagclh      | I2C_SEL = High                                                                                     | 0.9×<br>VCC_D  |         |                | v     | _     |

# ■ Electrical Characteristics (Reference value for design) (continued) at VCC\_D = 1.8 V, VCC\_SP = 3.8 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

| в                  | Demonster                                                          | Ourseland           | Quaditiana                                                     | Refe                  | erence va | lues | Linit | Notoo |

|--------------------|--------------------------------------------------------------------|---------------------|----------------------------------------------------------------|-----------------------|-----------|------|-------|-------|

| No.                | Parameter                                                          | Symbol              | Conditions                                                     | Min                   | Тур       | Max  | Unit  | Notes |

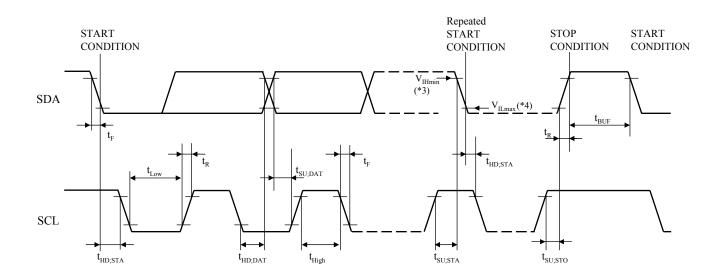

| l <sup>2</sup> C b | us (Bus line specifications)                                       |                     | -                                                              |                       |           | -    |       |       |

| 32                 | Bus free time between a condition of stop and a condition of start | t <sub>BUF</sub>    | _                                                              | 1.3                   | _         |      | μs    | *2    |

| 33                 | Setup time of a condition of start                                 | t <sub>SU;STA</sub> |                                                                | 0.6                   | _         |      | μs    | *2    |

| 34                 | Hold time of a condition of start                                  | t <sub>HD;STA</sub> | The first clock pulse is generated after t <sub>HD:STA</sub> . | 0.6                   | —         |      | μs    | *2    |

| 35                 | Low period of SCL clock                                            | t <sub>Low</sub>    | —                                                              | 1.3                   | —         | —    | μs    | *2    |

| 36                 | High period of SCL clock                                           | t <sub>High</sub>   | —                                                              | 0.6                   | —         | —    | μs    | *2    |

| 37                 | Rising time of SDA, SCL signal                                     | t <sub>R</sub>      | _                                                              | $20 + 0.1 \times C_b$ |           | 0.3  | μs    | *2    |

| 38                 | Fall time of SDA, SCL signal                                       | t <sub>F</sub>      | _                                                              | $20 + 0.1 \times C_b$ | —         | 0.3  | μs    | *2    |

| 39                 | Data setup time                                                    | t <sub>SU;DAT</sub> |                                                                | 0.1                   |           |      | μs    | *2    |

| 40                 | Data hold time                                                     | t <sub>HD;DAT</sub> |                                                                | 0                     |           | 0.9  | μs    | *2    |

| 41                 | Setup time of a condition of stop                                  | t <sub>SU;STO</sub> |                                                                | 0.6                   |           |      | μs    | *2    |

# ■ Electrical Characteristics (Reference value for design)(continued) at VCC\_D = 1.8 V, VCC\_SP = 3.8 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

|                     |                                                                                       |                 |                                                                                                                             | Refere                                               | ence val | ues |      |       |

|---------------------|---------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------|-----|------|-------|

| B No.               | Parameter                                                                             | Symbol          | Conditions                                                                                                                  | Min                                                  | Тур      | Max | Unit | Notes |

| l <sup>2</sup> C bu | is (Internal I/O stage characteri                                                     | stics)          |                                                                                                                             |                                                      |          |     |      |       |

| 42                  | Hysteresis of Schmitt trigger input                                                   | $V_{\rm hys}$   | Hysteresis of SDA, SCL                                                                                                      | $0.05 \times VCC_D$                                  | —        | _   | V    | *2    |

| 43                  | Fall time from $V_{IHmax}$ to $V_{ILmin}$                                             | t <sub>of</sub> | Bus capacitance : 10 pF to 400pF<br>$I_P \le 6 \text{ mA} (V_{OLmax} = 0.6 \text{ V})$<br>$I_P : Max. \text{ sink current}$ | $\begin{array}{c} 20 + \\ 0.1 \times Cb \end{array}$ |          | 250 | ns   | *2    |

| 44                  | Pulse width of spike which must<br>be suppressed by the input filter                  | t <sub>sp</sub> |                                                                                                                             | 0                                                    | _        | 50  | ns   | *2    |

| 45                  | Capacitance for each I/O pin                                                          | Ci              | _                                                                                                                           |                                                      | _        | 10  | pF   | *2    |

| l <sup>2</sup> C bu | is (Bus line specifications) (con                                                     | tinued)         |                                                                                                                             |                                                      |          |     |      |       |

| 46                  | Capacitive load for each bus line                                                     | Cb              | _                                                                                                                           | _                                                    | _        | 400 | pF   | *2    |

| 47                  | Noise margin at the Low-level<br>for each connected device<br>(including hysteresis)  | V <sub>aL</sub> |                                                                                                                             | 0.1 ×<br>VCC_D                                       |          |     | v    | *2    |

| 48                  | Noise margin at the High-level<br>for each connected device<br>(including hysteresis) | $V_{aH}$        |                                                                                                                             | 0.2×<br>VCC_D                                        |          |     | V    | *2    |

#### Electrical Characteristics (Reference value for design)(continued) at VCC\_D = 1.8 V, VCC\_SP = 3.8 V Note) $T_a = 25^{\circ}C \pm 2^{\circ}C$ unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

Notes) \*1 : The input threshold voltage of I<sup>2</sup>C bus (Vth) is linked to VCC\_D (I<sup>2</sup>C bus I/O stage supply voltage). In case the pull-up voltage is not VCC\_D, the threshold voltage (Vth) is fixed to ((VCC\_D / 2) ± (Schmitt width) / 2) and High-level, Low-level of input voltage are not specified.

- In this case, pay attention to Low-level (max.) value ( $V_{ILmax}$ ).

- It is recommended that the pull-up voltage of I<sup>2</sup>C bus is set to the I<sup>2</sup>C bus I/O stage supply voltage (VCC\_D).

- \*2 : All values are  $V_{IHmin} \left(*3\right)$  and  $V_{ILmax} \left(*4\right)$  level reference.

- \*3 : V<sub>IHmin</sub> is the minimum limit of the signal input high level (it indicates to Page\_No.10).

- \*4 : V<sub>ILmax</sub> is the maximum limit of the signal input low level (it indicates to Page\_No.10).

# Panasonic

#### Electrical Characteristics Test Procedures

|                      |                                                 |     | l <sup>2</sup> C-b | us data s | etting |     |       |

|----------------------|-------------------------------------------------|-----|--------------------|-----------|--------|-----|-------|

| C<br>No.             | Parameter                                       |     | S                  | ub-addre  | SS     |     | Notes |

| 110.                 |                                                 | 00H | 01H                | 02H       | 03H    | 04H |       |

| Circuit c            | current                                         |     |                    |           |        |     |       |

| 1                    | Circuit current 1 at non-signal (VCC_SP)        | 2EH | 92H                | 00H       | 00H    | 00H | _     |

| 2                    | Circuit current 2 at non-signal (VCC_D)         | 2EH | 92H                | 00H       | 00H    | 00H | _     |

| 3                    | Circuit current 1 in standby mode (VCC_SP)      | 28H | 92H                | 00H       | 00H    | 00H | _     |

| 4                    | Circuit current 2 in standby mode (VCC_D)       | 28H | 92H                | 00H       | 00H    | 00H | _     |

| 5                    | Circuit current 1 in speaker save mode (VCC_SP) | 2AH | 92H                | 00H       | 00H    | 00H |       |

| 6                    | Circuit current 2 in speaker save mode (VCC_D)  | 2AH | 92H                | 00H       | 00H    | 00H | _     |

| Input-O              | utput characteristic                            |     |                    |           |        |     |       |

| 7                    | SP reference output level                       | 2EH | 92H                | 00H       | 00H    | 00H |       |

| 8                    | SP reference output distortion                  | 2EH | 92H                | 00H       | 00H    | 00H | _     |

| 9                    | SP output noise voltage                         | 2EH | 92H                | 00H       | 00H    | 00H | _     |

| 10                   | SP maximum rating output                        | 26H | 92H                | 00H       | 00H    | 00H |       |

| 11                   | SP output level at power save                   | 2AH | 92H                | 00H       | 00H    | 00H |       |

| I <sup>2</sup> C bus | (Internal I/O stage characteristics)            |     |                    |           |        |     |       |

| 12                   | SCL, SDA signal low-level input                 | —   | _                  | _         | _      |     | _     |

| 13                   | SCL, SDA signal high-level input                | _   | _                  | _         | _      |     |       |

| 14                   | SDA signal low-level output                     | _   | _                  | _         | _      |     | _     |

| 15                   | SCL, SDA signal input current                   | _   |                    | _         | _      |     | _     |

| 16                   | SCL signal allowable input max. frequency       |     | _                  | _         | _      |     | _     |

| AGC Ch               | naracteristics                                  |     |                    |           |        |     |       |

| 17                   | SP AGC output level                             | 2EH | 92H                | 00H       | 00H    | 00H | _     |

# • I/O block circuit diagram and pin function descriptions

| Pin<br>No. | Waveform and voltage     | Internal circuit                             | Impedance                         | Description                                                                                                                                                   |

|------------|--------------------------|----------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1         | VREF<br>DC 1.35 V        |                                              | Input impedance<br>= About 150 kΩ | Reference Voltage<br>The reference voltage terminal for<br>determining DC bias of input<br>stage. Please connect an external<br>capacitor to remove a ripple. |

| A2         | INPUT<br>DC 1.35 V       | $A2 \xrightarrow{4k} \xrightarrow{16k} VREF$ | Input impedance<br>= About 20 kΩ  | Signal Input<br>Please insert the capacitor of 0.1<br>µF in series.                                                                                           |

| A3         | VCC_D<br>1.8 V (typ.)    | —                                            | _                                 | Power Supply for Logic Circuit                                                                                                                                |

| A4         | SDA/<br>AUTOSAVE<br>Hi-Z |                                              | Input impedance<br>= Hi-Z         | I <sup>2</sup> C Control Mode:<br>I <sup>2</sup> C-Bus SDA<br>Parallel Control Mode:<br>Auto SP Save ON/OFF Switch<br>Please don't make this pin open.        |

# • I/O block circuit diagram and pin function descriptions

| Pin<br>No. | Waveform and voltage                                      | Internal circuit                                                                                                                                                                                                                                            | Impedance                 | Description                                                                                                                                                                      |

|------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В1         | VCC_SP<br>3.8 V (typ.)                                    |                                                                                                                                                                                                                                                             | —                         | Power Supply for Speaker<br>Amplifier                                                                                                                                            |

| B2         | GSEL1<br>0 V or<br>1.8 V (typ.)<br>0 V or<br>2.5 V (max.) | WCC_D<br>B2<br>B2<br>B2<br>B2<br>B2<br>C<br>B2<br>C<br>C<br>D<br>C<br>C<br>D<br>C<br>C<br>D<br>C<br>C<br>D<br>C<br>C<br>D<br>C<br>C<br>D<br>C<br>C<br>D<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C | Input impedance<br>= Hi-Z | Gain Selection 1<br>Please don't make this pin open.                                                                                                                             |

| В3         | SCL /<br>AUTOSAVEL<br>Hi-Z                                |                                                                                                                                                                                                                                                             | Input impedance<br>= Hi-Z | I <sup>2</sup> C Control Mode:<br>I <sup>2</sup> C-Bus SCL<br>Parallel Control Mode:<br>Auto SP Save Non-signal<br>Threshold Level Selection<br>Please don't make this pin open. |

• I/O block circuit diagram and pin function descriptions

| Pin<br>No. | Waveform and voltage                                                   | Internal circuit                           | Impedance                                          | Description                                                                                                                                                                                       |

|------------|------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1         | OUT_NEG<br>0 V to<br>3.8 V (typ.)                                      | VCC_SP<br>VCC_SP<br>VCC_SP<br>VCC_SP<br>CI | Output impedance<br>= Equal to or less<br>than 1 Ω | Speaker Output (Negative Phase)                                                                                                                                                                   |

| C2         | DET_OFC<br>DC 1.35 V                                                   |                                            | Input impedance<br>= About 50 kΩ                   | Offset cancel terminal for Auto SP<br>Save function                                                                                                                                               |

| С3         | SLV_SEL /<br>GSEL2<br>0 V or<br>1.8 V (typ.)<br>0 V or<br>2.5 V (max.) |                                            | Input impedance<br>= Hi-Z                          | I <sup>2</sup> C Control Mode:<br>I <sup>2</sup> C Slave Address Selection<br>High level: B2H<br>Low level: B6H<br>Parallel Control Mode:<br>Gain Selection 2<br>Please don't make this pin open. |

| C4         | GND<br>DC 0 V                                                          | _                                          | _                                                  | Ground                                                                                                                                                                                            |

• I/O block circuit diagram and pin function descriptions

| Pin<br>No. | Waveform<br>and voltage                                     | Internal circuit                                                               | Impedance                                          | Description                                                                                                                                     |

|------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Dl         | GND_SP                                                      | _                                                                              | _                                                  | Ground for Speaker Amplifier                                                                                                                    |

| D2         | OUT_POS<br>0 V to<br>3.8 V (typ.)                           | VCC_SP<br>VCC_SP<br>VCC_SP<br>VCC_SP<br>VCC_SP<br>02<br>m<br>m<br>vcc_sp<br>02 | Output impedance<br>= Equal to or less<br>than 1 Ω | Speaker Output (Positive Phase)                                                                                                                 |

| D3         | I2C_SEL<br>0 V or<br>1.8 V (typ.)<br>0 V or<br>2.5 V (max.) |                                                                                | Input impedance<br>= Hi-Z                          | I <sup>2</sup> C Control Mode:<br>No Function (Connect to GND)<br>Parallel Control Mode:<br>Standby Control<br>Please don't make this pin open. |

| D4         | AGCL<br>0 V or<br>1.8 V (typ.)<br>0 V or<br>2.5 V (max.)    |                                                                                | Input impedance<br>= Hi-Z                          | AGC-ON Level Selection<br>Low level: 5 dBV<br>High level: 8 dBV<br>Please don't make this pin open.                                             |

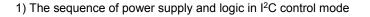

#### • The power supply and logic sequence

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed. The timing control of power-ON/OFF and each logic according to the procedure below should be recommended for the best pop performance caused in switching.

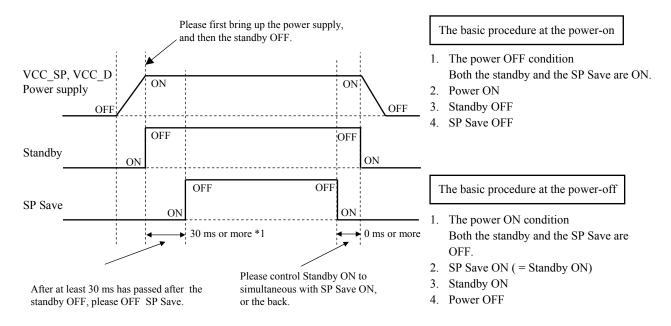

#### 2) The sequence of VCC\_SP and VCC\_D

This IC have not a standup and falling order in VCC\_SP and VCC\_D. The standup and falling time of VCC\_SP and VCC\_D recommend 1 ms or more.

Note) \*1 : This IC contains the pre-charge circuit, It is time until each bias is stabilized from Standby OFF.

It depends for this time on the capacity value linked to a standard voltage terminal (VREF), and the capacity value and resistance linked to an input terminal (IN).

It is a recommendation value in a constant given in the example of an application circuit (block diagram).

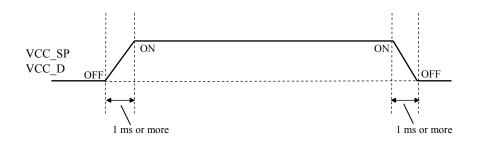

• The power supply and logic sequence (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed. The timing control of power-ON/OFF and each logic according to the procedure below should be recommended for the best pop performance caused in switching.

# **Panasonic**

## ■ Technical Data (continued)

•  $P_D - T_a$  diagram

#### Usage Notes

#### Special attention and precaution in using

- 1. This IC is intended to be used for general electronic equipment [cellular phones].

- Consult our sales staff in advance for information on the following applications:

- Special applications in which exceptional quality and reliability are required, or if the failure or malfunction of this IC may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (1) Space appliance (such as artificial satellite, and rocket)

- (2) Traffic control equipment (such as for automobile, airplane, train, and ship)

- (3) Medical equipment for life support

- (4) Submarine transponder

- (5) Control equipment for power plant

- (6) Disaster prevention and security device

- (7) Weapon

- (8) Others : Applications of which reliability equivalent to (1) to (7) is required

- 2. Pay attention to the direction of LSI. When mounting it in the wrong direction onto the PCB (printed-circuit-board), it might smoke or ignite.

- 3. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins. In addition, refer to the Pin Description for the pin configuration.

- 4. Perform a visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as a solderbridge between the pins of the semiconductor device. Also, perform a full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the LSI during transportation.

- Take notice in the use of this product that it might break or occasionally smoke when an abnormal state occurs such as output pin-V<sub>CC</sub> short (Power supply fault), output pin-GND short (Ground fault), or output-to-output-pin short (load short).

And, safety measures such as an installation of fuses are recommended because the extent of the above-mentioned damage and smoke emission will depend on the current capability of the power supply.

- 6. When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- 7. When using the LSI for new models, verify the safety including the long-term reliability for each product.

- 8. When the application system is designed by using this LSI, be sure to confirm notes in this book. Be sure to read the notes to descriptions and the usage notes in the book.

- 9. Please carry out the thermal design with sufficient margin such that the power dissipation will not be exceeded, based on the conditions of power supply, load and surrounding temperature. Although indicated also in the column of the maximum rating, the maximum rating becomes an instant and the marginal value which must not exceed. It sufficiently evaluates, and I use-wish-do so that it may not exceed certainly. Moreover, don't impress neither voltage nor current to PIN which is not indicated. It may destroy in both cases.

- 10. If SDA/AUTOSAVE (Pin A4), GSEL1(Pin B2), SCL/AUTOSAVEL (Pin B3), SLV\_SEL/GSEL2(Pin C3), I2C\_SEL(Pin D3), I2C\_SEL(Pin D3) and AGCL (Pin D4) are open, their inputs are arbitrary. Don't make them open.

Panasonic

#### Usage Notes (continued)

- Special attention and precaution in using (continued)

- 11. Due to unshielded structure of this IC, under exposure of light, function and characteristic of the product cannot be guaranteed. During normal operation or even under testing condition, please ensure that IC is not exposed to light.

- 12. Basically, chip surface is ground potential. Please design to ensure no contact between chip surface and metal shielding.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for general applications (such as office equipment, communications equipment, measuring instruments and household appliances), or for specific applications as expressly stated in this book. Consult our sales staff in advance for information on the following applications:

• Special applications (such as for airplanes, aerospace, automotive equipment, traffic signaling equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

It is to be understood that our company shall not be held responsible for any damage incurred as a result of or in connection with your using the products described in this book for any special application, unless our company agrees to your using the products in this book for any special application.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

(6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

(7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20100202