# V23806-A8-C1

Multimode 1300 nm LED Fast Ethernet/FDDI/ATM 10 dB

155 MBd 1x9 Transceiver

#### FEATURES

- Compliant with Fast Ethernet, FDDI, Fibre Channel, ATM/SONET/SDH standards

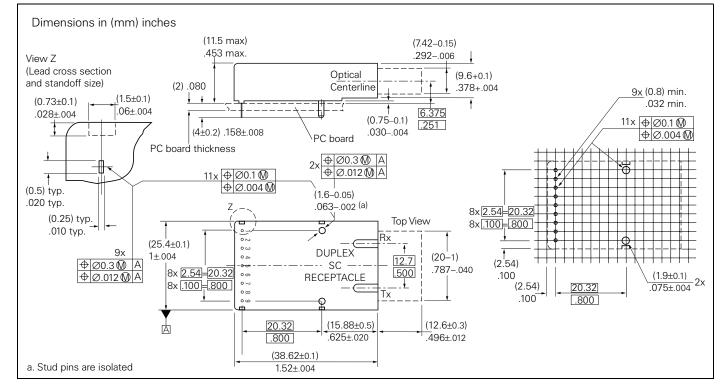

- Compact integrated transceiver unit with duplex SC receptacle

- Single power supply with +5.0 V±10%

- PECL differential inputs and outputs

- System optimized for 62.5/50  $\mu\text{m}$  graded index fiber

- Industry standard multisource footprint

- Wave solderable and washable with process plug inserted

- Testboard available

- UL-94 certified

- ESD Class 2 per MIL-STD 883 Method 3015

- Compliant with FCC (Class B) and EN 55022

- For distances of up to 2 km

# APPLICATIONS

- ATM switches/bridges/routers

- Fast Ethernet, FDDI

- High speed computer links

- Local area networks

- Switching systems

## **Absolute Maximum Ratings**

Exceeding any one of these values may destroy the device immediately.

| Supply Voltage (V <sub>CC</sub> –V <sub>EE</sub> )–0.5 V<br>Data Input Levels (PECL) (V <sub>IN</sub> )V <sub>F</sub> |         |

|-----------------------------------------------------------------------------------------------------------------------|---------|

|                                                                                                                       |         |

| Differential Data Input Voltage                                                                                       |         |

| Operating Ambient Temperature (TAMB) 0°C t                                                                            | o 70°C  |

| Storage Ambient Temperature40°C t                                                                                     | o 85°C  |

| Soldering Conditions, Temp/Time (T <sub>SOLD</sub> /t <sub>SOLD</sub> )                                               |         |

| (MIL-STD 883C, Method 2003) 250°                                                                                      | C/5.5 s |

| Output Current (I <sub>O</sub> )                                                                                      | 50 mA   |

## DESCRIPTION

This data sheet describes the Infineon Fast Ethernet/FDDI/ATM transceiver – part of Infineon Multistandard Transceiver Family. It is fully compliant with the Asynchronous Transfer Mode (ATM) OC-3 standard, the Fiber Distributed Data Interface (FDDI) Low Cost Fiber Physical Layer Medium Dependent (LCF-PMD) draft standard<sup>(1)</sup>, and the FDDI PMD standard<sup>(2)</sup>.

ATM was developed because of the need for multimedia applications, including real time transmission. The data rate is scalable and the ATM protocol is the basis of the broadband public networks being standardized in the International Telegraph and Telephone Consultative Committee (CCITT). ATM can also be used in local private applications.

FDDI is a Dual Token Ring standard developed in the U.S. by the Accredited National Standards Committee (ANSC) X3T9, within the Technical Committee X3T9.5. It is applied to the local area networks of stations, transferring data at 100 Mbits/s with a 125 MBaud transmission rate. LCF FDDI is specially developed for short distance applications of up to 500 m (fiber-to-the-desk) as compared to 2 km for backbone applications.

Fast Ethernet was developed because of the higher bandwidth requirement in local area networking. It is based on the proven effectiveness of millions of installed Ethernet systems.

The Infineon multimode transceiver is a single unit comprised of a transmitter, a receiver, and an SC receptacle. This design frees the customer from many alignment and PC board layout concerns. The modules are designed for low cost applications.

## **TECHNICAL DATA**

The electro-optical characteristics described in the following tables are valid only for use under the recommended operating conditions.

#### **Recommended Operating Conditions**

| _                                        |                                  |       | -    |       |       |

|------------------------------------------|----------------------------------|-------|------|-------|-------|

| Parameter                                | Symbol                           | Min.  | Тур. | Max.  | Units |

| Ambient Temperature                      | T <sub>AMB</sub>                 | 0     |      | 70    | °C    |

| Power Supply Voltage                     | $V_{CC-}V_{EE}$                  | 4.75  | 5.0  | 5.25  | V     |

| Supply Current +5 V <sup>(1)</sup>       | ICC                              | 140   | 170  | 210   | mA    |

| Transmitter                              |                                  |       |      |       |       |

| Data Input<br>High Voltage               | V <sub>IH</sub> -V <sub>CC</sub> | -1165 |      | -880  | mV    |

| Data Input<br>Low Voltage                | V <sub>IL</sub> -V <sub>CC</sub> | -1810 |      | -1475 | mV    |

| Input Data Rise/Fall,<br>20%–80%         | t <sub>R</sub> , t <sub>F</sub>  | 0.4   |      | 1.3   | ns    |

| Data High Time <sup>(2)</sup>            | t <sub>on</sub>                  |       |      | 1000  |       |

| Receiver                                 |                                  |       |      |       |       |

| Output Current                           | Ι <sub>Ο</sub>                   |       |      | 25    | mA    |

| Input Duty Cycle<br>Distortion           | <sup>t</sup> DCD                 |       |      | 1.0   | ns    |

| Input Data<br>Dependent Jitter           | t <sub>DDj</sub>                 |       |      |       |       |

| Input Random Jitter                      | t <sub>RJ</sub>                  |       |      | 0.76  |       |

| Input Center<br>Wavelength               | Ι <sub>C</sub>                   | 1260  | 1    | 1380  | nm    |

| Electrical Output<br>Load <sup>(3)</sup> | RL                               |       | 50   |       | W     |

#### Notes

- 1. For V<sub>CC</sub>–V<sub>EE</sub> (min., max.). 50% duty cycle. The supply current (I<sub>CC2</sub>+I<sub>CC3</sub>) does not include the load drive current (Icc1). Add max. 45 mA for the three outputs. Load is 50  $\Omega$  into V<sub>CC</sub>–2V.

- To maintain good LED reliability, the device should not be held in the ON state for more than the specified time. Normal operation should be done with 50% duty cycle.

- 3. To achieve proper PECL output levels the 50  $\Omega$  termination should be done to V<sub>CC</sub> –2 V. For correct termination see the application notes.

#### Fiber Optics

#### **Transmitter Electro-Optical Characteristics**

| Transmitter                                                      | Symbol                          | Min. | Тур. | Max. | Units |

|------------------------------------------------------------------|---------------------------------|------|------|------|-------|

| Data Rate                                                        | DR                              |      |      | 200  | MBd   |

| Launched Power (Average)<br>into 62.5 µm Fiber <sup>(1, 2)</sup> | P <sub>O</sub>                  | -20  | -17  | -14  | dBm   |

| Center Wavelength <sup>(2, 3)</sup>                              | λ <sub>C</sub>                  | 1270 |      | 1360 | nm    |

| Spectral Width (FWHM) <sup>(2, 4)</sup>                          | DI                              |      |      | 200  |       |

| Output Rise/Fall Time, 10%–90% <sup>(2, 5)</sup>                 | t <sub>R</sub> , t <sub>F</sub> | 0.6  |      | 2.5  | ns    |

| Extinction Ratio<br>(Dynamic) <sup>(2, 6)</sup>                  | ER                              |      |      | 10   | %     |

| Overshoot                                                        | OS                              |      |      | 10   | %     |

| Duty Cycle Distortion <sup>(7, 8)</sup>                          | t <sub>DCD</sub>                |      |      | 0.6  | ns    |

| Data Dependent Jitter <sup>(7, 9)</sup>                          | t <sub>DDJ</sub>                |      |      | 0.3  |       |

| Random Jitter <sup>(7, 10)</sup>                                 | t <sub>RJ</sub>                 |      |      | 0.6  |       |

Notes

- Measured at the end of 5 meters of 62.5/125/0.275 graded index fiber using calibrated power meter and a precision test ferrule. Cladding modes are removed. Values valid for EOL and worst-case temperature.

- 2. The input data pattern is a 12.5 MHz square wave pattern.

- 3. Center wavelength is defined as the midpoint between the two 50% levels of the optical spectrum of the LED.

- 4. Spectral width (full width, half max) is defined as the difference between 50% levels of the optical spectrum of the LED.

- 5. 10% to 90% levels. Measured using the 12.5 MHz square wave pattern with an optoelectronic measurement system (detector and oscilloscope) having 3 dB bandwidth ranging from less than 0.1 MHz to more than 750 MHz.

- 6. Extinction Ratio is defined as PL/PH x 100%. Measurement system as in Note 5.

- 7. Test method as for FDDI-PMD. Jitter values are peak-to-peak.

- Duty Cycle Distortion is defined as 0.5 [(width of wider state) minus (width of narrower state)]. It is measured with stream of Idle Symbols (62.5 MHz square wave).

- 9. Measured with the same pattern as for FDDI-PMD.

- 10. Measured with the Halt Line state (12.5 MHz square wave).

#### **Receiver Electro-Optical Characteristics**

| Receiver                                       | Symbol                                 | Min.  | Тур. | Max.  | Units |

|------------------------------------------------|----------------------------------------|-------|------|-------|-------|

| Data Rate                                      | DR                                     | 5     |      | 200   | MBd   |

| Sensitivity<br>Average Power) <sup>(1)</sup>   | P <sub>IN</sub>                        |       | -33  | -31   | dBm   |

| Saturation (Average<br>Power) <sup>(2)</sup>   | P <sub>SAT</sub>                       | -14   | -11  |       |       |

| Duty Cycle<br>Distortion <sup>(3, 4)</sup>     | <sup>t</sup> DCD                       |       |      | 1.4   | ns    |

| Deterministic Jitter <sup>(4, 5)</sup>         | t <sub>DJ</sub>                        |       |      | 2.2   |       |

| Random Jitter <sup>(4, 6)</sup>                | t <sub>RJ</sub>                        |       |      | 2.3   |       |

| Signal Detect<br>Assert Level <sup>(7)</sup>   | P <sub>SDA</sub>                       | -42.5 |      | -30   | dBm   |

| Signal Detect<br>Deassert Level <sup>(8)</sup> | P <sub>SDD</sub>                       | -45   |      | -31.5 |       |

| Signal Detect<br>Hysteresis                    | P <sub>SDA</sub> –<br>P <sub>SDD</sub> | 1.5   |      |       | dB    |

| Output Low Voltage <sup>(9)</sup>              | V <sub>OL</sub> -V <sub>CC</sub>       | -1810 |      | -1620 | mV    |

| Output High Voltage <sup>(9)</sup>             | V <sub>OH</sub> -V <sub>CC</sub>       | -1025 |      | -880  |       |

| Output Data<br>Rise/Fall Time,<br>20%–80%      | t <sub>R</sub> , t <sub>F</sub>        |       |      | 1.3   | ns    |

| Output SD<br>Rise/Fall Time,<br>20%–80%        |                                        |       |      | 40    |       |

Notes

**APPLICATION NOTE**

- For a BER of less than 1x10<sup>E-12</sup>. Measured in the center of the eye opening with a 2<sup>7</sup>-1 PRBS at 194 MBd.

- 3. Measured at an average optical power level of –20 dBm with a 62.5 MHz square wave.

- All jitter values are peak-to-peak. RX output jitter requirements are not considered in the ATM standard draft. In general the same requirements as for FDDI are met.

- 5. Measured at an average optical power level of -20 dBm.

- 6. Measured at -33 dBm average power.

- 7. An increase in optical power through the specified level will cause the SIGNAL detect output to switch from a Low state to a High state.

- 8. A decrease in optical power through the specified level will cause the SIGNAL detect output to switch from a High state to a Low state.

- 9. PECL compatible. Load is 50  $\Omega$  into V<sub>CC</sub> –2 V. Measured under DC conditions. For dynamic measurements a tolerance of 50 mV should be added for V<sub>CC</sub>=+5 V.

#### **Pin Description**

| Pin Nar                        | ne                  | Level/Logic                | Pin#      | Description                                                         |

|--------------------------------|---------------------|----------------------------|-----------|---------------------------------------------------------------------|

| $R_{x}V_{EE}$                  | Rx Ground           | Power Supply               | 1         | Negative power sup-<br>ply, normally ground                         |

| RD                             | Rx Output           | PECL Output                | 2         | Receiver output data                                                |

| RDn                            | Data                |                            | 3         | Inverted receiver out-<br>put data                                  |

| RxSD                           | RX Signal<br>Detect | PECL Output<br>active high | 4         | High level on this out-<br>put shows there is an<br>optical signal. |

| $R_{x}V_{CC}$                  | Rx +5 V             | Power Supply               | 5         | Positive power sup-                                                 |

| T <sub>x</sub> V <sub>CC</sub> | Tx +5 V             |                            | 6         | ply, +5 V                                                           |

| TxDn                           | Tx Input<br>Data    | PECL Input                 | 7         | Inverted transmitter input data                                     |

| TxD                            |                     |                            | 8         | Transmitter input<br>data                                           |

| T <sub>x</sub> V <sub>EE</sub> | Tx Ground           | Power Supply               | 9         | Negative power sup-<br>ply, normally ground                         |

| Stud                           | Ground              |                            | S1/<br>S2 | Ground connected,<br>Mech. support                                  |

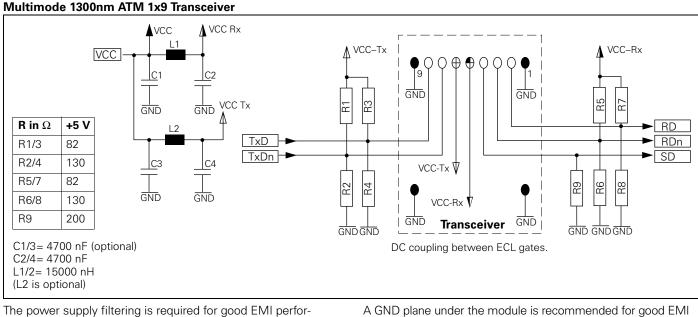

The power supply filtering is required for good EMI performance. Use short tracks from the inductor L1/L2 to the module  $V_{CC}$ -Rx/ $V_{CC}$ -Tx.

A GND plane under the module is recommended for good EMI and sensitivity performance as well as ground connection of studs.

Infineon Technologies AG i.Gr.• Fiber Optics • Wernerwerkdamm 16 • Berlin D-13623, Germany Infineon Technologies, Corp. • Fiber Optics • 19000 Homestead Road • Cupertino, CA 95014 USA Siemens K.K. • Fiber Optics • Takanawa Park Tower • 20-14, Higashi-Gotanda, 3-chome, Shinagawa-ku • Tokyo 141, Japan www.infineon.com/fiberoptics

For a bit error rate (BER) of less than 1x10<sup>E-12</sup> over a receiver eye opening of least 1.5 ns. Measured with a 2<sup>7</sup>-1 PRBS at 194 MBd.