# Color Television RGB to PAL/NTSC Encoder

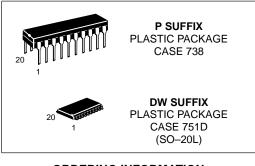

The MC1377 will generate a composite video from baseband red, green, blue, and sync inputs. On board features include: a color subcarrier oscillator; voltage controlled 90° phase shifter; two double sideband suppressed carrier (DSBSC) chroma modulators; and RGB input matrices with blanking level clamps. Such features permit system design with few external components and accordingly, system performance comparable to studio equipment with external components common in receiver systems.

- Self-contained or Externally Driven Reference Oscillator

- Chroma Axes, Nominally 90° (±5°), are Optionally Trimable

- PAL/NTSC Compatible

- Internal 8.2 V Regulator

## COLOR TELEVISION RGB to PAL/NTSC ENCODER

SEMICONDUCTOR TECHNICAL DATA

#### ORDERING INFORMATION

| Device   | Operating<br>Temperature Range | Package     |

|----------|--------------------------------|-------------|

| MC1377DW | T <sub>A</sub> = 0° to +70°C   | SO-20L      |

| MC1377P  | $I_{A} = 0 10 + 70 C$          | Plastic DIP |

© Motorola, Inc. 1995

#### MAXIMUM OPERATING CONDITIONS

| Rating                                         | Symbol           | Value       | Unit       |

|------------------------------------------------|------------------|-------------|------------|

| Supply Voltage                                 | VCC              | 15          | Vdc        |

| Storage Temperature                            | T <sub>stg</sub> | -65 to +150 | °C         |

| Power Dissipation Package<br>Derate above 25°C | PD               | 1.25<br>10  | W<br>mW/°C |

| Operating Temperature                          | Т <sub>А</sub>   | 0 to +70    | °C         |

#### **RECOMMENDED OPERATING CONDITIONS**

| Characteristics                                                                                                                     | Min | Тур      | Max               | Unit                 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------------------|----------------------|

| Supply Voltage                                                                                                                      | 10  | 12       | 14                | Vdc                  |

| IB Current (Pin 16)                                                                                                                 | 0   | -        | -10               | mA                   |

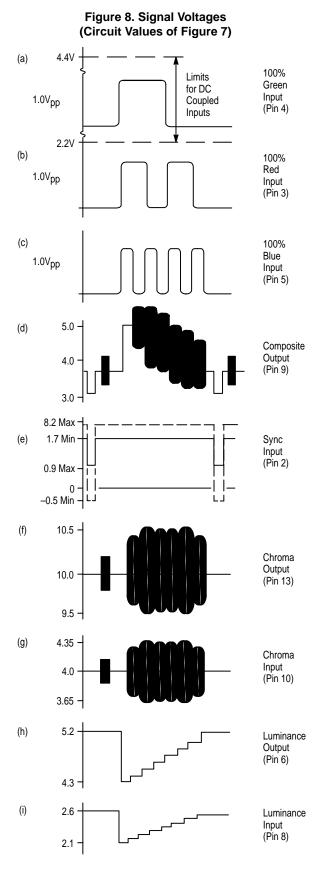

| Sync, Blanking Level (DC level between pulses, see Figure 9e)<br>Sync Tip Level (see Figure 9e)<br>Sync Pulse Width (see Figure 9e) |     | 0<br>    | 8.2<br>0.9<br>5.2 | Vdc<br>μs            |

| R, G, B Input (Amplitude)<br>R, G, B Peak Levels for DC Coupled Inputs, with Respect to Ground                                      |     | 1.0<br>_ | _<br>4.4          | V <sub>pp</sub><br>V |

| Chrominance Bandwidth (Non-comb Filtered Applications), (6 dB)                                                                      | 0.5 | 1.5      | 2.0               | MHz                  |

| Ext. Subscarrier Input (to Pin 17) if On–Chip Oscillator is not used.                                                               |     | 0.7      | 1.0               | V <sub>pp</sub>      |

## **ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = 12 Vdc, $T_A$ = 25°C, circuit of Figure 7, unless otherwise noted.)

| Characteristics                                                                                                                                                                                                                                                          |                                                                                     |               | Symbol                                                       | Min             | Тур                        | Max                    | Unit                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------|-----------------|----------------------------|------------------------|------------------------|

| SUPPLY CURRENT                                                                                                                                                                                                                                                           |                                                                                     |               |                                                              |                 |                            |                        |                        |

| Supply Current into V <sub>CC,</sub> No Load, on Pin 9.<br>Circuit Figure 7                                                                                                                                                                                              | $V_{CC} = 10 V \\ V_{CC} = 11 V \\ V_{CC} = 12 V \\ V_{CC} = 13 V \\ V_{CC} = 14 V$ | 14            | ICC                                                          | -<br>20<br>-    | 33<br>34<br>35<br>36<br>37 | -<br>-<br>40<br>-<br>- | mA                     |

| VOLTAGE REGULATOR                                                                                                                                                                                                                                                        |                                                                                     |               |                                                              |                 |                            |                        |                        |

| $ \begin{array}{l} V_B \text{ Voltage } (I_B = -10 \text{ mA},  V_{CC} = 12 \text{ V},  Figure 7) \\ Load Regulation  (0 < I_B \leq 10 \text{ mA},  V_{CC} = 12 \text{ V}) \\ Line Regulation  (I_B = 0 \text{ mA},  10 \text{ V} < V_{CC} < 14 \text{ V}) \end{array} $ |                                                                                     |               | V <sub>B</sub><br>Reg <sub>load</sub><br>Reg <sub>line</sub> | 7.7<br>-20<br>- | 8.2<br>120<br>4.5          | 8.7<br>+30<br>–        | Vdc<br>mV<br>mV/V      |

| OSCILLATOR AND MODULATION                                                                                                                                                                                                                                                |                                                                                     |               |                                                              |                 |                            | _                      |                        |

| Oscillator Amplitude with 3.58 MHz/4.43 MHz crystal                                                                                                                                                                                                                      |                                                                                     | 17            | Osc                                                          | -               | 0.6                        | -                      | V <sub>pp</sub>        |

| Subcarrier Input: Resistance at 3.58 MHz<br>4.43 MHz                                                                                                                                                                                                                     |                                                                                     | 17            | R <sub>osc</sub>                                             |                 | 5.0<br>4.0                 | -                      | kΩ                     |

| Capacitance                                                                                                                                                                                                                                                              |                                                                                     |               | C <sub>osc</sub>                                             | _               | 2.0                        | _                      | pF                     |

| Modulation Angle (R–Y) to (B–Y)<br>Angle Adjustment (R–Y)<br>DC Bias Voltage                                                                                                                                                                                             |                                                                                     | -<br>19<br>19 | Øm<br>Ưm<br>V <sub>1</sub> 9                                 |                 | ±5<br>0.25<br>6.4          | -<br>-<br>-            | Deg<br>Deg/µA<br>Vdc   |

| CHROMINANCE AND LUMINANCE                                                                                                                                                                                                                                                |                                                                                     |               |                                                              |                 |                            |                        |                        |

| Chroma Input DC Level<br>Chroma Input Level for 100% Saturation                                                                                                                                                                                                          |                                                                                     | 10            | Vin                                                          | -               | 4.0<br>0.7                 |                        | Vdc<br>V <sub>pp</sub> |

| Chroma Input: Resistance<br>Capacitance                                                                                                                                                                                                                                  |                                                                                     |               | R <sub>in</sub><br>C <sub>in</sub>                           |                 | 10<br>2.0                  |                        | kΩ<br>pF               |

| Chroma DC Output Level<br>Chroma Output Level at 100% Saturation                                                                                                                                                                                                         |                                                                                     | 13            | Vout                                                         | 8.9<br>-        | 10<br>1.0                  | 10.9<br>-              | Vdc<br>V <sub>pp</sub> |

| Chroma Output Resistance                                                                                                                                                                                                                                                 |                                                                                     |               | R <sub>out</sub>                                             | -               | 50                         | -                      | Ω                      |

| Luminance Bandwidth (-3.0 dB), Less Delay Line                                                                                                                                                                                                                           |                                                                                     | 9             | BW <sub>Luma</sub>                                           | I               | 8.0                        | -                      | MHz                    |

## **ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = 12 Vdc, $T_A$ = 25°C, circuit of Figure 7, unless otherwise noted.)

| Characteristics                                                                              | Pins    | Symbol                               | Min              | Тур                      | Max              | Unit             |

|----------------------------------------------------------------------------------------------|---------|--------------------------------------|------------------|--------------------------|------------------|------------------|

| VIDEO INPUT                                                                                  |         | •                                    | •                | •                        | •                | •                |

| R, G, B Input DC Levels                                                                      | 3, 4, 5 | RGB                                  | 2.8              | 3.3                      | 3.8              | Vdc              |

| R, G, B Input for 100% Color Saturation                                                      |         |                                      | -                | 1.0                      | -                | V <sub>pp</sub>  |

| R, G, B Input: Resistance<br>Capacitance                                                     |         | R <sub>RGB</sub><br>C <sub>RGB</sub> | 8.0<br>-         | 10<br>2.0                | 17<br>-          | kΩ<br>pF         |

| Sync Input Resistance (1.7 V < Input < 8.2)                                                  | 2       | Sync                                 | -                | 10                       | -                | kΩ               |

| COMPOSITE VIDEO OUTPUT                                                                       |         | •                                    | •                | •                        | •                |                  |

| Composite Output,<br>100% Saturation<br>(see Figure 8d) Sync<br>Luminance<br>Chroma<br>Burst | 9       | CV <sub>out</sub>                    | -<br>-<br>-<br>- | 0.6<br>1.4<br>1.7<br>0.6 | -<br>-<br>-<br>- | V <sub>pp</sub>  |

| Output Impedance (Note 1)                                                                    |         | R <sub>video</sub>                   | -                | 50                       | -                | Ω                |

| Subcarrier Leakage in Output (Note 2)                                                        |         | Vlk                                  | -                | 20                       | -                | mV <sub>pp</sub> |

**NOTES:** 1. Output Impedance can be reduced to less than 10  $\Omega$  by using a 150  $\Omega$  output load from Pin 9 to ground. Power supply current will increase to about 60 mA.

2. Subcarrier leakage can be reduced to less than 10 mV with optional circuitry (see Figure 12).

## **PIN FUNCTION DESCRIPTIONS**

| Symbol               | Pin | Description                                                                                                                                                         |  |

|----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| tr                   | 1   | External components at this pin set the rise time of the internal ramp function generator (see Figure 10).                                                          |  |

| Sync                 | 2   | Composite sync input. Presents 10 k $\Omega$ resistance to input.                                                                                                   |  |

| R                    | 3   | Red signal input. Presents 10 k $\Omega$ impedance to input. 1.0 V <sub>pp</sub> required for 100% saturation.                                                      |  |

| G                    | 4   | Green signal input. Presents 10 k $\Omega$ impedance to input. 1.0 Vpp required for 100% saturation.                                                                |  |

| В                    | 5   | Blue signal Input. Presents 10 k $\Omega$ impedance to input. 1.0 V <sub>pp</sub> required for 100% saturation.                                                     |  |

| -Yout                | 6   | Luma (-Y) output. Allows external setting of luma delay time.                                                                                                       |  |

| V <sub>clamp</sub>   | 7   | Video Clamp pin. Typical connection is a 0.01 $\mu$ F capacitor to ground.                                                                                          |  |

| -Y <sub>in</sub>     | 8   | Luma (-Y) input. Presents 10 kΩ input impedance.                                                                                                                    |  |

| CVout                | 9   | Composite Video output. 50 $\Omega$ output impedance.                                                                                                               |  |

| Chroma <sub>In</sub> | 10  | Chroma input. Presents 10 k $\Omega$ input impedance.                                                                                                               |  |

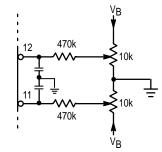

| B-Y <sub>clamp</sub> | 11  | B–Y clamp. Clamps B–Y during blanking with a 0.1 $\mu$ F capacitor to ground.<br>Also used with R–Y clamp to null residual color subcarrier in output.              |  |

| R-Y <sub>clamp</sub> | 12  | R–Y clamp. Clamps R–Y during blanking with a 0.1 $\mu$ F capacitor to ground.<br>Also used with B–Y clamp to null residual color subcarrier in output.              |  |

| ChromaOut            | 13  | Chroma output. 50 $\Omega$ output impedance.                                                                                                                        |  |

| VCC                  | 14  | Power supply pin for the IC; +12, $\pm$ 2.0 V, required at 35 mA (typical).                                                                                         |  |

| Gnd                  | 15  | Ground pin.                                                                                                                                                         |  |

| VB                   | 16  | 8.2 V reference from an internal regulator capable of delivering 10 mA to external circuitry.                                                                       |  |

| Osc <sub>in</sub>    | 17  | Oscillator input. A transistor base presents 5.0 k $\Omega$ to an external subcarrier input, or is available for constructing a Colpitts oscillator (see Figure 4). |  |

| Osc <sub>out</sub>   | 18  | Oscillator output. The emitter of the transistor, with base access at Pin 17, is accessible for completing the Colpitts oscillator. See Figure 4.                   |  |

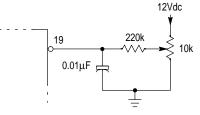

| Ø <sub>m</sub>       | 19  | Quad decoupler. With external circuitry, R–Y to B–Y relative angle errors can be corrected. Typically, requires a 0.01 µF capacitor to ground.                      |  |

| NTSC/PAL<br>Select   | 20  | NTSC/PAL switch. When grounded, the MC1377 is in the NTSC mode; if unconnected, in the PAL mode.                                                                    |  |

#### FUNCTIONAL DESCRIPTION

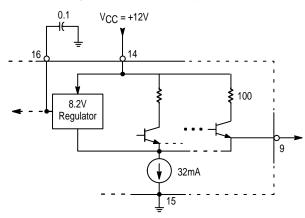

#### Figure 2. Power Supply and VB

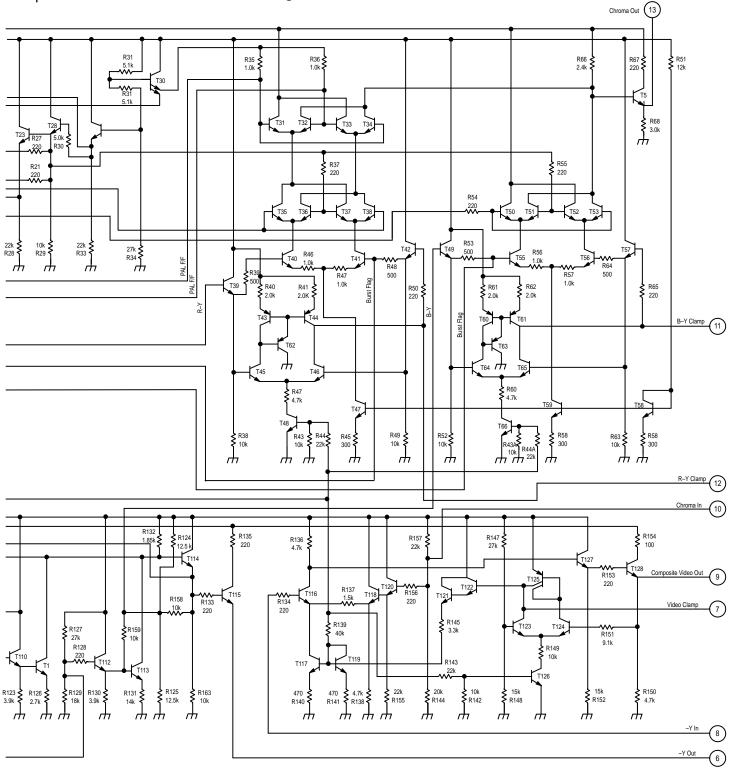

Figure 4. Chroma Section

#### Power Supply and VB (8.2 V Regulator)

The MC1377 pin for power supply connection is Pin 14. From the supply voltage applied to this pin, the IC biases internal output stages and is used to power the 8.2 V internal regulator (V<sub>B</sub> at Pin 16) which biases the majority of internal circuitry. The regulator will provide a nominal 8.2 V and is capable of 10 mA before degradation of performance. An equivalent circuit of the supply and regulator is shown in Figure 2.

#### R, G, B Inputs

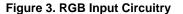

The RGB inputs are internally biased to 3.3 V and provide 10 k $\Omega$  of input impedance. Figure 3 shows representative input circuitry at Pins 3, 4, and 5.

The input coupling capacitors of 15  $\mu$ F are used to prevent tilt during the 50/60 Hz vertical period. However, if it is desired to avoid the use of the capacitors, then inputs to Pins 3, 4, and 5 can be dc coupled provided that the signal levels are always between 2.2 V and 4.4 V.

After input, the separate RGB information is introduced to the matrix circuitry which outputs the R–Y, B–Y, and –Y signals. The –Y information is routed out at Pin 6 to an external delay line (typically 400 ns).

#### **DSBSC Modulators and 3.58 MHz Oscillator**

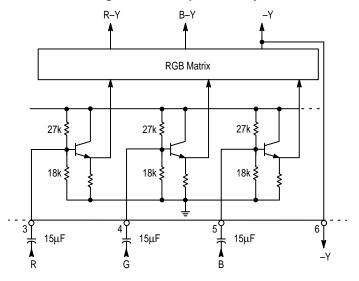

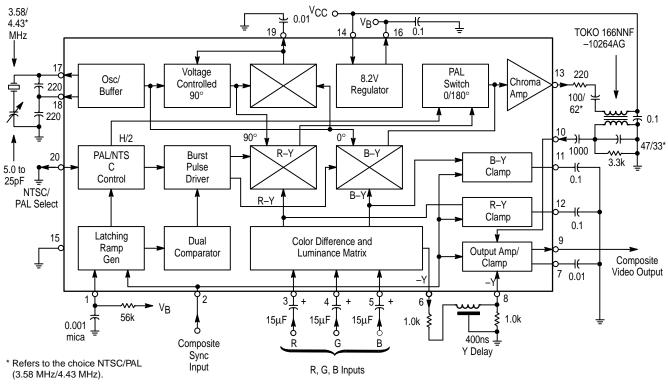

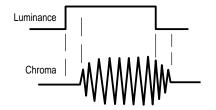

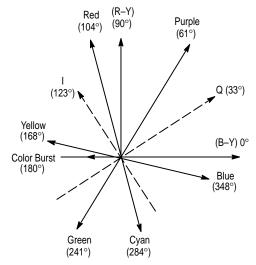

The R–Y and B–Y outputs (see (B–Y)/(R–Y) Axes versus I/Q Axes, Figure 22) from the matrix circuitry are amplitude modulated onto the 3.58/4.43 MHz subcarrier. These signals are added and color burst is included to produce composite chroma available at Pin 13. These functions plus others, depending on whether NTSC or PAL operation is chosen, are performed in the chroma section. Figure 4 shows a block diagram of the chroma section.

The MC1377 has two double balanced mixers, and regardless of which mode is chosen (NTSC or PAL), the mixers always perform the same operation. The B–Y mixer modulates the color subcarrier directly, the R–Y mixer receives a  $90^{\circ}$  phase shifted color subcarrier before being modulated by the R–Y baseband information. Additional operations are then performed on these two signals to make them NTSC or PAL compatible.

In the NTSC mode, the NTSC/PAL control circuitry allows an inverted burst of 3.58 MHz to be added only to the B–Y signal. A gating pulse or "burst flag" from the timing section permits color burst to be added to the B–Y signal. This color burst is 180° from the B–Y signal and 90° away from the R–Y signal (see Figure 22) and permits decoding of the color information. These signals are then added and amplified before being output, at Pin 13, to be bandpassed and then reintroduced to the IC at Pin 10.

In the PAL mode, NTSC/PAL control circuitry allows an inverted 4.43 MHz burst to be added to both R–Y and B–Y equally to produce the characteristic PAL 225°/135 burst phase. Also, the R–Y information is switched alternately from 180° to 0° of its original position and added to the B–Y information to be amplified and output.

#### **Timing Circuitry**

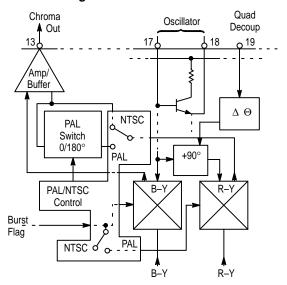

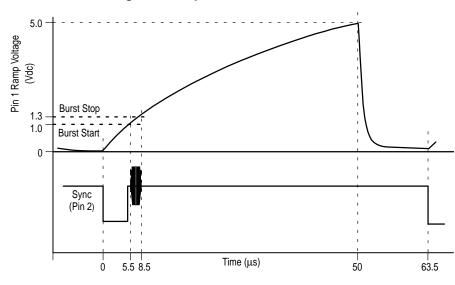

The composite sync input at Pin 2 performs three important functions: it provides the timing (but not the amplitude) for the sync in the final output; it drives the black level clamps in the modulators and output amplifier; and it triggers the ramp generator at Pin 1, which produces burst envelope and PAL switching. A representative block diagram of the timing circuitry is shown in Figure 5.

In order to produce a color burst, a burst envelope must be generated which "gates" a color subcarrier into the R-Y and B-Y modulators. This is done with the ramp generator at Pin 1.

The ramp generator at Pin 1 is an R–C type in which the pin is held low until the arrival of the *leading* edge of sync. The rising ramp function, with time constant R–C, passes through two level sensors – the first one starts the gating pulse and the second stops it (see Figure 10). Since the "early" part of the exponential is used, the timing provided is relatively accurate from chip–to–chip and assembly–to–assembly. Fixed components are usually adequate. The ramp continues to rise for more than half of the line interval, thereby inhibiting burst generation on "half interval" pulses on vertical front and back porches. The ramp method will produce burst on the vertical front and back "porches" at full line intervals.

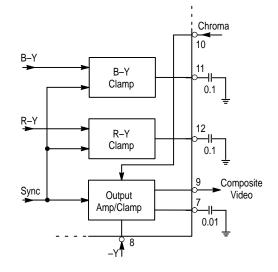

#### R-Y, B-Y Clamps and Output Clamp/Amplifier

The sync signal, shown in the block diagram of Figure 6, drives the R–Y and B–Y clamps which clamp the R–Y and B–Y signals to reference black during the blanking periods. The output amplifier/clamp provides this same function plus combines and amplifies the chroma and luma components for composite video output.

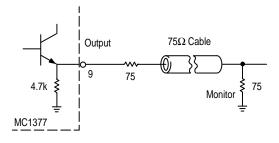

#### **Application Circuit**

Figure 7 illustrates the block diagram of the MC1377 and the external circuitry required for typical operation.

Figure 5. Timing Circuitry

Figure 6. R-Y, B-Y and Output Amplifier Clamps

## Figure 7. Block Diagram and Application Circuit

#### MOTOROLA ANALOG IC DEVICE DATA

6

#### **APPLICATION INFORMATION**

#### R, G, B Input Levels

The signal levels into Pins 3, 4, 5 should be 1.0 V<sub>pp</sub> for fully saturated, standard composite video output levels as shown in Figure 9(d). The inputs require 1.0 V<sub>pp</sub> since the internally generated sync pulse and color burst are at fixed and predetermined amplitudes.

Further, it is essential that the portion of each input which occurs during the sync interval represent black for that input since that level will be clamped to reference black in the color modulators and output stage. This implies that a refinement, such as a difference between black and blanking levels, must be incorporated in the RGB input signals.

If Y, R–Y, B–Y and burst flag components are available and the MC1377 is operating in NTSC, inputs may be as follows: the Y component can be coupled through a 15 pF capacitor to Pins 3, 4 and 5 tied together; the (–[R–Y]) component can be coupled to Pin 12 through a 0.1  $\mu$ F capacitor, and the (–[B–Y]) and burst flag components can be coupled to Pin 11 in a similar manner.

#### Sync Input

As shown in Figure 9(e), the sync input amplitude can be varied over a wide latitude, but will require bias pull–up from most sync sources. The important requirements are:

- 1) The voltage level between sync pulses must be between 1.7 V and 8.2 V, see Figure 9(e).

- 2) The voltage level for the sync tips must be between +0.9 V and -0.5 V, to prevent substrate leakage in the IC, see Figure 9(e).

- 3) The width of the sync pulse should be no longer than 5.2  $\mu$ s and no shorter than 2.5  $\mu$ s.

For PAL operation, correctly serrated vertical sync is necessary to properly trigger the PAL divider. In NTSC mode, simplified "block" vertical sync can be used but the loss of proper horizontal timing may cause "top hook" or "flag waving" in some monitors. An interesting note is that composite video can be used directly as a sync signal, provided that it meets the sync input criteria.

#### Latching Ramp (Burst Flag) Generator

The recommended application is to connect a close tolerance (5%) 0.001  $\mu$ F capacitor from Pin 1 to ground and a resistor of 51 k $\Omega$  or 56 k $\Omega$  from Pin 1 to V<sub>B</sub> (Pin 16). This will produce a burst pulse of 2.5  $\mu$ s to 3.5  $\mu$ s in duration, as shown in Figure 10. As the ramp on Pin 1 rises toward the charging voltage of 8.2 V, it passes first through a burst "start threshold" at 1.0 V, then a "stop threshold" at 1.3 V, and finally a ramp reset threshold at 5.0 V. If the resistor is reduced to 43 k $\Omega$ , the ramp will rise more quickly, producing a narrower and earlier burst pulse (starting approx. 0.4  $\mu$ s after sync and about 0.6  $\mu$ s wide). The burst will be wider and later if the resistor is raised to 62 k $\Omega$ , but more importantly, the 5.0 V reset point may not be reached in one full line interval, resulting in loss of alternate burst pulses.

As mentioned earlier, the ramp method does produce burst at full line intervals on the "vertical porches." If this is not desired, and the MC1377 is operating in the NTSC mode, burst flag may be applied to Pin 1 provided that the tip of the pulse is between 1.0 Vdc and 1.3 Vdc. In PAL mode this method is not suitable, since the ramp isn't available to drive the PAL flip–flop. Another means of inhibiting the burst pulse is to set Pin 1 either above 1.3 Vdc or below 1.0 Vdc for the duration that burst is not desired.

#### Color Reference Oscillator/Buffer

As stated earlier in the general description, there is an on-board common collector Colpitts color reference oscillator with the transistor base at Pin 17 and the emitter at Pin 18. When used with a common low-cost TV crystal and capacitive divider, about 0.6  $V_{pp}$  will be developed at Pin 17. The frequency adjustment can be done with a series 30 pF trimmer capacitor over a total range of about 1.0 kHz. Oscillator frequency should be adjusted for each unit, keeping in mind that most monitors and receivers can pull in 1200 Hz.

If an external color reference is to be used exclusively, it must be continuous. The components on Pins 17 and 18 can be removed, and the external source capacitively coupled into Pin 17. The input at Pin 17 should be a sine wave with amplitude between 0.5 V<sub>pp</sub> and 1.0 V<sub>pp</sub>.

Also, it is possible to do both; i.e., let the oscillator "free run" on its own crystal and override with an external source. An extra coupling capacitor of 50 pF from the external source to Pin 17 was adequate with the experimentation attempted.

#### Voltage Controlled 90°

The oscillator drives the (B–Y) modulator and a voltage controlled phase shifter which produces an oscillator phase of  $90^{\circ} \pm 5^{\circ}$  at the (R–Y) modulator. In most situations, the result of an error of  $5^{\circ}$  is very subtle to all but the most expert eye. However, if it is necessary to adjust the angle to better accuracy, the circuit shown in Figure 11 can be used.

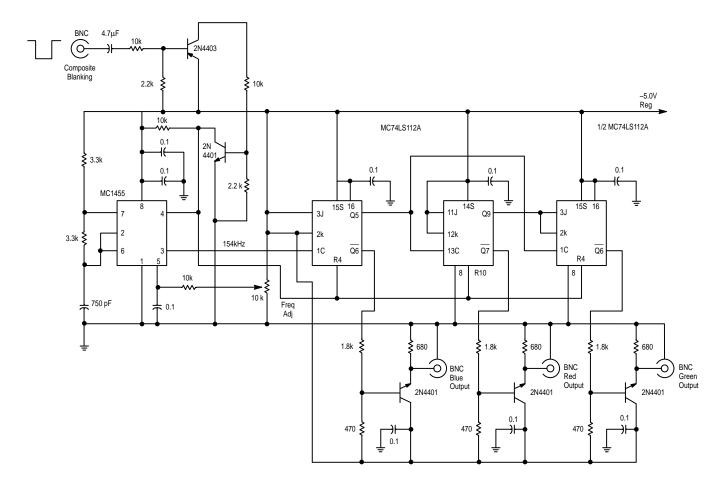

Pulling Pin 19 up will increase the (R–Y) to (B–Y) angle by about  $0.25^{\circ}/\mu$ A. Pulling Pin 19 down reduces the angle by the same sensitivity. The nominal Pin 19 voltage is about 6.3 V, so even though it is unregulated, the 12 V supply is best for good control. For effective adjustment, the simplest approach is to apply RGB color bar inputs and use a vectorscope. A simple bar generator giving R, G, and B outputs is shown in Figure 26.

#### Figure 9. Ramp/Burst Gate Generator

#### **Residual Feedthrough Components**

As shown in Figure 9(d), the composite output at Pin 9 for fully saturated color bars is about 2.6  $V_{pp}$ , output with full chroma on the largest bars (cyan and red) being 1.7  $V_{pp}$ . The typical device, due to imperfections in gain, matrixing, and modulator balance, will exhibit about 20 m $V_{pp}$  residual color subcarrier in both white and black. Both residuals can be reduced to less than 10 m $V_{pp}$  for the more exacting applications.

The subcarrier feedthrough in black is due primarily to imbalance in the modulators and can be nulled by sinking or sourcing small currents into clamp Pins 11 and 12 as shown in Figure 12. The nominal voltage on these pins is about 4.0 Vdc, so the 8.2 V regulator is capable of supplying a pull up source. Pulling Pin 11 down is in the 0° direction, pulling it up is towards 180°. Pulling Pin 12 down is in the 90° direction, pulling it up is towards 270°. Any direction of correction may be required from part to part.

White carrier imbalance at the output can only be corrected by juggling the relative levels of R, G, and B inputs for perfect balance. Standard devices are tested to be within 5% of balance at full saturation. Black balance should be adjusted first, because it affects all levels of gray scale equally. There is also usually some residual baseband video at the chroma output (Pin 13), which is most easily observed by disabling the color oscillator. Typical devices show  $0.4 V_{pp}$  of residual luminance for saturated color bar inputs. This is not a major problem since Pin 13 is always coupled to Pin 10 through a bandpass or a high pass filter, but it serves as a warning to pay proper attention to the coupling network.

#### Figure 10. Adjusting Modulator Angle

#### Figure 11. Nulling Residual Color in Black

#### Figure 12. Delay of Chroma Information

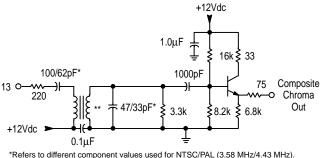

#### The Chroma Coupling Circuits

With the exception of S–VHS equipped monitors and receivers, it is generally true that most monitors and receivers have color IF 6.0 dB bandwidths limited to approximately  $\pm$ 0.5 MHz. It is therefore recommended that the encoder circuit should also limit the chroma bandwidth to approximately  $\pm$ 0.5 MHz through insertion of a bandpass circuit between Pin 13 and Pin 10. However, if S–VHS operation is desired, a coupling circuit which outputs the composite chroma directly for connection to a S–VHS terminal is given in the S–VHS application (see Figure 19).

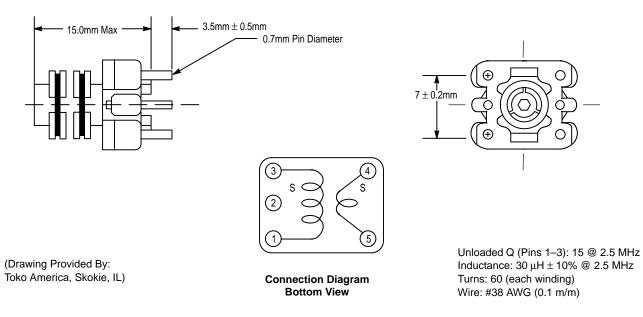

For proper color level in the video output, a  $\pm 0.5$  MHz bandwidth and a midband insertion loss of 3.0 dB is desired. The bandpass circuit shown in Figure 7, using the TOKO fixed tuned transformer, couples Pin 10 to Pin 13 and gives this result. However, this circuit introduces about 350 ns of delay to the chroma information (see Figure 13). This must be accounted for in the luminance path.

A 350 ns delay results in a visible displacement of the color and black and white information on the final display. The solution is to place a delay line in the luminance path from Pins 6 to 8, to realign the two components. A normal TV receiver delay line can be used. These delay lines are usually of 1.0 k $\Omega$  to 1.5 k $\Omega$  characteristic impedance, and the resistors at Pins 6 and 8 should be selected accordingly. A very compact, lumped constant delay line is available from TDK (see Figure 25 for specifications). Some types of delay lines have very low impedances (approx. 100  $\Omega$ ) and should not be used, due to drive and power dissipation requirements.

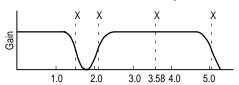

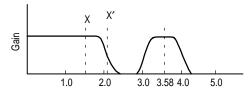

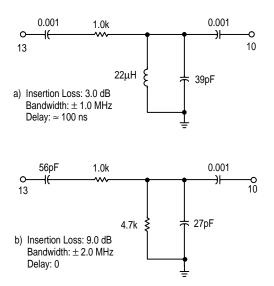

In the event of very low resolution RGB, the transformer and the delay line may be omitted from the circuit. Very low resolution for the MC1377 can be considered RGB information of less than 1.5 MHz. However, in this situation, a bandwidth reduction scheme is still recommended due to the response of most receivers. Figure 14(a) shows the output of the MC1377 with low resolution RGB inputs. If no bandwidth reduction is employed then a monitor or receiver with frequency response shown in Figure 14(b), which is fairly typical of non–comb filtered monitors and receivers, will detect an incorrect luma sideband at X'. This will result in cross–talk in the form of chroma information in the luma channel. To avoid this situation, a simpler bandpass circuit as shown in Figure 15(a), can be used.

Figure 13. MC1377 Output with Low Resolution RGB Inputs

(a) Encoder Output with Low Resolution Inputs and No Bandpass Transformer

(b) Standard Receiver Response

A final option is shown in Figure 15(b). This circuit provides very little bandwidth reduction, but enough to remove the chroma to luma feedthrough, with essentially no delay. There is, however, about a 9 dB insertion loss from this network.

It will be left to the designer to decide which, if any, compromises are acceptable. Color bars viewed on a good monitor can be used to judge acceptability of step luminance/chrominance alignment and step edge transients, but signals containing the finest detail to be encountered in the system must also be examined before settling on a compromise.

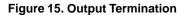

#### The Output Stage

The output amplifier normally produces about 2.0 Vpp and is intended to be loaded with 150  $\Omega$  as shown in Figure 16. This provides about 1.0  $V_{pp}$  into 75  $\Omega,$  an industry standard level (RS-343). In some cases, the input to the monitor may be through a large coupling capacitor. If so, it is necessary to connect a 150  $\Omega$  resistor from Pin 9 to ground to provide a low impedance path to discharge the capacitor. The nominal average voltage at Pin 9 is over 4.0 V. The 150  $\Omega$  dc load causes the current supply to rise another 30 mA (to approximately 60 mA total into Pin 14). Under this (normal) condition the total device dissipation is about 600 mW. The calculated worst case die temperature rise is 60°C, but the typical device in a test socket is only slightly warm to the touch at room temperature. The solid copper 20-pin lead frame in a printed circuit board will be even more effectively cooled.

#### Figure 14. Optional Chroma Coupling Circuits

#### **Power Supplies**

The MC1377 is designed to operate from an unregulated 10 V to 14 Vdc power supply. Device current into Pin 14 with open output is typically 35 mA. To provide a stable reference for the ramp generator and the video output, a high quality 8.2 V regulator can supply up to 10 mA for external uses,

with an effective source impedance of less than 1.0  $\Omega$ . This regulator is convenient for a tracking dc reference for dc coupling the output to an RF modulator. Typical turn–on drift for the regulator is approximately –30 mV over 1 to 2 minutes in otherwise stable ambient conditions.

#### SUMMARY

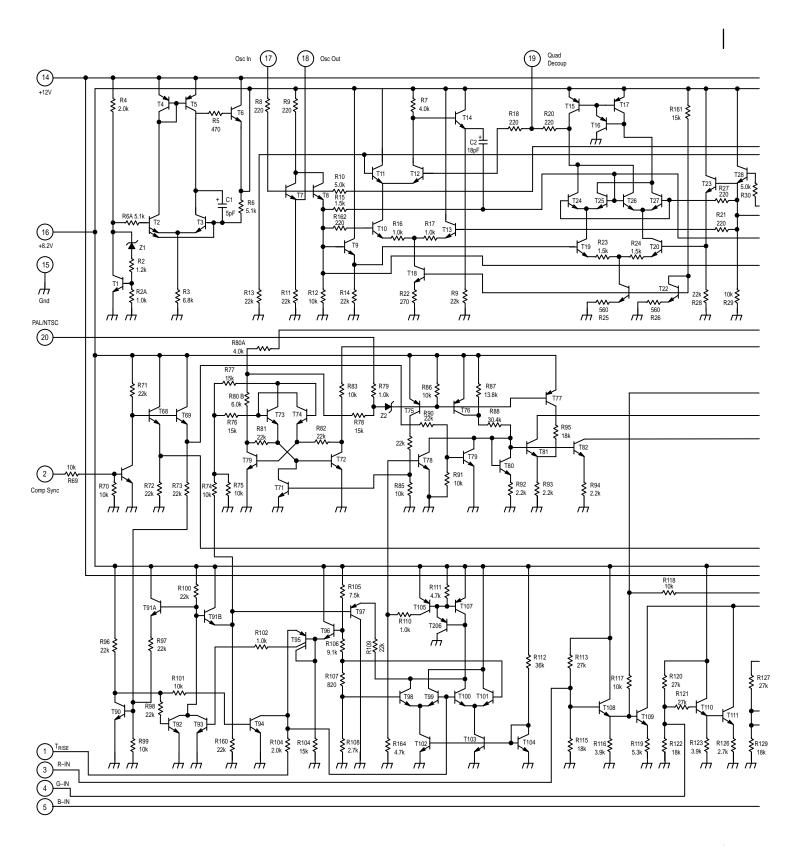

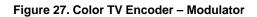

The preceding information was intended to detail the application and basis of circuit choices for the MC1377. A complete MC1377 application with the MC1374 VHF modulator is illustrated in Figure 17. The internal schematic diagram of the MC1377 is provided in Figure 8.

#### Figure 16. Application with VHF Modulator

#### **APPLICATIONS INFORMATION**

#### S-VHS

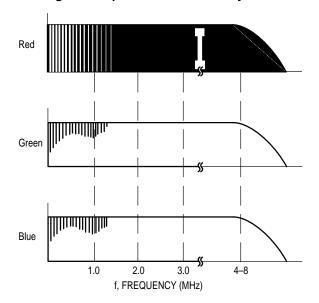

In full RGB systems (Figure 18), three information channels are provided from the signal source to the display to permit unimpaired image resolution. The detail reproduction of the system is limited only by the signal bandwidth and the capability of the color display device. Also, higher than normal sweep rates may be employed to add more lines within a vertical period and three separate projection picture tubes can be used to eliminate the "shadow mask" limitations of a conventional color CRT.

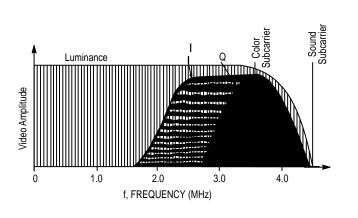

Figure 21 shows the "baseband" components of a studio NTSC signal. As in the previous example, energy is concentrated at multiples of the horizontal sweep frequency. The system is further refined by precisely locating the color subcarrier midway between luminance spectral components. This places all color spectra between luminance spectra and can be accomplished in the MC1377 only if "full interlaced" external color reference and sync are applied. The individual components of luminance and color can then be separated by the use of a comb filter in the monitor or receiver. This technique has not been widely used in consumer products, due to cost, but it is rapidly becoming less expensive and more common. Another technique which is gaining popularity is S-VHS (Super VHS).

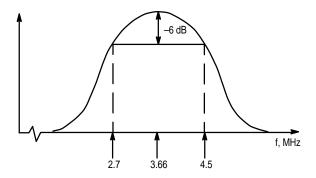

In S–VHS, the chroma and luma information are contained on separate channels. This allows the bandwidth of both the chroma and luma channels to be as wide as the monitors ability to reproduce the extra high frequency information. An output coupling circuit for the composite chroma using the TOKO transformer is shown in Figure 19. It is composed of the bandpass transformer and an output buffer and has the frequency performance shown in Figure 20. The composite output (Pin 9) then produces the luma information as well as composite sync and blanking.

Figure 17. Spectra of a Full RGB System

**Chroma Coupling Circuit**

\*\*Toko 166NNF-1026AG

Figure 19. Frequency Response of

#### I/Q System versus (R-Y)/(B-Y) System

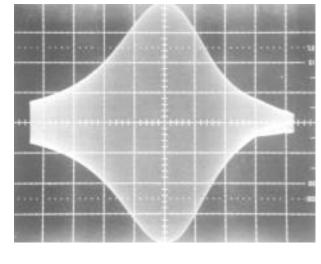

The NTSC standard calls for unequal bandwidths for I and Q (Figure 21). The MC1377 has no means of processing the unequal bandwidths because the I and Q axes are not used (Figure 22) and because the outputs of the (R-Y) and the (B-Y) modulators are added before being output at Pin 13. Therefore, any bandwidth reduction intended for the chroma information must be performed on the composite chroma information. This is generally not a problem, however, since most monitors compromise the standard quite a bit.

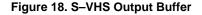

Figure 23 shows the typical response of most monitors and receivers. This figure shows that some crosstalk between luma and chroma information is always present. The acceptability of the situation is enhanced by the limited ability of the CRT to display information above 2.5 MHz. If the signal from the MC1377 is to be used primarily to drive conventional non-comb filtered monitors or receivers, it would be best to reduce the bandwidth at the MC1377 to that of Figure 23 to lessen crosstalk.

Figure 20. NTSC Standard Spectral Content

#### Figure 22. Frequency Response of Typical Monitor/TV

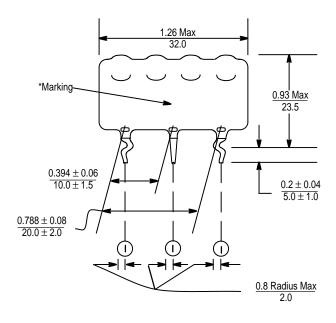

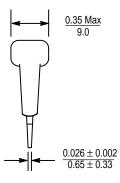

#### Figure 23. A Prototype Chroma Bandpass Transformer Toko Sample Number 166NNF–10264AG

Figure 24. A Prototype Delay Line TDK Sample Number DL122301D–1533

\*Marking: Part Number, Manufacturer's Identification, Date Code and Lead Number. Skokie, IL (TDK Corporation of America)

| Item                          | Specifications        |  |  |

|-------------------------------|-----------------------|--|--|

| Time Delay                    | 400 ns ± 10%          |  |  |

| Impedance                     | $1200~\Omega\pm10\%$  |  |  |

| Resistance                    | Less Than 15 $\Omega$ |  |  |

| Transient Response with 20 ns | Preshoot: 10% Max     |  |  |

| Rise Time Input Pulse         | Overshoot: 10% Max    |  |  |

|                               | Rise Time: 120 ns Max |  |  |

| Attenuation                   | 3 dB Max at 6.0 MHz   |  |  |

14

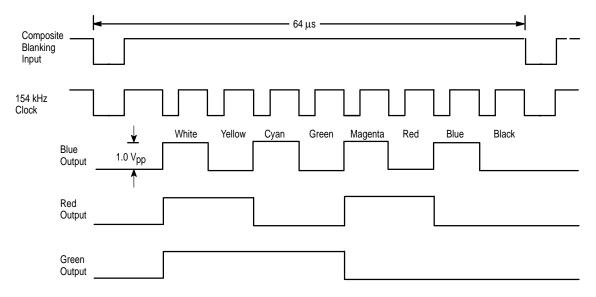

#### Figure 25. RGB Pulse Generator

#### **RGB Pulse Generator Timing Diagram for NTSC**

MOTOROLA ANALOG IC DEVICE DATA

Figure 26. Printed Circuit Boards for the MC1377

(CIRCUIT SIDE)

(COMPONENT SIZE)

16

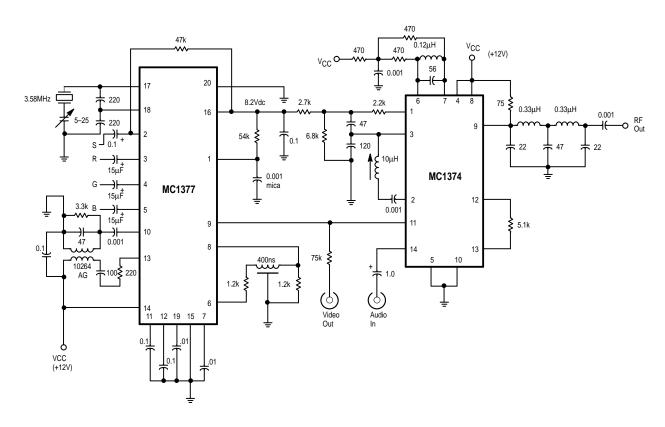

#### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death Motorola was negligent regarding the design or manuforizet of the part. Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE (602) 244–6609 INTERNET: http://Design-NET.com

HONG KONG: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298