## **Freescale Semiconductor**

### **Technical Data**

Document Number: MC13883

Rev. 3, 02/2010

## MC13883

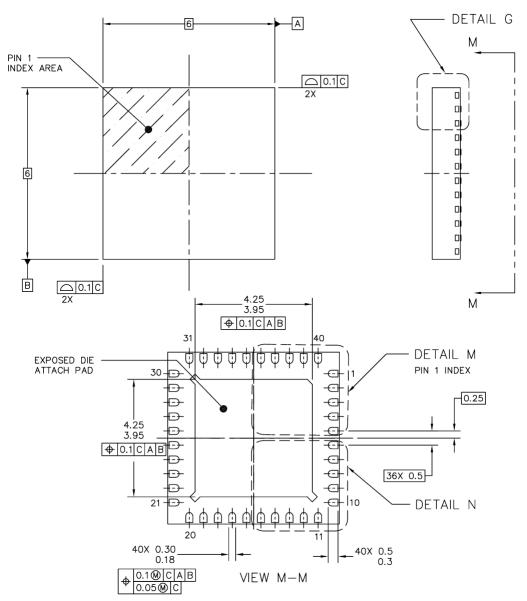

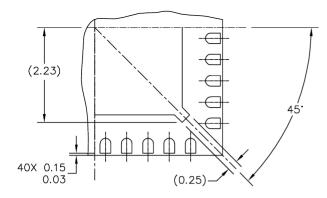

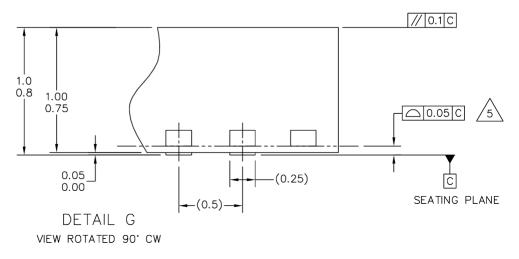

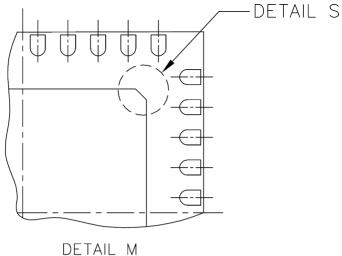

# Package Information Plastic Package Case 1624

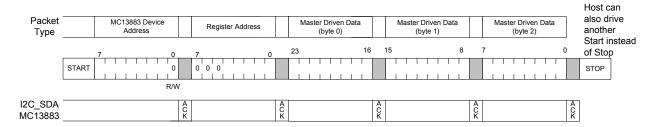

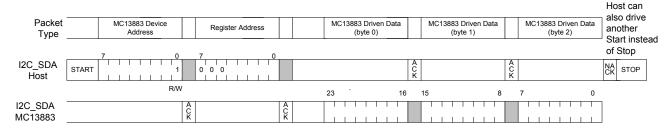

#### **Ordering Information**

| Device     | Device Marking or<br>Operating<br>Temperature Range | Package |

|------------|-----------------------------------------------------|---------|

| MC13883EP4 | -30 to +85° C                                       | QFN-40  |

## MC13883

## Integrated Charger USB Interface

## 1 Introduction

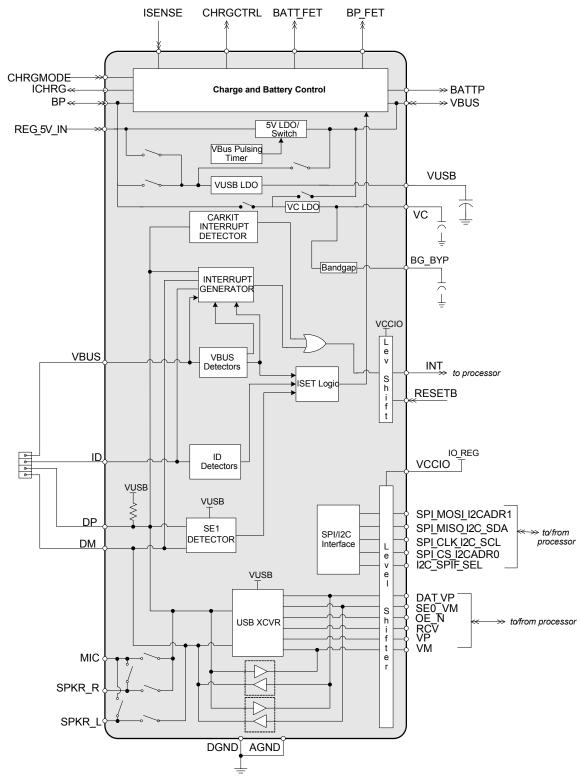

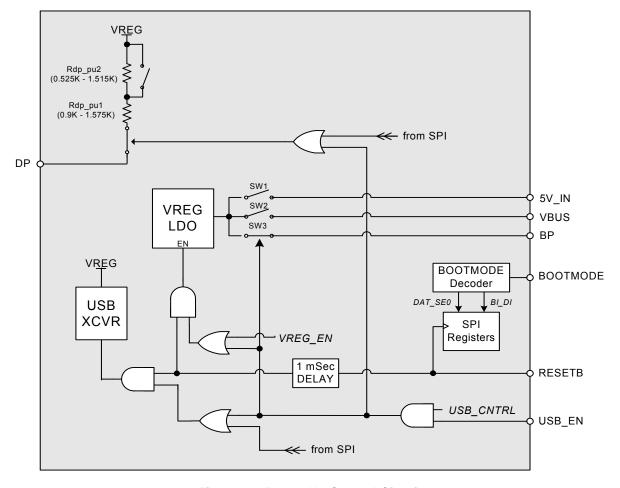

The MC13883 integrated charger, USB on-the-go transceiver, and carkit interface incorporates support for the CEA-936-A carkit specification. The MC13883 provides charging from a variety of sources, USB connectivity (including on-the-go, OTG), as well as support for phone-powered accessories. The MC13883 is an "all in one" IC that integrates nearly the entire interface, Li-Ion battery charging, and transceiver circuitry required to support these functions.

## 1.1 Key Features

- Allows charging of the phone through the USB connector

- Over-voltage protection for protecting the phone from faulty (high voltage) charging sources

- Reverse mode for charge path allows power to be sourced to the VBUS pin from the battery. This can be used to support phone powered device as described in the CEA-936-A standard.

- USB 2.0/OTG transceiver

#### **Contents**

| 1 | Introduction 1               |

|---|------------------------------|

| 2 | Signal Descriptions 4        |

| 3 | Electrical Characteristics 6 |

| 4 | Power Architecture 7         |

| 5 | Connectivity 29              |

| 6 | Serial Interface 48          |

| 7 | SPI/I2C Register Tables 54   |

| 8 | Packaging Information 60     |

| 9 | Product Documentation 64     |

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2005–2010. All rights reserved.

#### Introduction

- UART and audio signaling follow the protocol defined by CEA-936-A carkit specification

- 6 x 6 mm QFN-40 package

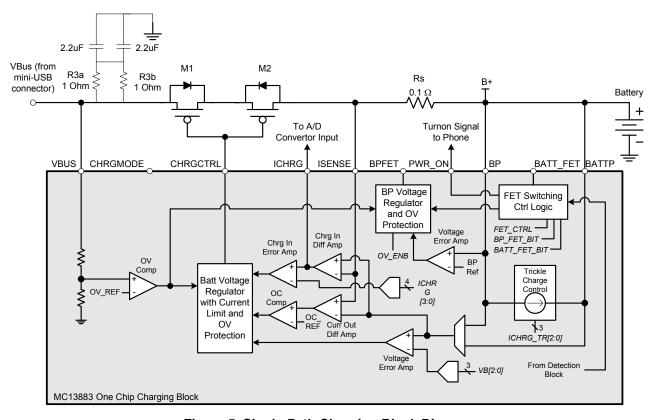

Figure 1. Block Diagram

MC13883 Technical Data, Rev. 3

### 1.2 Power Overview

### 1.2.1 Charging

The MC13883 allows charging of the phone via the mini-USB VBUS pin. This pin sources power from a variety of devices including wall chargers and carkits, as well as sources that traditionally are not used in charging. Specifically, the MC13883 allows the phone to be charged from a PC via a USB port. While this is a very useful feature from an end-user perspective, it is a feature that adds some additional requirements to the bus due to the unique limitations and requirements the USB specification places on devices that are attached to a USB port. The MC13883 simplifies the task of identifying whether a PC or a "traditional" charger is attached to the phone, allowing for a fairly simple methodology for handling these situations-a methodology that is not burdensome to the phone in terms of hardware or software cost and complexity.

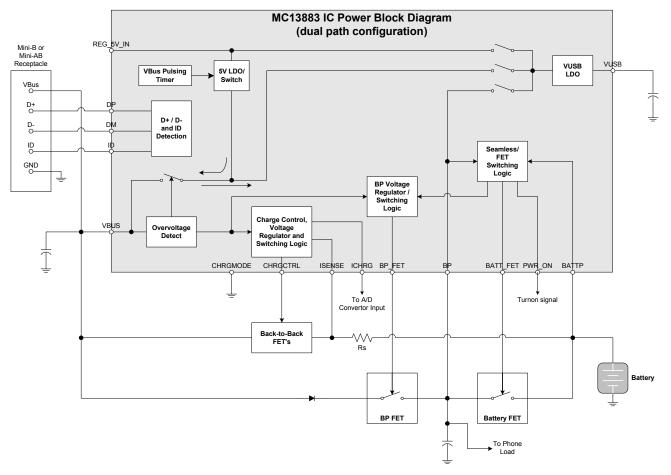

The charge circuitry can be configured as "dual path" charging. This means the power from the charge supply is routed simultaneously to both the battery for charging and the phone B+ point to operate the phone. It can also be configured for "single path" charging, in which case charge power is only routed to the battery and from the battery to the phone's B+ point. Or it can be configured as "serial path", in which case the charger powers the phone and a special trickle-charge path charges a deeply discharged battery.

# 1.2.2 Over-Voltage/Over-Current Protection and Reverse Charge Overview

The MC13883 has built-in over-voltage protection for protecting the phone from faulty (high voltage) charging sources. In addition, the MC13883 IC has the ability to place the charge path in reverse mode-allowing power to be sourced to the VBUS pin from the battery. This can be used to support phone-powered devices as described in the CEA-936-A standard. In order to protect the phone from short circuit conditions on the external pins, this path also has built-in over-current protection.

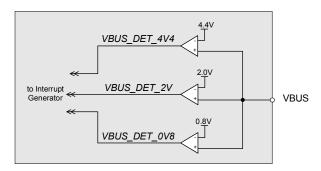

## 1.2.3 USB Voltage Generation

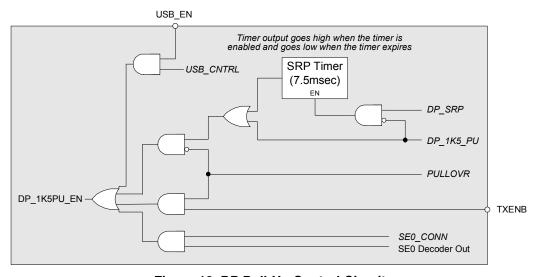

In addition to providing power to the phone to charge the battery and generate the main phone supply, the MC13883 also generates the various voltage supplies needed to support USB OTG. This includes an internal regulator to supply the USB transceiver (VUSB) as well as a 5V linear regulator to provide power out through the VBUS pin to support SRP—Session Request Protocol—a basic requirement of USB OTG.

## 1.3 Connectivity Overview

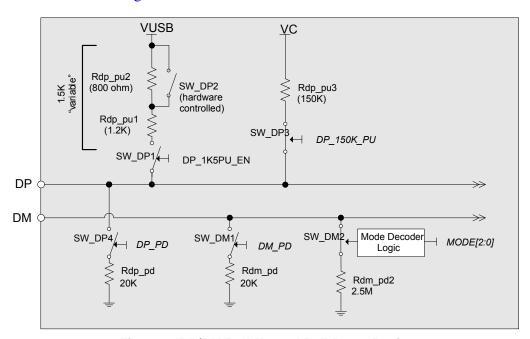

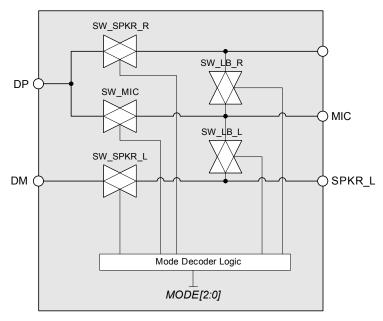

Various self powered devices (SPD) and phone powered devices (PPD) may be connected to the MC13883 interface. The phone needs to properly detect and identify each of these devices.

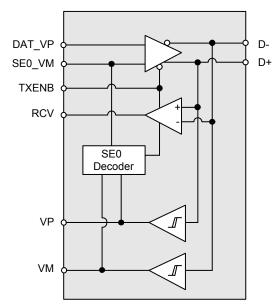

There are four signaling modes that the MC13883 bus supports: two digital data modes and two analog audio modes. Two data modes are standard USB signaling and UART signaling. Two audio modes are mono signaling and stereo signaling. The USB signaling follows the protocol defined in the USB 2.0 specification. UART and audio signaling follow the protocol defined in the CEA-936-A Carkit specification.

MC13883 Technical Data, Rev. 3

#### **Signal Descriptions**

Data and audio signaling modes share the same DP (Data Plus) and DM (Data Minus) pins of the mini-USB connector. The phone transitions between the four types of signaling modes using Signaling Negotiation Protocol (SNP) described in the CEA-936-A Carkit specification. The MC13883 bus supports both 4-wire and 5-wire protocols.

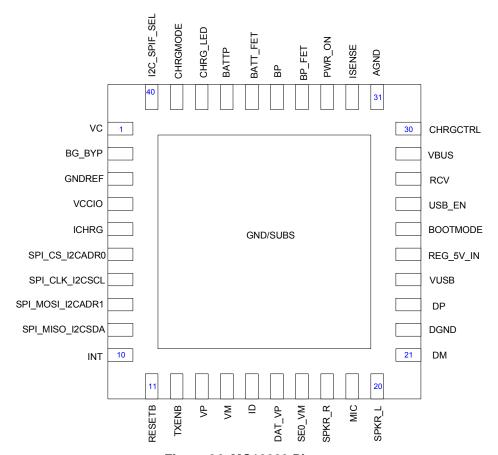

## 2 Signal Descriptions

**Table 1. Pin Descriptions**

| Pin<br># | Pin Name       | Description                                                      | Block   | I/O Supply | Туре    | I/O          |

|----------|----------------|------------------------------------------------------------------|---------|------------|---------|--------------|

| 1        | VC             | Internal supply                                                  |         |            | Analog  | Output       |

| 2        | BG_BYP         | Bandgap Bypass pin                                               | Bandgap |            | Analog  | Output       |

| 3        | GNDREF         | Ground                                                           | GND     |            | GND     | -            |

| 4        | VCCIO          | IO Supply                                                        | SPI/I2C | -          | Analog  | Input        |

| 5        | ICHRG          | Voltage proportional to the charge current.                      | Charger |            | Analog  | Output       |

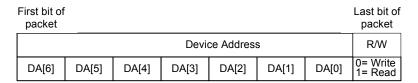

| 6        | SPICS_I2CADR   | SPI Chip Select / LSB of I2C<br>Device Address Offset            | SPI     | VCCIO      | Digital | Input        |

| 7        | SPICLK_I2CSCL  | SPI / I2C Clock                                                  | SPI/I2C | VCCIO      | Digital | Input        |

| 8        | SPIMOSI_I2CADR | SPI Master Out Slave In /<br>MSB of I2C Device Address<br>Offset | SPI/I2C | VCCIO      | Digital | Input        |

| 9        | SPIMISO_I2CSDA | SPI Master In Slave Out / I2C Data                               | SPI/I2C | VCCIO      | Digital | Input/Output |

| 10       | INT            | Interrupt signal                                                 | Control | VCCIO      | Digital | Output       |

| 11       | RESETB         | Reset Input signal                                               | SPI     | VCCIO      | Digital | Input        |

| 12       | TXENB          | USB Transmit Enable low                                          | USB     | VCCIO      | Digital | Input        |

| 13       | VP             | Dplus Receive                                                    | USB     | VCCIO      | Digital | Output       |

| 14       | VM             | Dminus Receive                                                   | USB     | VCCIO      | Digital | Output       |

| 15       | ID             | ID pin of USB connector                                          | USB     |            | Analog  | Input        |

| 16       | DAT_VP         | Data/DP input                                                    | USB     | VCCIO      | Digital | Input/Output |

| 17       | SEO_VM         | Single Ended Zero / DM input                                     | USB     | VCCIO      | Digital | Input/Output |

| 18       | SPKR_R         | Audio Right output                                               | AUDIO   | VUSB       | Analog  | Input        |

| 19       | MIC            | Microphone input                                                 | AUDIO   | VUSB       | Analog  | Output       |

| 20       | SPKR_L         | Audio Left output                                                | AUDIO   | VUSB       | Analog  | Input        |

| 21       | DM             | DM pin of USB connector                                          | USB     | VUSB       | Analog  | Input/Output |

| 22       | DGND           | Digital Ground                                                   | GND     |            | GND     | -            |

| 23       | DP             | DP pin of USB connector                                          | USB     | VUSB       | Analog  | Input/Output |

MC13883 Technical Data, Rev. 3

**Table 1. Pin Descriptions (continued)**

| Pin<br># | Pin Name     | Description                                     | Block       | I/O Supply | Туре    | I/O          |

|----------|--------------|-------------------------------------------------|-------------|------------|---------|--------------|

| 24       | VUSB         | Cap for 3.3V Vusb regulator                     | USB         |            | Analog  | Output       |

| 25       | REG_5V_IN    | VUSB Regulator input                            | USB         |            | Analog  | Input        |

| 26       | BOOTMODE     | Trinary USB transceiver mode                    | USB         | VC         | Digital | Input        |

| 27       | USB_EN       | USB Xcvr enable                                 | USB         | VCCIO      | Digital | Input        |

| 28       | RCV          | Differential Receive                            | USB         | VCCIO      | Digital | Output       |

| 29       | VBUS         | Charger Input Voltage                           | USB/Charger |            | Analog  | Input/Output |

| 30       | CHRGCTRL     | Gate driver output of Regulator                 | Charger     |            | Analog  | Output       |

| 31       | AGND         | Analog Ground                                   | GND         |            | GND     | -            |

| 32       | ISENSE       | Current Sense pin                               | Charger     |            | Analog  | Input        |

| 33       | PWR_ON       | Turnon signal to phone                          | Control     | VBUS       | Digital | Output       |

| 34       | BP_FET       | Gate driver output for BP<br>Switch             | Charger     |            | Analog  | Output       |

| 35       | BP           | Bplus                                           | Bandgap     |            | Analog  | Input        |

| 36       | BATT_FET     | Gate driver output for Battery<br>Switch        | Charger     |            | Analog  | Output       |

| 37       | BATTP        | Battery Voltage                                 | Charger     |            | Analog  | Input        |

| 38       | CHRG_LED     | Output for Sign-of-life LED indicator           |             |            |         |              |

| 39       | CHRGMODE     | Single /serial / dual path charging mode select | Control     | VC         | Digital | Input        |

| 40       | I2C_SPIF_SEL | SPI/I2C Select                                  | SPI/I2C     | VC         | Digital | Input        |

## 3 Electrical Characteristics

## 3.1 Absolute Maximum Ratings

Table 2 shows the absolute maximum voltage and temperature ratings of the MC13883 IC. Operation outside the limits shown may cause damage to the device and negatively affect performance.

**Table 2. Absolute Maximum Ratings**

| Parameter                                         | Condition | Min  | Тур | Max  | Units |

|---------------------------------------------------|-----------|------|-----|------|-------|

| VBUS, CHRGCTRL, BPFET,<br>PATH_SEL Voltage Rating | to AGND   | -0.3 | -   | 20   | V     |

| All GNDs                                          | to AGND   | -0.3 | 0   | -    | V     |

| DP, DM, ID                                        | to AGND   | -0.3 | -   | 5.25 | V     |

| ВР                                                | to AGND   | -0.3 | -   | 5.5  | V     |

| All other pins Voltage Rating                     | to AGND   | -0.3 | -   | 4.5  | V     |

| *Operating Temperature Range (Ambient)            |           | -30  | -   | 85   | °C    |

| Storage Temperature Range                         |           | -65  | -   | 150  | °C    |

| ESD Rating                                        | All pins  | 2.5  | -   |      | kV    |

| REG_5V_IN                                         | to AGND   | -    | -   | 6.0  | V     |

NOTE: Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Recommended Operating Conditions and Electrical Characteristics tables.

## 3.2 Operating Conditions

Table 3 gives the operating conditions under which the performance specifications provided in this document are guaranteed.

**Table 3. Operating Conditions**

| Parameter                                            | Condition | Min  | Тур | Max | Units |  |  |  |  |  |  |

|------------------------------------------------------|-----------|------|-----|-----|-------|--|--|--|--|--|--|

| Supply Input Voltage (-30°C < T <sub>A</sub> < 85°C) |           |      |     |     |       |  |  |  |  |  |  |

| VBUS                                                 |           | 2.3  |     | 5.5 | V     |  |  |  |  |  |  |

| VUSB                                                 |           | 1.65 |     | 3.6 | V     |  |  |  |  |  |  |

| REG_5V_IN                                            |           | 4.5  |     | 6.0 | V     |  |  |  |  |  |  |

| VCC_IO                                               |           | 1.65 |     | 2.9 | V     |  |  |  |  |  |  |

MC13883 Technical Data, Rev. 3

#### **Table 4. Quiescent Current**

$(2.7V < BP < 4.2 V), (-30°C < T_A < 85°C)$

| Parameter   | Conditions                                          | Min | Тур | Max | Units |

|-------------|-----------------------------------------------------|-----|-----|-----|-------|

| Active Mode | (Phone On,<br>RESETB=1,<br>VBUS=5.25V)              | -   | 300 | -   | μА    |

| Idle Mode   | (Phone On,<br>RESETB=1,<br>VBUS=0V)<br>ID_MUX_ENB_1 | -   | 100 | -   | μА    |

| Off Mode    | (Phone Off,<br>RESETB=0,<br>VBUS=0V)                | -   | 22  | -   | μА    |

## 4 Power Architecture

### 4.1 Power Architecture Overview

The MC13883 IC contains the following power-related features:

- Single and dual-path charging from USB connector

- Fully compliant with USB, USB OTG, enhanced mini-USB, and CEA-936-A specifications

- Over-voltage protection

- Reverse charge mode (allowing battery power to be sourced out to the VBUS pin)

- VBUS generation (including VBUS pulsing in support of USB OTG)

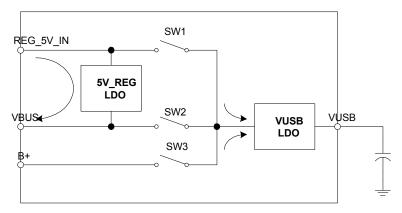

The Power Architecture block diagram is shown in Figure 2.

#### **Power Architecture**

Figure 2. Power Architecture Block Diagram

## 4.2 Charging

This section details the charging functionality. Charge current comes into VBUS from a USB source or charger and is routed to the battery. Power is also routed to the phone circuitry. This can be accomplished in different manners as described below.

If it is desired that the phone circuitry be guaranteed to be powered during charge, the "dual path" technique is probably desirable, as power separately reaches the battery and the phone so that the phone functions even though the battery may be very deeply discharged.

Component count can be reduced with a single-path charge architecture, but at the cost of reduced or delayed functionality when charging a battery that is severely discharged.

Dual Path, Single Path and Serial Path charging is described below and shown in Figures 3, 4 and 5.

## 4.2.1 Dual-Path Charging Overview

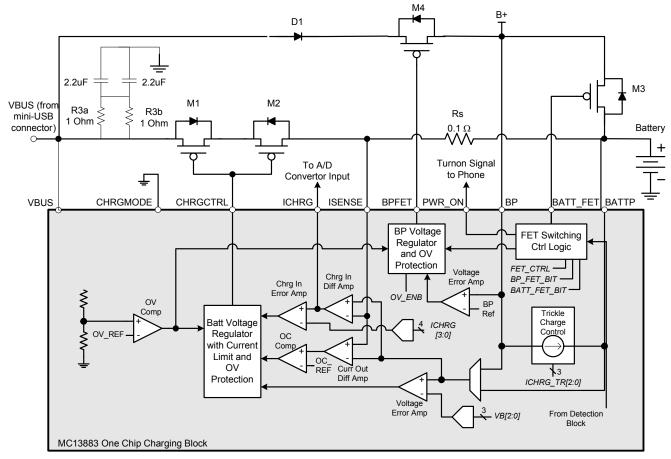

Figure 3. Dual-Path Charging Block Diagram

The basic feature of dual-path charging that sets it apart from single-path charging topologies is the fact that there are two separate current paths from the external charger input (V<sub>BUS</sub>) to the internal phone B+ supply rail (B+). One of these is a current-limited path through external FET's M1 and M2 to the battery positive terminal. This path is used to charge the battery and therefore is called the charge path. The second path is a non-charging path through D1 and M4 to the B+ node, (BP pin). (B+ is the main phone supply node from which most other internal phone power rails are derived, MC13883 pin BP is attached to it.) The basic supply path when a charger is not attached to the phone is from the battery through M3 to B+.

The charge current is sensed through an external sense resistor (nominally 100 m $\Omega$ ) limited to a current set by register bits ICHRG[3:0] via control of M1 and M2 through the CHRGCTRL pin.

There are redundant 1  $\Omega$  and 2.2 uF capacitors on the VBUS pin which are required parts for stability reasons. Each of the 2.2 uF capacitors should be X5R or better with a minimum capacitance of 1.3 uF with 5 volts applied.

The value of a ceramic capacitor is a function of the voltage applied to it. It should be rated for a high voltage, such as 20 volts to withstand failed chargers.

MC13883 Technical Data, Rev. 3

#### **Power Architecture**

The selection of devices appropriate for M1, M2 and M4 should be made carefully because of stability issues. The recommended device for these locations is shown in Table 5.

## 4.2.2 Serial Path Charging Overview

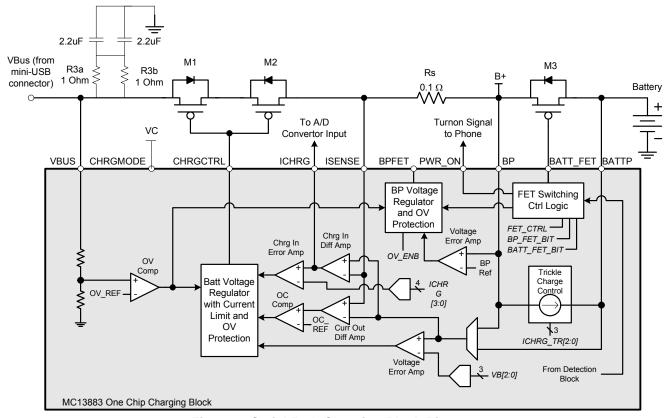

Figure 4. Serial-Path Charging Block Diagram

The serial path charging topology has the main charge path to the B+ node and a switch, M3, from the battery to the B+ node. When the battery is above 3.2 V, the charge current will pass to the battery via the B+ node. If the battery is below 3.2 V, FET M3 is opened and the charge path regulator powers the B+ node, so the phone can operate, the on-chip trickle current path simultaneously charges the battery. This way, the phone can turn on even with a deeply discharged battery.

There are redundant 1 ohm and 2.2 uF capacitors on the VBUS pin which are required parts for stability reasons. Each of the 2.2 uF capacitors should be X5R or better with a minimum capacitance of 1.3 uF with 5 volts applied.

The value of a ceramic capacitor is a function of the voltage applied to it. It should be rated for a high voltage, such as 20 volts to withstand failed chargers.

The selection of devices appropriate for M1 and M2 should be made carefully because of stability issues. The recommended device for these locations is shown in Table 5.

MC13883 Technical Data, Rev. 3

## 4.2.3 Single-Path Charging

Figure 5. Single-Path Charging Block Diagram

As implied by its name, a single-path charging topology has only one path from the charger to B+. The phone operates from the voltage at the battery terminals during charge, if the battery is significantly discharged, the phone will not turn on until the battery has charged to 3.2 V.

There are redundant 1  $\Omega$  and 2.2 uF capacitors on the VBUS pin which are required parts for stability reasons. Each of the 2.2 uF capacitors should be X5R or better with a minimum capacitance of 1.3 uF with 5 volts applied.

The value of a ceramic capacitor is a function of the voltage applied to it. It should be rated for a high voltage, such as 20 volts to withstand failed chargers.

The selection of devices appropriate for M1 and M2 should be made carefully because of stability issues. The recommended device for these locations is shown in Table 5.

|               | M1      | M2      | M4                |

|---------------|---------|---------|-------------------|

| Combination 1 | Si8401  | Si8401  | Si8401 or FDZ291P |

| Combination 2 | Si8415  | Si8401  | Si8401 or FDZ291P |

| Combination 3 | FDZ293P | FDZ293P | Si8401 or FDZ293P |

**Table 5. FET Combinations**

MC13883 Technical Data, Rev. 3

## 4.2.4 Charger Block Signal Description

#### **BATTP (BATT+)**

Connection to the phone main battery positive terminal.

### B+ (BP pin)

B+ is the main phone supply rail. Most internal voltage rails are derived from this supply. B+ is derived from the charger input (VBUS) and the main battery supply (BATT+).

#### **CHRGCTRL**

Charge control output voltage.

#### **ICHRG**

Muxed output voltage proportional to the charge current or the ID voltage.

#### **ISENSE**

Current sense input to the charge control circuitry.

#### PWR ON

Turn-on signal to phone.

#### **CHRGMODE**

Selects whether the phone is configured for single-path, serial-path or dual-path charging. In order to select single path mode, the CHRGMODE pin should be left floating. For Serial Path, CHRGMODE pin is connected to the output of regulator  $V_C$ . For dual-path, CHRGMODE should be grounded.

#### **VBUS**

Charger input to phone.

#### **BATT FET**

Gate drive to the battery FET (M3). This FET connects/disconnects the battery from the B+ (BP) node.

#### **BP FET**

Gate drive to the BP FET (M4). This FET regulates the voltage at the BP or can be controlled as a switch. In single-path charging mode BP\_FET is not used and can be left floating in single-path charging mode.

#### **BATTPON** (Internal Signal)

The BATTPON threshold is the threshold above which the phone will turn on while charging in either single-path mode or with a USB charger in serial- or dual-path mode.

#### **CHRG\_CURR** (Internal Signal)

The CHRG\_CURR threshold is 20 mA and is used as part of charger detection.

#### MC13883 Technical Data, Rev. 3

### **CHRGDET (Internal Signal)**

The CHRGDET threshold is the voltage at the VBUS pin that indicates that a valid charger has been attached.

Table 6. CHRGDET, BATTPON and CHRG\_CURR Thresholds

| Parameter            | Description | Min  | Тур  | Max  | Unit  |

|----------------------|-------------|------|------|------|-------|

| BATTPON Threshold    | Low to High | 3.33 | 3.43 | 3.53 | Volts |

| BATTPON Hysteresis   |             | 50   |      | 200  | mV    |

| CHRGDET Threshold    | Low to High | 3.70 |      | 3.90 | Volts |

| CHRGDET Threshold    | High to Low | 3.50 |      | 3.75 | Volts |

| CHRGDET Hysteresis   |             | 50   |      |      | mV    |

| CHRG_CURR Threshold  | High to Low | 10   | 20   | 30   | mA    |

| CHRG_CURR Hysteresis |             |      | 0.2  |      | mA    |

## 4.2.5 Charger Control Logic

Tables 7, 8 and 9 show the BP\_FET and BATT\_FET states and charge and trickle currents as a function of Vbus, ID, BATTP voltage, RESETB, DP, DM inputs and FET\_OVRD and FET\_CTRL bits. This information is separated into 3 tables, Table 7 for dual path, Table 8 for serial path and Table 9 for single path.

MC13883 Technical Data, Rev. 3

#### **Power Architecture**

Table 7. Charge Control Logic Table (Dual Path)

| Vbus | ID  | RESETB | DP | DM | FET_<br>OVRD | FET_<br>CTRL | BATTP<br>Voltage                                                                                                                                                                                          | BP<br>Regulator<br>BP_FET<br>(Dual Path<br>Only) | BATT_F<br>ET | Charge<br>Regulator | Trickle<br>Charge  | PWR_<br>ON<br>Signal | Description                                                                                          |

|------|-----|--------|----|----|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------|---------------------|--------------------|----------------------|------------------------------------------------------------------------------------------------------|

| н    | <3V | L      | L  | L  | Х            | Х            | <battpon< td=""><td>OFF</td><td>Н</td><td>100 mA</td><td>OFF</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                                | OFF                                              | Н            | 100 mA              | OFF                | L                    | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | Н  | х            | Х            | <battpon< td=""><td>OFF</td><td>Н</td><td>100 mA</td><td>OFF</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                                | OFF                                              | Н            | 100 mA              | OFF                | L                    | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | L  | Х            | Х            | <battpon< td=""><td>OFF</td><td>Н</td><td>100 mA</td><td>OFF</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                                | OFF                                              | Н            | 100 mA              | OFF                | L                    | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | L  | Х            | Х            | >BATTPON                                                                                                                                                                                                  | OFF                                              | L            | 100 mA              | OFF                | Ι                    | USB Host Attach. Limited activation current, Open BP_FET, open BATT_FET                              |

| Н    | <3V | L      | L  | Н  | Х            | Х            | >BATTPON                                                                                                                                                                                                  | OFF                                              | L            | 100 mA              | OFF                | н                    | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | L  | Х            | Х            | >BATTPON                                                                                                                                                                                                  | OFF                                              | L            | 100 mA              | OFF                | Н                    | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | Н  | Х            | Х            | <battpon< td=""><td>ON</td><td>H</td><td>OFF</td><td>OFF</td><td>Ι</td><td>Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.</td></battpon<>             | ON                                               | H            | OFF                 | OFF                | Ι                    | Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.   |

| Н    | <3V | L      | Н  | Н  | Х            | Х            | >BATTPON                                                                                                                                                                                                  | ON                                               | H            | OFF                 | OFF                | н                    | Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.   |

| Н    | <3V | Н      | L  | L  | 0            | Х            | Х                                                                                                                                                                                                         | OFF                                              | L            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | I                    | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | L  | Н  | 0            | Х            | Х                                                                                                                                                                                                         | OFF                                              | L            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | I                    | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | Н  | L  | 0            | Х            | Х                                                                                                                                                                                                         | OFF                                              | L            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | I                    | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | Н  | н  | 0            | Х            | х                                                                                                                                                                                                         | ON                                               | п            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | н                    | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | х  | х  | 1            | 0            | х                                                                                                                                                                                                         | ON                                               | п            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | н                    | Charger or USB Host attached, Phone on, no activation current. FET controlled by SPI FET_CTRL bit    |

| Н    | <3V | Н      | х  | х  | 1            | 1            | Х                                                                                                                                                                                                         | OFF                                              | L            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | н                    | Charger or USB Host attached, Phone on, no activation current. FET controlled by SPI FET_CTRL bit    |

| Н    | >3V | Х      | Х  | х  | х            | Х            | <battpon< td=""><td>ON</td><td>Н</td><td>*ICHRG<br/>bits</td><td>*ICHRG<br/>_TR bits</td><td>Н</td><td>Factory Mode, no activation current. FET controlled by SPI and Seamless comparator</td></battpon<> | ON                                               | Н            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | Н                    | Factory Mode, no activation current. FET controlled by SPI and Seamless comparator                   |

| Н    | >3V | Х      | Х  | х  | х            | Х            | >BATTPON                                                                                                                                                                                                  | ON                                               | Н            | *ICHRG<br>bits      | *ICHRG<br>_TR bits | н                    | Factory Mode, no activation current. FET controlled by SPI and Seamless comparator                   |

| L    | Х   | Х      | Х  | Х  | Х            | Х            | х                                                                                                                                                                                                         | OFF                                              | L            | OFF                 | OFF                | L                    | No Charger or USB Host attaced, no activation current. FET controlled by SPI and Seamless comparator |

### **Table 8. Charge Control Logic Table (Serial Path)**

| Vbus | ID  | RESETB | DP | DM | FET_<br>OVRD | FET_<br>CTRL | BATTP<br>Voltage                                                                                                                                                                         | BATT_FET                                                                         | Charge<br>Regulator | Trickle<br>Charge | PWR_ON<br>Signal | Description                                                                                          |

|------|-----|--------|----|----|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------|-------------------|------------------|------------------------------------------------------------------------------------------------------|

| Н    | <3V | L      | L  | L  | х            | Х            | <battpon< td=""><td>L</td><td>100 mA</td><td>OFF</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                           | L                                                                                | 100 mA              | OFF               | L                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | Н  | Х            | Х            | <battpon< td=""><td>L</td><td>100 mA</td><td>OFF</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                           | L                                                                                | 100 mA              | OFF               | L                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | н  | L  | Х            | х            | <battpon< td=""><td>L</td><td>100 mA</td><td>OFF</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                           | L                                                                                | 100 mA              | OFF               | L                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | L  | Х            | Х            | >BATTPON                                                                                                                                                                                 | L                                                                                | 100 mA              | OFF               | Н                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | Н  | Х            | Х            | >BATTPON                                                                                                                                                                                 | L                                                                                | 100 mA              | OFF               | Н                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | L  | Х            | х            | >BATTPON                                                                                                                                                                                 | L                                                                                | 100 mA              | OFF               | Н                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | Н  | Х            | х            | <battpon< td=""><td>Н</td><td>Full Rate</td><td>OFF</td><td>Н</td><td>Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.</td></battpon<> | Н                                                                                | Full Rate           | OFF               | Н                | Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.   |

| Н    | <3V | L      | Н  | Н  | Х            | х            | >BATTPON                                                                                                                                                                                 | Н                                                                                | Full Rate           | OFF               | Н                | Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.   |

| Н    | <3V | н      | L  | L  | 0            | Х            | Х                                                                                                                                                                                        | L                                                                                | *ICHRG<br>bits      | *ICHRG_TR<br>bits | н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | L  | Н  | 0            | х            | X                                                                                                                                                                                        | L                                                                                | *ICHRG<br>bits      | *ICHRG_TR<br>bits | н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | Н  | L  | 0            | х            | Х                                                                                                                                                                                        | L                                                                                | *ICHRG<br>bits      | *ICHRG_TR<br>bits | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | н  | н  | 0            | х            | X                                                                                                                                                                                        | Upon entry<br>into this<br>state, H if<br>already in<br>Full Rate<br>Otherwise L | *ICHRG<br>bits      | *ICHRG_TR<br>bits | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | н      | х  | х  | 1            | 0            | Х                                                                                                                                                                                        | Н                                                                                | *ICHRG<br>bits      | *ICHRG_TR<br>bits | I                | Charger or USB Host attached, Phone on, no activation current. FET controlled by SPI FET_CTRL bit    |

| Н    | <3V | Н      | х  | х  | 1            | 1            | х                                                                                                                                                                                        | L                                                                                | *ICHRG<br>bits      | *ICHRG_TR<br>bits | н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by SPI FET_CTRL bit    |

| Н    | >3V | Х      | х  | х  | Х            | х            | <battpon< td=""><td>Н</td><td>Full Rate</td><td>*ICHRG_TR<br/>bits</td><td>Н</td><td>Factory Mode, no activation current. FET controlled by SPI and Seamless comparator</td></battpon<>  | Н                                                                                | Full Rate           | *ICHRG_TR<br>bits | Н                | Factory Mode, no activation current. FET controlled by SPI and Seamless comparator                   |

| Н    | >3V | Х      | х  | х  | Х            | х            | >BATTPON                                                                                                                                                                                 | Н                                                                                | Full Rate           | *ICHRG_TR<br>bits | Н                | Factory Mode, no activation current. FET controlled by SPI and Seamless comparator                   |

| L    | Х   | Х      | х  | Х  | Х            | х            | X                                                                                                                                                                                        | L                                                                                | OFF                 | OFF               | L                | No Charger or USB Host attaced, no activation current. FET controlled by SPI and Seamless comparator |

**Table 9. Charge Control Logic Table (Single Path)**

| Vbus | ID  | RESETB | DP | DM | FET_<br>OVRD | FET_<br>CTRL | BATTP<br>Voltage                                                                                                                                                                                    | BATT_<br>FET | Charge<br>Regulator   | Trickle<br>Charge | PWR_ON<br>Signal | Description                                                                                          |

|------|-----|--------|----|----|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|-------------------|------------------|------------------------------------------------------------------------------------------------------|

| Н    | <3V | L      | L  | L  | х            | х            | <battpon< td=""><td>N/A</td><td>100 mA</td><td>N/A</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                                    | N/A          | 100 mA                | N/A               | L                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | Н  | Х            | Х            | <battpon< td=""><td>N/A</td><td>100 mA</td><td>N/A</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                                    | N/A          | 100 mA                | N/A               | L                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | L  | Х            | Х            | <battpon< td=""><td>N/A</td><td>100 mA</td><td>N/A</td><td>L</td><td>USB Host Attach. Limited activation current,<br/>Open BP_FET, open BATT_FET</td></battpon<>                                    | N/A          | 100 mA                | N/A               | L                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | L  | Х            | Х            | >BATTPON                                                                                                                                                                                            | N/A          | 100 mA                | N/A               | Н                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | L  | Н  | Х            | Х            | >BATTPON                                                                                                                                                                                            | N/A          | 100 mA                | N/A               | н                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | L  | Х            | Х            | >BATTPON                                                                                                                                                                                            | N/A          | 100 mA                | N/A               | Н                | USB Host Attach. Limited activation current,<br>Open BP_FET, open BATT_FET                           |

| Н    | <3V | L      | Н  | Н  | х            | Х            | <battpon< td=""><td>N/A</td><td>**100 / 300<br/>mA</td><td>N/A</td><td>L</td><td>Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.</td></battpon<> | N/A          | **100 / 300<br>mA     | N/A               | L                | Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.   |

| Н    | <3V | L      | Н  | н  | х            | х            | >BATTPON                                                                                                                                                                                            | N/A          | **100 / 300<br>mA     | N/A               | Н                | Charger attached, Phone off, no activation current. FET controlled by SPI and Seamless comparator.   |

| Н    | <3V | н      | L  | L  | Х            | Х            | Х                                                                                                                                                                                                   | N/A          | *ICHRG bits           | N/A               | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | н      | L  | Н  | Х            | Х            | Х                                                                                                                                                                                                   | N/A          | *ICHRG bits           | N/A               | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | Н  | L  | Х            | Х            | Х                                                                                                                                                                                                   | N/A          | *ICHRG bits           | N/A               | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | Н  | Н  | Х            | Х            | Х                                                                                                                                                                                                   | N/A          | *ICHRG bits           | N/A               | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by Seamless comparator |

| Н    | <3V | Н      | х  | х  | Х            | Х            | Х                                                                                                                                                                                                   | N/A          | *ICHRG bits           | N/A               | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by SPI FET_CTRL bit    |

| Н    | <3V | Н      | x  | х  | Х            | Х            | Х                                                                                                                                                                                                   | N/A          | *ICHRG bits           | N/A               | Н                | Charger or USB Host attached, Phone on, no activation current. FET controlled by SPI FET_CTRL bit    |

| Н    | >3V | Х      | х  | Х  | х            | х            | <battpon< td=""><td>N/A</td><td>***100/300/<br/>600 mA</td><td>N/A</td><td>L</td><td>Factory Mode, no activation current. FET controlled by SPI and Seamless comparator</td></battpon<>             | N/A          | ***100/300/<br>600 mA | N/A               | L                | Factory Mode, no activation current. FET controlled by SPI and Seamless comparator                   |

| Н    | >3V | Х      | х  | х  | Х            | Х            | >BATTPON                                                                                                                                                                                            | N/A          | ***100/300/<br>600 mA | N/A               | Н                | Factory Mode, no activation current. FET controlled by SPI and Seamless comparator                   |

| L    | х   | Х      | Х  | Х  | х            | Х            | X                                                                                                                                                                                                   | N/A          | OFF                   | N/A               | L                | No Charger or USB Host attaced, no activation current. FET controlled by SPI and Seamless comparator |

<sup>\*</sup> The control logic writes to the ICHRG[3:0] bits in the Power Control Register to set the current as indicated in the table above. When these bits are written to, the software overrides these settings.

MC13883 Technical Data, Rev. 3

<sup>\*\*</sup> In single path mode, the maximum activation charge current varies according to the battery voltage. When BATTP <2.7 V, the maximum charge current is 100 mA, when BATTP >2.7 V, the maximum charge current is 300 mA.

<sup>\*\*\*</sup> In factory, single path mode, an additional current step allows the phone to automatically turn on when no battery is present. The maximum charge current in this case is 100mA when BATTP < 2.7 V, 300 mA when 2.7 V< BATTP <3.7 V, and 600 mA when BATTP >3.7 V.

\*\*\*\* For the purpose of this table, when the BP Regulator / BP\_FET column indicates an "ON" condition, the BP regulator is ON if BP\_SWITCH=0 (the BP Regulator is being used as a regulator). If BP\_SWITCH=1 (indicating that the BP Regulator is acting as a switch) then an "ON" in this column indicates that the BP\_FET should be driven low. An "OFF" condition in this column indicates that the BP regulator should be OFF (BP\_SWITCH=0) or the BP\_FET should be driven high (BP\_SWITCH=1).

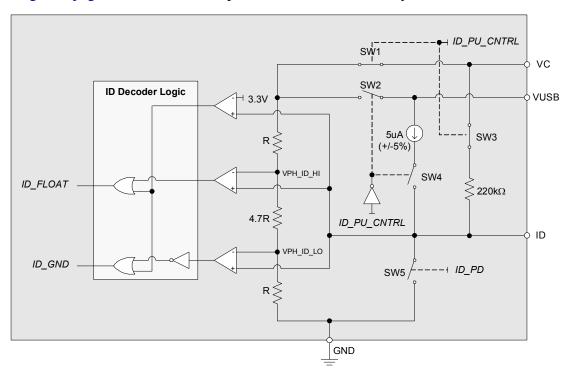

### 4.2.6 ICHRG Output

The ICHRG pin outputs either a voltage that is proportional to the current through Rs, the sense resistor, or outputs a voltage that is proportional to the ID pin voltage.

When the Charge regulator is enabled, the ICHRG pin outputs a voltage that is proportional to the current through Rs (from ISENSE to either BP or BATTP). When Reverse mode is enabled (RVRS\_MODE = 1), the ICHRG pin outputs a voltage that is proportional to the current through Rs (from either BP or BATTP to ISENSE). This voltage is scaled from 0 to 2.3 V for currents from 0 to 1.8 A (full scale). The accuracy of the ICHRG voltage should be  $\pm 10\%$  of the actual charge current (after scaling) for charge currents greater than 100 mA. For charge currents less than 100 mA, the accuracy requirement is  $\pm 10$  mA compared to the actual charge current.

If both the Charge Regulator and Reverse mode are disabled, the ICHRG pin outputs a voltage that is proportional to the ID pin.

In idle mode, the MC13883 IC draws extra current when the MUX associated with the ICHRG pin is enabled. This extra current is significant enough that standby time will be affected. To disable drive to this pin, the ID\_ICHRG\_MUX\_ENB can be asserted as listed in Table 50, Register 04 - Power Control 1 as Bit 4.

The ID pin voltage or the CHRG\_I current will not be able to be read when this pin is disabled. When the MUX is disabled, the ICHRG pin is high impedance.

The ICHRG pin will have an output impedance of a maximum of 1.5 k $\Omega$  for load currents of 10 uA or less. <sup>1</sup>

| Signal | Condition                           | Input Range           | Equation               | Tolerance                                                                                              |

|--------|-------------------------------------|-----------------------|------------------------|--------------------------------------------------------------------------------------------------------|

| ICHRG  | Charge Regulator Enabled            | Icharge = 0 - 1.8A    | Icharge*(2.3V/1.8A)    | +/- 50 mV for Icharge ≤ 391mA,<br>+/- 10% for Icharge > 391mA                                          |

| ICHRG  | RVRS_MODE = 1                       | Idischarge = 0 - 1.8A | Idischarge*(2.3V/1.8A) | +/- 50 mV for Icharge < 391 mA,<br>+/- 10% for Icharge > 391 mA                                        |

| ICHRG  | ICHRG[3:0] = 0 and<br>RVRS_MODE = 1 | ID = 0 to 5V          | ID Voltage*0.9         | + 75 mV/-3% for ID < 1.0 V,<br>+/- 3% for 1.0 V < ID < 2.2 V,<br>ICHRG = 2.2 V to 2.5 V for ID = 5.0 V |

Table 10. Charge Control Logic Table

MC13883 Technical Data, Rev. 3

<sup>1.</sup> For version 3.1, the ICHRG output impendance in ID mode is ~50 k $\Omega$ .

## 4.2.7 Over-voltage Protection

There are three paths in the MC13883 IC that are protected from an over-voltage event: through the two external paths present in dual path charging as well as an internal path from VBUS to the USB section of the IC. When an over-voltage condition is sensed at the VBUS pin, all 3 paths are opened. This is accomplished by driving the CHRGCTRL and BP\_FET pins high while opening the internal path. When an OV condition occurs, an interrupt will occur (VBUSOV\_INT). Also, the ICHRG bits will clear and the BP regulator will be disabled.

The VBUSOV\_SNS bit can be read to see if the OV condition has cleared.

Once the OV condition clears, the BP regulator will re-enable (in Dual Path mode) however the ICHRG bits will have to be reprogrammed by software.

| Parameter                                                  | Condition                                                 | Min     | Тур  | Max | Units |

|------------------------------------------------------------|-----------------------------------------------------------|---------|------|-----|-------|

| Input/output voltage range                                 | VBUS, CHRGCTRL, BP_FET                                    | 3.0     |      | 20  | V     |

| Input Voltage Slew Rate [dv/dt]Rise                        | 0V< VBUS < 20V, at power up                               | 0.00125 |      | 360 | V/µs  |

| Input Voltage Slew Rate [dv/dt]Rise                        | 3V< VBUS < 20V, While in normal operation                 | 0.00125 |      | 12  | V/μs  |

| OV Comparator Voltage Threshold (VTh), measured at VBUS    | High to Low, Low to High                                  | 5.6     | 5.75 | 5.9 | V     |

| OV Comparator Voltage Hysteresis (VHyst), measured at VBUS |                                                           | 50      |      | 200 | mV    |

| Turn-off delay (TOFF)                                      | CL=6nF, VBUS > VTh to<br>CHRGCTRL=VBUS and<br>BP_FET=VBUS |         |      | 1   | μS    |

**Table 11. Over-voltage Protection Performance Specifications**

## 4.2.8 Reverse Charge Mode

This mode allows the current to be sourced from the battery out the VBUS line to be used to power or charge external devices. The FET's M1 and M2 are turned on with CHRGCTRL and current is monitored through Rs from BP or BATTP to ISENSE. This mode is enabled with SPI Bit: RVRS\_MODE. The current limit that disables the function and generates an interrupt (RVRS\_MODE\_INT) is shown in Table 4.

Because there may be a large capacitor in the phone powered device which needs to be charged and because rapid charging of it may cause a transient dip in the Battery voltage, the rate that M1 and M2 get turned on is controlled. The reverse path enable current is specified in Table 12. The rate at which M1 and M2 turn on is slowed as a result and the external large capacitor is charged up slowly.

In the event of a short in the phone powered device, the current flowing from the battery to the phone powered device may be excessive. A dual threshold system is employed so that the phone powered device path will shut off very quickly for high currents and will not trip for lower transient currents.

If the current through Rs goes above the first threshold Rth1 for a duration inside the RCR1 time window, without going over Rth2, then the Phone Powered Device path will be opened and an interrupt shall be generated.

MC13883 Technical Data, Rev. 3

If the current through Rs goes above the first threshold Rth2 for a duration above the RCR2 time threshold, then the Phone Powered Device path will be opened and an interrupt shall be generated.

**Table 12. Reverse Over-current Protection Performance Specifications**

| Parameter                              | Condition                                                                                                                                      | Min | Тур | Max  | Units |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| Reverse Path Enable Current            | CHRGCNTRL Pin Sink Current (RVRS_MODE bit = 1)                                                                                                 | 2   | 4   | 6    | μΑ    |

| Reverse Current Threshold 1 (Rth1)     | Current Threshold 1                                                                                                                            | 725 | 800 | 1010 | mA    |

| Reverse Current Threshold 2 (Rth2)     | Current Threshold 2                                                                                                                            | 1.7 | -   | 2.3  | Α     |

| Reverse Current Reaction Time 1 (RCR1) | Rth2 > Current > Rth1                                                                                                                          | 1   | -   | 5    | mS    |

| Reverse Current Reaction Time 2 (RCR2) | Current > Rth2                                                                                                                                 | 100 | -   | 200  | μS    |

| RVRS_CHRG_INT current threshold (RCT)  | RVRS_MODE=1, this current threshold applies to current flowing through the 100 m $\Omega$ sense resistor in the direction towards the battery  | 1   | 20  | 30   | mA    |

| RVRS_MODE Delay                        | Following RVRS_CHRG_INT being set by the hardware, the software needs to wait for at least this amount of time before enabling RVRS_MODE path. | 1   | -   | 5    | mS    |

When RVRS\_MODE = 1, then the phone will be sourcing power, not receiving power from the VBUS pin of the USB connector. Because the VCHRG regulator will be disabled in this mode, ensure the battery doesn't accidentally get charged in this mode. If the current going into the battery goes above 20 mA threshold (RCT) for a debounce period described in Table 41, then the RVRS\_MODE path will be turned off and the RVRS\_CHRG\_INT bit will be set and the RVRS\_MODE bit is cleared. Before re-enabling the RVRS\_MODE path, the source of the over current condition should be understood and corrected. The RVRS\_MODE bit cannot be set again until 1 ms has elapsed from the time of the interrupt. If the software tries to program the RVRS\_MODE bit before 1 ms has passed, the bit will remain cleared and the path will remain disabled.

If the software tries to program RVRS\_MODE to 1 when the IC is not ready (within this 1 ms period), the RVRS\_MODE bit will remain cleared and the RVRS path will remain disabled.

## 4.2.9 Charge Current Regulation

The ICHRG[3:0] bits set the maximum current for the main charger, as shown in Table 13. This current is the actual current that flows through the  $100 \text{ M}\Omega$  sense resistor. It does not include any other currents that go into the CHRGRAW/VBUS pins including the charge LED.

**Table 13. Battery Charge Current Control Settings**

| Parameter  | Value             | Cha                                                         | arge Current (in I | mA)  |  |

|------------|-------------------|-------------------------------------------------------------|--------------------|------|--|

| Parameter  | value             | min                                                         | nom                | max  |  |

| ICHRG[3:0] | 0000              | 0                                                           | 0                  | 0    |  |

|            | 0001              | 55                                                          | 70                 | 85   |  |

|            | 0010              | 141                                                         | 177                | 213  |  |

|            | 0011              | 212                                                         | 266                | 320  |  |

|            | 0100              | 319                                                         | 355                | 390  |  |

|            | 0101              | 398                                                         | 443                | 488  |  |

|            | 0110              | 478                                                         | 532                | 585  |  |

|            | 0111              | 558                                                         | 621                | 6835 |  |

|            | 1000              | 638                                                         | 710                | 781  |  |

|            | 1001              | 717                                                         | 798                | 878  |  |

|            | 1010              | 797                                                         | 886                | 976  |  |

|            | 1011              | 877                                                         | 975                | 1073 |  |

|            | 1100              | 957                                                         | 1064               | 1170 |  |

|            | 1101              | 1037                                                        | 1152               | 1268 |  |

|            | 1110              | 1276                                                        | 1596               | 1915 |  |

|            | 1111 <sup>A</sup> | Fully On - Disallow battery FET to be turned on in hardware |                    |      |  |

A As an additional layer of protection, in mode 1111, "fully on", BATT\_FET will not attempt to turn on the path to B+.

Redundant 1 ohm and 2.2 uF capacitors on the VBUS pin are required parts for stability reasons. Each of the 2.2 uF capacitors should be X5R or better with a minimum capacitance of 1.3 uF with 5 volts applied.

The value of a ceramic capacitor is a function of the voltage applied to it. It should be rated for a high voltage, such as 20 volts to withstand failed chargers. See Figure 3, Figure 4, and Figure 5 for more information.

## 4.2.10 Trickle Charging

The ICHRG\_TR[2:0] bits set the maximum current for the trickle charger, as shown in Table 14. The current tolerance is  $\pm$  30% (the table shows the nominal values in mA). This Trickle Charger is of use when the Battery is low while in the Serial Path Configuration. The values in Table 14 are valid for a difference between BP and BATTP of 1.0 Volt or more. When operated with a headroom of 0.8 Volts, the trickle current level will degrade from  $\pm$  30% to  $\pm$  40%.

| Parameter     | Value | Trickle Charge Current (in mA) |     |     |  |

|---------------|-------|--------------------------------|-----|-----|--|

|               |       | Min                            | Nom | Max |  |

| ICHRG_TR[2:0] | 000   | 0                              | 0   | 0   |  |

|               | 001   | 6                              | 9   | 12  |  |

|               | 010   | 14                             | 20  | 26  |  |

|               | 011   | 25                             | 36  | 47  |  |

|               | 100   | 29                             | 42  | 55  |  |

|               | 101   | 35                             | 50  | 65  |  |

|               | 110   | 41                             | 59  | 77  |  |

|               | 111   | 50                             | 68  | 86  |  |

**Table 14. Trickle Charge Current Control Settings**

## 4.2.11 Standalone Trickle Charging

MC13883 has a standalone trickle charge mode of operation in order to ensure that a completely discharged battery can be charged without the microprocessor's control. This is especially important in single path configurations and when charging from a USB host.

Upon plugging a valid USB Host to the phone in Dual Path or Serial Path mode, the trickle cycle is started at a current of TRICKLEL and remains at this level until charging is terminated. The standalone trickle charger will terminate upon charger removal, an over-voltage condition, when the charge current falls below the CHRG\_CURR threshold or if SPI register 3 is written.

Similarly, in Single Path mode, the trickle charger will start upon the insertion of a valid USB host except that the charge current will vary based on the battery voltage. For an extremely low battery, below BATTL, the trickle charge current level is set to the TRICKLEL. When the battery voltage increases above the BATTL threshold and the charger is not a USB host, the trickle charge level is increased to the TRICKLEM level. When the battery voltage rises above the BATTON threshold, which is sufficient voltage for phone operation, a power up sequence is automatically initiated. Standalone trickle charging will terminate under the same conditions as those when in Dual Path and Serial Path mode; charger removal, an over-voltage condition, when the charge current falls below the CHRG\_CURR threshold, or if SPI register 3 is written.

In all charge modes even after the phone has powered up, the standalone trickle charger will remain on until software does an initial write to Register 3. Also, if the standalone trickle charger is enabled and a read is performed on Register 3 prior to re-writing the bits, ICHRG(3:0) will read back "0000".

MC13883 Technical Data, Rev. 3

#### **Power Architecture**

During hardware trickle charging at TRICKLEL and TRICKLEM levels, The PWR\_ON pin remains low until the BATTON threshold is crossed. If the battery voltage was already greater than BATTON when a charger is attached, the phone will power up immediately without starting a trickle charge cycle. In any case, the charge path regulator will ensure the battery voltage during trickle charging will not exceed the value as set by VCHRG[2:0].

If factory mode (UID > 3V) is detected in the single path charging configuration and the battery voltage is above BATTH comparator threshold, the charge current is set to TRICKLEH.

When plugging a USB host without a battery placed in the phone, the trickle charge cycle will cause the battery voltage to rise, creating a power up event by setting the PWR\_ON signal high. However, because of USB requirements, the charge current is set to TRICKLEL and the phone will immediately shut down because there will not be enough current to sustain a power-up cycle.

Built-in control prevents the phone from continuously power-up and power-down due to this condition. As a result, when applying a battery to the phone at a later stage, the USB trickle charge will not automatically start until the USB cable is removed and reinserted.

Since normal LED control via the SPI bus is not possible in the standalone trickle mode, a current sink at the CHRGLED pin will be active as long as the standalone trickle charge is active. This means that the trickle LED will remain on until the charger is programmed by SPI. The LED can be connected to either BP or VBUS. Once the phone has powered on, the trickle LED can be disabled by clearing the CHRGLEDEN SPI bit. The trickle LED is also disabled when an over-voltage condition occurs unless the CHRGLEDEN bit was set high by software.

**Table 15. Trickle Charge Main Characteristics**

| Trickle current TRICKLEL | ICHRG[3:0]=0001 A |

|--------------------------|-------------------|

| Trickle current TRICKLEM | ICHRG[3:0]=0011   |

| Trickle current TRICKLEH | ICHRG[3:0]=0110   |

A For battery voltages under ~2.4V, the current may be slightly lower during trickle charging.

**Table 16. Battery Detectors Main Characteristics**

| Parameter Description        | Min | Тур  | Max | Units |

|------------------------------|-----|------|-----|-------|

| BATTL Threshold Low to High  | -3% | 2.7  | +3% | V     |

| BATTON Threshold Low to High | -3% | 3.43 | +3% | V     |

| BATTH Threshold Low to High  | -3% | 3.7  | +3% | V     |

## 4.2.12 Charge Voltage Regulator (VCHRG)

This is the Regulator-Charger (Voltage and Current Control) that controls current through M1 and M2 using CHRGCTRL. For charging, it has the capability of regulating to a fixed voltage.

- It requires an output capacitor of 10 μF on both BP and BATTP pins.

- Output voltage sensing is done at the ISENSE pin.

MC13883 Technical Data, Rev. 3

- Output current sensing is either the BATTP or BP pin.

- An interrupt is generated when the charge goes from constant current to constant voltage (CC to CV).

- It is designed for use with an external current sensing resistor of 100 m $\Omega$

**Table 17. VCHRG Output Voltage Settings**

| Parameter  | Value | Battery Regulator Output<br>Voltage (V) |

|------------|-------|-----------------------------------------|

| VCHRG[2:0] | 000   | 4.05                                    |

|            | 001   | 4.375                                   |

|            | 010   | 4.15                                    |

|            | 011   | 4.20                                    |

|            | 100   | 4.25                                    |

|            | 101   | 4.30                                    |

|            | 110   | 3.80                                    |

|            | 111   | 4.50                                    |

**Table 18. VCHRG Performance Specifications**

| Parameter                | Condition                                                        | Min           | Тур | Max      | Units |

|--------------------------|------------------------------------------------------------------|---------------|-----|----------|-------|

| Load Cap, CL             | Regulating the BP node                                           | 5             | 10  | 30       | μF    |

| Load Cap, CL             | Regulating the BATT+ node                                        | 5             | 10  | 30       | μF    |

| Load Capacitor ESR       | At capacitor resonance                                           | 4             | -   | 30       | mΩ    |

| Output Voltage           | BP/BATTP, 100 μA < IL < 100mA,<br>(Vout +500 mV) < Vin           | Nom<br>-1.25% | nom | nom + 1% |       |

| Output Voltage           | BP/ BATTP, 100 mA < IL < 1.5 A,<br>(Vout +500 mV) < Vin          | Nom5%         | nom | Nom + 1% |       |

| PSRR                     | Vin = Vout +1 V<br>IL = 75% of Imax                              | 20            | -   | -        | dB    |

| Start-Up Overshoot       | IL = 0                                                           | -             | 1   | -        | %     |

| Turn-on Time             | ENABLE to 90% of Vout                                            | -             | -   | 100      | ms    |

| Transient Response       | IL = 10 mA to 1.5A, Tr = 5 μs                                    | -             | 1   | -        | %     |

| VBUS to CHRGCTRL Voltage | Batt = 3.6V<br>VBUS = 4.1V<br>ICHRG ≠0000<br>Charge path is OPEN | 1.9           |     |          | V     |

MC13883 Technical Data, Rev. 3

### 4.2.13 PWR-ON

PWR\_ON Output Low

The PWR\_ON signal has two functions. It is meant to turn on an external power management device when VBUS goes above the CHRGDET threshold. It is to be referenced to VBUS so that the charger voltage can be read by the phone's ADC.

Parameter

Condition

Min

Typ

Max

Unit

PWR\_ON Output High

VBUS > CHRGDET threshold Rload = 10 K

80% of VBUS

Volts

20% of

**VBUS**

Volts

VBUS < CHRGDET threshold

Table 19. PWR\_ON Performance Specifications

## 4.2.14 VC Regulator and Bandgap

The VC regulator is the MC13883's internal regulator. It gets powered by the BP or VBUS. It powers the bandgap. VC powers much of the ICs' internal functions. No external loading on VC or BG\_BYP is allowed.

|         | Parameter                  | Target  |

|---------|----------------------------|---------|

| VC      | Output voltage in ON mode  | 2.775 V |

|         | Accuracy in ON mode        | 3%      |

|         | Output voltage in OFF mode | 2,65 V  |

|         | Bypass Capacitor           | 1 uF    |

| Bandgap | Output voltage in ON mode  | 1.20 V  |

|         | Output voltage in OFF mode | 0 V     |

|         | Absolute Accuracy          | 0.5%    |

|         | Temperature Drift          | 0.25%   |

|         | PSRR at BP = 3.0V          | 90 dB   |

|         | Bypass Capacitor           | 100 nF  |

**Table 20. VC and Bandgap Performance Specifications**

## 4.2.15 Constant Current / Constant Voltage Sense Bit (CC\_CV)

There are two phases used in the charging of lithium ion batteries, constant current and constant voltage. The sensing of the transition between these two phases is useful in charge metering.

During the constant current phase, the current regulator may be operating to regulate the current into the battery pack per the ICHRG bit settings or it may not be operating to regulate the current into the battery pack in the case of a collapsed charger. However, once the battery voltage reaches the VCHRG value, the voltage regulator will begin regulating. CC\_CV is designed to trip at 97% of the programmed charge voltage, measured at the ISENSE Pin. A debounce and mask and interrupt bits are defined in Section 7, "SPI/I2C Register Tables", on page 53.

MC13883 Technical Data, Rev. 3

### 4.2.16 Shorted Charger Protection

If during the charge of a battery in the configurations of Section 4.2.1, "Dual-Path Charging Overview", Section 4.2.2, "Serial Path Charging Overview", and Section 4.2.3, "Single-Path Charging", the charging input, CHRGRAW/VBUS is shorted to ground, a large current can flow from the battery pack out through M1/M2. This is undesirable.

Therefore, the ICHRG bits are automatically set to 0000 whenever the CHRGRAW voltage goes below the CHRG\_DET threshold (see Table 6 in Section 4.2.4, "Charger Block Signal Description") and the charge current going into the battery pack goes below the CHRG\_CURR threshold (20 mA typical) as is the case when the current goes through M1/M2 in the direction towards CHRGRAW and debounced per the CHRG\_CURR sense bit.

## 4.2.17 USB and Non-USB Dead Battery Recovery

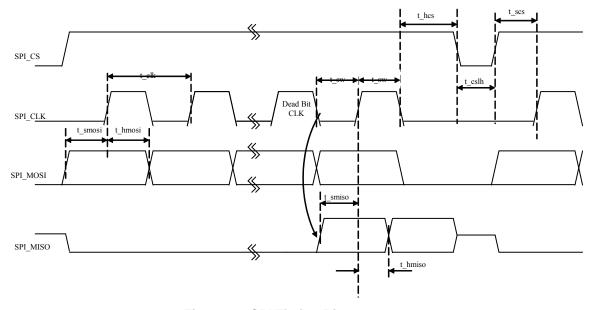

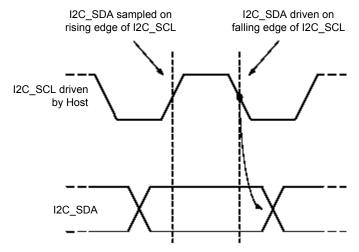

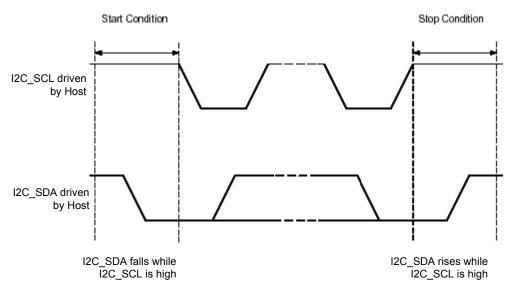

The control logic in Section 4.2.5, "Charger Control Logic" supports this section. When a USB power source is connected, the IC recognizes it as a USB power source (no SE1). If the battery is low (less than the BATT\_ON threshold of 3.43 volts), the M1/M2 charging path charges the battery at a charge rate below 100 mA (see ICHRG bit setting 0001). The phone is turn turned on, it enumerates, etc. and the battery finishes its charging.