**Features**

## Low-Voltage, Phase-Reversal **Analog Switch**

#### General Description

The MAX4528 low-voltage, CMOS analog IC is configured as a phase-reversal switch and optimized for highspeed applications such as chopper amplifiers. It operates from a +2.7V to +12V single supply or from  $\pm 2.7V$  to  $\pm 6V$  dual supplies.

On-resistance (110 $\Omega$  max) is matched between switches to  $7\Omega$  (max). Each switch can handle Rail-to-Rail® analog signals. The leakage current is only 0.5nA at +25°C and 20nA at +85°C. All digital inputs have 0.8V to 2.4V logic thresholds, ensuring both TTL- and CMOS-logic compatibility.

For higher voltage operation, see the MAX4526/ MAX4527 data sheet.

#### Applications Ordering Information

| PART       | TEMP. RANGE    | PIN-PACKAGE   |

|------------|----------------|---------------|

| MAX4528CPA | 0°C to +70°C   | 8 Plastic DIP |

| MAX4528CSA | 0°C to +70°C   | 8 SO          |

| MAX4528CUA | 0°C to +70°C   | 8 μMAX        |

| MAX4528C/D | 0°C to +70°C   | Dice*         |

| MAX4528EPA | -40°C to +85°C | 8 Plastic DIP |

| MAX4528ESA | -40°C to +85°C | 8 SO          |

| MAX4528EUA | -40°C to +85°C | 8 μMAX        |

<sup>\*</sup>Contact factory for availability.

# ♦ 5pC (max) Charge Injection

- **♦ 110**Ω Signal Paths with ±5V Supplies

- ♦ Rail-to-Rail Signal Handling

- ♦ Transition Time <100ns with ±5V Supplies</p>

- ♦ 1.0µA (max) Current Consumption

- → >2kV ESD Protection per Method 3015.7

- **♦ TTL/CMOS-Compatible Input**

- ♦ Small Packages: 8-Pin SO, DIP, and µMAX

## Balanced Modulators/Demodulators **Data Acquisition**

**Chopper-Stabilized Amplifiers**

Test Equipment

Audio-Signal Routing

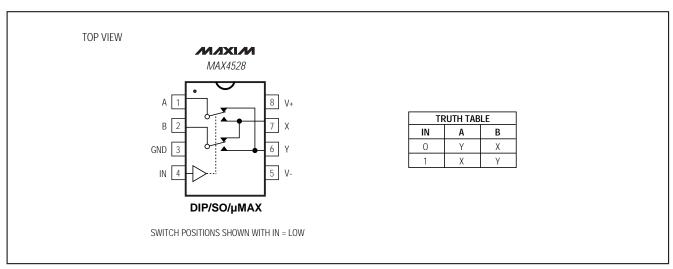

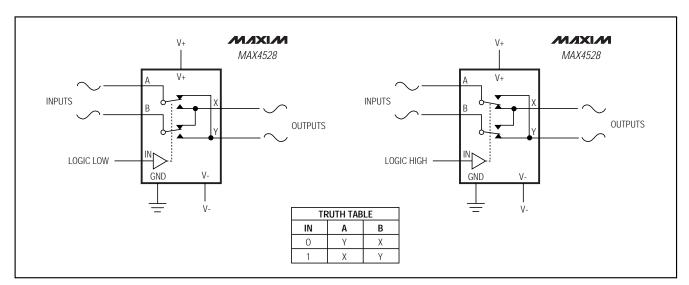

#### Pin Configuration/Functional Diagram/Truth Table

Rail-to-Rail is a registered trademark of Nippon Motorola Ltd.

NIXIN Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 408-737-7600 ext. 3468.

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages Referenced to GND)         |                        |

|--------------------------------------|------------------------|

| V+                                   | 0.3V to 13V            |

| V                                    | 13V to 0.3V            |

| V+ to V                              | 0.3V to 13V            |

| All Other Pins (Note 1)              | (V0.3V) to $(V++0.3V)$ |

| Continuous Current into Any Terminal | ±20mA                  |

| Peak Current into Any Terminal       |                        |

| (pulsed at 1ms, 10% duty cycle)      | ±50mA                  |

| ESD per Method 3015.7                | >2000V                 |

| Continuous Power Dissipation (TA = + |                |

|--------------------------------------|----------------|

| Plastic DIP (derate 9.09mW/°C above  | ve +70°C)727mW |

| SO (derate 5.88mW/°C above +70°      | C)471mW        |

| μMAX (derate 4.10mW/°C above +7      | 70°C)330mW     |

| Operating Temperature Ranges         |                |

| MAX4528C                             | 0°C to +70°C   |

| MAX4528E                             | 40°C to +85°C  |

| Storage Temperature Range            | 65°C to +150°C |

| Lead Temperature (soldering, 10sec)  | +300°C         |

|                                      |                |

**Note 1:** Signals on IN, A, B, X, or Y exceeding V+ or V- are clamped by internal diodes. Limit forward-diode current to maximum current rating.

Note 2: All leads are soldered or welded to PC boards.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS: ±5V Dual Supplies**

(V+ = 5V, V- = -5V, VINH = 2.4V, VINL = 0.8V, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                             | SYMBOL                                                               | CONDITIONS                                                                       | TA            | MIN         | TYP<br>(Note 3) | MAX        | UNITS |

|-------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------|-------------|-----------------|------------|-------|

| ANALOG SWITCH                                         |                                                                      |                                                                                  | ll            |             |                 |            |       |

| Analog-Signal Range                                   | V <sub>A</sub> , V <sub>B</sub> ,<br>V <sub>X</sub> , V <sub>Y</sub> | (Note 4)                                                                         | C, E          | V-          |                 | V+         | V     |

| A-X, A-Y, B-X, B-Y<br>On-Resistance                   | Ron                                                                  | $V_A = V_B = \pm 3V$ , $I_A = I_B = 1mA$                                         | +25°C<br>C, E |             | 70              | 110<br>130 | Ω     |

| A-X, A-Y, B-X, B-Y<br>On-Resistance Match (Note 5)    | ΔRon                                                                 | VA = VB = ±3V, IA = IB = 1mA                                                     | +25°C<br>C, E |             | 3               | 7          | Ω     |

| A-X, A-Y, B-X, B-Y<br>On-Resistance Flatness (Note 6) | R <sub>FLAT</sub> (ON)                                               | $V_A = V_B = 3V$ , 0V, -3V;<br>$I_A = I_B = 1mA$                                 | +25°C<br>C, E |             | 9               | 15<br>17   | Ω     |

| A-B, X-Y Leakage Current<br>(Note 7)                  | Ι <sub>Α</sub> , Ι <sub>Β</sub> ,<br>Ιχ, Ιγ                          | $V+=5.5V; V-=-5.5V; V_{IN}=0V, 3V; V_A=\pm 4.5V; V_B=\mp 4.5V$                   | +25°C<br>C, E | -0.5<br>-20 | 0.01            | 0.5        | nA    |

| LOGIC INPUT                                           |                                                                      |                                                                                  |               |             |                 |            |       |

| IN Input Logic Threshold High                         | V <sub>INH</sub>                                                     |                                                                                  | C, E          |             | 1.6             | 2.4        | V     |

| IN Input Logic Threshold Low                          | VINL                                                                 |                                                                                  | C, E          | 0.8         | 1.6             |            | V     |

| IN Input Current Logic High or Low                    | I <sub>INH</sub> ,<br>I <sub>INL</sub>                               | V <sub>IN</sub> _ = 0.8V or 2.4V                                                 | C, E          | -1          | 0.03            | 1          | μA    |

| SWITCH DYNAMIC CHARACTE                               | RISTICS                                                              |                                                                                  |               |             |                 |            |       |

| Transition Time                                       | ttrans                                                               | VA - VB - ±5V, V1 - 5V, V - 5V,                                                  | +25°C         |             | 70              | 100        | ns    |

| Transition Time                                       | TRANS                                                                |                                                                                  | C, E          |             |                 | 125        | 113   |

| Break-Before-Make Time Delay                          | t <sub>BBM</sub>                                                     | $V_A = V_B = \pm 3V$ , $V_{+} = 5V$ , $V_{-} = -5V$ ,                            | +25°C         | 1           | 20              |            | ns    |

| Charge Injection (Nets 4)                             | 0                                                                    | $R_L = 300\Omega$ , Figure 4                                                     | C, E          |             | 1               |            | n C   |

| Charge Injection (Note 4)                             |                                                                      | $C_L = 1.0$ nF, $V_A$ or $V_B = 0$ V, Figure 5                                   | +25°C         |             | 1               | 5          | pC    |

| A-X, A-Y, B-X, B-Y Capacitance                        | Con                                                                  | $V_A = V_B = GND$ , $f = 1MHz$ , Figure 6                                        | +25°C         |             | 13              |            | pF    |

| A-X, A-Y, B-X, B-Y Isolation<br>(Note 8)              | V <sub>ISO</sub>                                                     | $R_L = 50\Omega$ , $C_L = 15pF$ , $f = 1MHz$ , $V_A = V_B = 1V_{RMS}$ , Figure 7 | +25°C         |             | -68             |            | dB    |

#### **ELECTRICAL CHARACTERISTICS: ±5V Dual Supplies (continued)**

$(V+=5V,\,V-=-5V,\,V_{INH}=2.4V,\,V_{INL}=0.8V,\,T_A=T_{MIN}\,to\,T_{MAX},\,unless\,otherwise\,noted.\,Typical\,values\,are\,at\,T_A=+25^{\circ}C.)$

| PARAMETER            | SYMBOL          | CONDITIONS                        | TA    | MIN  | TYP<br>(Note 3) | MAX | UNITS |

|----------------------|-----------------|-----------------------------------|-------|------|-----------------|-----|-------|

| POWER SUPPLY         |                 |                                   |       |      |                 |     |       |

| Power-Supply Range   | V+, V-          |                                   | C, E  | ±2.7 |                 | ±6  | V     |

| V. Supply Current    |                 | $I+$ $V_{IN} = OV \text{ or } V+$ | +25°C | -1   |                 | 1   | μA    |

| V+ Supply Current    | 1+              |                                   | C, E  | -10  |                 | 10  | ] µA  |

| V Supply Current     |                 | 1 1/ 0// //                       | +25°C | -1   |                 | 1   | μΑ    |

| V- Supply Current I- | VIIV — OV OI V+ | C, E                              | -10   |      | 10              | ]   |       |

#### **ELECTRICAL CHARACTERISTICS: +5V Single Supply**

$(V + = 5V, V - = 0V, V_{INH} = 2.4V, V_{INL} = 0.8V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                                | SYMBOL                                                               | CONDITIONS                                                                       | TA    | MIN  | TYP<br>(Note 3) | MAX | UNITS        |

|------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|-------|------|-----------------|-----|--------------|

| ANALOG SWITCH                            |                                                                      |                                                                                  |       |      |                 |     |              |

| Analog-Signal Range                      | V <sub>A</sub> , V <sub>B</sub> ,<br>V <sub>X</sub> , V <sub>Y</sub> | (Note 4)                                                                         | C, E  | V-   |                 | V+  | V            |

| A-X, A-Y, B-X, B-Y                       | Ron                                                                  | VA = VB = 3V. IA = IB = 1mA                                                      | +25°C |      | 120             | 175 | 175<br>200 Ω |

| On-Resistance                            | KON                                                                  | VA - VB - 3V, IA - IB - IIIIA                                                    | C, E  |      |                 | 200 |              |

| A-X, A-Y, B-X, B-Y                       | ΔRon                                                                 | VA = VB = 3V, IA = IB = 1mA                                                      | +25°C |      | 5               | 10  | Ω            |

| On-Resistance Match (Note 5)             | ZIVON                                                                | VA - VB - 3V, IA - IB - 1111A                                                    | C, E  |      |                 | 12  | 32           |

| A-B, X-Y Leakage Current                 | IA, IB,                                                              | $V+ = 5.5V; V_{IN} = 0V, 3V;$                                                    | +25°C | -0.5 | 0.01            | 0.5 | nA           |

| (Note 9)                                 | Ιχ, Ιγ                                                               | $V_A = 4.5V$ , 1V; $V_B = 1V$ , 4.5V                                             | C, E  | -20  |                 | 20  |              |

| LOGIC INPUT                              | •                                                                    |                                                                                  |       |      |                 |     | •            |

| IN Input Logic Threshold High            | VINH                                                                 |                                                                                  | C, E  |      | 1.6             | 2.4 | V            |

| IN Input Logic Threshold Low             | VINL                                                                 |                                                                                  | C, E  | 0.8  | 1.6             |     | V            |

| IN Input Current Logic High or Low       | I <sub>INH</sub> ,<br>I <sub>INL</sub>                               | V <sub>IN</sub> _ = 0.8V or 2.4V                                                 | C, E  | -1   | 0.03            | 1   | μΑ           |

| SWITCH DYNAMIC CHARACTE                  | RISTICS (No                                                          | te 4)                                                                            |       |      |                 |     |              |

| Transition Time                          | t==                                                                  | $V_A = V_B = 3V$ , $V_+ = 5V$ , $R_L = 300\Omega$ , Figure 3                     | +25°C |      | 110             | 175 | nc           |

| Transmon fille                           | trans                                                                |                                                                                  | C, E  |      |                 | 200 | ns           |

| Break-Before-Make Time Delay             | t <sub>BBM</sub>                                                     | $V_A = V_B = 3V$ , $V_{+} = 5V$ , $R_L = 300\Omega$ ,                            | +25°C | 1    | 20              |     | ns           |

| break-before-wake fillie belay           | rBRIM                                                                | Figure 4                                                                         | C, E  |      |                 |     | 1 113        |

| Charge Injection                         | Q                                                                    | $C_L = 1.0$ nF, $V_A$ or $V_B = 0$ V, Figure 5                                   | +25°C |      | 1.5             | 5   | рС           |

| A-X, A-Y, B-X, B-Y Capacitance           | Coff                                                                 | $V_A = V_B = GND$ , $f = 1MHz$ , Figure 6                                        | +25°C |      | 17              |     | pF           |

| A-X, A-Y, B-X, B-Y Isolation<br>(Note 8) | V <sub>ISO</sub>                                                     | $R_L = 50\Omega$ , $C_L = 15pF$ , $f = 1MHz$ , $V_A = V_B = 1V_{RMS}$ , Figure 7 | +25°C |      | -70             |     | dB           |

| POWER SUPPLY                             | •                                                                    |                                                                                  |       |      |                 |     | •            |

| Power-Supply Range                       | V+                                                                   |                                                                                  | C, E  | 2.7  |                 | 12  | V            |

| V. Cupply Current                        | 1.                                                                   | 1                                                                                | +25°C | -1   |                 | 1   |              |

| V+ Supply Current                        | I+                                                                   | VIN = 0V or V+                                                                   | C, E  | -10  |                 | 10  | μΑ           |

#### **ELECTRICAL CHARACTERISTICS: +3V Single Supply**

(V+ = 2.7V to 3.6V, V- = 0V,  $V_{INH}$  = 2.4V,  $V_{INL}$  = 0.6V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                          | SYMBOL                                                               | CONDITIONS                                                                            | TA    | MIN | TYP<br>(Note 3) | MAX  | UNITS |

|------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-----|-----------------|------|-------|

| ANALOG SWITCH                      |                                                                      |                                                                                       |       |     |                 |      |       |

| Analog-Signal Range                | V <sub>A</sub> , V <sub>B</sub> ,<br>V <sub>X</sub> , V <sub>Y</sub> | (Note 4)                                                                              | C, E  | V-  |                 | V+   | V     |

| A-X, A-Y, B-X, B-Y                 | Ron                                                                  | $V + = 3V$ , $V_A = V_B = 1.5V$ ,                                                     | +25°C |     | 250             | 900  | Ω     |

| On-Resistance                      | KON                                                                  | $I_A = I_B = 0.1 \text{mA}$                                                           | C, E  |     |                 | 1000 | 22    |

| LOGIC INPUT                        |                                                                      |                                                                                       |       |     |                 |      |       |

| IN Input Logic Threshold High      | VINH                                                                 | V+ = 3V                                                                               | C, E  |     | 0.9             | 2.4  | V     |

| IN Input Logic Threshold Low       | VINL                                                                 | V+ = 3V                                                                               | C, E  | 0.6 | 0.9             |      | V     |

| IN Input Current Logic High or Low | I <sub>INH</sub> ,<br>I <sub>INL</sub>                               | VIN_ = 0V or V+                                                                       | C, E  | -1  | 0.03            | 1    | μΑ    |

| SWITCH DYNAMIC CHARACTE            | RISTICS (No                                                          | te 4)                                                                                 |       |     |                 |      |       |

| Transition Time                    | tTDANIO                                                              | $V_A = 1.5V$ , $V_B = 0V$ , $V_{+} = 3V$ , $V_{-} = 0V$ , $R_L = 1k\Omega$ , Figure 3 | +25°C |     | 150             | 400  | nc    |

| Transition Time                    | ttrans                                                               |                                                                                       | C, E  |     |                 | 500  | ns    |

| Break-Before-Make Time Delay       | VA = $1.5V$ , $V_B = 0V$ , $V_{+} = 3V$ ,                            | +25°C                                                                                 | 2     | 150 |                 | ns   |       |

| bleak-belole-Make Time Delay       | tBBM                                                                 | $V$ - = 0V, $R_L$ = 1k $\Omega$ , Figure 4                                            | C, E  |     |                 |      | 1115  |

| Charge Injection                   | Q                                                                    | $C_L = 1.0$ nF, $V_A$ or $V_B = 0$ V, Figure 5                                        | +25°C |     | 1               | 5    | рС    |

| POWER SUPPLY                       | •                                                                    |                                                                                       |       |     |                 |      | •     |

| Power-Supply Range                 | V+, V-                                                               |                                                                                       | C, E  | 2.7 |                 | 12   | V     |

| V. Supply Current                  |                                                                      |                                                                                       | +25°C | -1  |                 | 1    |       |

| V+ Supply Current                  | I+                                                                   | VIN = 0V  or  V+                                                                      | C, E  | -10 |                 | 10   | μΑ    |

- Note 3: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

- Note 4: Guaranteed by design.

- Note 5:  $\Delta RON = \Delta RON(MAX) \Delta RON(MIN)$ .

- **Note 6:** Resistance flatness is defined as the difference between the maximum and the minimum value of on-resistance as measured over the specified analog-signal range.

- Note 7: Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at +25°C.

- **Note 8:** Off isolation =  $20\log_{10} [(V_X \text{ or } V_Y) / (V_A \text{ or } V_B)]$ ,  $V_A \text{ or } V_B = \text{ output}$ ,  $V_A \text{ or } V_B = \text{ input to off switch}$ .

- Note 9: Leakage testing for single-supply operation guaranteed by testing with dual supplies.

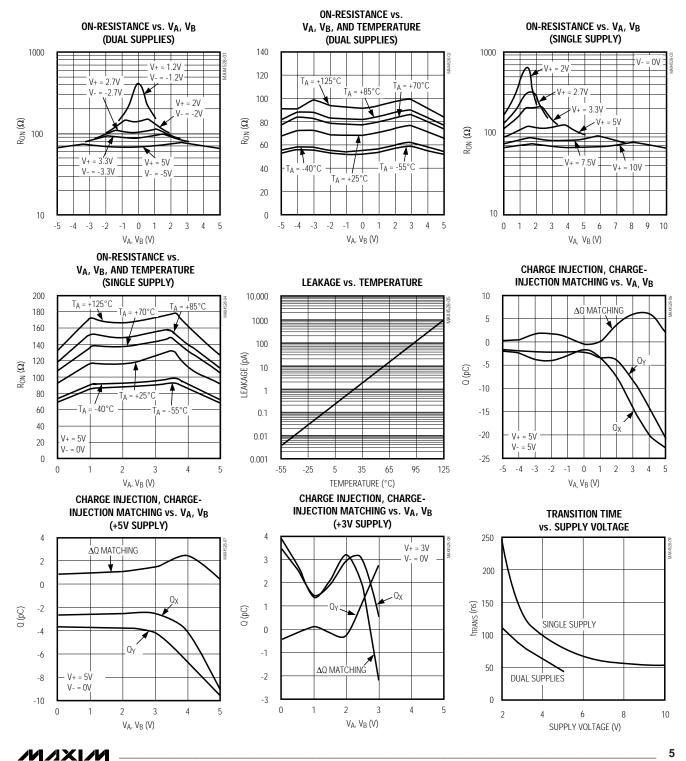

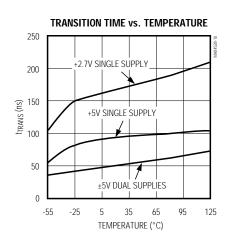

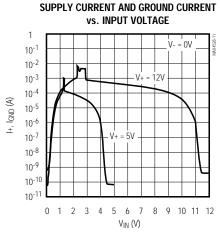

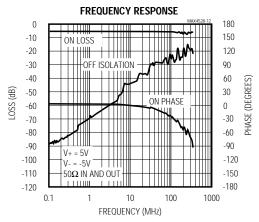

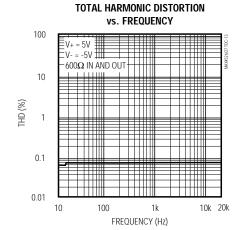

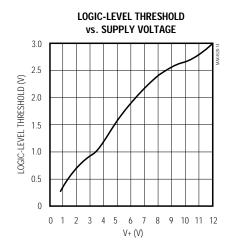

Typical Operating Characteristics

$(V + = 5V, V - = -5V, GND = 0V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### Typical Operating Characteristics (continued)

$(V + = 5V, V - = -5V, GND = 0V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### Pin Description

| PIN | NAME                              | FUNCTION                                                                                                       |  |

|-----|-----------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| 1   | А                                 | Analog-Switch Input Terminal A. Connected to Y when IN is low; connected to X when IN is high.                 |  |

| 2   | В                                 | Analog-Switch Input Terminal B. Connected to X when IN is low; connected to Y when IN is high.                 |  |

| 3   | GND                               | Ground. Connect GND to digital ground. (Analog signals have no ground reference; they are limited to V+ and V) |  |

| 4   | IN                                | Logic-Level Control Inputs (see <i>Truth Table</i> )                                                           |  |

| 5   | V-                                | Negative Analog Supply-Voltage Input. Connect V- to GND for single-supply operation.                           |  |

| 6   | Υ                                 | Analog-Switch Output Terminal Y                                                                                |  |

| 7   | X Analog-Switch Output Terminal X |                                                                                                                |  |

| 8   | V+                                | Positive Analog/Digital Supply-Voltage Input. Internally connected to substrate.                               |  |

**Note:** Pins A, B, X, and Y are identical and interchangeable. Any may be considered as an input or output; signals pass equally well in either direction. However, AC symmetry is best when A and B are the inputs and X and Y are the outputs. Reduce AC balance in critical applications by using A and X or A and Y as the input, and B and X or B and Y as the output.

#### Detailed Description

The MAX4528 is a phase-reversal analog switch consisting of two normally open and two normally closed CMOS analog switches arranged in a bridge configuration. Analog signals are put into two input pins and taken out of two output pins. A logic-level signal controls whether the input signal is routed through normally or inverted. A low-resistance DC path goes from inputs to outputs at all times, yet isolation between the two signal paths is excellent. Analog signals range from V- to V+.

These parts are characterized and optimized with ±5V supplies, and can operate from a single supply.

The MAX4528 is designed for DC and low-frequencysignal phase-reversal applications, such as chopper amplifiers, modulator/demodulators, and self-zeroing or self-calibrating circuits. Unlike conventional CMOS switches externally wired in a bridge configuration, both DC and AC symmetry are optimized with a small 8-pin configuration that allows simple board layout and isolation of logic signals from analog signals.

### Power-Supply Considerations

Overview

The MAX4528's construction is typical of most CMOS analog switches. It has three supply pins: V+, V-, and GND. V+ and V- drive the internal CMOS switches and set the analog-voltage limits on any switch. Reverse ESD-protection diodes are internally connected between each analog-signal pin and both V+ and V-. One of these diodes conducts if any analog signal exceeds V+ or V-.

Virtually all of the analog leakage current is through the ESD diodes to V+ or V-. Although the ESD diodes on a given signal pin are identical and therefore fairly well balanced, they are reverse biased differently. Each is biased by either V+ or V- and the analog signal. This means their leakages vary as the signal varies. The *difference* in the two diode leakages from the signal path to the V+ and V- pins constitutes the analog-signal-path leakage current. All analog leakage current flows to the supply terminals, not to the other switch terminal. This explains how both sides of a given switch can show leakage currents of either the same or opposite polarity.

There is no connection between the analog-signal paths and GND. The analog-signal paths consist of an N-channel and P-channel MOSFET with their sources and drains paralleled and their gates driven out-of-phase to V+ and V- by the logic-level translators.

V+ and GND power the internal logic and logic-level translator and set the input logic threshold. The logic-level translator converts the logic levels to switched V+ and V- signals to drive the analog switches' gates. This drive signal is the only connection between GND and the analog supplies. V+ and V- have ESD-protection diodes to GND. The logic-level input has ESD protection to V+ and V-, but not to GND, so the logic signal can go below GND (as low as V-) when bipolar supplies are used.

Increasing V- has no effect on the logic-level thresholds, but it does increase the drive to the internal P-channel switches, reducing overall switch on-resistance. V- also sets the negative limit of the analog-signal voltage.

The logic-level input pin (IN) has ESD-protection diodes to V+ and V- but not to GND, so it can be safely driven to V+ and V-. The logic-level threshold ( $V_{\rm IN}$ ) is CMOS/TTL compatible when V+ is between 4.5V and 12V (see *Typical Operating Characteristics*).

#### **Bipolar Supplies**

The MAX4528 operates with bipolar supplies between  $\pm 2.7V$  and  $\pm 6.0V$ . The V+ and V- supplies need not be symmetrical, but their sum cannot exceed the 13V absolute maximum rating (see *Absolute Maximum Ratings*).

#### Single Supply

The MAX4528 operates from a single +2.7V to +12V supply when V- is connected to GND. Observe all of the bipolar precautions when operating from a single supply.

#### \_Applications Information

The MAX4528 is designed for DC and low-frequency-signal phase-reversal applications. Both DC and AC symmetry are optimized for use with  $\pm 5V$  supplies.

#### Signal Phase/Polarity Reversal

The MAX4528 can reverse the phase or polarity of a pair of signals that are out-of-phase and balanced to ground. This is done by routing signals through the MAX4528 and, under control of IN, reversing the two signals paths inside the switch before sending out to a balanced output. Figure 1 shows a typical example.

The MAX4528 cannot reverse the phase or polarity of a single grounded signal, as can be done with an inverting op amp or transformer.

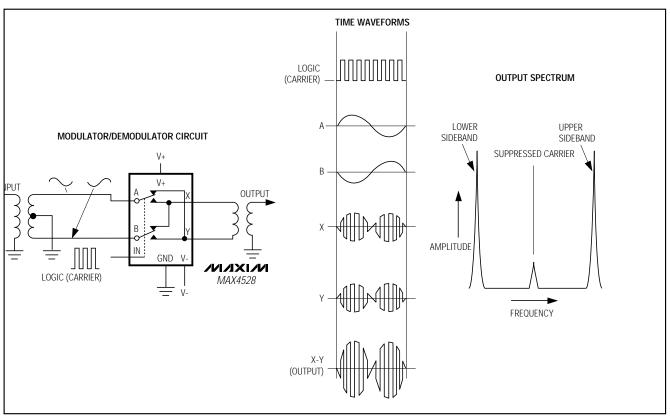

#### Balanced Modulator/Demodulator

The MAX4528 can be used as a balanced modulator/demodulator at carrier frequencies up to 100kHz (Figure 2). Higher frequencies are possible, but as frequency increases, small imbalances in the MAX4528's internal capacitance and resistance gradually impair performance. Similarly, imbalances in external circuit capacitance and resistance to GND reduce overall carrier suppression.

The carrier is applied as a logic-level square wave to IN. (Note that this voltage can go as negative as V-.) For best carrier suppression, the power-supply voltages should be equal, the square wave should have a precise 50% duty cycle, and both the input and output signals should be symmetrical around ground. Bypass V+ and V- to GND with 0.1µF ceramic capacitors, as close to the IC pins as possible. In critical applications, carrier suppression can be optimized by trimming duty cycle, DC bias around GND, or external source and load capacitance.

In signal lines, balancing both capacitance and resistance to GND produces the best carrier suppression.

Transformer coupling of input and output signals provides the best isolation and carrier suppression. Transformers can also provide signal filtering, impedance matching, or low-noise voltage gain. Use a center-tapped transformer or high-resistance voltage divider to provide a DC path to GND on either the input or output signal. This ensures a DC path to GND and symmetrical operation of the internal switches.

Figure 1. Typical Application Circuits

8 \_\_\_\_\_\_ /N/X///

9

## Low-Voltage, Phase-Reversal Analog Switch

Figure 2. Balanced Modulator/Demodulator

#### \_Test Circuits/Timing Diagrams

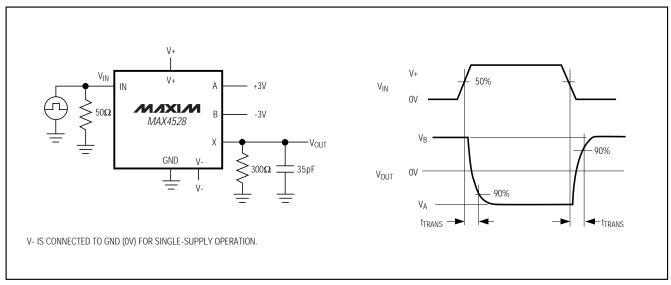

Figure 3. Address Transition Time

## Test Circuits/Timing Diagrams (continued)

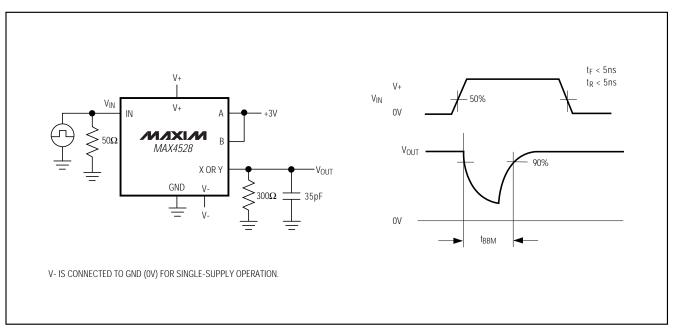

Figure 4. Break-Before-Make Interval

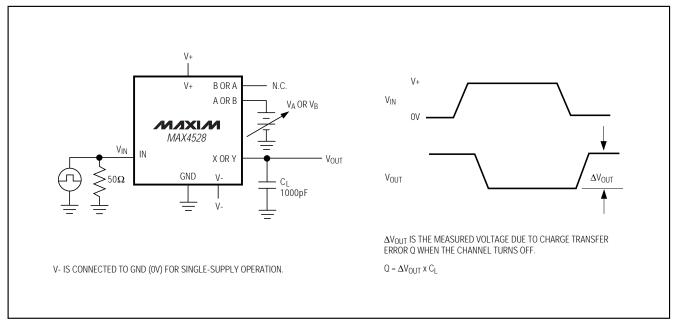

Figure 5. Charge Injection

10 \_\_\_\_\_\_ **/\/**/**X**|**/\/**

### Test Circuits/Timing Diagrams (continued)

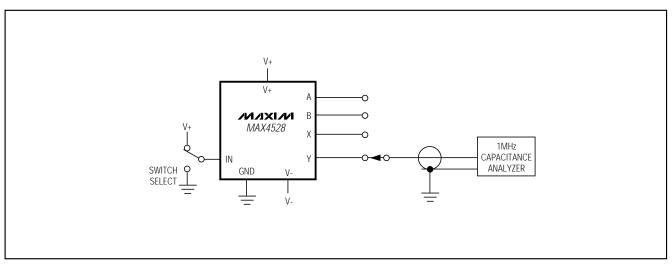

Figure 6. A, B, X, Y Capacitance

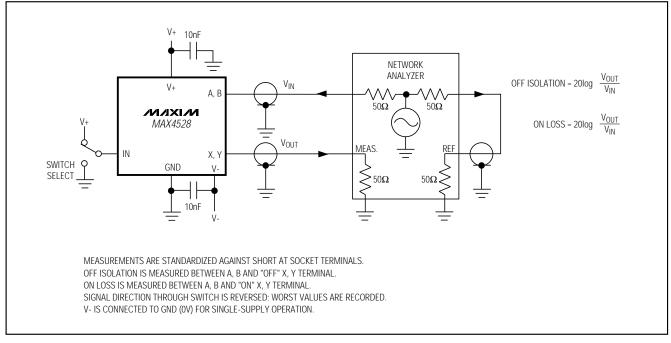

Figure 7. Off Isolation and On Loss

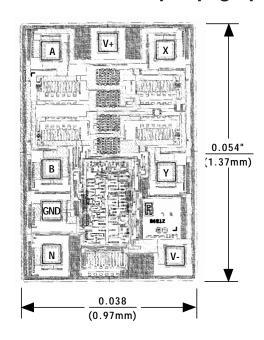

\_Chip Topography

TRANSISTOR COUNT: 141

SUBSTRATE IS INTERNALLY CONNECTED TO V+

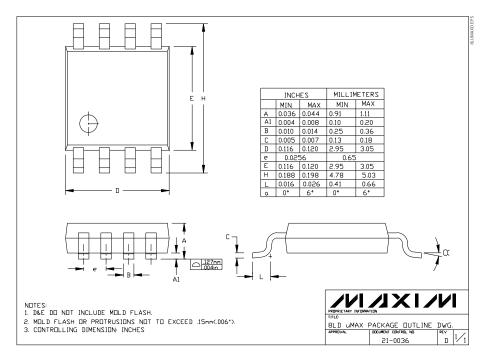

#### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1998 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.