# Advance Information

# Dual Differential (EIA-422-A)/ Quad Single-Ended (EIA-423-A) Line Drivers

The AM26LS30 is a low power Schottky set of line drivers which can be configured as two differential drivers which comply with EIA–422–A standards, or as four single–ended drivers which comply with EIA–423–A standards. A mode select pin and appropriate choice of power supplies determine the mode. Each driver can source and sink currents in excess of 50 mA.

In the differential mode (EIA–422–A), the drivers can be used up to 10 Mbaud. A disable pin for each driver permits setting the outputs into a high impedance mode within a  $\pm 10$  V common mode range.

In the single–ended mode (EIA–423–A), each driver has a slew rate control pin which permits setting the slew rate of the output signal so as to comply with EIA–423–A and FCC requirements and to reduce crosstalk. When operated from symmetrical supplies ( $\pm 5.0 \text{ V}$ ), the outputs exhibit zero imbalance.

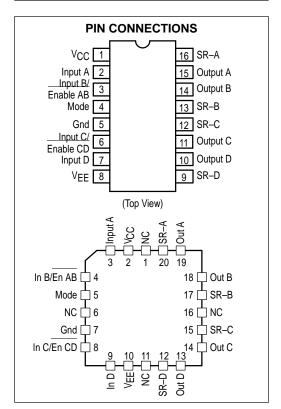

The AM26LS30 is available in a 16-pin plastic DIP and surface mount package. Operating temperature range is -40° to +85°C.

- Operates as Two Differential EIA–422–A Drivers, or Four Single–Ended EIA–423–A Drivers

- High Impedance Outputs in Differential Mode

- Short Circuit Current Limit In Both Source and Sink Modes

- ± 10 V Common Mode Range on High Impedance Outputs

- ± 15 V Range on Inputs

- Low Current PNP Inputs Compatible with TTL, CMOS, and MOS Outputs

- Individual Output Slew Rate Control in Single-Ended Mode

- Replacement for the AMD AM25LS30 and National Semiconductor DS3691

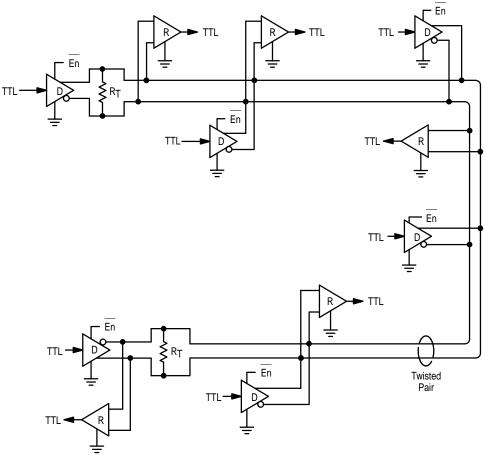

#### **Representative Block Diagrams** Single-Ended Mode **Differential Mode** EIA-423-A EIA-422-A Enable AB SR-A Out A Input A Out B SR-B Out B Out C Input D Out D SR-C Out C Enable CD SR-D $V_{CC}-1$ Gnd-5 Mode-4 VEE-8 Out D

This document contains information on a new product. Specifications and information herein are subject to change without notice.

## AM26LS30

# DUAL DIFFERENTIAL/ QUAD SINGLE-ENDED LINE DRIVERS

SEMICONDUCTOR TECHNICAL DATA

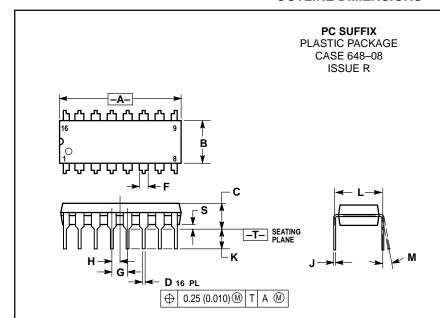

PC SUFFIX PLASTIC PACKAGE CASE 648

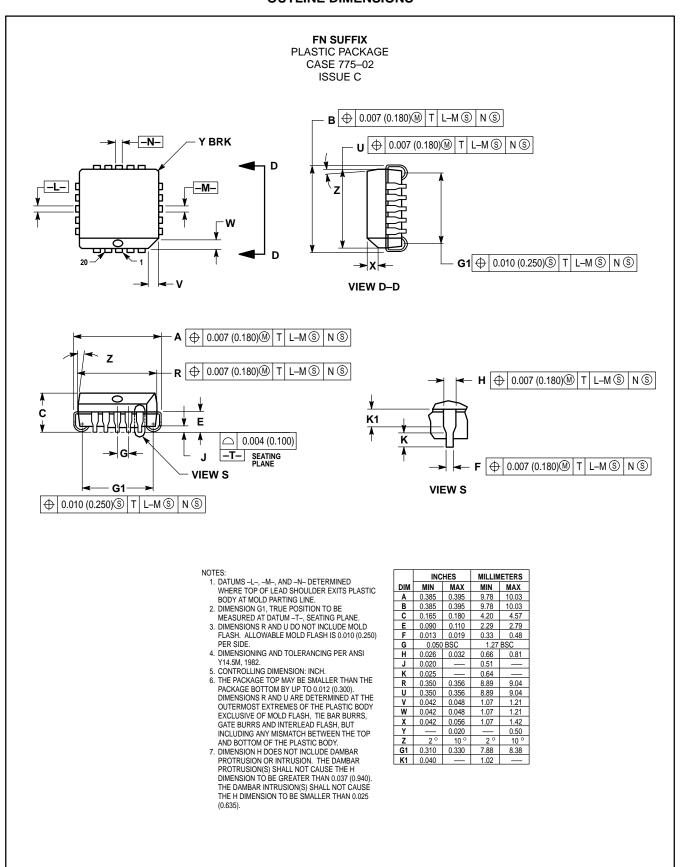

FN SUFFIX PLASTIC PACKAGE CASE 775

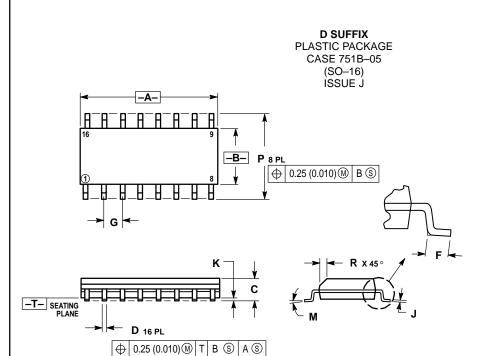

D SUFFIX PLASTIC PACKAGE CASE 751B (SO–16)

#### ORDERING INFORMATION

| Device     | Operating<br>Temperature Range                      | Package     |

|------------|-----------------------------------------------------|-------------|

| AM26LS30PC |                                                     | Plastic DIP |

| MC26LS30D  | $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | SO-16       |

| AM26LS30FN |                                                     | PLCC-20     |

© Motorola, Inc. 1995

#### MAXIMUM OPERATING CONDITIONS (Pin numbers refer to DIP and SO-16 packages only.)

| Rating                                                                                                             | Symbol          | Value                    | Unit |

|--------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|------|

| Power Supply Voltage                                                                                               | V <sub>CC</sub> | -0.5, +7.0<br>-7.0, +0.5 | Vdc  |

| Input Voltage (All Inputs)                                                                                         | V <sub>in</sub> | -0.5, +20                | Vdc  |

| Applied Output Voltage when in High Impedance Mode (V <sub>CC</sub> = 5.0 V, Pin 4 = Logic 0, Pins 3, 6 = Logic 1) | V <sub>za</sub> | ±15                      | Vdc  |

| Output Voltage with V <sub>CC</sub> , V <sub>EE</sub> = 0 V                                                        | $V_{zb}$        | ±15                      |      |

| Output Current                                                                                                     | lo              | Self limiting            | _    |

| Junction Temperature                                                                                               | TJ              | <del>-65, +150</del>     | °C   |

Devices should not be operated at these limits. The "Recommended Operating Conditions" table provides conditions for actual device operation.

#### **RECOMMENDED OPERATING CONDITIONS**

| Rating                                                                                                                      | Symbol                                                | Min             | Тур          | Max               | Unit |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|--------------|-------------------|------|

| Power Supply Voltage (Differential Mode)                                                                                    | V <sub>CC</sub>                                       | +4.75<br>-0.5   | 5.0<br>0     | +5.25<br>+0.3     | Vdc  |

| Power Supply Voltage (Single–Ended Mode)                                                                                    | V <sub>CC</sub>                                       | +4.75<br>-5.25  | +5.0<br>-5.0 | +5.25<br>-4.75    |      |

| Input Voltage (All Inputs) Applied Output Voltage (when in High Impedance Mode) Applied Output Voltage, V <sub>CC</sub> = 0 | V <sub>in</sub><br>V <sub>za</sub><br>V <sub>zb</sub> | 0<br>-10<br>-10 | 1 1 1        | +15<br>+10<br>+10 | Vdc  |

| Output Current                                                                                                              | lo                                                    | -65             | -            | +65               | mA   |

| Operating Ambient Temperature (See text)                                                                                    | TA                                                    | -40             | _            | +85               | °C   |

All limits are not necessarily functional concurrently.

### $\textbf{ELECTRICAL CHARACTERISTICS} \hspace{0.2cm} \text{(EIA-422-A differential mode, Pin 4} \leqslant 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant \text{V}_{CC} \leqslant 5.25 \text{ V}, \\ = 0.8 \text{ V}, -40^{\circ}\text{C} \\ <\text{T}_{A} < 85^{\circ}\text{C}, 4.75 \text{ V} \leqslant 1.05 \text{$ $V_{\mbox{\scriptsize EE}}$ = Gnd, unless otherwise noted. Pin numbers refer to DIP and SO-16 packages only.)

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Symbol                                                                                                                   | Min                                               | Тур                           | Max                               | Unit                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------------|

| Output Voltage (see Figure 1)   Differential, $R_L = \infty$ , $V_{CC} = 5.25 \text{ V}$ Differential, $R_L = 100 \Omega$ , $V_{CC} = 4.75 \text{ V}$ Change in Differential Voltage, $R_L = 100 \Omega$ (Note 4)   Offset Voltage, $R_L = 100 \Omega$ Change in Offset Voltage*, $R_L = 100 \Omega$                                                                                                                                                                                             | V <sub>OD1</sub>  <br> V <sub>OD2</sub>  <br>  <sub>\Delta V<sub>OD2</sub> </sub><br>  <sub>\Delta V<sub>OS</sub> </sub> | _<br>2.0<br>_<br>_<br>_                           | 4.2<br>2.6<br>10<br>2.5<br>10 | 6.0<br>-<br>400<br>3.0<br>400     | Vdc<br>Vdc<br>mVdc<br>Vdc<br>mVdc |

| Output Current (each output) Power Off Leakage, $V_{CC} = 0$ , $-10 \text{ V} \leq V_O \leq +10 \text{ V}$ High Impedance Mode, $V_{CC} = 5.25 \text{ V}$ , $-10 \text{ V} \leq V_O \leq +10 \text{ V}$ Short Circuit Current (Note 2) High Output Shorted to Pin 5 ( $T_A = 25^{\circ}$ C) High Output Shorted to Pin 5 ( $-40^{\circ}$ C $< T_A < +85^{\circ}$ C) Low Output Shorted to +6.0 V ( $T_A = 25^{\circ}$ C) Low Output Shorted to +6.0 V ( $-40^{\circ}$ C $< T_A < +85^{\circ}$ C) | IOLK IOZ ISC- ISC- ISC+ ISC+                                                                                             | -100<br>-100<br>-150<br>-150<br>60<br>50          | 0<br>0<br>-95<br>-<br>75<br>- | +100<br>+100<br>-60<br>-50<br>150 | μA<br>mA                          |

| Inputs Low Level Voltage High Level Voltage Current @ $V_{in} = 2.4 \text{ V}$ Current @ $V_{in} = 15 \text{ V}$ Current @ $V_{in} = 0.4 \text{ V}$ Current, $0 \le V_{in} \le 15 \text{ V}$ , $V_{CC} = 0$ Clamp Voltage ( $I_{in} = -12 \text{ mA}$ )                                                                                                                                                                                                                                          | VIL<br>VIH<br>IIH<br>IIL<br>IIX<br>VIK                                                                                   | _<br>2.0<br>_<br>_<br>_<br>_200<br>_<br>_<br>_1.5 | -<br>0<br>0<br>-8.0<br>0      | 0.8<br>-<br>40<br>100<br>-<br>-   | Vdc<br>Vdc<br>μA                  |

| Power Supply Current ( $V_{CC}$ = +5.25 V, Outputs Open)<br>(0 $\leq$ Enable $\leq$ $V_{CC}$ )                                                                                                                                                                                                                                                                                                                                                                                                   | ICC                                                                                                                      | _                                                 | 16                            | 30                                | mA                                |

NOTES: 1. All voltages measured with respect to Pin 5.

- 2. Only one output shorted at a time, for not more than 1 second.

3. Typical values established at +25°C,  $V_{CC}$  = +5.0 V,  $V_{EE}$  = -5.0 V.

4.  $V_{in}$  switched from 0.8 to 2.0 V.

5. Imbalance is the difference between  $|V_{O2}|$  with  $V_{in}$  < 0.8 V and  $|V_{O2}|$  with  $V_{in}$  > 2.0 V.

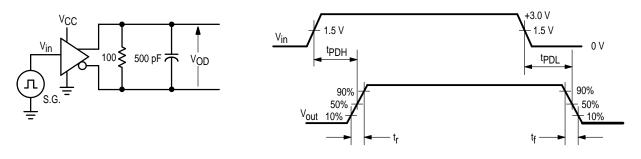

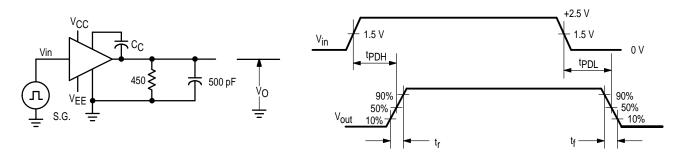

**TIMING CHARACTERISTICS** (EIA–422–A differential mode, Pin  $4 \le 0.8 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ ,  $V_{CC} = 5.0 \text{ V}$ ,  $V_{EE} = \text{Gnd}$ , (Notes 1 and 3) unless otherwise noted.)

| Characteristic                                                                                                                                                                                 | Symbol                                                                       | Min              | Тур                     | Max                      | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|-------------------------|--------------------------|------|

| Differential Output Rise Time (Figure 3)                                                                                                                                                       | t <sub>r</sub>                                                               | _                | 70                      | 200                      | ns   |

| Differential Output Fall Time (Figure 3)                                                                                                                                                       | t <sub>f</sub>                                                               | _                | 70                      | 200                      | ns   |

| Propagation Delay Time – Input to Differential Output<br>Input Low to High (Figure 3)<br>Input High to Low (Figure 3)                                                                          | tPDH<br>tPDL                                                                 | -<br>-           | 90<br>90                | 200<br>200               | ns   |

| Skew Timing (Figure 3)    tpDH to tpDL   for Each Driver  Max to Min tpDH Within a Package  Max to Min tpDL Within a Package                                                                   | <sup>†</sup> SK1<br><sup>†</sup> SK2<br><sup>†</sup> SK3                     | -<br>-<br>-      | 9.0<br>2.0<br>2.0       | -<br>-<br>-              | ns   |

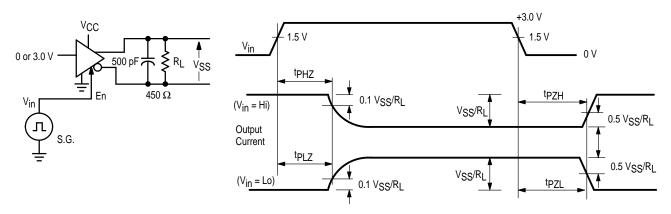

| Enable Timing (Figure 4) Enable to Active High Differential Output Enable to Active Low Differential Output Enable to 3–State Output From Active High Enable to 3–State Output From Active Low | <sup>†</sup> PZH<br><sup>†</sup> PZL<br><sup>†</sup> PHZ<br><sup>†</sup> PLZ | -<br>-<br>-<br>- | 150<br>190<br>80<br>110 | 300<br>350<br>350<br>300 | ns   |

**ELECTRICAL CHARACTERISTICS** (EIA–423–A single–ended mode, Pin  $4 \ge 2.0 \text{ V}$ ,  $-40^{\circ}\text{C} < T_A < 85^{\circ}\text{C}$ ,  $4.75 \text{ V} \le |V_{CC}|$ ,  $|V_{EE}| \le 5.25 \text{ V}$ , (Notes 1 and 3) unless otherwise noted).

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                    | Symbol                                                       | Min                                               | Тур                      | Max                              | Unit                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------|--------------------------|----------------------------------|-------------------------|

| Output Voltage ( $V_{CC} =  V_{EE}  = 4.75 \text{ V}$ )<br>Single–Ended Voltage, $R_L = \infty$ (Figure 2)<br>Single–Ended Voltage, $R_L = 450 \Omega$ , (Figure 2)<br>Voltage Imbalance (Note 5), $R_L = 450 \Omega$                                                                                                                                                                                                                             | V <sub>O1</sub>  <br> V <sub>O2</sub>  <br> ΔV <sub>O2</sub> | 4.0<br>3.6<br>–                                   | 4.2<br>3.95<br>0.05      | 6.0<br>6.0<br>0.4                | Vdc                     |

| Slew Control Current (Pins 16, 13, 12, 9)                                                                                                                                                                                                                                                                                                                                                                                                         | ISLEW                                                        | _                                                 | ±120                     | -                                | μΑ                      |

| Output Current (Each Output)  Power Off Leakage, $V_{CC} = V_{EE} = 0$ , $-6.0 \text{ V} \le V_O \le +6.0 \text{ V}$ Short Circuit Current (Output Short to Ground, Note 2) $V_{in} \le 0.8 \text{ V} (T_A = 25^{\circ}\text{C})$ $V_{in} \le 0.8 \text{ V} (-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C})$ $V_{in} \ge 2.0 \text{ V} (T_A = 25^{\circ}\text{C})$ $V_{in} \ge 2.0 \text{ V} (-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C})$ | IOLK ISC+ ISC+ ISC- ISC-                                     | -100<br>60<br>50<br>-150<br>-150                  | 0<br>80<br>-<br>-95<br>- | +100<br>150<br>150<br>-60<br>-50 | μA<br>mA                |

| Inputs Low Level Voltage High Level Voltage Current @ $V_{in} = 2.4 \text{ V}$ Current @ $V_{in} = 15 \text{ V}$ Current @ $V_{in} = 0.4 \text{ V}$ Current, $0 \le V_{in} \le 15 \text{ V}$ , $V_{CC} = 0$ Clamp Voltage ( $I_{in} = -12 \text{ mA}$ )                                                                                                                                                                                           | V <sub>IL</sub><br>VIH<br>IIH<br>IIL<br>IIX<br>VIK           | _<br>2.0<br>_<br>_<br>_<br>_200<br>_<br>_<br>_1.5 | -<br>0<br>0<br>-8.0<br>0 | 0.8<br>-<br>40<br>100<br>-<br>-  | Vdc<br>Vdc<br>μA<br>Vdc |

| Power Supply Current (Outputs Open)<br>$V_{CC} = +5.25 \text{ V}, V_{EE} = -5.25 \text{ V}, V_{in} = 0.4 \text{ V}$                                                                                                                                                                                                                                                                                                                               | ICC<br>IEE                                                   | -<br>-22                                          | 17<br>-8.0               | 30<br>-                          | mA                      |

**TIMING CHARACTERISTICS** (EIA–423–A single–ended mode, Pin 4  $\geq$  2.0 V,  $T_A$  = 25°C,  $V_{CC}$  = 5.0 V,  $V_{EE}$  = –5.0 V, (Notes 1 and 3) unless otherwise noted.)

| Characteristic                                                  | Symbol           | Min | Тур  | Max | Unit  |

|-----------------------------------------------------------------|------------------|-----|------|-----|-------|

| Output Timing (Figure 5)                                        |                  |     |      |     |       |

| Output Rise Time, $C_C = 0$                                     | t <sub>r</sub>   | -   | 65   | 300 | ns    |

| Output Fall Time, C <sub>C</sub> = 0                            | tf               | _   | 65   | 300 |       |

| Output Rise Time, C <sub>C</sub> = 50 pF                        | t <sub>r</sub>   | _   | 3.0  | _   | μs    |

| Output Fall Time, $C_C = 50 \text{ pF}$                         | tf               | -   | 3.0  | _   |       |

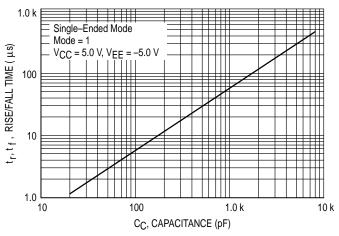

| Rise Time Coefficient (Figure 16)                               | C <sub>rt</sub>  | _   | 0.06 | -   | μs/pF |

| Propagation Delay Time, Input to Single Ended Output (Figure 5) |                  |     |      |     | ns    |

| Input Low to High, $C_C = 0$                                    | t <sub>PDH</sub> | _   | 100  | 300 |       |

| Input High to Low, $C_C = 0$                                    | t <sub>PDL</sub> | _   | 100  | 300 |       |

| Skew Timing, C <sub>C</sub> = 0 (Figure 5)                      |                  |     |      |     | ns    |

| tpDH to tpDL for Each Driver                                    | t <sub>SK4</sub> | _   | 15   | _   |       |

| Max to Min tpDH Within a Package                                | tSK5             | _   | 2.0  | _   |       |

| Max to Min tpDL Within a Package                                | tSK6             | _   | 5.0  | _   |       |

Table 1

|              |      |      |      | Inp | uts |   |   |   | Out | puts |   |

|--------------|------|------|------|-----|-----|---|---|---|-----|------|---|

| Operation    | vcc  | VEE  | Mode | Α   | В   | С | D | Α | В   | С    | D |

| Differential | +5.0 | Gnd  | 0    | 0   | 0   | 0 | 0 | 0 | 1   | 1    | 0 |

| (EIA-422-A)  |      |      | 0    | 1   | 0   | 0 | 1 | 1 | 0   | 0    | 1 |

| ,            |      |      | 0    | Х   | 1   | 0 | 1 | Z | Z   | 0    | 1 |

|              |      |      | 0    | 1   | 0   | 0 | 0 | 1 | 0   | 1    | 0 |

|              |      |      | 0    | 0   | 0   | 0 | 1 | 0 | 1   | 0    | 1 |

|              |      |      | 0    | 1   | 0   | 1 | Χ | 1 | 0   | Z    | Z |

| Single-Ended | +5.0 | -5.0 | 1    | 0   | 0   | 0 | 0 | 0 | 0   | 0    | 0 |

| (EIA-423-A)  |      |      | 1    | 1   | 0   | 0 | 0 | 1 | 0   | 0    | 0 |

|              |      |      | 1    | 0   | 1   | 0 | 0 | 0 | 1   | 0    | 0 |

|              |      |      | 1    | 0   | 0   | 1 | 0 | 0 | 0   | 1    | 0 |

|              |      |      | 1    | 0   | 0   | 0 | 1 | 0 | 0   | 0    | 1 |

| Х            | 0    | Х    | Х    | Х   | Х   | Х | Χ | Z | Z   | Z    | Z |

X = Don't Care

**Figure 1. Differential Output Test**

**S** R<sub>L</sub>/2 (0.8 or 2.0 V)  $V_{OD2}$  $R_{L}/2$ Mode = 0

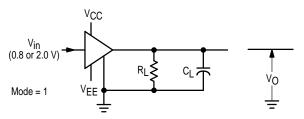

Figure 2. Single-Ended Output Test

Figure 3. Differential Mode Rise/Fall Time and Data Propagation Delay

- **NOTES:** 1. S.G. set to:  $f \le 1.0$  MHz; duty cycle = 50%;  $t_f$ ,  $t_f$ ,  $\le 10$  ns. 2.  $t_{SK1} = |t_{PDH} t_{PDL}|$  for each driver. 3.  $t_{SK2}$  computed by subtracting the shortest  $t_{PDH}$  from the longest  $t_{PDH}$  of the 2 drivers within a package. 4.  $t_{SK3}$  computed by subtracting the shortest  $t_{PDL}$  from the longest  $t_{PDL}$  of the 2 drivers within a package.

Z = High Impedance (Off)

Figure 4. Differential Mode Enable Timing

**NOTES:** 1. S.G. set to:  $f \le 1.0$  MHz; duty cycle = 50%;  $t_p$ ,  $t_f$ ,  $\le 10$  ns. 2. Above tests conducted by monitoring output current levels.

Figure 5. Single-Ended Mode Rise/Fall Time and Data Propagation Delay

**NOTES:** 1. S.G. set to:  $f \le 100$  kHz; duty cycle = 50%;  $t_f$ ,  $t_f$ ,  $\le 10$  ns.

- 2. t<sub>SK4</sub> = |t<sub>PDH</sub>-t<sub>PDL</sub>| for each driver.

3. t<sub>SK5</sub> computed by subtracting the shortest t<sub>PDH</sub> from the longest t<sub>PDH</sub> of the 4 drivers within a package.

4. t<sub>SK6</sub> computed by subtracting the shortest t<sub>PDL</sub> from the longest t<sub>PDL</sub> of the 4 drivers within a package.

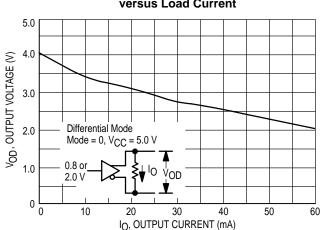

Figure 6. Differential Output Voltage versus Load Current

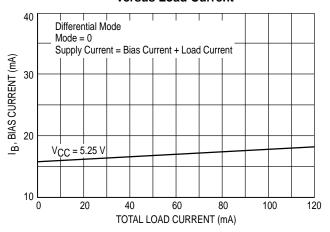

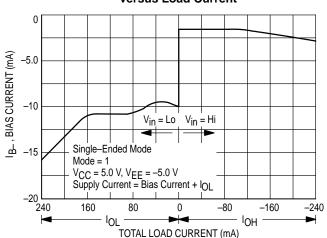

Figure 7. Internal Bias Current versus Load Current

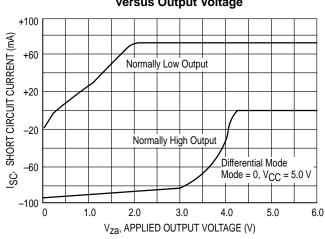

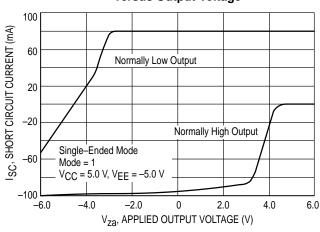

Figure 8. Short Circuit Current versus Output Voltage

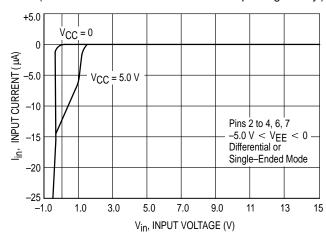

Figure 9. Input Current versus Input Voltage

(Pin numbers refer to DIP and SO-16 packages only.)

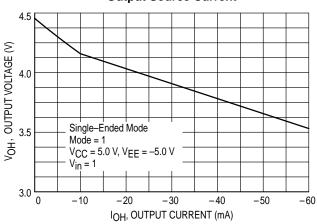

Figure 10. Output Voltage versus

Output Source Current

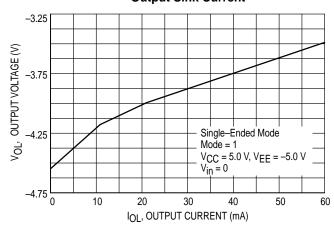

Figure 11. Output Voltage versus Output Sink Current

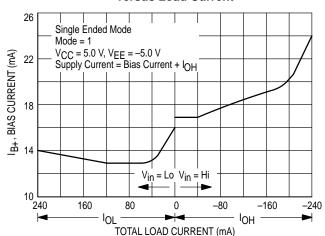

Figure 12. Internal Positive Bias Current versus Load Current

Figure 13. Internal Negative Bias Current versus Load Current

Figure 14. Short Circuit Current versus Output Voltage

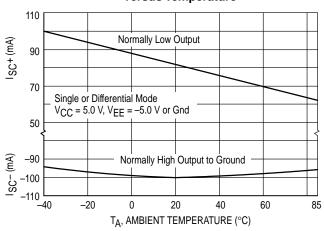

Figure 15. Short Circuit Current versus Temperature

Figure 16. Rise/Fall Time versus Capacitance

#### **APPLICATIONS INFORMATION**

(Pin numbers refer to DIP and SO-16 packages only.)

#### Description

The AM26LS30 is a dual function line driver – it can be configured as two differential output drivers which comply with EIA–422–A Standard, or as four single–ended drivers which comply with EIA–423–A Standard. The mode of operation is selected with the Mode pin (Pin 4) and appropriate power supplies (see Table 1). Each of the four outputs is capable of sourcing and sinking 60 to 70 mA while providing sufficient voltage to ensure proper data transmission.

As differential drivers, data rates to 10 Mbaud can be transmitted over a twisted pair for a distance determined by the cable characteristics. EIA-422-A Standard provides guidelines for cable length versus data rate. The advantage of a differential (balanced) system over a single-ended system is greater noise immunity, common mode rejection, and higher data rates.

Where extraneous noise sources are not a problem, the AM26LS30 may be configured as four single–ended drivers transmitting data rates to 100 Kbaud. Crosstalk among wires within a cable is controlled by the use of the slew rate control pins on the AM26LS30.

# Mode Selection (Differential Mode)

In this mode (Pins 4 and 8 at ground), only a +5.0 V supply  $\pm5\%$  is required at V<sub>CC</sub>. Pins 2 and 7 are the driver inputs, while Pins 10, 11, 14 and 15 are the outputs (see Block Diagram on page 1). The two outputs of a driver are always complementary and the differential voltage available at each pair of outputs is shown in Figure 6 for V<sub>CC</sub> = 5.0 V. The differential output voltage will vary directly with V<sub>CC</sub>. A "high" output can only source current, while a "low" output can only sink current (except for short circuit current – see Figure 8).

The two outputs will be in a high impedance mode when the respective Enable input (Pin 3 or 6) is high, or if  $V_{CC} \le 1.1 \text{ V}$ . Output leakage current over a common mode range of  $\pm$  10 V is typically less than 1.0  $\mu$ A.

The outputs have short circuit current limiting, typically, less than 100 mA over a voltage range of 0 to +6.0 V (see Figure 8). Short circuits should not be allowed to last indefinitely as the IC may be damaged.

Pins 9, 12, 13 and 16 are not normally used when in this mode, and should be left open.

#### (Single-Ended Mode)

In this mode (Pin 4  $\geq$  2.0 V) V<sub>CC</sub> requires +5.0 V, and V<sub>EE</sub> requires -5.0 V, both  $\pm$ 5.0%. Pins 2, 3, 6, and 7 are inputs for the four drivers, and Pins 15, 14, 11, and 10 (respectively) are the outputs. The four drivers are independent of each other, and each output will be at a positive or a negative voltage depending on its input state, the load current, and the supply voltage. Figures 10 & 11 indicate the high and low output voltages for V<sub>CC</sub> = 5.0 V, and V<sub>EE</sub> = -5.0 V. The graph of Figure 10 will vary directly with V<sub>CC</sub>, and the graph of

Figure 11 will vary directly with VEE. A "high" output can only source current, while a "low" output can only sink current (except short circuit current – see Figure 14).

The outputs will be in a high impedance mode only if  $V_{CC} \le 1.1$  V. Changing  $V_{EE}$  to 0 V does not set the outputs to a high impedance mode. Leakage current over a common mode range of  $\pm 10$  V is typically less than  $1.0 \mu A$ .

The outputs have short circuit current limiting, typically less than 100 mA over a voltage range of ±6.0 V (see Figure 14). Short circuits should not be allowed to last indefinitely as the IC may be damaged.

Capacitors connected between Pins 9, 12, 13, and 16 and their respective outputs will provide slew rate limiting of the output transition. Figure 16 indicates the required capacitor value to obtain a desired rise or fall time (measured between the 10% and 90% points). The positive and negative transition times will be within  $\approx \pm 5\%$  of each other. Each output may be set to a different slew rate if desired.

#### Inputs

The five inputs determine the state of the outputs in accordance with Table 1. All inputs (regardless of the operating mode) have a nominal threshold of +1.3 V, and their voltage must be kept within a range of 0 V to +15 V for proper operation. If an input is taken more than 0.3 V below ground, excessive currents will flow, and the proper operation of the drivers will be affected. An open pin is equivalent to a logic high, but good design practices dictate that inputs should never be left open. Unused inputs should be connected to ground. The characteristics of the inputs are shown in Figure 9.

#### **Power Supplies**

VCC requires +5.0 V,  $\pm5\%$ , regardless of the mode of operation. The supply current is determined by the IC's internal bias requirements and the total load current. The internally required current is a function of the load current and is shown in Figure 7 for the differential mode.

In the single–ended mode, VEE must be -5.0 V,  $\pm 5\%$  in order to comply with EIA–423–A standards. Figures 12 and 13 indicate the internally required bias currents as a function of total load current (the sum of the four output loads). The discontinuity at 0 load current exists due to a change in bias current when the inputs are switched. The supply currents vary  $\approx \pm 2.0 \text{ mA}$  as VCC and VEE are varied from |4.75 V| to |5.25 V|.

Sequencing of the supplies during power–up/power–down is not required.

Bypass capacitors (0.1  $\mu$ F minimum on each supply pin) are recommended to ensure proper operation. Capacitors reduce noise induced onto the supply lines by the switching action of the drivers, particularly where long P.C. board tracks are involved. Additionally, the capacitors help absorb transients induced onto the drivers' outputs from the external cable (from ESD, motor noise, nearby computers, etc.).

#### **Operating Temperature Range**

The maximum ambient operating temperature, listed as +85°C, is actually a function of the system use (i.e., specifically how many drivers within a package are used) and at what current levels they are operating. The maximum power which may be dissipated within the package is determined by:

$$P_{Dmax} = \frac{T_{Jmax} - T_{A}}{R_{\theta,IA}}$$

where  $R_{\theta}JA$  = package thermal resistance which is typically: 67°C/W for the DIP (PC) package,

120°C/W for the SOIC (D) package,

T<sub>Jmax</sub> = max. allowable junction temperature (150°C)

T<sub>A</sub> = ambient air temperature near the IC package.

#### 1) Differential Mode Power Dissipation

For the differential mode, the power dissipated within the package is calculated from:

$$P_D = [(V_{CC} - V_{OD}) \times I_O]$$

(each driver) +  $(V_{CC} \times I_B)$

where:  $V_{CC}$  = the supply voltage

V<sub>OD</sub> = is taken from Figure 6 for the known value of I<sub>O</sub>

I<sub>B</sub> = the internal bias current (Figure 7)

As indicated in the equation, the first term (in brackets) must be calculated and summed for each of the two drivers, while the last term is common to the entire package. Note that the term ( $V_{CC} - V_{OD}$ ) is constant for a given value of  $I_O$  and does not vary with  $V_{CC}$ . For an application involving the following conditions:

$T_A = +85^{\circ}C$ ,  $I_O = -60$  mA (each driver),  $V_{CC} = 5.25$  V, the suitability of the package types is calculated as follows.

The power dissipated is:

$$P_D = [3.0 \text{ V} \times 60 \text{ mA} \times 2] + (5.25 \text{ V} \times 18 \text{ mA})$$

$$P_D = 454 \text{ mW}$$

The junction temperature calculates to:

T<sub>J</sub> =  $85^{\circ}$ C + (0.454 W ×  $67^{\circ}$ C/W) =  $115^{\circ}$ C for the DIP package,

$T_J = 85^{\circ}C + (0.454 \text{ W} \times 120^{\circ}\text{C/W}) = 139^{\circ}\text{C}$  for the SOIC package.

Since the maximum allowable junction temperature is not exceeded in any of the above cases, either package can be used in this application.

#### 2) Single-Ended Mode Power Dissipation

For the single-ended mode, the power dissipated within the package is calculated from:

$$P_D = (I_{B+} \times V_{CC}) + (I_{B-} \times V_{EE}) + [(I_O \times (V_{CC} - V_{OH})](each driver)]$$

The above equation assumes IO has the same magnitude for both output states, and makes use of the fact that the absolute value of the graphs of Figures 10 and 11 are nearly identical. IB+ and IB- are obtained from the right half of Figures 12 and 13, and ( $V_{CC} - V_{OH}$ ) can be obtained from Figure 10. Note that the term ( $V_{CC} - V_{OH}$ ) is constant for a given value of IO and does not vary with  $V_{CC}$ . For an application involving the following conditions:

$T_A = +85^{\circ}C$ ,  $I_O = -60$  mA (each driver),  $V_{CC} = 5.25$  V,  $V_{EE} = -5.25$  V, the suitability of the package types is calculated as follows.

The power dissipated is:

$$P_D = (24 \text{ mA} \times 5.25 \text{ V}) + (-3.0 \text{ mA} \times -5.25 \text{ V}) + [60 \text{ mA} \times 1.45 \text{ V} \times 4.0]$$

$P_{D} = 490 \, \text{mW}$

The junction temperature calculates to:

$$T_J = 85^{\circ}\text{C} + (0.490 \text{ W} \times 67^{\circ}\text{C/W}) = 118^{\circ}\text{C}$$

for the DIP package,

TJ =

$$85^{\circ}$$

C + (0.490 W × 120°C/W) = 144°C for the SOIC package.

Since the maximum allowable junction temperature is not exceeded in any of the above cases, either package can be used in this application.

#### SYSTEM EXAMPLES

(Pin numbers refer to DIP and SO-16 packages only.)

#### **Differential System**

An example of a typical EIA-422-A system is shown in Figure 17. Although EIA-422-A does not specifically address multiple driver situations, the AM26LS30 can be used in this manner since the outputs can be put into a high impedance mode. It is, however, the system designer's responsibility to ensure the Enable pins are properly controlled so as to prevent two drivers on the same cable from being "on" at the same time.

The limit on the number of receivers and drivers which may be connected on one system is determined by the input current of each receiver, the maximum leakage current of each "off" driver, and the DC current through each terminating resistor. The sum of these currents must not exceed the capability of the "on" driver (≈60 mA). If the cable is of any significant length, with receivers at various points along its length, the common mode voltage may vary along its length, and this parameter must be considered when calculating the maximum driver current.

The cable requirements are defined not only by the AC characteristics and the data rate, but also by the DC resistance. The maximum resistance must be such that the minimum voltage across any receiver inputs is never less than 200 mV.

The ground terminals of each driver and receiver in Figure 17 must be connected together by a dedicated wire (or the shield) in the cable to provide a common reference. Chassis grounds or power line grounds should not be relied on for this common connection as they may generate significant common mode differences. Additionally, they usually do not provide a sufficiently low impedance at the frequencies of interest.

#### Single-Ended System

An example of a typical EIA–423–A system is shown in Figure 18. Multiple drivers on a single data line are not possible since the drivers cannot be put into a high impedance mode. Although each driver is shown connected to a single receiver, multiple receivers can be driven from a single driver as long as the total load current of the receivers and the terminating resistor does not exceed the capability of the driver ( $\approx$ 60 mA). If the cable is of any significant length, with receivers at various points along its length, the common mode voltage may vary along its length, and this parameter must be considered when calculating the maximum driver current.

The cable requirements are defined not only by the AC characteristics and the data rate, but also by the DC resistance. The maximum resistance must be such that the

minimum voltage across any receiver inputs is never less than 200 mV.

The ground terminals of each driver and receiver in Figure 18 must be connected together by a dedicated wire (or the shield) in the cable so as to provide a common reference. Chassis grounds or power line grounds should not be relied on for this common connection as they may generate significant common mode differences. Additionally, they usually do not provide a sufficiently low impedance at the frequencies of interest.

#### **Additional Modes of Operation**

If compliance with EIA–422–A or EIA–423–A Standard is not required in a particular application, the AM26LS30 can be operated in two other modes.

- 1) The device may be operated in the differential mode (Pin 4=0) with VEE connected to any voltage between ground and -5.25 V. Outputs in the low state will be referenced to VEE, resulting in a differential output voltage greater than that shown in Figure 6. The Enable pins will operate the same as previously described.

- 2) The device may be operated in the single-ended mode (Pin 4 = 1) with VEE connected to any voltage between ground and -5.25 V. Outputs in the high state will be at a voltage as shown in Figure 10, while outputs in a low state will be referenced to VEE.

#### **Termination Resistors**

Transmission line theory states that, in order to preserve the shape and integrity of a waveform traveling along a cable, the cable must be terminated in an impedance equal to its characteristic impedance. In a system such as that depicted in Figure 17, in which data can travel in both directions, both physical ends of the cable must be terminated. Stubs leading to each receiver and driver should be as short as possible.

In a system such as that depicted in Figure 18, in which data normally travels in one direction only, a terminator is theoretically required only at the receiving end of the cable. However, if the cable is in a location where noise spikes of several volts can be induced onto it, then a terminator (preferably a series resistor) should be placed at the driver end to prevent damage to the driver.

Leaving off the terminations will generally result in reflections which can have amplitudes of several volts above VCC or several volts below ground or VEE. These overshoots/undershoots can disrupt the driver and/or receiver, create false data, and in some cases, damage components on the bus.

Figure 17. EIA-422-A Example

NOTES: 1. Terminating resistors R<sub>T</sub> should be located at the physical ends of the cable.

2. Stubs should be as short as possible.

3. Receivers = AM26LS32, MC3486, SN75173 or SN75175.

4. Circuit grounds must be connected together through a dedicated wire.

Figure 18. EIA-423-A Example AM26LS30 AM26LS32, MC3486, SN75173, or SN75175

#### **OUTLINE DIMENSIONS**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

|     | INC                 | HES   | MILLIM   | IETERS |  |  |  |  |

|-----|---------------------|-------|----------|--------|--|--|--|--|

| DIM | MIN                 | MAX   | MIN      | MAX    |  |  |  |  |

| Α   | 0.740 0.770         |       | 18.80    | 19.55  |  |  |  |  |

| В   | 0.250 0.270         |       | 6.35     | 6.85   |  |  |  |  |

| С   | 0.145               | 0.175 | 3.69     | 4.44   |  |  |  |  |

| D   | 0.015               | 0.021 | 0.39     | 0.53   |  |  |  |  |

| F   | 0.040               | 0.70  | 1.02     | 1.77   |  |  |  |  |

| G   | 0.100               | BSC   | 2.54 BSC |        |  |  |  |  |

| Н   | 0.050               | BSC   | 1.27     | BSC    |  |  |  |  |

| J   | 0.008               | 0.015 | 0.21     | 0.38   |  |  |  |  |

| K   | <b>(</b> 0.110 0.13 |       | 2.80     | 3.30   |  |  |  |  |

| L   | 0.295               | 0.305 | 7.50     | 7.74   |  |  |  |  |

| M   | 0°                  | 10°   | 0°       | 10 °   |  |  |  |  |

| S   | 0.020               | 0.040 | 0.51     | 1.01   |  |  |  |  |

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC   | HES   |  |

|-----|--------|--------|-------|-------|--|

| DIM | MIN    | MAX    | MIN   | MAX   |  |

| Α   | 9.80   | 10.00  | 0.386 | 0.393 |  |

| В   | 3.80   | 4.00   | 0.150 | 0.157 |  |

| С   | 1.35   | 1.75   | 0.054 | 0.068 |  |

| D   | 0.35   | 0.49   | 0.014 | 0.019 |  |

| F   | 0.40   | 1.25   | 0.016 | 0.049 |  |

| G   | 1.27   | BSC    | 0.050 | ) BSC |  |

| J   | 0.19   | 0.25   | 0.008 | 0.009 |  |

| K   | 0.10   | 0.25   | 0.004 | 0.009 |  |

| M   | 0°     | 7°     | 0°    | 7°    |  |

| Р   | 5.80   | 6.20   | 0.229 | 0.244 |  |

| R   | 0.25   | 0.50   | 0.010 | 0.019 |  |

#### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE (602) 244–6609 INTERNET: http://Design\_NET.com

$\Diamond$

**JAPAN**: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

**HONG KONG**: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

AM26LS30/D