MQ342-01

**EPSON**

Application Manual

# Real Time Clock Module RTC-4553AC

## **SEIKO EPSON CORPORATION**

In pursuit of "Saving" Technology, Epson electronic device. Our Lineup of semiconductors, Liquid crystal displays and quartz devices assists in creating the products of our customers' dreams. Epson IS energy savings.

## NOTICE

- No part of this material may be reproduced or duplicated in any form or any means without the written permission of Seiko Epson.

- Seiko Epson reserves the right to make changes to this material without notice.

- Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products.

- Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party.

- This material of portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of international Trade and industry or other approval from another government agency.

## CONTETS

| 1. Overview1                                                                                                                                                                            | l      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2. Block Diagram1                                                                                                                                                                       | I      |

| 3. Terminal description       2         3.1. Terminal connections       2         3.2. Terminal functions       2                                                                       | 2      |

| 4. Absolute maximum ratings                                                                                                                                                             | 3      |

| 5. Recommended operating conditions                                                                                                                                                     | 3      |

| 6. Frequency characteristics                                                                                                                                                            | 3      |

| 7. Electrical characteristics       4         7.1. DC, AC Characteristics       4         7.1.1. VDD = 5 V.       4         7.1.2. VDD = 3 V.       5         7.2. Timing Chart       6 | 4<br>5 |

| 8. How to use                                                                                                                                                                           |        |

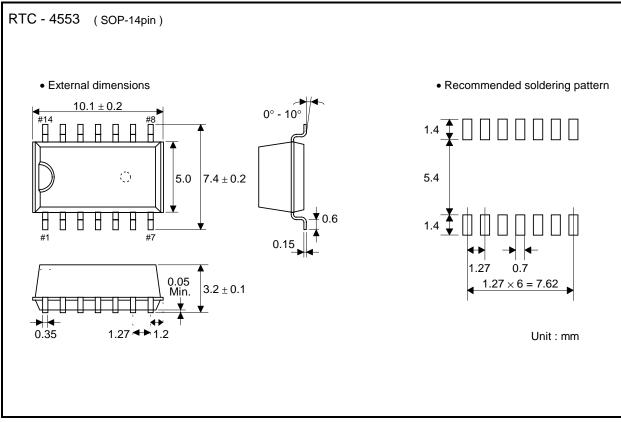

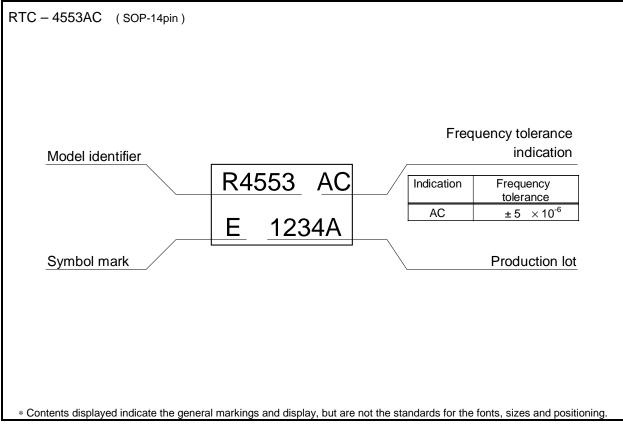

| 9. External dimensions / Marking layout                                                                                                                                                 | 1      |

| 10. Reference Data22                                                                                                                                                                    | 2      |

| 11. Application notes       23         11.1. Notes on handling       23         11.2. Notes on packaging       23                                                                       | 3      |

## Real-Time Clock Module

## RTC – 4553AC

- Designed for E-mater

- Built-in 32.768 kHz quartz crystal allows adjustment- free operation and assures high accuracy

- Integrated clock (hours, minutes, seconds) and calendar (year, month, day, day of the week) counter

- Automatic leap year compensation until 2099

- Selectable 24-hour/12-hour display mode (with AM/PM indication)

- Clock data modification using increment method

- Clock data serial output in BCD format

- Software controlled 30 second adjustment

- Selectable 1/10 Hz or 1024 Hz timing pulse output

- Built-in SRAM ( $30 \times 4$  bit)

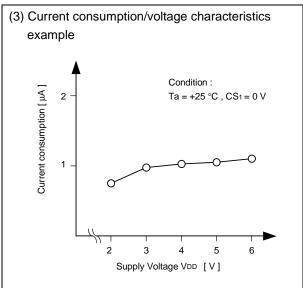

- Constant voltage drive realizes low power consumption (1 μA Typ.) and minimizes voltage-induced frequency fluctuations

- Supports low-voltage operation (3 V)

### 1. Overview

The RTC-4553 is a very compact real-time clock module with permanent calendar and serial data input/output. The module is designed for E-mater; time accuracy is within  $\pm 5 \times 10^{-6}$  ( $\pm 0.432$  sec./day). It incorporates a heat-resistant 32.768 kHz quartz oscillator. The space saving package allows high-density mounting and facilitates automated production.

Besides the clock and calendar functions (comprising all items from years to seconds), the RTC-4553 incorporates also a  $30 \times 4$  bit SRAM and offers other useful features.

The use of a CMOS IC makes possible low-voltage, low-power operation, to ensure proper timekeeping also when powered from a backup battery.

## 2. Block Diagram

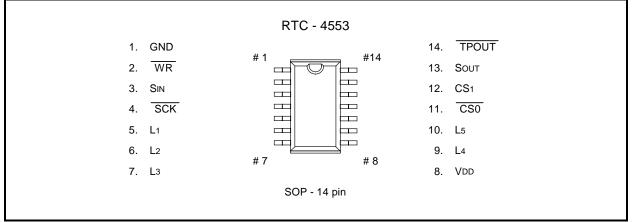

## 3. Terminal description

## 3.1. Terminal connections

#### 3.2. Terminal functions

| Signal designation | Pin No. | Input    | Function                                                                             |

|--------------------|---------|----------|--------------------------------------------------------------------------------------|

|                    |         | / Output |                                                                                      |

| GND                | 1       | _        | Power supply negative pin. Connect to ground.                                        |

|                    |         |          | Address and data are written at WR = "L". Counter data (second digit to              |

| WR                 | 2       | 1        | year digit) are written using the incrementing method.                               |

| (WRITE enable)     | Z       | I        | Data at the specified address are read at WR = "H". While the address is             |

|                    |         |          | being set at SIN, the data at SOUT are for the previously specified address.         |

| Sin                | 3       | 1        | Serial address and data I/O pin. Serves for address and control register             |

| (Serial input)     | 3       | 1        | writing for the various counters, and for RAM address and data writing.              |

| SCK                |         |          | Serial I/O sync signal input pin. Input a sync signal to this pin to allow address   |

| ( Serial clock )   | 4       | I        | and data read/write synchronized to this signal.                                     |

| ( Senar Clock )    |         |          | One cycle comprises 8 clocks (4 address clocks + 4 data clocks)                      |

| L1–L3              | 5–7     |          | Test pins reserved for use by Epson. Be sure to leave these pins                     |

| L4 , L5            | 9, 10   |          | unconnected.                                                                         |

|                    |         |          | Power supply pin. Connect to a power source. For normal operation and bus            |

| Vdd                | 8       | _        | access, supply 5 V $\pm$ 10% or 3 V $\pm$ 10%. For backup battery operation, provide |

| VDD                | 0       |          | a voltage of 2 V or higher.                                                          |

|                    |         |          | See Note 1.                                                                          |

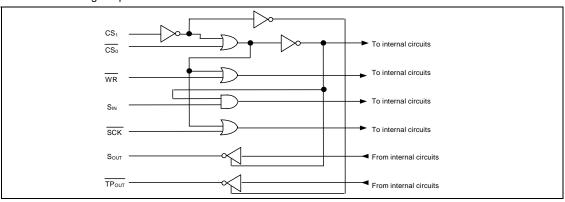

| CS0                |         |          | This pin serves to select the RTC. While CS0 is "L", the microprocessor              |

| (Chip select 0)    | 11      | I        | can perform register access. While $\overline{\text{CSO}}$ is "H", SOUT is in the    |

| ( Chip select 0 )  |         |          | high-impedance state.                                                                |

| CS1                |         |          | Connect this pin to the power down detection circuit. If no power down               |

| (Chip select 1)    | 12      | I        | detection circuit is used, fix the pin at "H" (VDD). When CS1 is "L", SOUT and       |

| ( Chip select 1 )  |         |          | TPOUT are in the high-impedance state, regardless of CS0.                            |

| SOUT               | 13      | ο        | Serial address and data output pin. Serves for address and control register          |

| (Serial output)    | 15      | 0        | readout of the various counters, and for RAM address and data readout.               |

| ΤΡουτ              |         |          | Output pin for 1024 Hz or 1/10 Hz timing pulse, based on internal reference          |

| (Timing pulse      | 14      | 0        | clock. For clock accuracy checking, use 1/10 Hz.                                     |

| output )           |         |          | For 1024 Hz, the duty cycle changes once every 10 seconds.                           |

Note1 At initial power-on or voltage restoration from an intermediate potential outside of the range where operation is assured (0.3 V to 1.9 V), the power-on reset circuit may not operate normally, leading to possible malfunction. (See section " 8.3.9. Power-On Reset ".)

Note2 Be sure to connect a bypass capacitor of 0.1  $\mu$ F or more directly between VDD and GND.

## 4. Absolute maximum ratings

| 4. Absolute maxin    | num rati | ngs                                 |                                      |                                       | GND=0 V     |

|----------------------|----------|-------------------------------------|--------------------------------------|---------------------------------------|-------------|

| Item                 | Symbol   | Condition (pin)                     | Max.                                 | Unit                                  |             |

| Power supply voltage | Vdd      | Vdd-GND                             | -0.3                                 | +6.0                                  |             |

| Input voltage        | Vin      | SIN, SCK, WR, CS0, CS1              | -0.3                                 | VDD+0.3                               | V           |

| Output voltage       | Vout     | SOUT, TPOUT                         | -0.3                                 | Vdd+0.3                               |             |

| Storage temperature  | Tstg     | Stored bare product after unpacking | -55                                  | +125                                  | °C          |

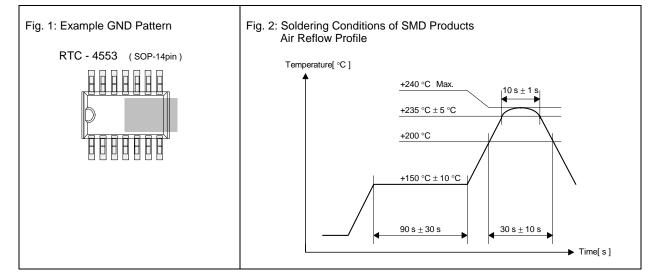

| Soldering conditions | TSOL     | —                                   | Twice at under +<br>under +230 °C wi | 260 °C within 10 s<br>ithin 3 minutes | seconds, or |

## 5. Recommended operating conditions

| 5. Recommended        | l operati | ng conditions   |      |      |      | GND=0 V |

|-----------------------|-----------|-----------------|------|------|------|---------|

| Item                  | Symbol    | Condition       | Min. | Тур. | Max. | Unit    |

| Power supply voltage  | Vdd       | Vdd-GND         | 2.7  | 5.0  | 5.5  | V       |

| Operation temperature | TOPR      | No condensation | -30  | _    | +70  | °C      |

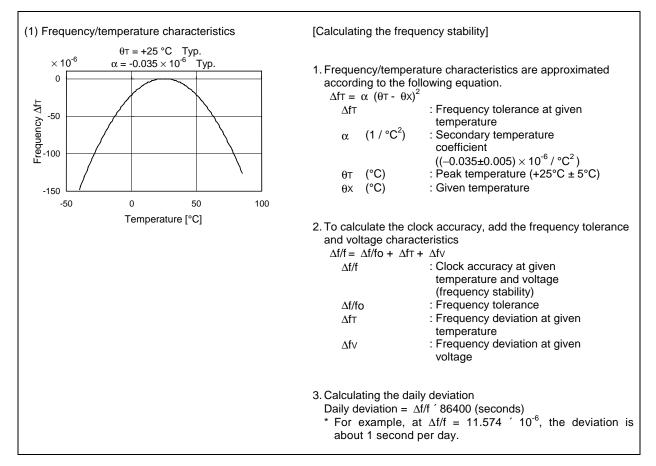

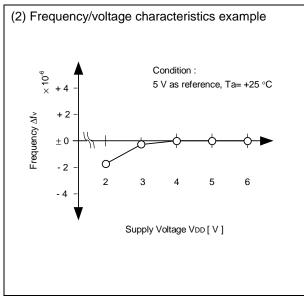

## 6. Frequency characteristics

| 6. Frequency cha                      | racterist | ICS                                                   |            |             | GND=0 V                          |

|---------------------------------------|-----------|-------------------------------------------------------|------------|-------------|----------------------------------|

| Item                                  | Symbol    | Condition                                             |            | Rating      | Unit                             |

| Frequency precision                   | Δ f / fo  | Ta = +25 °C                                           | AC         | ± 5         | × 10 <sup>-6</sup>               |

| Frequency precision                   | Δ1710     | VDD = 5.0 V                                           | AC         | ± 0.432     | sec. / day                       |

| Frequency/temperature characteristics | tOP       | Ta = -10 °C to +7<br>VDD = 5 V (Referenced a          | ,          | +10<br>–120 | × 10 <sup>-6</sup>               |

| Frequency/voltage characteristics     | f / V     | Ta = Fixed, VDD = 2 V to 5.5 V<br>(Referenced at 5 V) |            | ± 5         | × 10 <sup>-6</sup>               |

| Aging                                 | fa        | Ta = +25 °C, VDD = 5 V                                | First year | ± 5         | $\times$ 10 <sup>-6</sup> / year |

Note

(1) Frequency tolerance rating applies to VDD = 5.0 V. (At VDD = 3 V, voltage characteristics must be taken into consideration.)

(2) Frequency tolerance rating applies at the time of shipment.

(3) Design the peripheral circuitry so that power start-up time (tR) is  $1.0 \,\mu\text{s/V} \le \text{tR} \le 1.6 \,\text{ms/V}$ .

## 7. Electrical characteristics

#### 7.1. DC, AC Characteristics

7.1.1. VDD = 5 V

#### (1) DC Characteristics

| (1) DC Characteris          | tics                  |                  |              | ( GND=0 V    | , Ta = −30 °C | C ~ +70 °C) |

|-----------------------------|-----------------------|------------------|--------------|--------------|---------------|-------------|

| ltem                        | Symbol                | Condition        | VD           | D = 5 V ± 10 | ) %           | Unit        |

| Item                        | Gymbol                | Condition        | Min.         | Тур.         | Typ. Max.     |             |

| Data retention<br>voltage   | Vdh                   | _                | 2.0          | —            | 5.5           | V           |

|                             | IDD1                  | SCK = 500 kHz    |              |              | 100           |             |

| Current                     | (normal operation)    | CS0 = L, CS1 = H |              |              | 100           |             |

| consumption                 | IDD2                  | SCK = 0 Hz       |              |              |               | μA          |

|                             | (backup<br>operation) | CS0 = H, CS1 = L | _            | 1.0          | 3.0           |             |

| Output voltage              | Vон                   | Юн = -400 μА     | Vdd -<br>0.4 | —            | —             | V           |

|                             | Vol                   | IOL = 1.6 mA     | —            | —            | 0.4           |             |

| Output leak                 | ЮZH                   | VOUT = 5.5 V     | -2.0         | —            | 2.0           |             |

| current                     | Iozl                  | Vout = 0 V       | -2.0         | —            | 2.0           | μA          |

| Input voltage               | Vih                   | —                | 4/5 Vdd      | —            | —             | V           |

| input voltage               | VIL                   | —                | —            | _            | 1/5 Vdd       | v           |

| Input current               | Ін                    | VIN = 5.5 V      | -2.0         | _            | 2.0           |             |

|                             | lı∟                   | VIN = 0 V        | -2.0         | —            | 2.0           | μA          |

| Oscillation<br>startup time | Ts                    | Ta = +25 °C      | _            |              | 3.0           | S           |

#### (2) AC Characteristics ( GND=0 V , Ta = $-30 \degree C \sim +70 \degree C$ ) $VDD = 5 V \pm 10 \%$ Item Condition Unit Symbol Min. Тур. Max. SCK frequency **f**CLK \_ 500 kHz \_\_\_\_ \_\_\_\_ SCK "L" time **t**WCKL \_ 1.0 \_ \_ SCK "H" time 1.0 twcкн \_\_\_\_ SCK pause time 1.0 tPS \_\_\_\_ \_\_\_\_ CS0 setup time tscs 0 \_\_\_\_ — \_\_\_\_ μs CS0 hold time 0.5 tHCS \_\_\_\_ \_\_\_\_ \_\_\_\_ SIN data setup time 0.2 tsD \_\_\_\_ \_\_\_\_ SIN data hold time tHD — 0.2 — — WR setup time tswr 1.0 \_\_\_\_ \_\_\_\_ WR hold time thwr 0.5 \_ \_\_\_\_ \_\_\_\_ SOUT delay time tDS0 CL=100 pF 150 500 \_ Time lag between CS0 , CS1 enable tDSZ1 CL=100 pF 100 \_\_\_\_ \_\_\_\_\_ and SOUT output Time lag between CS0 disable and tDSZ2 CL=100 pF 100 \_ \_\_\_\_ SOU⊤ high Z ns Time lag between CS1 enable and CL=100 pF tDPZ1 100 \_\_\_\_ \_\_\_\_ TPO∪⊤ output Time lag between CS1 disable and tDPZ2 CL=100 pF 100 \_\_\_\_\_ \_\_\_\_ TPOUT high Z

#### 7.1.2. VDD = 3 V

## (1) DC Characteristic

| (1) DC Characteris        | tics                          |        |                              |         | ( GND=0 V        | , Ta = −30 °C | C ~ +70 °C) |

|---------------------------|-------------------------------|--------|------------------------------|---------|------------------|---------------|-------------|

| Item                      | Symbol                        |        | Condition                    |         | D = 3 V ±10      |               | Unit        |

|                           | Gymbol                        |        | Condition                    | Min.    | Тур.             | Max.          | Onic        |

| Data retention<br>voltage | Vdh                           |        | _                            | 2.0     | _                | 3.3           | V           |

| Current                   | IDD1<br>(normal operation)    |        | CK = 300 kHz<br>= L, CS1 = H | _       | _                | 100           | μA          |

| consumption               | IDD2<br>(backup<br>operation) |        | SCK = 0 Hz<br>= H, CS1 = L   | _       | 1.0              | 3.0           | μς          |

| Output voltage            | Vон                           |        | н = -400 μА                  | VDD-0.4 |                  | _             | V           |

| Output voltage            | Vol                           |        | OL = 1.2 mA                  |         |                  | 0.4           | v           |

| Output leak               | Іодн                          | `      | /out = 3.3 V                 | -2.0    |                  | 2.0           | μA          |

| current                   | Iozl                          |        | Vout = 0 V                   | -2.0    | _                | 2.0           | μΛ          |

| Input voltage             | Vih                           |        | —                            | 4/5 VDD | _                |               | V           |

|                           | VIL                           |        |                              | _       |                  | 1/5 VDD       |             |

| Input current             | Ін                            |        | VIN = 3.3 V                  | -2.0    | _                | 2.0           | μA          |

| Oscillation               | lı∟                           |        | VIN = 0 V                    | -2.0    | _                | 2.0           |             |

| startup time              | Ts                            |        | Ta = +25 °C                  | —       | —                | 3.0           | S           |

| (2) AC Characterist       | tics                          |        |                              |         | ( GND=0 V        | , Ta = −30 °C | C ~ +70 °C) |

| 1+.                       | em                            | Symbol | Condition                    | VD      | $D = 3 V \pm 10$ | %             | Unit        |

| 10                        | em                            | Symbol | Condition                    | Min.    | Тур.             | Max.          | Unit        |

| SCK frequency             |                               | fCLK   | _                            | _       | _                | 300           | kHz         |

| SCK "L" time              |                               | twckl  | _                            | 1.5     | _                |               |             |

| SCK "H" time              | SCK "H" time                  |        | _                            | 1.5     | _                |               |             |

| SCK pause time            | SCK pause time                |        | _                            | 1.5     | _                |               |             |

| CS0 setup time            |                               | tscs   | _                            | 0       | —                |               |             |

|                                                                       | CONCE |           | 1.0 |     |     |    |

|-----------------------------------------------------------------------|-------|-----------|-----|-----|-----|----|

| SCK "H" time                                                          | twcкн | —         | 1.5 | -   | —   |    |

| SCK pause time                                                        | tPS   | _         | 1.5 | _   | —   |    |

| CS0 setup time                                                        | tscs  | _         | 0   | _   | —   |    |

| CS0 hold time                                                         | tHCS  | _         | 1.0 | _   | —   | μs |

| SIN data setup time                                                   | tSD   | _         | 0.2 | _   | _   |    |

| SIN data hold time                                                    | tHD   |           | 0.2 |     |     |    |

| WR setup time                                                         | tswr  | _         | 1.5 | _   | —   |    |

| WR hold time                                                          | thwr  | _         | 1.0 | _   | —   |    |

| Sou⊤ delay time                                                       | tDSO  | CL=100 pF | _   | 300 | 500 |    |

| Time lag between $\overline{\text{CS0}}$ , CS1 enable and SOUT output | tDSZ1 | CL=100 pF | —   |     | 200 |    |

| Time lag between CS0 disable and Sout high Z                          | tDSZ2 | CL=100 pF | —   | _   | 200 | ns |

| Time lag between CS1 enable and TPOUT output                          | tDPZ1 | CL=100 pF | _   | _   | 200 |    |

| Time lag between CS1 disable and TPout high Z                         | tDPZ2 | CL=100 pF | —   | _   | 200 |    |

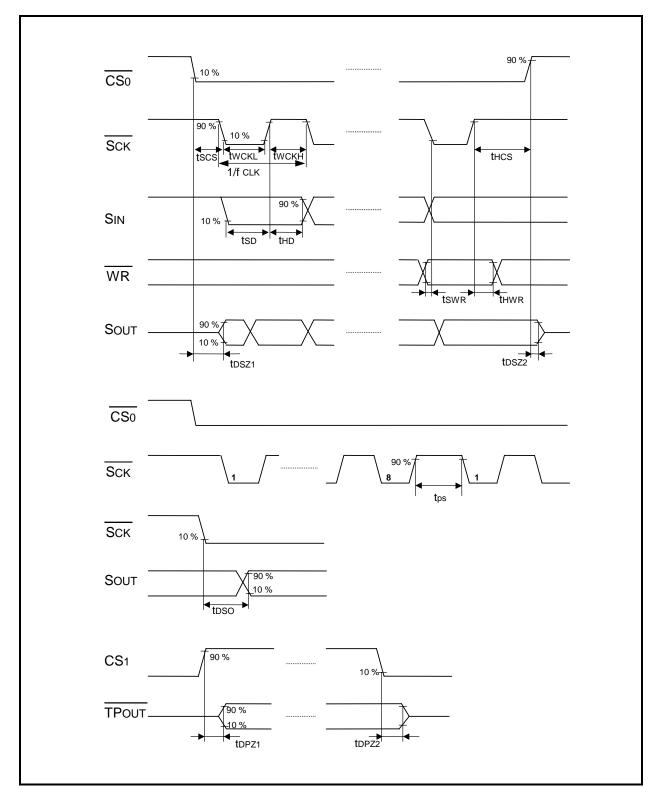

## 7.2. Timing Chart

## 8. How to use

#### 8.1. Registers

8.1.1. Register Table

|   |    |        |    |    |             |                 |                                                                       |                        |          |                                  | MO       | DE 2 (   | User             | RAM              | l regist          | ter 2)             |                   |

|---|----|--------|----|----|-------------|-----------------|-----------------------------------------------------------------------|------------------------|----------|----------------------------------|----------|----------|------------------|------------------|-------------------|--------------------|-------------------|

|   |    |        |    |    |             |                 |                                                                       |                        |          | A                                | ddres    | SS       |                  |                  | User F            | RAM reg            | ister             |

|   |    |        |    |    |             |                 |                                                                       |                        |          | A3                               | A2       | A1       | A0               | D3               | D2                | D1                 | D0                |

|   |    |        |    |    |             |                 |                                                                       | (                      | 0        | 0                                | 0        | 0        | 0                | RA <sub>6</sub>  | 3 RA <sub>6</sub> | 2 RA <sub>61</sub> | RA <sub>60</sub>  |

|   |    |        |    |    |             |                 |                                                                       |                        | MO       | DE                               | 1 (Us    | ser R/   | AM re            | giste            | r 1)              |                    | RA <sub>64</sub>  |

|   |    |        |    |    |             |                 |                                                                       | A                      | ddre     |                                  | . (      |          |                  | -                | M reg             | ister              | RA <sub>68</sub>  |

|   |    |        |    |    |             |                 |                                                                       | A3                     | A2       | A                                | 1 A      | 0.0      | 03               | D2               | D1                | D0                 | RA <sub>72</sub>  |

|   |    |        |    |    |             |                 | 0                                                                     | 0                      | 0        |                                  |          |          |                  | RA2              | RA1               | RA <sub>0</sub>    | RA <sub>76</sub>  |

|   |    |        |    |    |             |                 | MODE 0                                                                | 1                      |          | _                                |          |          |                  |                  |                   | RA₄                | RA <sub>80</sub>  |

|   | A  | ddress | ;  |    | Register    |                 |                                                                       | Co                     | ounte    | r cont                           | trol reg | ister    |                  |                  |                   | RA <sub>8</sub>    | RA <sub>84</sub>  |

|   | A3 | A2     | A1 | A0 | designation | D3              | D2                                                                    | D1                     |          | D0                               |          |          | egister          | name             |                   | RA <sub>12</sub>   | RA <sub>88</sub>  |

| 0 | 0  | 0      | 0  | 0  | S1          | S <sub>8</sub>  | S4                                                                    | S <sub>2</sub>         |          | S <sub>1</sub>                   |          | 1-sec    | ond di           | git cour         | nter              | RA <sub>16</sub>   | RA <sub>92</sub>  |

| 1 | 0  | 0      | 0  | 1  | S10         | 0               | 0 S <sub>40</sub> S <sub>20</sub> S <sub>10</sub> 10-second digit cou |                        |          |                                  | igit cou | nter     | RA <sub>20</sub> | RA <sub>96</sub> |                   |                    |                   |

| 2 | 0  | 0      | 1  | 0  | MI1         | mi <sub>8</sub> | mi4                                                                   | mi <sub>2</sub>        |          | mi₁                              |          | 1-mir    | nute dig         | git cour         | nter              | RA <sub>24</sub>   | RA <sub>100</sub> |

| 3 | 0  | 0      | 1  | 1  | MI10        | 0               | mi <sub>40</sub>                                                      | mi <sub>20</sub>       |          | mi <sub>10</sub>                 | )        |          |                  | git cou          |                   | RA <sub>28</sub>   | RA <sub>104</sub> |

| 4 | 0  | 1      | 0  | 0  | H1          | h <sub>8</sub>  | h4                                                                    | h <sub>2</sub>         |          | h <sub>1</sub>                   |          |          | 0                | t count          |                   | RA <sub>32</sub>   | RA <sub>108</sub> |

| 5 | 0  | 1      | 0  | 1  | H10         |                 | 0                                                                     | h <sub>20</sub>        |          | h <sub>10</sub>                  |          | 10-h     | our dig          | it coun          | ter               | RA <sub>36</sub>   | RA <sub>112</sub> |

| 6 | 0  | 1      | 1  | 0  | W           | 0               |                                                                       |                        |          | W1                               |          | ov of th |                  | diait a          | ounter            | RA <sub>40</sub>   | RA <sub>116</sub> |

| 7 | 0  | 1      | 1  | 1  | D1          | d <sub>8</sub>  | W <sub>4</sub><br>d <sub>4</sub>                                      | W <sub>2</sub>         |          | w <sub>1</sub><br>d <sub>1</sub> |          |          |                  | counte           |                   | RA <sub>44</sub>   | MS0               |

| 8 | 1  | 0      | 0  | 0  | D10         | 0               | 0                                                                     | d <sub>20</sub>        |          | d <sub>10</sub>                  |          |          |                  | t count          |                   | RA <sub>48</sub>   |                   |

| 9 | 1  | 0      | 0  | 1  | MO1         | mo <sub>8</sub> | mo₄                                                                   | mo <sub>2</sub>        |          | mo <sub>1</sub>                  |          |          |                  | it coun          |                   | RA <sub>52</sub>   |                   |

| A | 1  | 0      | 1  | 0  | MO10        | 0               | 0                                                                     | 0                      |          | mo <sub>10</sub>                 |          |          |                  | git cour         |                   | RA <sub>56</sub>   |                   |

| В | 1  | 0      | 1  | 1  | Y1          | <u>У</u> 8      | У4                                                                    | y <sub>2</sub>         |          | y1                               | ·        |          |                  | t count          |                   | MS0                |                   |

| С | 1  | 1      | 0  | 0  | Y10         | <b>y</b> 80     | y40                                                                   | <b>y</b> <sub>20</sub> |          | <b>y</b> 10                      |          | 10-y     | ear dig          | it coun          | ter               |                    |                   |

| D | 1  | 1      | 0  | 1  | CNT 1       | TPS             | 30ADJ                                                                 | CNT                    | <b>۲</b> | 24/ 12                           | 2        | Co       | ontrol r         | egister          | 1                 | ]                  |                   |

| Е | 1  | 1      | 1  | 0  | CNT 2       | BUSY            | PONC                                                                  |                        |          | *                                |          | Co       | ontrol r         | egister          | 2                 | 1                  |                   |

| F | 1  | 1      | 1  | 1  | CNT 3       | SYSR            | TEST                                                                  | MS1                    |          | MSC                              | )        | Co       | ontrol r         | egister          | 3                 | ]                  |                   |

\* In positive logic, "H" on the data bus corresponds to "1" in the register. "ADDRESS\_F" of MODE 1 and MODE 2 is the same as "ADDRESS\_F" of MODE 0.

Notes

(1) Do not set invalid (out of range) data for the time and calendar. Otherwise counting errors may occur.

(2) At power-on (before initialization), the data for each bit are cleared. Write the registers to set the values.

(3) Always set the D0 bit ( \* bit) of the control register 2 to "0".

(4) When reading the D1 bit (— bit) of the control register 2, data of this bit are undefined.

(5) Always set the D3 bit (TEST bit) of the control register 3 to "0".

## 8.1.2. Register Bit Functions

| Bit name                        |                                                                                         |                                                   |           | F                     | unctio    | n          |          |           |           |                |  |

|---------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------|-----------|-----------------------|-----------|------------|----------|-----------|-----------|----------------|--|

| Bit marked "0"                  | Unused bit that cannot be written. Always read as "0".                                  |                                                   |           |                       |           |            |          |           |           |                |  |

| Second to year digit            | BCD code. Data                                                                          |                                                   |           |                       |           |            |          |           |           |                |  |

| PM/ AM                          | "1" indicates PM                                                                        |                                                   |           |                       |           |            | read al  | so whe    | n 24-hc   | our format is  |  |

|                                 | selected (24/12=                                                                        |                                                   |           | 11:59, F              | PM: 12:   | 00 to 23   | 8:59)    |           |           |                |  |

|                                 | To be coded as                                                                          | 7-base cou                                        | inter.    |                       |           |            |          |           |           |                |  |

| Day of the week digit           | Example                                                                                 |                                                   |           |                       |           |            |          |           | -         |                |  |

| Day of the week digit           |                                                                                         | Data 0 1 2 3 4 5 6                                |           |                       |           |            |          |           |           |                |  |

|                                 | Coded day of                                                                            | the week                                          | Sun.      | Mon.                  | Tue.      | Wed.       | Thu.     | Fri.      | Sat.      |                |  |

| Year digit                      | Automatic leap y                                                                        | /ear compe                                        | ensatior  | n up to 2             | 2099      |            |          |           |           |                |  |

| User RAM area                   | 30 × 4 bit SRAM                                                                         |                                                   |           |                       |           |            |          |           |           |                |  |

|                                 | Bit for selecting                                                                       | reference s                                       | signal o  | utput                 |           | TPSI       | oit      | Frequer   | ncy (cycl | e time)        |  |

| TPS                             | waveform.                                                                               |                                                   |           |                       |           | 0          |          | )24 Hz (9 |           |                |  |

| (Timing pulse selection)        | Note 1/10 Hz i                                                                          | s not outp                                        | out for   | 10 sec                | onds      | 1          |          | 10 Hz (1  |           | ,              |  |

| ( ST ,                          | after powe                                                                              |                                                   |           |                       |           | ļ          |          | - (       | /         | J              |  |

|                                 | "L").                                                                                   |                                                   |           |                       |           |            |          |           |           |                |  |

| 30ADJ                           | Setting this bit to                                                                     |                                                   |           |                       |           |            |          |           |           |                |  |

| (30 seconds adjustment)<br>CNTR | The bit automati                                                                        |                                                   |           |                       |           |            |          | pleted (  | after 76  | 5.3 μs).       |  |

| (Counter reset)                 | Setting this bit to                                                                     | ) i resets                                        | the un    | le and c              | alenua    | rcounte    | 15.      |           |           |                |  |

| · · · · · ·                     | 24-hour or 12-ho                                                                        | our format                                        | selectio  | n bit. W              | hen se    | t to "1".  | 24-hou   | ır forma  | t is use  | d. When set    |  |

| 24/ 12                          | to "0", 12-hour fo                                                                      |                                                   |           |                       |           | ,          |          |           |           |                |  |

|                                 | Used when reading/writing time and calendar counter data. Set to "1" when carry occurs. |                                                   |           |                       |           |            |          |           |           |                |  |

| _                               | BUSY bit Mode Meaning                                                                   |                                                   |           |                       |           |            |          |           |           |                |  |

| Busy                            | 0 No carry Time/calendar counter read/write possible                                    |                                                   |           |                       |           |            |          |           |           |                |  |

|                                 |                                                                                         | arry Tin                                          | ne/caler  | idar cou              | nter rea  | d/write p  | rohibite | ed        |           |                |  |

|                                 | At power-on, th                                                                         | e power-or                                        | n-clear   | function              | autom     | natically  | sets th  | his bit t | o "1". T  | his has the    |  |

|                                 | same effect as c                                                                        | 1                                                 | ation.    |                       |           |            |          |           |           |                |  |

|                                 | Register                                                                                |                                                   |           | l manth (             | Data      | M 12-hou   |          | -         |           |                |  |

| PONC                            | Time/calendar cou                                                                       |                                                   |           |                       |           | of the we  |          |           |           |                |  |

| (Power-on-clear detection)      | Control registers                                                                       |                                                   |           | NC = "1")             | ia, o aay | 01 110 110 | 0.11     | 1         |           |                |  |

|                                 | User RAM area                                                                           | U                                                 | ndefined  |                       |           |            |          | 1         |           |                |  |

|                                 | When PONC is                                                                            | "1", data m                                       | ust be    | set. Firs             | st clear  | this bit   | (this ca | an be do  | one by v  | writing "1" to |  |

|                                 | SYSR and then                                                                           | releasing s                                       | ystem i   | eset) ar              | nd then   | set the    |          |           |           |                |  |

| Bit marked " – "                | Cannot be writte                                                                        |                                                   |           |                       |           | fined.     |          |           |           |                |  |

| Bit marked " * "                | Can be written b                                                                        |                                                   |           |                       |           |            |          |           |           |                |  |

|                                 | At SYSR = "1" a<br>transition of CS0                                                    |                                                   |           |                       |           | SYSR bi    | t is res | set to "C | " by ca   | using an up    |  |

|                                 | Register                                                                                |                                                   | vn trans  |                       | Data      |            |          | 1         |           |                |  |

| SYSR                            | Time/calendar cou                                                                       |                                                   | 0-year, 0 | 1-month, (            |           | M 12-hou   | r,       | 1         |           |                |  |

| (System reset)                  |                                                                                         |                                                   |           |                       | nd, 0-day | of the we  | ek       |           |           |                |  |

|                                 | Control registers All "0" (SYSR = "1")                                                  |                                                   |           |                       |           |            |          |           |           |                |  |

|                                 | User RAM area                                                                           | U                                                 | ndefined  |                       |           |            |          | ]         |           |                |  |

| TEST                            | Epson test bit. N                                                                       | lust be set                                       | to "0".   |                       |           |            |          |           |           |                |  |

|                                 | These 2 bits ser                                                                        |                                                   |           | tion.                 |           |            |          |           |           |                |  |

|                                 | MS1 MS0                                                                                 | Mode name                                         |           |                       | Conter    | nt         |          | ٦         |           |                |  |

|                                 | 0 0                                                                                     | Mode 0                                            | Time      |                       |           | and cont   | rol      | 1         |           |                |  |

| MS0, MS1                        |                                                                                         |                                                   | -         | ers 1 - 3<br>calendar | counters  | and cont   | rol      | -         |           |                |  |

| (Mode selection)                | 0 1                                                                                     | Mode 0                                            | regist    | ers 1 - 3             |           |            |          | _         |           |                |  |

|                                 | 1 0                                                                                     | User RAM area (RA0 - RA59) and control register 3 |           |                       |           |            |          |           |           |                |  |

|                                 | 1 1                                                                                     | Mode 2                                            |           | RAM area              |           | RA119) a   | nd       |           |           |                |  |

|                                 |                                                                                         | ļ                                                 | John      |                       | -         |            |          |           |           |                |  |

#### 8.2. Register Description

#### 8.2.1. Time/Calendar Counter Registers

$\cdot$  In normal mode (CNTR = "0"), the counter is incremented by a write operation.

(1) Second digit counter

Counts values from 0 to 59. The counter can be read and incremented. When the second digit counter is incremented, fractions below full seconds are reset. Therefore a carry occurs 1 second after the increment operation is finished.

| A3 | A2 | A1 | A0 | Name | D3             | D2                    | D1                    | D0              | Register contents          |

|----|----|----|----|------|----------------|-----------------------|-----------------------|-----------------|----------------------------|

| 0  | 0  | 0  | 0  | S1   | S <sub>8</sub> | <b>S</b> <sub>4</sub> | <b>S</b> <sub>2</sub> | S <sub>1</sub>  | 1-second digit counter     |

| 0  | 0  | 0  | 1  | S10  | 0              | S <sub>40</sub>       | S <sub>20</sub>       | S <sub>10</sub> | 10-second digit<br>counter |

#### (2) Minute digit counter

| A3                                                                  | A2 | A1 | A0 | Name | D3  | D2               | D1               | D0               | Register contents       |  |  |  |

|---------------------------------------------------------------------|----|----|----|------|-----|------------------|------------------|------------------|-------------------------|--|--|--|

| 0                                                                   | 0  | 1  | 0  | MI1  | miଃ | mi4              | mi <sub>2</sub>  | mi₁              | 1-minute digit counter  |  |  |  |

| 0                                                                   | 0  | 1  | 1  | MI10 | 0   | mi <sub>40</sub> | mi <sub>20</sub> | mi <sub>10</sub> | 10-minute digit counter |  |  |  |

| Counte values from 0 to 50. The counter can be read and incremented |    |    |    |      |     |                  |                  |                  |                         |  |  |  |

Counts values from 0 to 59. The counter can be read and incremented.

#### (3) Hour digit counter

| A3 | A2 | A1 | A0 | Name | D3             | D2 | D1              | D0              | Register contents       |

|----|----|----|----|------|----------------|----|-----------------|-----------------|-------------------------|

| 0  | 1  | 0  | 0  | H1   | h <sub>8</sub> | h4 | h <sub>2</sub>  | h1              | 1-minute digit counter  |

| 0  | 1  | 0  | 1  | H10  | PM/AM          | 0  | h <sub>20</sub> | h <sub>10</sub> | 10-minute digit counter |

Counts values from 0 to 23. The counter can be read, and the 1-hour digit counter can be incremented. (The 10-hour digit counter cannot be incremented.)

D0 in the control register 1 sets the 12-hour/24-hour display format.

| 24/12 bit          | Displayed time                             |

|--------------------|--------------------------------------------|

| 0 (12-hour format) | AM 12:00 to AM 11:59, PM 12:00 to PM 11:59 |

| 1 (24-hour format) | AM 00:00 to AM 11:59, PM 12:00 to PM 23:59 |

\* PM/AM bit: This bit is output also when 24-hour format is selected.

\* Time keeping is not affected also when the 12-hour/24- hour format is switched during clock operation.

#### (4) Day of the week digit counter

| A3 | A2 | A1 | A0 | Name | D3 | D2 | D1 | D0         | Register contents                |

|----|----|----|----|------|----|----|----|------------|----------------------------------|

| 0  | 1  | 1  | 0  | W    | 0  | W4 | W2 | <b>W</b> 1 | Day of the week digit<br>counter |

Counts values from 0 to 6. The counter can be read and incremented. The correspondence between count value and day of the week is set by the user.

| Example | Data                  | 0    | 1    | 2    | 3    | 4    | 5    | 6    |

|---------|-----------------------|------|------|------|------|------|------|------|

|         | Coded day of the week | Sun. | Mon. | Tue. | Wed. | Thu. | Fri. | Sat. |

#### (5) Day digit counter

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A3 | A2 | A1 | A0 | Name | D3             | D2             | D1              | D0              | Register contents    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|------|----------------|----------------|-----------------|-----------------|----------------------|

| $\begin{array}{ c c c c c c c c c } 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 \\ \hline 1 & 0 & 0 & 0 & 0 \\ \hline$ | 0  | 1  | 1  | 1  | D1   | d <sub>8</sub> | d <sub>4</sub> | d <sub>2</sub>  | d <sub>1</sub>  | 1-day digit counter  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1  | 0  | 0  | 0  | D10  | 0              | 0              | d <sub>20</sub> | d <sub>10</sub> | 10-day digit counter |

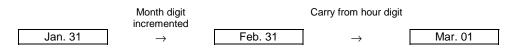

The counter value is different depending on the month.

(a) For long months (1, 3, 5, 7, 8, 10, 12), the counter counts values from 1 to 31. The counter can be read and incremented.

(b) For short months (4, 6, 9, 11), the counter counts values from 1 to 30. The counter can be read and incremented.

(c) For February, the counter counts values from 1 to 29 if it is a leap year and from 1 to 28 in other years. The counter can be read and incremented.

#### (6) Month digit counter

| Ļ |    | Ŭ  |    | Ŭ  | more | Ū               | Ŭ               | Ū               | 11010           | to month aigh counter  |

|---|----|----|----|----|------|-----------------|-----------------|-----------------|-----------------|------------------------|

| Т | 1  | 0  | 1  | 0  | MO10 | 0               | 0               | 0               | <b>mo</b> 10    | 10-month digit counter |

|   | 1  | 0  | 0  | 1  | MO1  | mo <sub>8</sub> | mo <sub>4</sub> | mo <sub>2</sub> | mo <sub>1</sub> | 1-month digit counter  |

|   | A3 | A2 | A1 | A0 | Name | D3              | D2              | D1              | D0              | Register contents      |

Counts values from 1 to 12. The counter can be read and incremented.

#### (7) Year digit counter

| A3        | A2        | A1 | A0  | Name | D3          | D2              | D1                     | D0          | Register contents                  |

|-----------|-----------|----|-----|------|-------------|-----------------|------------------------|-------------|------------------------------------|

| 1         | 0         | 1  | 1   | Y1   | <b>y</b> 8  | У4              | <b>y</b> 2             | У1          | 1-year digit counter               |

| 1         | 1         | 0  | 0   | Y10  | <b>y</b> 80 | y <sub>40</sub> | <b>y</b> <sub>20</sub> | <b>y</b> 10 | 10-year digit counter              |

| Country 1 | alues for |    | 0 ( | 1    | 11.11.11.11 | d               | . <b>T</b> I           |             | a ha an a ha a ha a hin an an an a |

Counts values from 0 to 99 for the last two digits of the year. The counter can be read and incremented. Until 2099, leap year compensation is automatically provided. ('92, '96, '00, '04, '08, '12, '16, '20 ... are leap years.)

#### 8.2.2. Control Registers

#### (1) Control register 1

| A3 / | AZ | A1 | A0 | Name  | D3  | D2    | D1   | D0    | Register contents  |

|------|----|----|----|-------|-----|-------|------|-------|--------------------|

| 1    | 1  | 0  | 1  | CNT 1 | TPS | 30ADJ | CNTR | 24/12 | Control register 1 |

Control register 1 performs 12-hour/24-hour display format switching, digit counter reset, 30 second adjustment, and timing pulse signal switching. The register allows data read and write.

#### (a) TPS bit (D3)

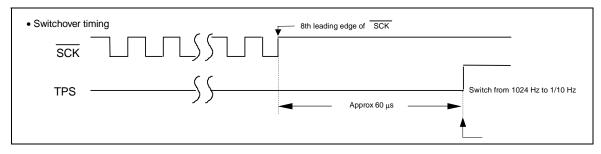

The TPS bit selects the timing pulse output waveform.

| TPS bit | Frequency (cycle)  | "L" level duty  |

|---------|--------------------|-----------------|

| 0       | 1024 Hz (976.5 μs) | 1/2 (488.28 μs) |

| 1       | 1/10 Hz (10 s)     | 3/5 (6 s)       |

|         |                    |                 |

1/10 Hz is not output for 10 seconds after power-on or system reset (output is "L").

#### (b) 30ADJ bit (D2)

When "1" is written to this bit, one of the following reset operations is carried out.

| Seconds digit before<br>adjustment | Seconds digit after adjustment                           |

|------------------------------------|----------------------------------------------------------|

| 29 seconds or less                 | Seconds reset to "00" without carry to 1-minute<br>digit |

| 30 seconds or more                 | Seconds reset to "00" with carry to 1-minute digit       |

When "1" was written to the 30ADJ bit, the bit automatically resets itself to "0" within 76.3  $\mu$ s The 30 second adjustment function also resets fractions below full seconds. The TPOUT 1/10 Hz duty changes for one cycle only during 30 second adjustment.

#### (c) CNTR bit (D1)

The CNTR bit resets the time/calendar counters.

| CNTR bit | Content                                                 |

|----------|---------------------------------------------------------|

| 0        | Normal mode (time/calendar counters can be incremented) |

| 1        | Selected counter is reset to "0"                        |

\* For counters other than the year, selecting either the 1 or the 10 digit counter will reset both counters.

When CNTR is used to reset the seconds, fractions below full seconds are also reset. The TPOUT 1/10 Hz duty changes for one cycle only during reset.

#### (d) 24/12 bit (D0)

The 24/12 bit serves to switch between 12-hour and 24-hour format.

| 24/12 bit          | Displayed time                             |

|--------------------|--------------------------------------------|

| 0 (12-hour format) | AM 12:00 to AM 11:59, PM 12:00 to PM 11:59 |

| 1 (24-hour format) | AM 00:00 to AM 11:59, PM 12:00 to PM 23:59 |

|                    |                                            |

\* PM/AM bit: This bit is output also when 24-hour format is selected.

\* Time keeping is not affected also when the 12-hour/24- hour format is switched during clock operation.

(2) Control register 2

| A3 | A2 | A1 | A0 | Name  | D3   | D2   | D1 | D0 | Register contents  |

|----|----|----|----|-------|------|------|----|----|--------------------|

| 1  | 1  | 1  | 0  | CNT 2 | BUSY | PONC | _  | *  | Control register 2 |

Control register 2 provides flags for carry detect and power-on-clear detect.

#### (a) BUSY bit (D3)

|  | ounter digit carry detection. |

|--|-------------------------------|

|  |                               |

| BUSY bit | Mode        | Meaning                                     |

|----------|-------------|---------------------------------------------|

| 0        | Normal mode | Time/calendar counter read/write possible   |

| 1        | Carry       | Time/calendar counter read/write prohibited |

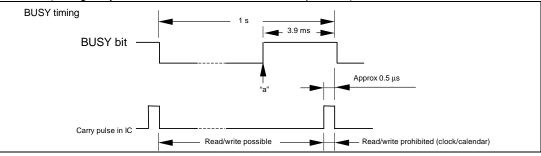

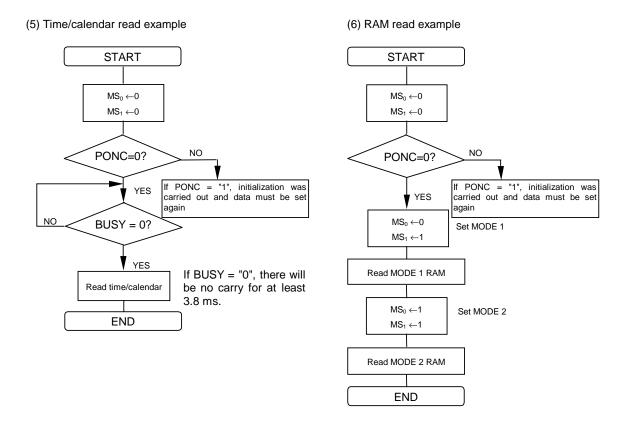

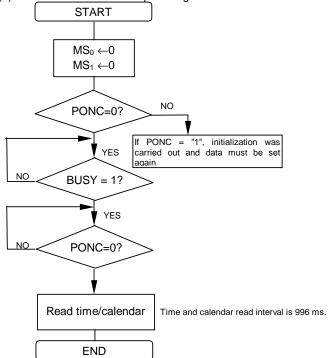

If the BUSY bit is "L", carry does not occur for at least 3.9 ms. (Also when read/write is carried out at point "a" in the chart below, carry does not occur for 3.9 ms.)

Take the processing time into consideration and design the read/write operation to complete within 3.8 ms. Clock read/write during carry

· Read It may not be possible to read correct data.

• Write Because the clock has priority, the write operation does not increment the counter.

(During carry, the result is the same as for a read operation.)

#### (b) PONC bit (D2)

The PONC bit is the power-on-clear detection bit (see next page). It is set to "1" when power-on-clear is detected. The PONC bit is reset  $(1 \rightarrow 0)$  by setting the SYSR bit to "1".

(c) D1 bit (bit marked "-")

When this bit is read, data are undefined.

(d) D0 bit (bit marked " \* ")

When writing this bit, always set it to "0".

#### (3) Control register 3

Control registers 3 serves for reading and writing data for address mode switching and making system reset settings.

The control register 3 applies to modes 0 - 2.

| A3 | A2 | A1 | A0 | Name  | D3   | D2   | D1              | D0     | Register contents  |

|----|----|----|----|-------|------|------|-----------------|--------|--------------------|

| 1  | 1  | 1  | 1  | CNT 3 | SYSR | TEST | MS <sub>1</sub> | $MS_0$ | Control register 3 |

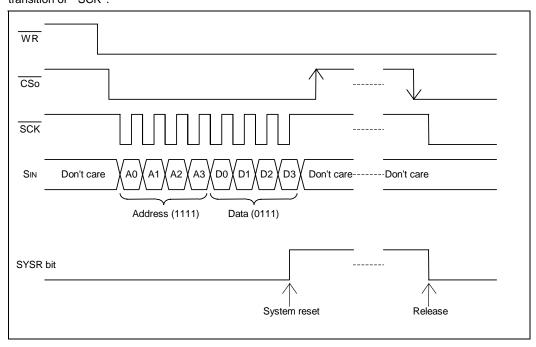

(a) SYSR bit (D3)

The SYSR bit serves for clearing all counter registers (see section on initialization on next page). This bit is reset by making  $\overline{CS0}$  High and  $\overline{SCK}$  Low.

#### (b) TEST bit (D2)

The TEST bit serves to switch the IC to the test mode.

Note Be sure to permanently set this bit to "0". Otherwise correct operation is not assured.

(c) MS1, MS0 bit (D1, D0)

The MS1 and MS0 bits serve for address switching.

| Γ | MS1 | MS0 | Mode name | Content                                                                      |

|---|-----|-----|-----------|------------------------------------------------------------------------------|

|   | 0   | 0   | MODE 0    | Time/calendar counters and control registers 1 - 3                           |

|   | 0   | 1   | MODE 0    | Time/calendar counters and control registers 1 - 3                           |

|   | 1   | 0   | MODE 1    | User RAM area (RA <sub>0</sub> - RA <sub>59</sub> ) and control register 3   |

|   | 1   | 1   | MODE 2    | User RAM area (RA <sub>60</sub> - RA <sub>119</sub> ) and control register 3 |

#### 8.3. How to use

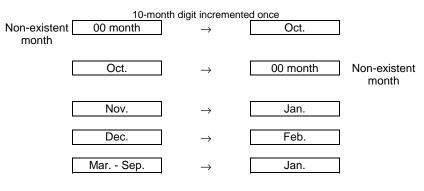

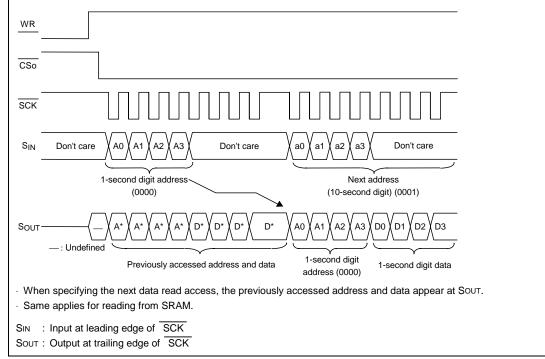

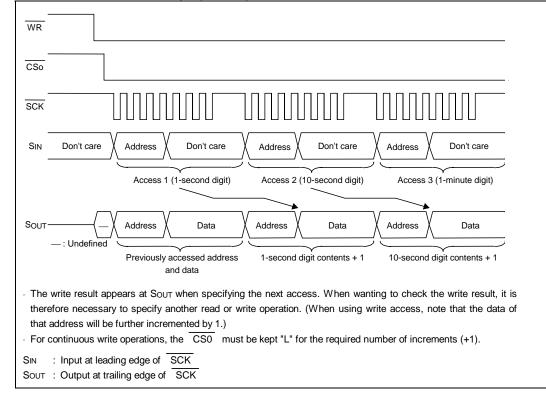

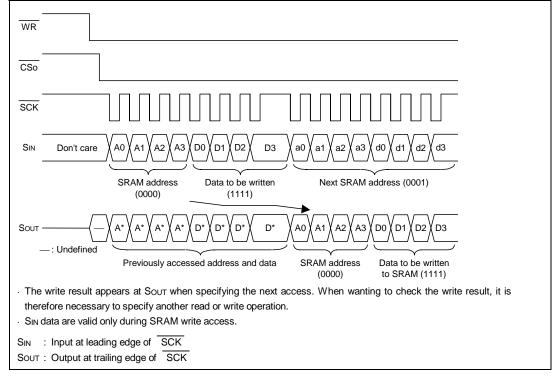

#### 8.3.1. Data Read

When  $\overline{CSO}$  is "L", the serial address data input at SIN is read at the leading edge of  $\overline{SCK}$ . Next, when  $\overline{WR} =$  "H" is taken in on the 8th pulse leading edge of  $\overline{SCK}$  the counter control register or RAM address is selected. The data of the selected counter control register or RAM address are output in the following cycle from SOUT, in sync with the  $\overline{SCK}$  trailing edge.

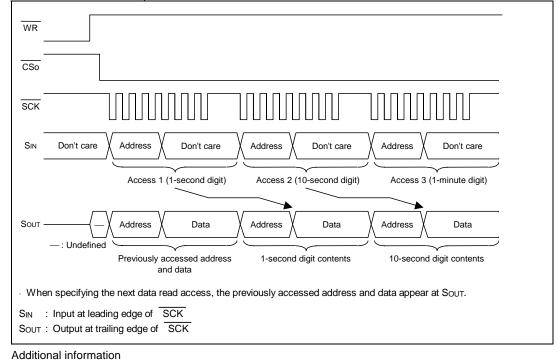

#### 8.3.2. Data Write/Modify

When  $\overline{CSO}$  is "L", the serial address data input at SIN is read at the leading edge of  $\overline{SCK}$ . Next, when  $\overline{WR}$  = "H" is taken in on the 8th pulse leading edge of  $\overline{SCK}$ , the counter control register or RAM address is selected, and data are written as shown below.

| Item                 | Content                                        |

|----------------------|------------------------------------------------|

| Time/calendar        | Counter, counter data increment (+1) *         |

| Control register/RAM | Serial address/lower 4 bit of data are written |

The selected counter register or RAM address data are output in the following cycle from SOUT, in sync with the  $\overline{SCK}$  trailing edge.

\* The hour digit counter can be incremented via the 1-hour digit counter.

#### 8.3.3. Initialize

(1) System reset

When the SYSR bit in the control register 3 is set to "1", all logic bits are initialized. The SYSR bit is reset to "0" by causing an up transition of  $\overline{CS0}$  and a down transition of  $\overline{SCK}$ .

| Register               | Data                                                                                                 |

|------------------------|------------------------------------------------------------------------------------------------------|

| Time/calendar counters | <ul> <li>year, 01-month, 01-day, AM 12-hour, 00-minute,<br/>00- second, 0-day of the week</li> </ul> |

| Control registers      | All "0" (SYSR = "1")                                                                                 |

| User RAM area          | Undefined                                                                                            |

Until system reset is released, TPOUT is fixed to "L".

1/10 Hz is not output for 10 seconds after system reset is released.

#### (2) Power-on-clear

At power-on, the power-on-clear function automatically performs a sequence identical to system reset. However, because the PONC bit remains at "1", a system reset must be performed to set the PONC bit to "0" before setting the time and calendar.

#### 8.3.4. Timing Pulse Output

The timing pulse is output from the TPOUT pin.

Normally, a 1024 Hz signal is output. By setting the TPS bit in the control register 1 to "1", this can be switched to 1/10 Hz.

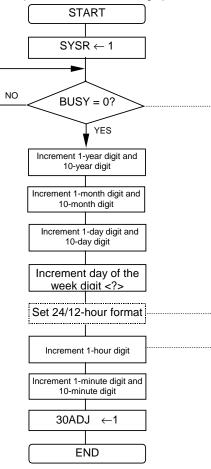

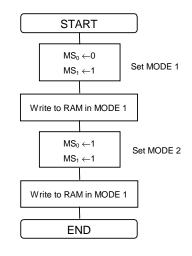

8.3.5. Sample Operation Flow Charts

(1) Time/calendar initialize example

(Example for initialization through power-on-clear when battery was changed etc.)

- Release PONC bit = "1"  $(1 \rightarrow 0)$

- While BUSY = "1", a carry operation is in progress and the setting should not be carried out. The following processing steps must be completed within 996 ms after SYSR ← "1" or after the BUSY bit down transition was detected. If the process takes longer, the BUSY bit must be checked again for continued processing.

- It is advisable to start the setting from the year digit, to prevent setting nonexistent data.

- When the 1-digit of the year, month, day, hour, minute, or second is set, carry to the 10-digit can occur.

- It is advisable to set this before setting the hour digit, to prevent setting nonexistent data.

- Set the 10-hour digit by incrementing the 1-hour digit.

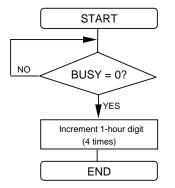

(2) Time/calendar modify example (8:00  $\rightarrow$  12:00)

While BUSY = "1", a carry operation is in progress and the setting should not be carried out.

4 times (8  $\rightarrow$  9  $\rightarrow$  10 $\rightarrow$  11 $\rightarrow$  12)  $\uparrow$

MS0=0, MS1=0

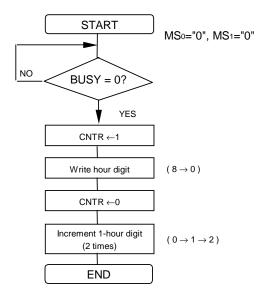

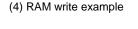

10-hour digit is automatically carried. The processing should be completed within 3.8 ms after detecting BUSY = "0". (3) Time/calendar modify example using counter reset (8:00  $\rightarrow$  2:00)

Note 1 If processing is not completed within 3.8 ms, check the BUSY bit again. Note 2 Reset (CNTR  $\leftarrow$  "1") applies to the digits for which writing was perfor

Reset (CNTR  $\leftarrow$  "1") applies to the digits for which writing was performed [1-hour digit and 10-hour digit in example (3)]. Consequently, to change the setting from 11:00 to 2:00, the hour digit must be reset (CNTR  $\rightarrow$  "1").

For the year, CNTR is used separately for the 1-year digit and 10-year digit. Performing CNTR on the 1-year digit does not change the 10-year digit. Conversely, performing CNTR on the 10-year digit does not change the 1-year digit.

(7) Time/calendar read example using BUSY bit down transition

8.3.6. CS1 and CS0 Operation

When designing a floating arrangement, take the following into consideration.  $\overline{CSO}$  can be floating while CS1 = "L", but CS1 can never be floating. (Otherwise a through current would flow, leading to increased current consumption during operation on backup battery power.) When CS1 = "L", input is disabled, and SOUT and  $\overline{TPOUT}$  are at high impedance.

#### 8.3.7. System Power Down During Interface Operation

When the system power goes down during interface operation with the CPU, causing CS1 to become "L", the incomplete data will be invalid. Immediately after system power restoration, when CS1 has become "H", the output data from SOUT are undefined for one cycle.

#### 8.3.8. Power Supply and CS1 Operation

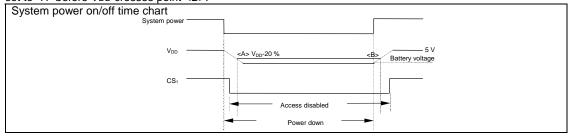

When the system power is shut down, VDD falls to the battery voltage. When used at VDD  $\pm 10\%$ , CS1 must be set to "L" before VDD crosses point <A> in the diagram below. When system power is restored, CS1 must be set to "H" before VDD crosses point <B>.

#### 8.3.9. Power-On Reset

When the system power is turned on, the power-on reset function operates automatically, performing a sequence identical to system reset. However, because the PONC bit remains at "1", a system reset must be performed to set the PONC bit to "0" before setting the time and calendar.

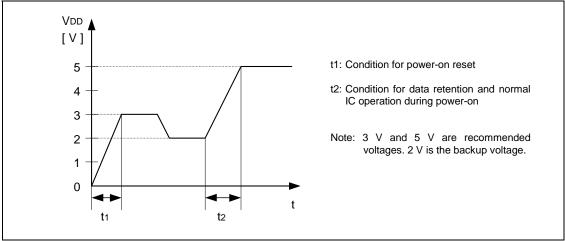

The conditions for power-on reset and the conditions for data retention and normal IC operation during power fluctuation are shown below.

|     |                                                                                                        |          | Ta = -30 °C to +70 °C                   |

|-----|--------------------------------------------------------------------------------------------------------|----------|-----------------------------------------|

| t 1 | Condition tR for power-on reset<br>at $0^{+0.3}$ V $\rightarrow$ 3 V or $0^{+0.3}$ V $\rightarrow$ 5 V | (Note 1) | 1.0 $\mu s/V \leq t R \leq 1.6 \ ms/V$  |

| t 2 | Condition tR for no power-on reset at 2 V $\rightarrow$ 3 V or 2 V $\rightarrow$ 5 V                   | (Note 2) | 1.0 $\mu$ s/V $\leq$ tR $\leq$ 1.6 ms/V |

- Note 1 The voltage level before initial power-on should be 0.3 V or less. If powering up from an intermediate potential, power-on reset may not be performed correctly. Be sure to verify correct operation.