#### **General Description**

The MAX2078 octal-channel ultrasound front-end is a fully integrated bipolar, high-density octal-channel ultrasound receiver optimized for low cost, high-channel count, high-performance portable and cart-based ultrasound systems. The easy-to-use IC allows the user to achieve high-end 2D, PW, and CW Doppler (CWD) imaging capability using substantially less space and power. The highly compact imaging receiver lineup. including low-noise amplifier (LNA), variable-gain amplifier (VGA), and anti-alias filter (AAF), achieves an ultra-low 2.4dB noise figure at  $R_S = R_{IN} = 200\Omega$  at a very low 64.8mW per channel power dissipation. The full imaging receiver channel has been optimized for second-harmonic imaging with -64dBFS second-harmonic distortion performance with a 1VP-P 5MHz output signal. The bipolar front-end has also been optimized for excellent low-velocity PW and color-flow Doppler sensitivity with an exceptional near-carrier SNR of 140dBc/Hz at 1kHz offset from a 5MHz 1VP-P output clutter signal.

A fully integrated high-performance, programmable CWD beamformer is also included. Separate I/Q mixers for each channel are available for optimal CWD sensitivity in high-clutter environments, yielding an impressive near-carrier SNR of 154dBc/Hz at 1kHz offset from a 1.25MHz 200mV<sub>P-P</sub> input clutter signal.

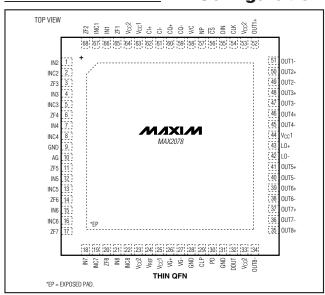

The MAX2078 octal-channel ultrasound front-end is available in a small 10mm x 10mm, 68-pin thin QFN package with an exposed pad and is specified over a 0°C to +70°C temperature range.

#### **Applications**

Medical Ultrasound Imaging Sonar

### **Ordering Information**

| PART        | TEMP RANGE   | PIN-PACKAGE     |

|-------------|--------------|-----------------|

| MAX2078CTK+ | 0°C to +70°C | 68 Thin QFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

#### **Features**

- 8 Full Channels of LNA, VGA, AAF, and CWD Mixers in a Small, 10mm x 10mm TQFN Package

- ♦ Pin Compatible with MAX2077 with LNA, VGA. and AAF in 10mm x 10mm TQFN Variant

- Ultra-Low Full-Channel Noise Figure of 2.4dB at  $R_{IN} = R_S = 200\Omega$

- ◆ Low Output-Referred Noise of 23nV/√Hz at 5MHz, 20dB Gain, Yielding a Broadband SNR of 68dB\*\* for Excellent Second-Harmonic Imaging

- ♦ High Near-Carrier SNR of 140dBc/Hz at 1kHz Offset from a 5MHz, 1V<sub>P-P</sub> Output Signal, and 20dB of Gain for Excellent Low-Velocity PW and Color-Flow Doppler Sensitivity in a High-Clutter **Environment**

- ♦ Ultra-Low-Power 64.8mW per Full-Channel (LNA, VGA, and AAF) Normal Imaging Mode (234mW per Channel in CWD Mode)

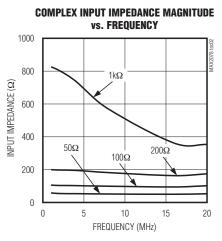

- ♦ Selectable Active Input-Impedance Matching of  $50\Omega$ ,  $100\Omega$ ,  $200\Omega$ , and  $1k\Omega$

- ♦ Wide Input-Voltage Range of 330mV<sub>P-P</sub> in High LNA Gain Mode and 550mV<sub>P-P</sub> in Low LNA Gain Mode

- ♦ Integrated Selectable 3-Pole 9MHz, 10MHz, 15MHz, and 18MHz Butterworth AAF

- ♦ Fast-Recovery, Low-Power Modes (< 2µs)

- ◆ Fully Integrated, High Dynamic Range CWD Beamformer with Near-Carrier SNR of 154dBc/Hz at 1kHz Offset from a 1.25MHz, 200mV<sub>P-P</sub> Input **Clutter Signal**

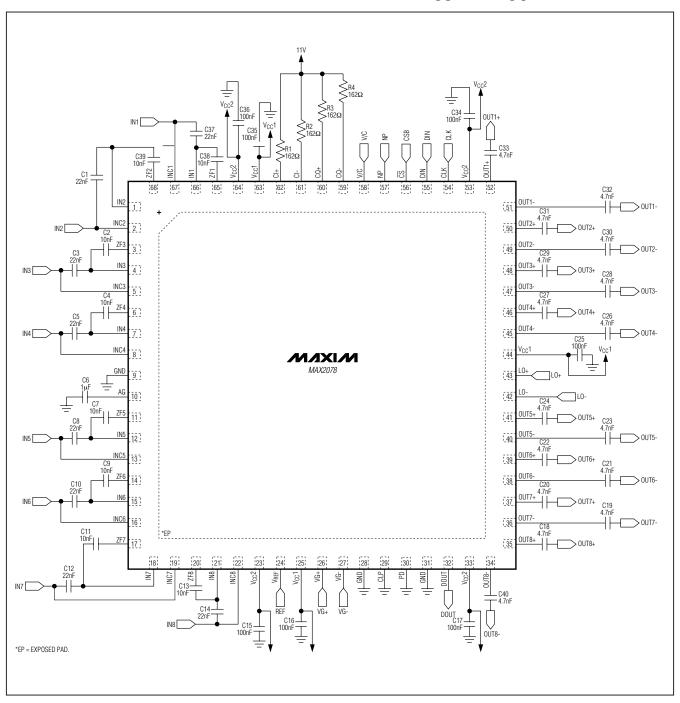

### Pin Configuration

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

<sup>\*</sup>EP = Exposed pad.

<sup>\*\*</sup>When coupled with the MAX1437B ADC.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +5.5V                              | be applied in this order                              |

|------------------------------------------------------------------|-------------------------------------------------------|

| Vcc2 - Vcc1> -0.3V                                               | Input Differential Voltage2.0VP-P differential        |

| CI_, CQ_ to GND0.3V to +13V                                      | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| ZF_, IN_, AG to GND0.3V to (V <sub>CC</sub> + 0.3V)              | 68-Pin TQFN (derated 40mW/°C above +70°C)4W           |

| INC20mA DC                                                       | Operating Temperature Range (Note 1A)0°C to +70°C     |

| V <sub>REF</sub> to GND0.3V to +3V                               | Junction Temperature+150°C                            |

| IN_ to AG0.6V to +0.6V                                           | θ <sub>JC</sub> (Note 1B, 1C)+0.3°C/W                 |

| OUT_, LO_, DIN, DOUT, VG_, NP, $\overline{\text{CS}}$ , CLK, PD, | θ <sub>JA</sub> (Note 1C, 1D)+20°C/W                  |

| CLP, V/C to GND0.3V to V <sub>CC</sub> 1 + 0.3V                  | Storage Temperature Range40°C to +150°C               |

| CI_, CQ_, VCC_, VREF analog and digital control signals must     | Lead Temperature (soldering, 10s)+300°C               |

- Note 1A: T<sub>C</sub> is the temperature on the exposed pad of the package. T<sub>A</sub> is the ambient temperature of the device and PCB.

- Note 1B: Junction temperature T<sub>J</sub> = T<sub>C</sub> + (θ<sub>JC</sub> x V<sub>CC</sub> x I<sub>CC</sub>). This formula can only be used if the component is soldered down to a printed circuit board pad containing multiple ground vias to remove the heat. The junction temperature must not exceed 150°C.

- **Note 1C:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

- Note 1D: Junction temperature  $T_J = T_A + (\theta_{JA} \times V_{CC} \times I_{CC})$ , assuming there is no heat removal from the exposed pad. The junction temperature must not exceed 150°C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit,  $V_{REF} = 2.475V$  to 2.525V,  $V_{CC}1 = 3.13V$  to 3.47V,  $V_{CC}2 = 4.5V$  to 5.25V,  $T_{A} = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ , CLP = 0, PD = 0, no RF signals applied. Typical values are at  $V_{CC}1 = 3.3V$ ,  $V_{CC}2 = 4.75V$ ,  $T_{A} = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                        | SYMBOL            | CONDITIONS                                                         | MIN   | TYP               | MAX   | UNITS |

|----------------------------------|-------------------|--------------------------------------------------------------------|-------|-------------------|-------|-------|

| 3.3V Supply Voltage              | V <sub>CC</sub> 1 |                                                                    | 3.13  | 3.3               | 3.47  | V     |

| 4.75V/5V Supply Voltage          | V <sub>CC</sub> 2 |                                                                    | 4.5   | 4.75              | 5.25  | V     |

| External Reference Voltage Range | V <sub>REF</sub>  | (Note 3)                                                           | 2.475 |                   | 2.525 | V     |

| CMOS Input High Voltage          | VIH               | Applies to CMOS control inputs                                     | 2.5   |                   |       | V     |

| CMOS Input Low Voltage           | V <sub>IL</sub>   | Applies to CMOS control inputs                                     |       |                   | 0.8   | V     |

| CMOS Input Leakage Current       | I <sub>IN</sub>   | T <sub>A</sub> = +25°C, applies to CMOS control inputs; 0 to 3.47V |       |                   | 10    | μΑ    |

| DATA Output High Voltage         | DOUT_HI           | 10MΩ load                                                          |       | V <sub>CC</sub> 1 |       | V     |

| DATA Output Low Voltage          | DOUT_LO           | 10MΩ load                                                          |       | 0                 |       | V     |

#### DC ELECTRICAL CHARACTERISTICS—VGA MODE

(Typical Application Circuit,  $V_{REF} = 2.475V$  to 2.525V,  $V_{CC}1 = 3.13V$  to 3.47V,  $V_{CC}2 = 4.5V$  to 5.25V,  $T_{A} = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ ,  $V_{CD} = 0$ ,  $V_{CC} = 1$ ,

| PARAMETER                              | SYMBOL      | SYMBOL CONDITIONS                     |  | TYP  | MAX  | UNITS |

|----------------------------------------|-------------|---------------------------------------|--|------|------|-------|

| 4.75V/5V Supply Standby Current        | I_NP_5V_TOT | NP = 1, all channels                  |  | 3.9  | 6    | mA    |

| 3V Supply Standby Current              | I_NP_3V_TOT | NP = 1, all channels                  |  | 1.7  | 3    | mA    |

| 4.75V/5V Power-Down Current            | I_PD_5V_TOT | PD = 1, all channels                  |  | 0.4  | 10   | μΑ    |

| 3V Power-Down Current                  | I_PD_3V_TOT | PD = V <sub>CC</sub> 1, all channels  |  | 0.3  | 10   | μΑ    |

| 3V Supply Current per Channel          | I_3V_NM     | Total I divided by 8, VG+ - VG- = -2V |  | 11   | 16   | mA    |

| 4.75V/5V Supply Current per<br>Channel | I_5V_NM     | Total I divided by 8                  |  | 6.0  | 8.3  | mA    |

| DC Power per Channel                   | P_NM        |                                       |  | 64.8 | 92.3 | mW    |

2 \_\_\_\_\_\_ *M*/XI/N

#### DC ELECTRICAL CHARACTERISTICS—VGA MODE (continued)

(Typical Application Circuit,  $V_{REF} = 2.475V$  to 2.525V,  $V_{CC}1 = 3.13V$  to 3.47V,  $V_{CC}2 = 4.5V$  to 5.25V,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ ,  $V_{CC}1 = 3.3V$ ,  $V_{CC}2 = 4.75V$

| PARAMETER                                            | SYMBOL           | CONDITIONS    | MIN   | TYP         | MAX   | UNITS |

|------------------------------------------------------|------------------|---------------|-------|-------------|-------|-------|

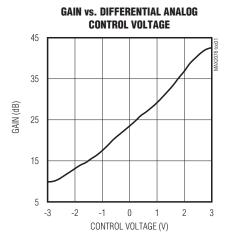

| Differential Analog Control<br>Voltage Range         | VGAIN_RANG       | VG+ - VG-     |       | ±3          |       | V     |

| Common-Mode Voltage for<br>Difference Analog Control | VGAIN_COMM       | (VG+ + VG-)/2 |       | 1.65<br>±5% |       | V     |

| Source/Sink Current for Gain<br>Control Pins         | I_ACONTROL       | Per pin       |       | ±1.6        | ±2.3  | μΑ    |

| Reference Voltage Input                              | V <sub>REF</sub> |               | 2.475 |             | 2.525 | V     |

| Reference Current                                    | IREF             | All channels  |       | 9.7         | 13    | μΑ    |

| Output Common-Mode Level                             | V <sub>CMO</sub> |               |       | 1.73        |       | V     |

#### DC ELECTRICAL CHARACTERISTICS—CW MODE

(Typical Application Circuit,  $V_{REF}=2.475V$  to 2.525V,  $V_{CC}1=3.13V$  to 3.47V,  $V_{CC}2=4.5V$  to 5.25V,  $T_{A}=0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND}=0V$ , NP=0,  $P_{CC}1=0$ ,  $P_{CC$

| PARAMETER                                  | SYMBOL        | CONDITIONS                                    | MIN | TYP          | MAX  | UNITS             |

|--------------------------------------------|---------------|-----------------------------------------------|-----|--------------|------|-------------------|

| Reference Current                          | IREF          |                                               |     | 82.7         |      | μΑ                |

| Mixer LVDS LO Input Common-Mode Voltage    | V_LVDS_CM     | LO+ and LO-                                   |     | 1.25<br>±0.2 |      | V                 |

| LVDS LO Differential Input Voltage         | V_LVDS_DM     | Common-mode input voltage = 1.25V (Note 4)    | 200 | 700          |      | mV <sub>P-P</sub> |

| LVDS LO Input Common-Mode<br>Current       | I_LVDS_CM     | Current out of each pin,<br>V_LVDS_CM = 1.25V |     | 130          |      | μΑ                |

| LVDS LO Differential Input Resistance      | R_DM_LVDS     | (Note 5)                                      | 4   |              |      | kΩ                |

| POWER-DOWN MODE                            |               |                                               |     |              |      |                   |

| 4.75V/5V Supply Current per Channel        | I_C_5V_P      | PD = 1                                        |     | 0.6          | 10   | μΑ                |

| 3.3V Supply Current per Channel            | I_C_3_3V_P    | PD = 1                                        |     | 0.1          | 10   | μΑ                |

| LOW-POWER MODE                             |               |                                               |     |              |      |                   |

| 4.75V/5V Supply Current per Channel        | I_C_5V_L      | CLP = 1                                       |     | 27           | 30   | mA                |

| 3.3V Supply Current per Channel            | I_C_3_3V_L    | CLP = 1                                       |     | 0.4          | 0.95 | mA                |

| 11V Supply Current per Channel             | I_C_11V_L     | CLP = 1                                       |     | 6.8          | 8.4  | mA                |

| On-Chip Power Dissipation (All 8 Channels) | PDIS_FP_TOT_L | CLP = 1                                       |     | 1.44         | 1.7  | W                 |

| NORMAL POWER MODE                          |               |                                               |     |              |      |                   |

| 4.75V/5V Supply Current per Channel        | I_C_5V_N      |                                               |     | 31           | 34   | mA                |

| 3.3V Supply Current per Channel            | I_C_3_3V_N    |                                               |     | 0.4          | 0.95 | mA                |

| 11V Supply Current per Channel             | I_C_11V_N     |                                               |     | 11.3         | 13   | mA                |

| On-Chip Power Dissipation (All 8 Channels) | PDIS_FP_TOT_N | (Note 6)                                      |     | 1.87         | 2.2  | W                 |

#### **AC ELECTRICAL CHARACTERISTICS**

(Typical Application Circuit,  $V_{REF}=2.475V$  to 2.525V,  $V_{CC}1=3.13V$  to 3.47V,  $V_{CC}2=4.5V$  to 5.25V,  $T_A=0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND}=0V$ , NP=0, PD=0, PD=0,

| PARAMETER                                 | CONDITIONS                                    | MIN | TYP  | MAX | UNITS                            |

|-------------------------------------------|-----------------------------------------------|-----|------|-----|----------------------------------|

| Mode Select Response Time                 | V/C stepped from 0 to 1, DC stable within 10% |     | 1    |     |                                  |

| (Note 7)                                  | V/C stepped from 1 to 0, DC stable within 10% |     | 1    |     | μs                               |

| High Gain Maximum Input-<br>Voltage Range | High LNA gain D43/D42/D41/D40 = 1/0/1/0       |     | 0.33 |     | V <sub>P-P</sub><br>differential |

| Low Gain Maximum Input-Voltage<br>Range   | Low LNA gain D43/D42/D41/D40 = 0/0/0/1        |     | 0.6  |     | V <sub>P-P</sub><br>differential |

#### AC ELECTRICAL CHARACTERISTICS—VGA MODE

(Typical Application Circuit,  $V_{REF}=2.475V$  to 2.525V,  $V_{CC}1=3.13V$  to 3.47V,  $V_{CC}2=4.5V$  to 5.25V,  $T_{A}=0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND}=0V$ , V/C=1, NP=0, PD=0, PD=0

| PARAMETER                                 | CONDITIONS                                                                                                  | MIN  | TYP  | MAX  | UNITS              |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|--------------------|

|                                           | $D42/D41/D40 = 0/0/0, R_{IN} = 50\Omega$                                                                    | 47.5 | 50   | 60   |                    |

| Input Impedance                           | $D42/D41/D40 = 0/0/1$ , $R_{IN} = 100\Omega$                                                                | 90   | 100  | 110  | $\frac{1}{\Omega}$ |

| Input Impedance                           | $D42/D41/D40 = 0/1/0$ , $R_{IN} = 200\Omega$                                                                | 185  | 200  | 210  |                    |

|                                           | $D42/D41/D40 = 0/1/1$ , $R_{IN} = 1000\Omega$ , $f_{RF} = 2MHz$                                             | 700  | 830  | 1000 |                    |

|                                           | $R_S = R_{IN} = 50\Omega$ , $VG + - VG - = +3V$                                                             |      | 4.5  |      |                    |

| Noise Figure                              | $R_S = R_{IN} = 100\Omega$ , $VG+ - VG- = +3V$                                                              |      | 3.4  |      | dB                 |

| Noise Figure                              | $R_S = R_{IN} = 200\Omega$ , $VG+ - VG- = +3V$                                                              |      | 2.4  |      | UD UD              |

|                                           | $R_S = R_{IN} = 1000\Omega$ , $VG+ - VG- = +3V$                                                             |      | 2.1  |      |                    |

| Low-Gain Noise Figure                     | D43/D42/D41/D40 = 0/0/0/1, LNA gain = 12.5dB,<br>R <sub>S</sub> = $R_{IN}$ = 200 $\Omega$ , VG+ - VG- = +3V |      | 3.9  |      | dB                 |

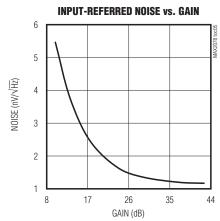

| Input-Referred Noise Voltage              | D43/D42/D41/D40 = 1/1/1/0                                                                                   |      | 0.9  |      | nV/√Hz             |

| Input-Referred Noise Current              | D43/D42/D41/D40 = 1/1/1/0                                                                                   |      | 2.1  |      | pA/√Hz             |

| Maximum Gain, High Gain Setting           | VG+ - VG- = +3V                                                                                             | 41   | 42.8 | 45   | dB                 |

| Minimum Gain, High Gain Setting           | VG+ - VG- = -3V                                                                                             | 8.5  | 10   | 11   | dB                 |

| Maximum Gain, Low Gain Setting            | D43/D42/D41/D40 = 0/0/0/1, VG+ - VG- = +3V                                                                  | 35   | 36.8 | 38   | dB                 |

| Minimum Gain, Low Gain Setting            | D43/D42/D41/D40 = 0/0/0/1, VG+ - VG- = -3V                                                                  | 2.5  | 4    | 6    | dB                 |

|                                           | D45/D44 = 0/0, f <sub>C</sub> = 9MHz                                                                        |      | 9    |      |                    |

| Anti-Aliasing Filter 3dB Corner Frequency | $D45/D44 = 0/1$ , $f_C = 10MHz$                                                                             |      | 10   |      | NALI-              |

|                                           | $D45/D44 = 1/0, f_C = 15MHz$                                                                                |      | 15   |      | MHz                |

|                                           | $D45/D44 = 1/1, f_C = 18MHz$                                                                                |      | 18   |      |                    |

| Gain Range                                | VG+ - VG- = -3V  to  +3V                                                                                    |      | 33   |      | dB                 |

### AC ELECTRICAL CHARACTERISTICS—VGA MODE (continued)

(Typical Application Circuit,  $V_{REF}=2.475V$  to 2.525V,  $V_{CC}1=3.13V$  to 3.47V,  $V_{CC}2=4.5V$  to 5.25V,  $T_A=0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND}=0V$ , V/C=1, NP=0, PD=0, PD=0,

| PARAMETER                                  | CONDITIONS                                                                                                                                                                                                                 | MIN                                  | TYP   | MAX | UNITS   |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|-----|---------|

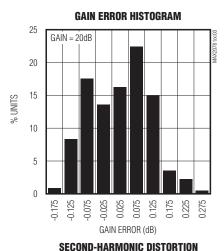

|                                            | Measured at $T_A = +25^{\circ}C$ , $VG+-VG-=-2V$                                                                                                                                                                           |                                      | ±0.4  |     | _       |

| Absolute Gain Error                        | Measured at $T_A = +25^{\circ}C$ , $VG+ - VG- = 0V$                                                                                                                                                                        |                                      | ±0.4  |     | dB      |

|                                            | Measured at $T_A = +25^{\circ}C$ , $VG+ - VG- = +2V$                                                                                                                                                                       |                                      | ±0.4  |     |         |

| Input Cain Compression                     | VG+ - VG- = -3V (VGA minimum gain), gain ratio with 330mV <sub>P-P</sub> /50mV <sub>P-P</sub> input tones                                                                                                                  |                                      | 1.4   |     | - dB    |

| Input Gain Compression                     | LNA low gain = 12.5dB, VG+ - VG- = -3V (VGA minimum gain), gain ratio with $600mV_{P-P}/50mV_{P-P}$                                                                                                                        |                                      | 0.8   |     | ив      |

| VGA Gain Response Time                     | Gain step up ( $V_{IN} = 5mV_{P-P}$ , gain changed from 10dB to 44dB, settling time is measured within 1dB final value)                                                                                                    |                                      | 1.4   |     | -10     |

| van daiii nesponse nine                    | Gain step down (V <sub>IN</sub> = 5mV <sub>P-P</sub> , gain changed from 44dB to 10dB, settling time is measured within 1dB final value)                                                                                   |                                      | 1.6   |     | μs      |

| VGA Output Offset Under Pulsed<br>Overload | Overdrive is ±10mA in clamping diodes, gain at 30dB, 16 pulses at 5MHz, repetition rate 20kHz; offset is measured at output when RF duty cycle is off                                                                      | 180                                  |       | mV  |         |

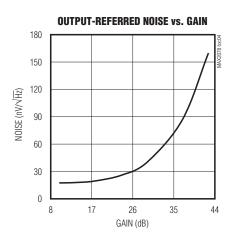

| Small-Signal Output Noise                  | 20dB of gain, VG+ - VG- = -0.85V, no input signal                                                                                                                                                                          |                                      | 23    |     | nV/√Hz  |

| Large-Signal Output Noise                  | 20dB of gain, VG+ - VG- = -0.85V, f <sub>RF</sub> = 5MHz,<br>f <sub>NOISE</sub> = f <sub>RF</sub> + 1kHz, V <sub>OUT</sub> = 1V <sub>P-P</sub> differential                                                                |                                      | 35    |     | nV/√Hz  |

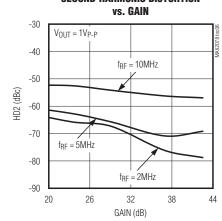

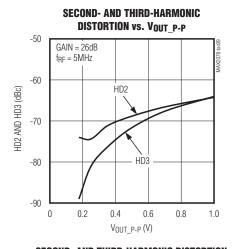

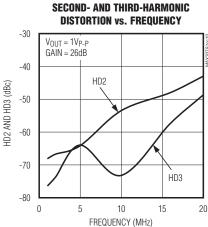

| Second Harmonic (HD2)                      | $V_{IN} = 50 \text{mV}_{P-P}, f_{RF} = 2 \text{MHz}, V_{OUT} = 1 \text{V}_{P-P}$                                                                                                                                           |                                      | -67   |     | dBc     |

| Second Harmonic (FID2)                     | $V_{IN} = 50 \text{mV}_{P-P}, f_{RF} = 5 \text{MHz}, V_{OUT} = 1 \text{V}_{P-P}$                                                                                                                                           |                                      | -64.2 |     | UDC     |

| High-Gain IM3 Distortion                   | $V_{IN} = 50 \text{mV}_{P-P}, f_{RF1} = 5 \text{MHz}, f_{RF2} = 5.01 \text{MHz}, \\ V_{OUT} = 1 \text{V}_{P-P} \text{ (Note 8)}$                                                                                           | -52                                  | -61   |     | dBc     |

| Low-Gain IM3 Distortion                    | D43/D42/D41/D40 = 0/0/0/1 (R <sub>IN</sub> = 200 $\Omega$ , LNA gain = 12.5dB),V <sub>IN</sub> = 100mV <sub>P-P</sub> , f <sub>RF1</sub> = 5MHz, f <sub>RF2</sub> = 5.01MHz, V <sub>OUT</sub> = 1V <sub>P-P</sub> (Note 8) | -50                                  | -60   |     | dBc     |

| Standby Mode Power-Up<br>Response Time     | Gain set for 26dB, $f_{RF}$ = 5MHz, $V_{OUT}$ = 1 $V_{P-P}$ , settled with in 1dB from transition on NP pin                                                                                                                |                                      | 2.1   |     | μs      |

| Standby Mode Power-Down<br>Response Time   | To reach DC current target ±10%                                                                                                                                                                                            |                                      | 2.0   |     | μs      |

| Power-Up Response Time                     | Gain set for 28dB, $f_{RF}$ = 5MHz, $V_{OUT}$ = 1 $V_{P-P}$ , settled within 1dB from transition on PD                                                                                                                     | JT = 1V <sub>P-P</sub> , settled 2.7 |       |     | ms      |

| Power-Down Response Time                   | Gain set for 28dB, f <sub>RF</sub> = 5MHz, DC power reaches 6mW/channel, from transition on PD                                                                                                                             |                                      | 5     |     | ns      |

| Adjacent Channel Crosstalk                 | V <sub>OUT</sub> = 1V <sub>P-P</sub> differential, f <sub>RF</sub> = 10MHz, 28dB of gain                                                                                                                                   |                                      | -58   | -   | dBc     |

| Nonadjacent Channel Crosstalk              | V <sub>OUT</sub> = 1V <sub>P-P</sub> differential, f <sub>RF</sub> = 10MHz, 28dB of gain                                                                                                                                   |                                      | -71   |     | dBc     |

| Phase Matching Between Channels            | Gain = 28dB, VG+ - VG- = 0.4V, $V_{OUT}$ = 1 $V_{P-P}$ , $f_{RF}$ = 10MHz                                                                                                                                                  |                                      | ±1.2  |     | Degrees |

### AC ELECTRICAL CHARACTERISTICS—VGA MODE (continued)

(Typical Application Circuit,  $V_{REF}=2.475V$  to 2.525V,  $V_{CC}1=3.13V$  to 3.47V,  $V_{CC}2=4.5V$  to 5.25V,  $T_{A}=0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND}=0V$ , V/C=1, NP=0, PD=0, PD=0

| PARAMETER                                          | CONDITIONS                                                                                                                                                                                                              | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| 3V Supply Modulation Ratio                         | Gain = 28dB, VG+ - VG- = 0.4V, V <sub>OUT</sub> = 1V <sub>P-P</sub> , f <sub>RF</sub> = 5MHz, f <sub>MOD</sub> = 1kHz, V <sub>MOD</sub> = 50mV <sub>P-P</sub> , ratio of output sideband at 5.001MHz, 1V <sub>P-P</sub> | -73 |     | dBc |       |

| 4.75V/5V Supply Modulation<br>Ratio                | Gain = 28dB, VG+ - VG- = 0.4V, V <sub>OUT</sub> = 1V <sub>P-P</sub> , f <sub>RF</sub> = 5MHz, f <sub>MOD</sub> = 1kHz, V <sub>MOD</sub> = 50mV <sub>P-P</sub> , ratio of output sideband at 5.001MHz, 1V <sub>P-P</sub> | -82 |     | dBc |       |

| Gain Control Lines Common-<br>Mode Rejection Ratio | Gain = 28dB, VG+ - VG- = 0.4V, f <sub>MOD</sub> = 5MHz,<br>V <sub>MOD</sub> = 50mV <sub>P-P</sub> , V <sub>OUT</sub> = 1.0V <sub>P-P</sub>                                                                              |     | -74 |     | dBc   |

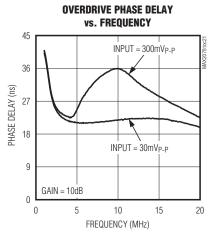

| Overdrive Phase Delay                              | VG+ - VG- = -3V, delay between $V_{IN}$ = 300mVp-p and $V_{IN}$ = 30mVp-p differential                                                                                                                                  | 5   |     | ns  |       |

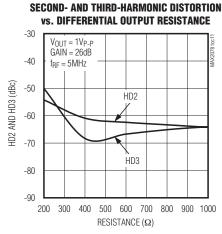

| Output Impedance                                   | Differential                                                                                                                                                                                                            |     | 100 |     | Ω     |

#### AC ELECTRICAL CHARACTERISTICS—CW MODE

(Typical Application Circuit, V/C = 0, PD = 0, NP = 0, CLP = 0, D43/D42/D41/D40 = 1/0/1/0 (R<sub>IN</sub> =  $200\Omega$ , LNA gain = 18.5dB), f<sub>RF</sub> = 1/0/16 = 5MHz, R<sub>S</sub> =  $200\Omega$ , Cl\_, CQ\_ pulled up to 11V through four separate 0.1%  $162\Omega$  resistors, the rise/fall time of the LVDS clock driving the LO\_ is required to be 0.5ns, reference noise less than 10nV/ $\sqrt{\text{Hz}}$  from 1kHz to 20MHz (Note 9). Typical values are at V<sub>CC</sub>1 = 3.3V, V<sub>CC</sub>2 = 4.75V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                  | CONDITIONS                                                                                       |     | TYP    | MAX | UNITS  |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------|-----|--------|-----|--------|--|--|--|--|

| CW DOPPLER MIXER                           |                                                                                                  |     |        |     |        |  |  |  |  |

| Mixer RF Frequency Range                   |                                                                                                  | 0.9 |        | 7.6 | MHz    |  |  |  |  |

| LO Frequency Range                         | LO+ and LO-                                                                                      | 16  |        | 120 | MHz    |  |  |  |  |

| Mixer Output Frequency Range               |                                                                                                  | DC  |        | 100 | kHz    |  |  |  |  |

| FULL-POWER MODE                            | FULL-POWER MODE                                                                                  |     |        |     |        |  |  |  |  |

| Noise Figure                               | No carrier                                                                                       |     | 3.4    |     | dB     |  |  |  |  |

| Noise Figure at 100mV <sub>P-P</sub> Input | $100 \text{mV}_{P-P}$ at input, $f_{RF} = f_{LO}/16 = 1.25 \text{MHz}$ , measured at 1kHz offset |     | 3.6    |     | dB     |  |  |  |  |

| Noise Figure at 200mV <sub>P-P</sub> Input | $200 \text{mV}_{P-P}$ at input, $f_{RF} = f_{LO}/16 = 1.25 \text{MHz}$ , measured at 1kHz offset |     | 4.1    |     | dB     |  |  |  |  |

| SNR at 100mV <sub>P-P</sub> Input          | 100mV <sub>P-P</sub> at input, $f_{RF} = f_{LO}/16 = 1.25$ MHz, measured at 1kHz offset          |     | -148.3 |     | dBc/Hz |  |  |  |  |

| SNR at 200mV <sub>P-P</sub> Input          | 200mV <sub>P-P</sub> at input, $f_{RF} = f_{LO}/16 = 1.25$ MHz, measured at 1kHz offset          |     | -153.8 |     | dBc/Hz |  |  |  |  |

### AC ELECTRICAL CHARACTERISTICS—CW MODE (continued)

(Typical Application Circuit, V/C = 0, PD = 0, NP = 0, CLP = 0, D43/D42/D41/D40 = 1/0/1/0 (R<sub>IN</sub> = 200 $\Omega$ , LNA gain = 18.5dB), f<sub>RF</sub> = f<sub>LO</sub>/16 = 5MHz, R<sub>S</sub> = 200 $\Omega$ , Cl\_, CQ\_ pulled up to 11V through four separate 0.1% 162 $\Omega$  resistors, the rise/fall time of the LVDS clock driving the LO\_ is required to be 0.5ns, reference noise less than 10nV/ $\sqrt{\text{Hz}}$  from 1kHz to 20MHz (Note 9). Typical values are at V<sub>CC</sub>1 = 3.3V, V<sub>CC</sub>2 = 4.75V, TA = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                  | CONDITIONS                                                                                                               |                                            | MIN | TYP    | MAX | UNITS   |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|--------|-----|---------|

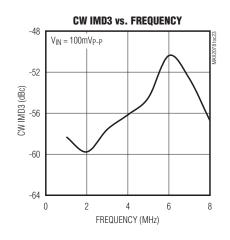

| Two-Tone Intermodulation IMD3 at 100mV     | $f_{RF1} = 5MHz$ , 0.1 $V_{P-P}$ , $f_{RF2} = 5.01M$<br>$f_{LO} = 80MHz$ (Note 8)                                        | Hz at -25dBc,                              | -50 | -55    |     | dBc     |

| Two-Tone Intermodulation IMD3 at 200mV     | $f_{RF1} = 5MHz$ , 0.2V <sub>P-P</sub> , $f_{RF2} = 5.01M$<br>$f_{LO} = 80MHz$ (Note 8)                                  | Hz at -25dBc,                              |     | -48.5  |     | dBc     |

| Mixer Output-Voltage<br>Compliance         | Valid voltage range (AC + DC) on significant                                                                             | ummed mixer output                         | 4.5 |        | 12  | V       |

| Channel-to-Channel Phase Matching          | Measured under zero beat condition fRF = 5MHz, fLO = 80MHz (Note 10)                                                     | ns, $V_{RF} = 100 \text{mV}_{P-P}$ ,       |     | ±0.4   |     | Degrees |

| Channel-to-Channel Gain<br>Matching        | Measured under zero beat condition fRF = 5MHz, fLO = 80MHz (Notes 10                                                     |                                            |     | ±0.2   |     | dB      |

| Transconductance                           | Calculated from LNA input voltage and twice the I or Q current                                                           | $f_{RF} = 0.9MHz$ ,<br>$f_{LO}/16 = 1MHz$  | 19  | 23     | 26  | - mS    |

| Transconductance                           |                                                                                                                          | $f_{RF} = 7.6MHz,$<br>$f_{LO}/16 = 7.5MHz$ | 19  | 22.5   | 26  | 1112    |

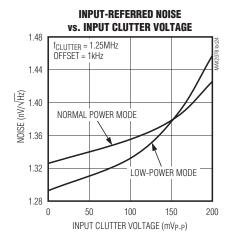

| LOW-POWER MODE (CLP = 1)                   |                                                                                                                          |                                            |     |        |     |         |

| Noise Figure                               | No carrier                                                                                                               | No carrier                                 |     |        |     | dB      |

| Noise Figure at 100mV <sub>P-P</sub> Input | $100 \text{mV}_{P-P}$ on input, $f_{RF} = f_{LO}/16 = 1$ at 1kHz offset                                                  | .25MHz, measured                           |     | 3.5    |     | dB      |

| Noise Figure at 200mV <sub>P-P</sub> Input | $200\text{mV}_{P-P}$ on input, $f_{RF} = f_{LO}/16 = 1$ at 1kHz offset                                                   | .25MHz, measured                           |     | 4.3    |     | dB      |

| SNR at 100mV <sub>P-P</sub> Input          | $100 \text{mV}_{P-P}$ on input, $f_{RF} = f_{LO}/16 = 1$ at $1 \text{kHz}$ offset                                        | .25MHz, measured                           |     | -148.2 |     | dBc/Hz  |

| SNR at 200mV <sub>P-P</sub> Input          | $200\text{mV}_{P-P}$ on input, $f_{RF} = f_{LO}/16 = 1$ at $1\text{kHz}$ offset                                          | .25MHz, measured                           |     | -153.6 |     | dBc/Hz  |

| Two-Tone Intermodulation IMD3              | f <sub>RF1</sub> = 5MHz, 0.1V <sub>P-P</sub> , f <sub>RF2</sub> = 5.01MHz at -25dBc,<br>f <sub>LO</sub> = 80MHz (Note 8) |                                            |     | -44    |     | dBc     |

| Mixer Output-Voltage Compliance            | Valid voltage range on summed mixer output pins (Note 12)                                                                |                                            | 4.5 |        | 12  | V       |

| Transportductors (Nets 40)                 | Calculated from LNA input voltage                                                                                        | $f_{RF} = 1.1MHz,$<br>$f_{LO}/16 = 1MHz$   | 19  | 21.5   | 26  | ~~°     |

| Transconductance (Note 13)                 | and twice the I or Q current                                                                                             | $f_{RF} = 7.6MHz,$<br>$f_{LO}/16 = 7.5MHz$ | 19  | 21.5   | 26  | - mS    |

#### AC ELECTRICAL CHARACTERISTICS—SERIAL PERIPHERAL INTERFACE

(DOUT loaded with 60pF and  $10M\Omega$ , 2ns rise and fall edges on CLK.)

| PARAMETER                             | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------------|-----------------|------------|-----|-----|-----|-------|

| Clock Speed                           |                 |            |     |     | 10  | MHz   |

| Mininimum Data-to-Clock Setup<br>Time | tcs             |            |     | 5   |     | ns    |

| Mininimum Data-to-Clock Hold Time     | tсн             |            |     | 0   |     | ns    |

| Mininimum Clock-to-CS Setup<br>Time   | tES             |            |     | 5   |     | ns    |

| CS Positive Mininimum Pulse Width     | t <sub>EW</sub> |            |     | 1   |     | ns    |

| Mininimum Clock Pulse Width           | tcw             |            |     | 2   |     | ns    |

| Mininimum CS High to Mixer Clock on   | tMIXCS          |            |     | 2   |     | ns    |

- Note 2: Minimum and maximum limits at T<sub>A</sub> = +25°C and +70°C are guaranteed by design, characterization, and/or production test.

- Note 3: Noise performance of the device is dependent on the noise contribution from V<sub>REF</sub>. Use a low-noise supply for V<sub>REF</sub>.

- Note 4: Note that the LVDS CWD LO clocks are DC-coupled. This is to ensure immediate synchronization when the clock is first turned on. An AC-coupled LO is problematic in that the RC time constant associated with the coupling capacitors and the input impedance of the pin causes a period of time (related to the RC time constant) when the DC level on the chip side of the capacitor is outside the acceptable common-mode range and the LO swing does not exceed both of the logic thresholds required for proper operation. This problem associated with AC-coupling causes an inability to ensure synchronization among beamforming channels. The LVDS signal is terminated differentially with an external 100Ω resistor on the board.

- **Note 5:** An external  $100\Omega$  resistor terminates the LVDS differential signal path.

- Note 6: Total on-chip power dissipation is calculated as P<sub>DISS</sub> = V<sub>CC</sub>1 x I<sub>CC</sub>1 + V<sub>CC</sub>2 x I<sub>CC</sub>2 + V<sub>REF</sub> x I<sub>REF</sub> + [11V (I<sub>11V</sub>/4) x 162] x I<sub>11V</sub>.

- **Note 7:** This response time does not include the CW output highpass filter. When switching to VGA mode, the CW outputs stop drawing current and the output voltage goes to the rail. If a highpass filter is used, the recovery time may be excessive and a switching network is recommended, as shown in the *Applications Information* section.

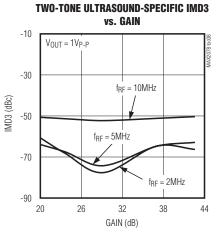

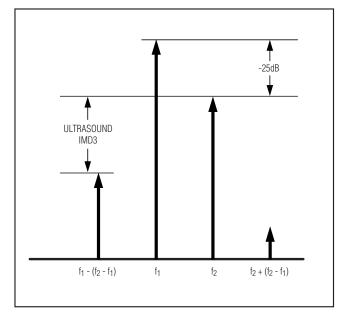

- Note 8: See the *Ultrasound-Specific IMD3 Specification* section.

- **Note 9:** The reference input noise is given for 8 channels, knowing that the reference-noise contributions are correlated in all 8 channels. If more channels are used, the reference noise must be reduced to get the best noise performance.

- **Note 10:** Channel-to-channel gain and phase matching measured on 30 pieces during engineering characterization at room temperature. Each mixer is used as a phase detector and produces a DC voltage in the IQ plane. The phase is given by the angle of the vector drawn on that plane. Multiple channels from multiple parts are compared to each other to produce the phase variation.

- **Note 11:** Voltage gain is measured by subtracting the output-voltage signal from the input-voltage signal. The output-voltage signal is obtained by taking the differential CW I output and summing it in quadrature with the differential CW Q output. The input voltage is defined as the differential voltage applied to the CW input pins.

- Note 12: Mixer output-voltage compliance is the range of acceptable voltages allowed on the CW mixer outputs.

- **Note 13:** Transconductance is defined as the quadrature-combined CW differential output current at baseband divided by the mixer's input voltage.

N/IXI/N/

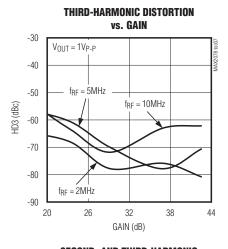

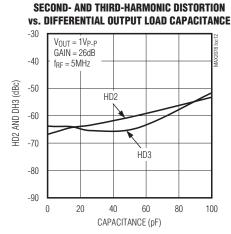

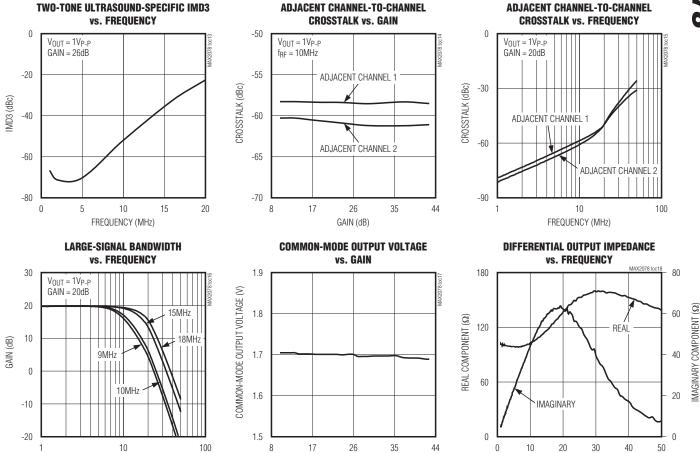

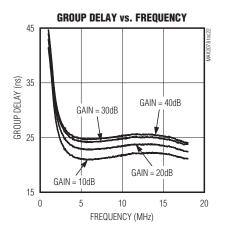

### **Typical Operating Characteristics**

(Typical Application Circuit,  $V_{REF}=2.475V$  to 2.525V,  $V_{CC}1=3.13V$  to 3.47V,  $V_{CC}2=4.5V$  to 5.25V,  $T_{A}=0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND}=0V$ , NP=0, PD=0, PD=0

### Typical Operating Characteristics (continued)

(Typical Application Circuit,  $V_{REF} = 2.475V$  to 2.525V,  $V_{CC}1 = 3.13V$  to 3.47V,  $V_{CC}2 = 4.5V$  to 5.25V,  $T_{A} = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ , NP = 0, PD =

### Typical Operating Characteristics (continued)

(Typical Application Circuit,  $V_{REF} = 2.475V$  to 2.525V,  $V_{CC}1 = 3.13V$  to 3.47V,  $V_{CC}2 = 4.5V$  to 5.25V,  $T_{A} = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ , NP = 0, PD =

GAIN (dB)

FREQUENCY (MHz)

FREQUENCY (MHz)

### Typical Operating Characteristics (continued)

(Typical Application Circuit,  $V_{REF} = 2.475V$  to 2.525V,  $V_{CC}1 = 3.13V$  to 3.47V,  $V_{CC}2 = 4.5V$  to 5.25V,  $T_{A} = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ , NP = 0, PD =

### **Pin Description**

| PIN               | NAME              | FUNCTION                                                                                                                                                                                                                                                                                           |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | IN2               | Channel 2 Input                                                                                                                                                                                                                                                                                    |

| 2                 | INC2              | Channel 2 Clamp Input. Connect to a coupling capacitor. See the <i>Typical Application Circuit</i> for details.                                                                                                                                                                                    |

| 3                 | ZF3               | Channel 3 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                                                                                                                                               |

| 4                 | IN3               | Channel 3 Input                                                                                                                                                                                                                                                                                    |

| 5                 | INC3              | Channel 3 Clamp Input. Connect to a coupling capacitor. See the <i>Typical Application Circuit</i> for details.                                                                                                                                                                                    |

| 6                 | ZF4               | Channel 4 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                                                                                                                                               |

| 7                 | IN4               | Channel 4 Input                                                                                                                                                                                                                                                                                    |

| 8                 | INC4              | Channel 4 Clamp Input. Connect to the input coupling capacitor. See the <i>Typical Application Circuit</i> for details.                                                                                                                                                                            |

| 9, 28, 31         | GND               | Ground                                                                                                                                                                                                                                                                                             |

| 10                | AG                | AC Ground. Connect a low-ESR 1µF capacitor to ground.                                                                                                                                                                                                                                              |

| 11                | ZF5               | Channel 5 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                                                                                                                                               |

| 12                | IN5               | Channel 5 Input                                                                                                                                                                                                                                                                                    |

| 13                | INC5              | Channel 5 Clamp Input. Connect to a coupling capacitor. See the <i>Typical Application Circuit</i> for details.                                                                                                                                                                                    |

| 14                | ZF6               | Channel 6 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                                                                                                                                               |

| 15                | IN6               | Channel 6 Input                                                                                                                                                                                                                                                                                    |

| 16                | INC6              | Channel 6 Clamp Input. Connect to a coupling capacitor. See the Typical Application Circuit for details.                                                                                                                                                                                           |

| 17                | ZF7               | Channel 7 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                                                                                                                                               |

| 18                | IN7               | Channel 7 Input                                                                                                                                                                                                                                                                                    |

| 19                | INC7              | Channel 7 Clamp Input. Connect to the input coupling capacitor. See the <i>Typical Application Circuit</i> for details.                                                                                                                                                                            |

| 20                | ZF8               | Channel 8 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                                                                                                                                               |

| 21                | IN8               | Channel 8 Input                                                                                                                                                                                                                                                                                    |

| 22                | INC8              | Channel 8 Clamp Input. Connect to a coupling capacitor. See the Typical Application Circuit for details.                                                                                                                                                                                           |

| 23, 33,<br>53, 64 | V <sub>CC</sub> 2 | 4.75V Power Supply. Connect to an external 4.75V power supply. Connect all 4.75V supply pins together externally and bypass with 100nF capacitors as close as possible to the pin.                                                                                                                 |

| 24                | V <sub>REF</sub>  | External 2.5V Reference Supply. Connect to a low-noise power supply. Bypass to GND with a 0.1µF capacitor as close as possible to the pins. Note that noise performance of the device is dependent on the noise contribution from V <sub>REF</sub> . Use a low-noise supply for V <sub>REF</sub> . |

| 25, 44, 63        | V <sub>CC</sub> 1 | 3.3V Power Supply. Connect to an external 3.3V power supply. Connect all 3.3V supply pins together externally and bypass with 100nF capacitors as close as possible to the pin.                                                                                                                    |

| 26                | VG+               | VGA Analog Gain Control Differential Input. Set the differential voltage to -3V for minimum gain and to                                                                                                                                                                                            |

| 27                | VG-               | +3V for maximum gain.                                                                                                                                                                                                                                                                              |

| 29                | CLP               | CW Low-Power Mode Select Input. Drive CLP high to place CW mixers in low-power mode.                                                                                                                                                                                                               |

| 30                | PD                | Power-Down Mode Select Input. Set PD to V <sub>CC</sub> 1 to place the entire device in power-down mode. Drive PD low for normal operation. This mode overrides the standby mode.                                                                                                                  |

| 32                | DOUT              | Serial Port Data Output. Data output for ease of daisy-chain programming. The level is 3.3V CMOS.                                                                                                                                                                                                  |

| 34                | OUT8-             | Channel 8 Negative Differential Output                                                                                                                                                                                                                                                             |

| 35                | OUT8+             | Channel 8 Positive Differential Output                                                                                                                                                                                                                                                             |

| 36                | OUT7-             | Channel 7 Negative Differential Output                                                                                                                                                                                                                                                             |

### Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37  | OUT7+ | Channel 7 Positive Differential Output                                                                                                                                            |

| 38  | OUT6- | Channel 6 Negative Differential Output                                                                                                                                            |

| 39  | OUT6+ | Channel 6 Positive Differential Output                                                                                                                                            |

| 40  | OUT5- | Channel 5 Negative Differential Output                                                                                                                                            |

| 41  | OUT5+ | Channel 5 Positive Differential Output                                                                                                                                            |

| 42  | LO-   | Differential Local Oscillator Input. LO is divided in the beamformer.                                                                                                             |

| 43  | LO+   | Differential Eocal Oscillator Input. Eo is divided in the beamformer.                                                                                                             |

| 45  | OUT4- | Channel 4 Negative Differential Output                                                                                                                                            |

| 46  | OUT4+ | Channel 4 Positive Differential Output                                                                                                                                            |

| 47  | OUT3- | Channel 3 Negative Differential Output                                                                                                                                            |

| 48  | OUT3+ | Channel 3 Positive Differential Output                                                                                                                                            |

| 49  | OUT2- | Channel 2 Negative Differential Output                                                                                                                                            |

| 50  | OUT2+ | Channel 2 Positive Differential Output                                                                                                                                            |

| 51  | OUT1- | Channel 1 Negative Differential Output                                                                                                                                            |

| 52  | OUT1+ | Channel 1 Positive Differential Output                                                                                                                                            |

| 54  | CLK   | Serial Port Clock Input (Positive Edge Triggered). 3.3V CMOS. Clock input for programming the serial shift registers.                                                             |

| 55  | DIN   | Serial Port Data Input. 3.3V CMOS. Data input to program the serial shift registers.                                                                                              |

| 56  | CS    | Serial Port Chip Select Input. 3.3V CMOS. Used to store programming bits in registers, as well as in CW mode, synchronizing all channel phases (on a rising edge).                |

| 57  | NP    | VGA Standby Mode Select Input. Set NP to 1 to place the entire device in standby mode. Overrides soft channel shutdown in serial shift register, but not general power-down (PD). |

| 58  | V/C   | VGA/CW Mode Select Input. Set V/C to a logic-high to enable the VGAs and disable CW mode. Set V/C to a logic-low to enable the CW mixers and disable the VGA mode.                |

| 59  | CQ-   | 8-Channel CW Negative Quadrature Output. Connect to an external 11V power supply with a $162\Omega$ external pullup resistor.                                                     |

| 60  | CQ+   | 8-Channel CW Positive Quadrature Output. Connect to an external 11V power supply with a $162\Omega$ external pullup resistor.                                                     |

| 61  | CI-   | 8-Channel CW Negative In-Phase Output. Connect to an external 11V power supply with a $162\Omega$ external pullup resistor.                                                       |

| 62  | CI+   | 8-Channel CW Positive In-Phase Output. Connect to an external 11V power supply with a $162\Omega$ external pullup resistor.                                                       |

| 65  | ZF1   | Channel 1 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                              |

| 66  | IN1   | Channel 1 Input                                                                                                                                                                   |

| 67  | INC1  | Channel 1 Clamp Input. Connect to the input coupling capacitor. See the <i>Typical Application Circuits</i> for details.                                                          |

| 68  | ZF2   | Channel 2 Active Impedance Matching Line. AC-couple to source with a 10nF capacitor.                                                                                              |

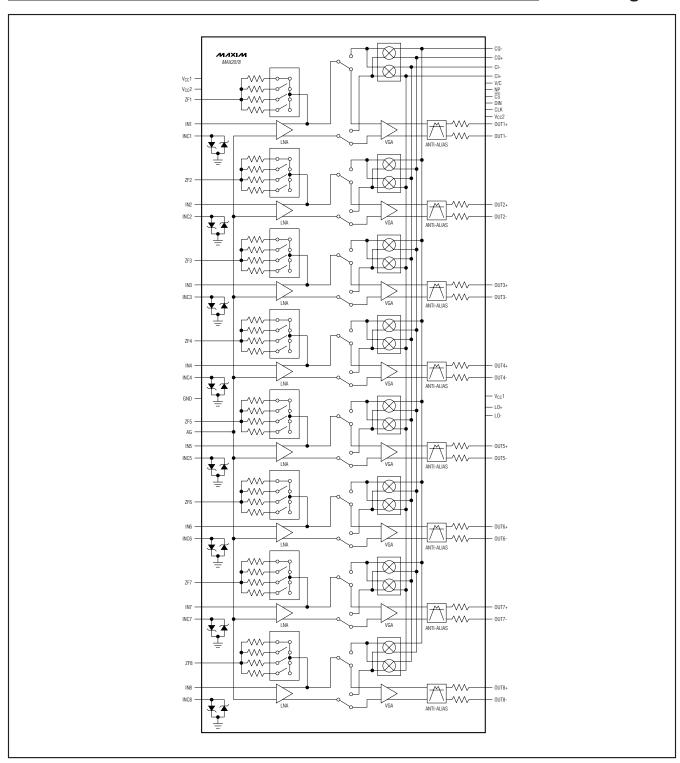

**Block Diagram**

### **Detailed Description**

The MAX2078 is a high-density, octal-channel ultrasound receiver optimized for low cost, high-channel count, high-performance portable and cart-based ultrasound applications. The integrated octal LNA, VGA, AAF, and programmable CWD beamformer offer a complete multi-specialty, ultrasound receiver solution.

Imaging path dynamic range has been optimized for exceptional second-harmonic performance. The complete imaging receive channel exhibits an exceptional 68dBFS\*\* SNR at 5MHz. The bipolar front-end has also been optimized for exceptionally low near-carrier modulation noise for exceptional low-velocity pulsed and color-flow Doppler sensitivity under high-clutter conditions, achieving an impressive near-carrier SNR of 140dBc/Hz at 1kHz offset from a VOUT = 1VP-P, 5MHz clutter signal.

The MAX2078 also integrates an octal quadrature mixer array and programmable LO phase generators for a complete continuous-wave Doppler (CWD) beamforming solution. Separate mixers for each channel are available for optimal CWD sensitivity, yielding an impressive SNR of 154dBc/Hz at 1kHz offset from a 200mVP-P, 1.25MHz input signal. The LO phase selection for each channel is programmed using a digital serial interface and a single high-frequency clock. The serial interface is designed to allow multiple devices to be easily daisy-chained to minimize program interface wiring. The outputs of the mixers are summed into single I and Q differential current outputs.

#### **Modes of Operation**

The MAX2078 requires programming before it can be used. The operating modes are controlled by 47 programming bits. Tables 1 and 2 show the functions of these programming bits.

**Table 1. Summary of Programming Bits**

| BIT NAME      | DESCRIPTION                                  |

|---------------|----------------------------------------------|

| D40, D41, D42 | Input impedance programming                  |

| D43           | LNA gain (D43 = 0 is low gain)               |

| D44, D45      | Anti-alias filter f <sub>C</sub> programming |

| D46           | Don't care                                   |

| D0-D39        | Beamformer programming, from channel 1 to 8  |

**Table 2. Logic Functions of Programming Bits**

| D46 | D45 | D44 | D43 | D42 | D41 | D40 | MODE                                     |

|-----|-----|-----|-----|-----|-----|-----|------------------------------------------|

| Χ   | Х   | Х   | 1   | 0   | 0   | 0   | $R_{IN} = 50\Omega$ , LNA gain = 18.5dB  |

| Χ   | Х   | Х   | 1   | 0   | 0   | 1   | $R_{IN} = 100\Omega$                     |

| Χ   | X   | Х   | 1   | 0   | 1   | 0   | $R_{IN} = 200\Omega$                     |

| Χ   | Х   | Х   | 1   | 0   | 1   | 1   | $R_{IN} = 1000\Omega$                    |

| Χ   | Х   | Х   | 0   | 0   | 0   | 0   | $R_{IN} = 100\Omega$ , LNA gain = 12.5dB |

| Χ   | X   | X   | 0   | 0   | 0   | 1   | $R_{IN} = 200\Omega$                     |

| Χ   | Х   | X   | 0   | 0   | 1   | 0   | $R_{IN} = 400\Omega$                     |

| Χ   | Х   | Х   | 0   | 0   | 1   | 1   | $R_{IN} = 2000\Omega$                    |

| Χ   | Х   | Χ   | 1   | 1   | Х   | Х   | Open feedback                            |

| Χ   | 0   | 0   | Х   | Х   | Χ   | Χ   | $f_C = 9MHz$                             |

| Χ   | 0   | 1   | Х   | Х   | Х   | Х   | $f_C = 10MHz$                            |

| Χ   | 1   | 0   | Х   | Х   | Х   | Х   | $f_C = 15MHz$                            |

| Х   | 1   | 1   | Х   | Х   | Х   | Х   | $f_C = 18MHz$                            |

X = Don't care.

<sup>\*\*</sup>When coupled with the MAX1437B ADC.

#### Low-Noise Amplifier (LNA)

The MAX2078's LNA is optimized for excellent dynamic range and linearity performance characteristics, making it ideal for ultrasound imaging applications. When the LNA is placed in low-gain mode, the input resistance (R<sub>IN</sub>), being a function of the gain A (R<sub>IN</sub> = R<sub>F</sub>/(1 + A)), increases by a factor of approximately 2. Consequently, the switches that control the feedback resistance (R<sub>F</sub>) have to be changed. For instance, the  $100\Omega$  mode in high gain becomes the  $200\Omega$  mode in low gain (see Table 2).

#### Variable-Gain Amplifier (VGA)

The MAX2078's VGAs are optimized for high linearity, high dynamic range, and low output-noise performance, all of which are critical parameters for ultrasound imaging applications. Each VGA path includes circuitry for adjusting analog gain, as well as an output buffer with differential output ports (OUT\_+, OUT\_-) for driving ADCs. See the High-Level CW Mixer and Programmable Beamformer Functional Diagram for details.

The VGA gain can be adjusted through the differential gain control input VG+ and VG-. Set the differential gain control input voltage at -3V for minimum gain and +3V for maximum gain. The differential analog control common-mode voltage is 1.65V (typ).

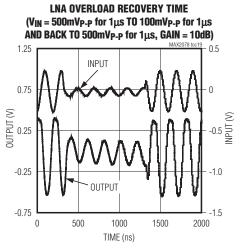

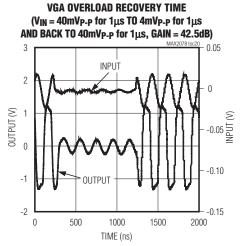

#### **Overload Recovery**

The device is also optimized for quick overload recovery for operation under the large input signal conditions that are typically found in ultrasound input buffer imaging applications. See the *Typical Operating Characteristics* for an illustration of the rapid recovery time from a transmit-related overload.

#### Octal Continuous-Wave (CW) Mixer

The MAX2078 CW mixers are designed using an active double-balanced topology. The mixers achieve high dynamic range and high linearity performance, with exceptionally low thermal and jitter noise, ideal for ultrasound CWD signal reception. The octal quadrature mixer array provides noise performance of 154dBc/Hz at 1kHz offset from a 1.25MHz, 200mVp-p input clutter signal and a two-tone third-order ultrasound-specific intermodulation product of -48.5dBc (typ). See the *Ultrasound-Specific IMD3 Specification* section.

The octal array exhibits quadrature and in-phase differential current outputs (CQ+, CQ-, CI+, CI-) to produce the total CWD beamformed signal. The maximum differential current output is typically 3mAp-p and the mixeroutput compliance voltage ranges from 4.5V to 12V.

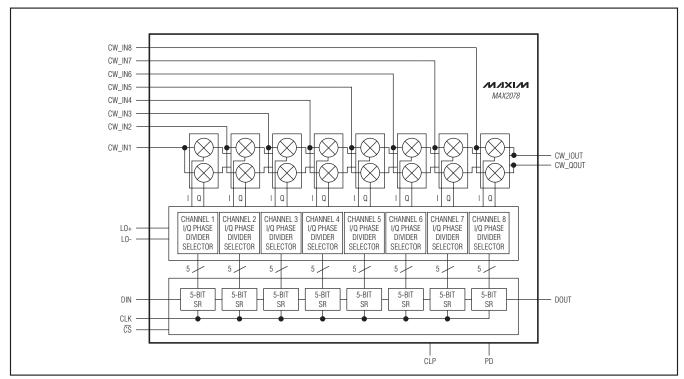

### \_High-Level CW Mixer and Programmable Beamformer Functional Diagram

MIXIM

Each mixer can be programmed to 1 of 16 phases; therefore, 4 bits are required for each channel for programming. Each CW channel can be programmed to an off state by setting bit Di to 1. The power-down mode (PD) line overrides this soft shutdown.

After the serial shift registers have been programmed, the  $\overline{\text{CS}}$  signal, when going high, loads the phase information in the form of 5 bits per channel into the I/Q phase divider/selectors. This presets the dividers, selecting the appropriate mixer phasing. See Table 3 for mixer phase configurations.

#### **CW Mixer Output Summation**

The outputs from the octal-channel mixer array are summed internally to produce the total CWD summed beamformed signal. The octal array produces eight differential quadrature (Q) outputs and eight differential in-phase (I) outputs. All quadrature and in-phase outputs are summed into single I and Q differential current outputs (CQ+, CQ-, CI+, CI-).

#### **LO Phase Select**

The LO phase dividers can be programmed through the shift registers to allow for 16 quadrature phases for a complete CW beamforming solution.

#### **Synchronization**

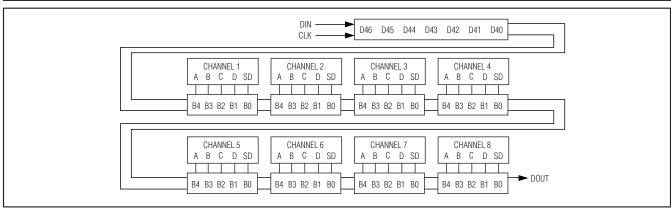

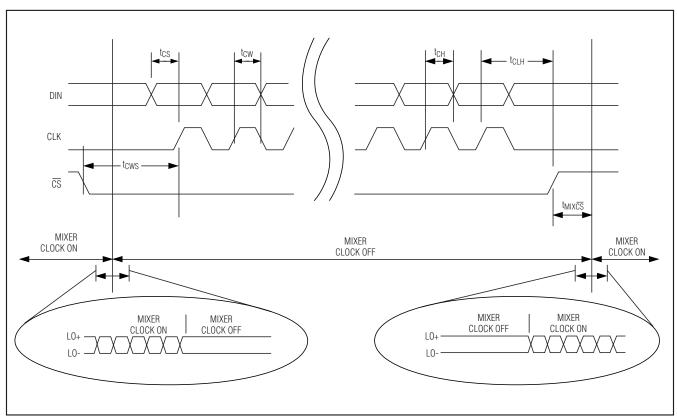

Figure 1 illustrates the serial programming of the eight individual channels through the serial data port. Note that the serial data can be daisy-chained from one part to another, allowing a single data line to be used to program multiple chips in the system.

**Table 3. Mixer Phase Configurations**

| PER CHANNEL    | MSB    |        |        | LSB    | SHUTDOWN |

|----------------|--------|--------|--------|--------|----------|

| PHASE (DEGREE) | Di + 4 | Di + 3 | Di + 2 | Di + 1 | Di       |

| 0              | 0      | 0      | 0      | 0      | 0/1      |

| 22.5           | 1      | 0      | 0      | 0      | 0/1      |

| 45             | 0      | 1      | 0      | 0      | 0/1      |

| 67.5           | 1      | 1      | 0      | 0      | 0/1      |

| 90             | 0      | 0      | 1      | 0      | 0/1      |

| 112.5          | 1      | 0      | 1      | 0      | 0/1      |

| 135            | 0      | 1      | 1      | 0      | 0/1      |

| 157.5          | 1      | 1      | 1      | 0      | 0/1      |

| 180            | 0      | 0      | 0      | 1      | 0/1      |

| 202.5          | 1      | 0      | 0      | 1      | 0/1      |

| 225            | 0      | 1      | 0      | 1      | 0/1      |

| 247.5          | 1      | 1      | 0      | 1      | 0/1      |

| 270            | 0      | 0      | 1      | 1      | 0/1      |

| 292.5          | 1      | 0      | 1      | 1      | 0/1      |

| 315            | 0      | 1      | 1      | 1      | 0/1      |

| 337.5          | 1      | 1      | 1      | 1      | 0/1      |

Figure 1. Data Flow of Serial Shift Register

#### **VGA and CW Mixer Operation**

During normal operation, the MAX2078 is configured so that either the VGA path is enabled while the mixer array is powered down (VGA mode), or the quadrature mixer array is enabled while the VGA path is powered down (CW mode). For VGA mode, set V/C to a logichigh and for CW mode, set V/C to a logic-low.

#### Power-Down and Low-Power Mode

The MAX2078 can also be powered down with PD. Set PD to V<sub>CC</sub>1 for power-down mode. In power-down mode, the device draws a total supply current less than 1µA. Set PD to logic-low for normal operation.

A low-power mode is available to lower the required power for CWD operation. When selected, the complex mixers operate at lower quiescent currents and the total per-channel current is lowered to 34.2mA. Note that operation in this mode slightly reduces the dynamic performance of the device. Table 4 shows the logic function of the standard operating modes.

### **Applications Information**

#### **Mode Select Response Time**

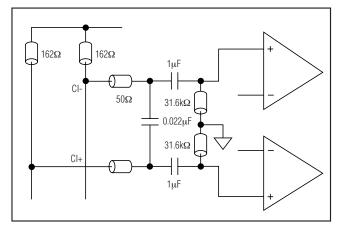

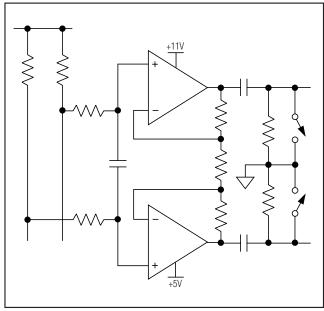

The mode select response time is the time that the device takes to switch between CW and VGA modes. Figure 2 depicts one possible approach to interfacing the CW outputs to an instrumentation amplifier, which is used to drive an ADC. In this implementation, there are four large-value (in the range of 470nF to 1µF) capacitors between each of the CQ+, CQ-, CI+, CI- outputs and the circuitry they are driving. The output of the CW

Figure 2. Typical Example of a CW Mixer's Output Circuit

mixer usually drives the input of an instrumentation amplifier made up of op amps whose input impedance is set by common-mode setting resistors.

There are clearly both a highpass corner and a lowpass corner present in this output network. The lowpass corner is set primarily by the  $162\Omega$  mixer pullup resistors, the series  $50\Omega$  resistors, and the shunt  $0.022\mu\text{F}$  capacitor. This lowpass corner is used to filter a combination of LO leakage and upper sideband. The highpass corner, however, is of a larger concern since it is dominated by the combination of a  $1\mu\text{F}$  DC-blocking capacitor and the pair of shunt  $31.6k\Omega$  resistors.

**Table 4. Logic Function of Standard Operating Modes**

| PD<br>INPUT | V/C | CLP | VGA | CW<br>MIXER | INTERNAL<br>SWITCH<br>TO VGA | INTERNAL<br>SWITCH<br>TO CW<br>MIXER | 3.3V V <sub>CC</sub><br>CURRENT<br>CONSUMPTION | 5V V <sub>CC</sub><br>CURRENT<br>CONSUMPTION | 11V V <sub>MIX</sub><br>CURRENT<br>CONSUMPTION |

|-------------|-----|-----|-----|-------------|------------------------------|--------------------------------------|------------------------------------------------|----------------------------------------------|------------------------------------------------|

| 1           | 1   | N/A | Off | Off         | Off                          | Off                                  | 0.3μΑ                                          | 0.4μΑ                                        | 0                                              |

| 1           | 0   | N/A | Off | Off         | Off                          | Off                                  | 0.1μΑ                                          | 0.6μΑ                                        | 0                                              |

| 0           | 0   | 0   | Off | On          | Off                          | On                                   | 3.2mA                                          | 248mA                                        | 90.4mA                                         |

| 0           | 0   | 1   | Off | On          | Off                          | On                                   | 3.2mA                                          | 216mA                                        | 54.4mA                                         |

| 0           | 1   | N/A | On  | Off         | On                           | Off                                  | 88mA                                           | 48mA                                         | 0                                              |

N/A = Not applicable.

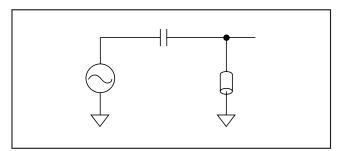

If drawn, the simplified dominant highpass network would look like Figure 3.

The highpass pole in this case is at fp =  $1/(2 \times pi \times RC) \sim 5$ Hz. Note that this low highpass corner frequency is required to filter the downconverted clutter tone, which appears at DC, but not interfere with CWD imaging at frequencies as low as 400Hz. For example, if one wanted to use CWD down to 400Hz, then a good choice for the highpass pole would be at least a decade below this (< 40Hz) as not to incur rolloff due to the pole. Remember, if the highpass pole is set to 400Hz, the response is 3dB down at that corner frequency. The placement of the highpass pole at 5Hz in the above example is between the DC and 40Hz limitations just discussed.

The bottom line is that any reasonably sized DC block between the output of the mixer and the instrumentation amplifier poses a significant time constant that slows the mode select switching speed.

An alternative solution to the approach in Figure 2, which enables faster mode select response time, is shown in Figure 4.

In Figure 4, the outputs of the CWD mixers are DC-coupled into the inputs of the instrumentation amplifiers. Therefore, the op amps must be able to accommodate the full compliance range of the mixer outputs, which is a maximum of 11V when the mixers are disabled, down to the 5V supply of the MAX2078 when the mixers are enabled. The op amps can be powered from 11V for the high rail and 5V for the low rail, requiring a 6V op amp.

#### Serial Interface

The MAX2078 is programmed using a serial shift register arrangement. This greatly simplifies the complexity of the program circuitry, reduces the number of IC pins necessary for programming, and reduces the PCB layout complexity. See Table 5 for the programming bit order. The data in (DIN) and data out (DOUT) can be daisy-chained from device to device and all front-ends can run off a single programming clock.

The data can be entered after  $\overline{\text{CS}}$  goes low. Once a whole word is entered,  $\overline{\text{CS}}$  needs to rise. When programming the part, enter LSB first and MSB last.

#### **Programming the Beamformer**

During the normal CWD mode, the mixer clock (LO+, LO-) is on and the programming signals (DIN, CLK,  $\overline{CS}$ ) are off ( $\overline{CS}$  = high, CLK = low, and DIN = don't care, but fixed to a high or a low). To start the programming sequence, turn off the mixer clock. Data is shifted into

Figure 3. Simplified Circuit of Highpass Pole

Figure 4. Improved Mode Select Response Time Achieved with DC-Coupled Input to Instrumentation Amplifier

the shift register at a recommended 10MHz programming rate or 100ns minimum data clock period/time. Assuming a 64-channel CWD receiver, this takes about 30ms for 5 bits per channel. See Figure 5 for timing details. After the shift registers are programmed, pulling  $\overline{CS}$  high loads the internal counters into I/Q phase divider/selectors with the proper values. The mixer clock needs to be off when this occurs or there may be timing issues between the load line timing and the mixer clock timing. The user turns on the mixer clock to start beamforming. The clock must turn on so that it starts at the beginning of a mixer clock cycle. A narrow glitch on the mixer clock is not acceptable and could cause metastability in the I/Q phase dividers.

**Table 5. Programming Bit Order**