## ANALOG DEVICES

# $\pm 15$ kV ESD Protected, EMC Compliant Slew Rate Limited, EIA RS-485 Transceiver

# ADM483E

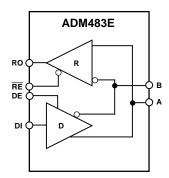

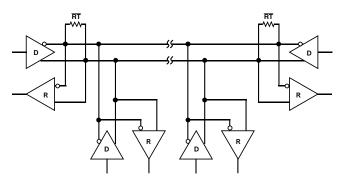

### FUNCTIONAL BLOCK DIAGRAM

Robust RS-485 Transceiver 15 kV ESD Protection Using HBM 2 kV EFT Protection Meets IEC1000-4-4 High EM Immunity Meets IEC1000-4-3 Reduced Slew Rate for Low EM Interference 250 kbps Data Rate Single +5 V  $\pm$  10% Supply -7 V to +12 V Bus Common-Mode Range 12 k $\Omega$  Input Impedance Short Circuit Protection Excellent Noise Immunity 36  $\mu$ A Supply Current 0.1  $\mu$ A Shutdown Current

#### **APPLICATIONS**

**FEATURES**

Low Power RS-485 Systems Electrically Harsh Environments EMI Sensitive Applications DTE-DCE Interface Packet Switching Local Area Networks

#### **GENERAL DESCRIPTION**

The ADM483E is a robust, low power differential line transceiver suitable for communication on multipoint bus transmission lines. Internal protection against electrostatic discharge (ESD), electrical fast transient (EFT) and electromagnetic immunity (EMI) allows operation in electrically harsh environments. ESD protection on the I-O lines meets  $\pm 15$  kV when tested using the Human Body Model. EFT protection meets  $\pm 2$  kV in accordance with IEC1000-4-4, while EMI immunity is in excess of 10 V/m meeting IEC1000-4-3.

The level of unwanted emissions is also carefully controlled using slew limiting on the driver outputs. This reduces reflections with improperly terminated cables and also minimizes electromagnetic interference. The controlled slew rate limits the data rate to 250 kbps.

The ADM483E is intended for balanced data transmission and complies with both EIA Standards RS-485 and RS-422. It contains a differential line driver and a differential line receiver and is suitable for half duplex data transmission, as the driver and receiver share the same differential pins. The input impedance on the ADM483E is 12 k $\Omega$ , allowing up to 32 transceivers on the bus.

The ADM483E operates from a single +5 V  $\pm$  10% power supply. Excessive power dissipation caused by bus contention or by output shorting is prevented by a thermal shutdown circuit. This feature forces the driver output into a high impedance state if, during fault conditions, a significant temperature increase is detected in the internal driver circuitry.

The receiver contains a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating).

The ADM483E is fabricated on BiCMOS, an advanced mixed technology process combining low power CMOS with robust bipolar technology.

It is fully specified over the industrial temperature range and is available in 8-lead DIP and SOIC packages.

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 World Wide Web Site: http://www.analog.com Fax: 617/326-8703 © Analog Devices, Inc., 1997

# $\label{eq:ADM483E} ADM483E \mbox{--} SPECIFICATIONS (V_{CC} = +5 \ V \ \pm \ 10\%. \ All \ specifications \ T_{MIN} \ to \ T_{MAX} \ unless \ otherwise \ noted)$

| Parameter                                                     | Min  | Тур     | Max  | Units     | Test Conditions/Comments                                     |

|---------------------------------------------------------------|------|---------|------|-----------|--------------------------------------------------------------|

| DRIVER                                                        |      |         |      |           |                                                              |

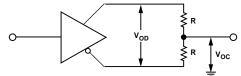

| Differential Output Voltage, V <sub>OD</sub>                  |      |         | 5.0  | V         | $V_{CC} = 5.25 \text{ V}. \text{ R} = \infty$ , Figure 1     |

|                                                               | 2.0  |         | 5.0  | V         | $R = 50 \Omega$ (RS-422), Figure 1                           |

|                                                               | 1.5  |         | 5.0  | V         | $R = 27 \Omega$ (RS-485), Figure 1                           |

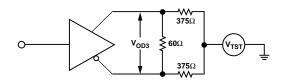

|                                                               | 1.5  |         | 5.0  | V         | $V_{TST} = -7$ V to +12 V, Figure 2, $V_{CC} \ge 4.75$ V     |

| $\Delta  V_{OD} $ for Complementary Output States             |      |         | 0.2  | V         | $R = 27 \Omega \text{ or } 50 \Omega$ , Figure 1             |

| Common-Mode Output Voltage $V_{OC}$                           |      |         | 3    | v         | $R = 27 \Omega \text{ or } 50 \Omega$ , Figure 1             |

| $\Delta  V_{OC} $ for Complementary Output States             |      |         | 0.2  | v         | $R = 27 \Omega \text{ or } 50 \Omega$                        |

| Output Short Circuit Current ( $V_{OUT}$ = High)              |      |         | 250  | мA        | $-7 V \le V_0 \le +12 V$                                     |

| Output Short Circuit Current ( $V_{OUT}$ = Low)               |      |         | 250  | mA        | $-7 V \le V_0 \le +12 V$                                     |

| CMOS Input Logic Threshold Low, $V_{INI}$                     |      | 1.4     | 0.8  | V         |                                                              |

| CMOS Input Logic Threshold High, V <sub>INL</sub>             | 2.0  | 1.4     | 0.0  | v         |                                                              |

| Logic Input Current (DE, DI)                                  | 2.0  | 1.7     | ±1.0 | μA        |                                                              |

| RECEIVER                                                      |      |         |      | •         |                                                              |

| Differential Input Threshold Voltage, V <sub>TH</sub>         | -0.2 |         | +0.2 | V         | $-7 \text{ V} \le \text{V}_{\text{CM}} \le +12 \text{ V}$    |

| Input Voltage Hysteresis, $\Delta V_{TH}$                     | -0.2 | 70      | ±0.2 | v<br>mV   | $ V_{CM} = 0 V $                                             |

| Input Voltage Hysteresis, $\Delta v_{TH}$<br>Input Resistance | 12   | 70      |      | hiv<br>kΩ | $V_{CM} = 0$ V<br>-7 V $\leq V_{CM} \leq +12$ V              |

| Input Current (A, B)                                          | 12   |         | +1   | mA        | $ V_{\rm IN}  = 12 \text{ V}$                                |

| Input Current (A, B)                                          | 0.0  |         | Τ1   |           |                                                              |

| $\mathbf{L}_{\mathbf{r}}$                                     | -0.8 |         | . 1  | mA        | $V_{IN} = -7 V$                                              |

| Logic Enable Input Current (RE)                               |      |         | ±1   | μA        |                                                              |

| CMOS Output Voltage Low, V <sub>OL</sub>                      | 1.0  |         | 0.4  | V         | $I_{OUT} = +4.0 \text{ mA}$                                  |

| CMOS Output Voltage High, V <sub>OH</sub>                     | 4.0  |         | 05   | V .       | $I_{OUT} = -4.0 \text{ mA}$                                  |

| Short Circuit Output Current                                  | 7    |         | 85   | mA        | $V_{OUT} = GND \text{ or } V_{CC}$                           |

| Three-State Output Leakage Current                            |      |         | ±1.0 | μA        | $0.4 \text{ V} \le \text{V}_{\text{OUT}} \le +2.4 \text{ V}$ |

| POWER SUPPLY CURRENT                                          |      |         |      |           | Outputs Unloaded, Receivers Enabled                          |

| I <sub>CC</sub> (ADM483E)                                     |      | 36      | 60   | μA        | $DE = 0 V (Disabled) \overline{RE} = 0 V$                    |

|                                                               |      | 270     | 360  | μA        | $DE = 5 V (Enabled) = \overline{RE} = 0 V$                   |

| Supply Current in Shutdown                                    |      | 0.1     | 10   | μA        | $DE = 0 V, \overline{RE} = V_{CC}$                           |

| ESD/EFT IMMUNITY                                              |      |         |      |           |                                                              |

| ESD Protection                                                |      | ±15     |      | kV        | HBM Air Discharge. A, B Pins                                 |

|                                                               |      | ±3.5    |      | kV        | HBM 3015.7 Contact Discharge. All Pins                       |

| EFT Protection                                                |      | $\pm 2$ |      | kV        | IEC1000-4-4, A, B Pins                                       |

| EMI Immunity                                                  |      | 10      |      | V/m       | IEC1000-4-3                                                  |

Specifications subject to change without notice.

### TIMING SPECIFICATIONS ( $V_{CC} = +5 V \pm 10\%$ . All specifications $T_{MIN}$ to $T_{MAX}$ unless otherwise noted.)

| Parameter                                                             | Min | Тур | Max  | Units | Test Conditions/Comments                                                          |

|-----------------------------------------------------------------------|-----|-----|------|-------|-----------------------------------------------------------------------------------|

| DRIVER                                                                |     |     |      |       |                                                                                   |

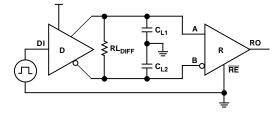

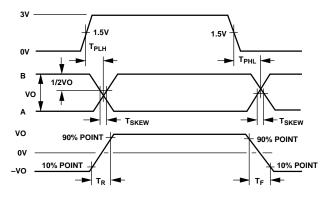

| Propagation Delay Input to Output T <sub>PLH</sub> , T <sub>PHL</sub> | 250 |     | 2000 | ns    | $R_L$ Diff = 54 $\Omega$ C <sub>L1</sub> = C <sub>L2</sub> = 100 pF, Figure 5     |

| Driver O/P to $\overline{O/P}$ T <sub>SKEW</sub>                      |     | 100 | 800  | ns    | $R_L \text{ Diff} = 54 \Omega C_{L1} = C_{L2} = 100 \text{ pF}, \text{ Figure 5}$ |

| Driver Rise/Fall Time T <sub>R</sub> , T <sub>F</sub>                 | 250 |     | 2000 | ns    | $R_L$ Diff = 54 $\Omega$ C <sub>L1</sub> = C <sub>L2</sub> = 100 pF, Figure 5     |

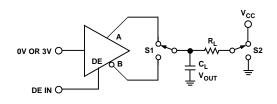

| Driver Enable to Output Valid                                         | 250 |     | 2000 | ns    | $R_L = 500 \Omega, C_L = 100 pF$ , Figure 3                                       |

| Driver Disable Timing                                                 | 300 |     | 3000 | ns    | $R_L = 500 \Omega$ , $C_L = 15 pF$ , Figure 3                                     |

| RECEIVER                                                              |     |     |      |       |                                                                                   |

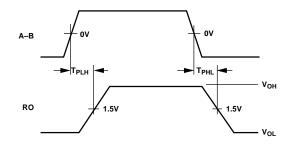

| Propagation Delay Input to Output T <sub>PLH</sub> , T <sub>PHL</sub> | 250 |     | 2000 | ns    | $C_L = 15 \text{ pF}$ , Figure 5                                                  |

| Skew  T <sub>PLH</sub> -T <sub>PHL</sub>                              |     | 200 |      | ns    |                                                                                   |

| Receiver Enable T <sub>EN1</sub>                                      |     | 10  | 50   | ns    | $R_L = 1 \text{ k}\Omega, C_L = 15 \text{ pF}, \text{ Figure } 4$                 |

| Receiver Disable T <sub>EN2</sub>                                     |     | 10  | 50   | ns    | $R_L = 1 k\Omega$ , $C_L = 15 pF$ , Figure 4                                      |

| SHUTDOWN                                                              |     |     |      |       |                                                                                   |

| Time to Shutdown                                                      | 50  | 200 | 600  | ns    |                                                                                   |

| Driver Enable from Shutdown                                           |     |     | 2000 | ns    | $R_L = 500 \Omega, C_L = 100 pF, Figure 3$                                        |

| Receiver Enable from Shutdown                                         |     |     | 2500 | ns    | $R_L = 1 k\Omega, C_L = 15 pF$ , Figure 4                                         |

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS\*

| $(T_A = +25^{\circ}C \text{ unless otherwise noted})$                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{CC}$ +7 V                                                                                                                               |

| Inputs                                                                                                                                      |

| Driver Input (DI) $\dots \dots \dots$       |

| Control Inputs (DE, RE) $\dots \dots \dots$ |

| Receiver Inputs (A, B)14 V to +14 V                                                                                                         |

| Outputs                                                                                                                                     |

| Driver Outputs                                                                                                                              |

| Receiver Output $\dots \dots \dots$         |

| ESD Rating: Air (Human Body Model) (A, B Pins) ±15 kV                                                                                       |

| ESD Rating: Contact (Human Body Model)                                                                                                      |

| (A, B Pins) $\pm 8 \text{ kV}$                                                                                                              |

| ESD Rating MIL-STD-883B Method 3015                                                                                                         |

| (Except A, B) ±3.5 kV                                                                                                                       |

| EFT Rating (IEC1000-4-4) (A, B Pins) ±2 kV                                                                                                  |

| EMI Immunity (IEC1000-4-3) 10 V/m                                                                                                           |

| Power Dissipation 8-Pin DIP 727 mW                                                                                                          |

| $\theta_{JA}$ , Thermal Impedance                                                                                                           |

| Power Dissipation 8-Pin SOIC 470 mW                                                                                                         |

| $\theta_{JA}$ , Thermal Impedance                                                                                                           |

| Operating Temperature Range                                                                                                                 |

| Industrial (A Version)                                                                                                                      |

| Storage Temperature Range –65°C to +150°C                                                                                                   |

| Lead Temperature (Soldering, 10 sec) +300°C                                                                                                 |

| Vapor Phase (60 sec) +215°C                                                                                                                 |

| Infrared (15 sec) +220°C                                                                                                                    |

|                                                                                                                                             |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **ORDERING GUIDE**

| Model     | Temperature Range | Package Option |

|-----------|-------------------|----------------|

| ADM483EAN | -40°C to +85°C    | N-8            |

| ADM483EAR | -40°C to +85°C    | SO-8           |

### PIN FUNCTION DESCRIPTION

| Pin | Mnemonic        | Function                                                                                                                                    |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RO              | Receiver Output. When enabled if A > B by<br>200 mV, then RO = High. If A < B by<br>200 mV, then RO = Low.                                  |

| 2   | RE              | Receiver Output Enable. A low level enables<br>the receiver output, RO. A high level places it<br>in a high impedance state.                |

| 3   | DE              | Driver Output Enable. A high level enables<br>the driver differential outputs, A and B. A<br>low level places it in a high impedance state. |

| 4   | DI              | Driver Input. When the driver is enabled a logic Low on DI forces A low and B high while a logic High on DI forces A high and B low.        |

| 5   | GND             | Ground Connection, 0 V.                                                                                                                     |

| 6   | А               | Noninverting Receiver Input A/Driver<br>Output A.                                                                                           |

| 7   | В               | Inverting Receiver Input B/Driver Output B.                                                                                                 |

| 8   | V <sub>CC</sub> | Power Supply, 5 V $\pm$ 10%.                                                                                                                |

#### **PIN CONFIGURATION**

| RO 1 | •                          | 8 V <sub>CC</sub> |

|------|----------------------------|-------------------|

| RE 2 | ADM483E                    | 7 B               |

| DE 3 | TOP VIEW<br>(Not to Scale) | 6 A               |

| DI 4 |                            | 5 GND             |

|      |                            |                   |

### Table I. Selection Table

| Part No. | Duplex | Data Rate<br>kb/s | Low Power<br>Shutdown | Tx/Rx<br>Enable | Ι <sub>CC</sub><br>μΑ | No of Tx/Rx<br>On Bus | ESD<br>kV | EFT<br>kV | EMI<br>V/m |

|----------|--------|-------------------|-----------------------|-----------------|-----------------------|-----------------------|-----------|-----------|------------|

| ADM483E  | Half   | 250               | Yes                   | Yes             | 36                    | 32                    | ±15       | ±2        | 10         |

### **Test Circuits**

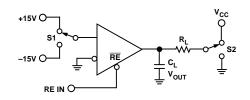

Figure 1. Driver Voltage Measurement Test Circuit

Figure 2. Driver Voltage Measurement Test Circuit 2

Figure 3. Driver Enable/Disable Test Circuit

Figure 4. Receiver Enable/Disable Test Circuit

Figure 5. Receiver Propagation Delay Test Circuit

### **Switching Characteristics**

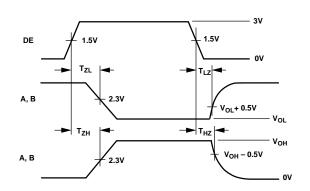

Figure 6. Driver Propagation Delay, Rise/Fall Timing

Figure 8. Receiver Propagation Delay

Figure 7. Driver Enable/Disable Timing

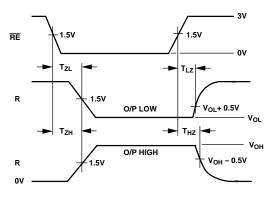

Figure 9. Receiver Enable/Disable Timing

### **Typical Performance Characteristics–ADM483E**

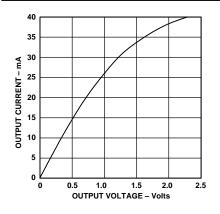

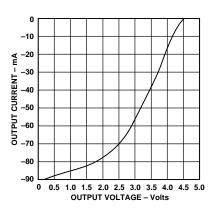

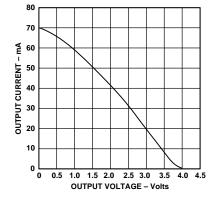

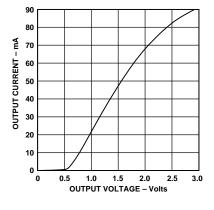

Figure 11. Receiver Output Low Voltage vs. Output Current

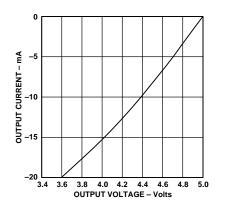

Figure 12. Receiver Output High Voltage vs. Output Current

Figure 14. Driver Output High Voltage vs. Output Current

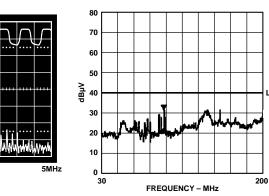

500kHz/DIV

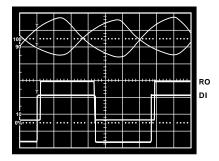

Figure 17. Driver Output Waveform

and FFT Plot Transmitting @ 150 kHz

*Figure 15. Driver Differential Output Voltage vs. Output Current*

LIMIT

Figure 13. Driver Output Low Voltage vs. Output Current

*Figure 16. ADM483E Driving 4000 ft. of Cable*

Figure 18. Radiated Emissions

Figure 19. Conducted Emissions

REV. 0

10dB/DIV

### **GENERAL INFORMATION**

The ADM483E is a ruggedized RS-485 transceiver that operates from a single +5 V supply.

It contains protection against radiated and conducted interference, including high levels of electrostatic discharge.

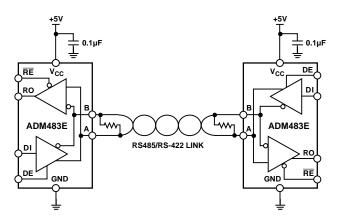

It is ideally suited for operation in electrically harsh environments or where cables may be plugged/unplugged. It is also immune to high RF field strengths without special shielding precautions. It is intended for balanced data transmission and complies with both EIA Standards RS-485 and RS-422. It contains a differential line driver and a differential line receiver, and is suitable for half duplex data transmission as the driver and receiver share the same differential pins.

The input impedance on the ADM483E is 12 k $\Omega$ , allowing up to 32 transceivers on the differential bus.

The ADM483E operates from a single +5 V  $\pm$  10% power supply. Excessive power dissipation caused by bus contention or by output shorting is prevented by a thermal shutdown circuit. This feature forces the driver output into a high impedance state if, during fault conditions, a significant temperature increase is detected in the internal driver circuitry.

The receiver contains a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating).

A high level of robustness is achieved using internal protection circuitry, eliminating the need for external protection components such as tranzorbs or surge suppressors.

Low electromagnetic emissions are achieved using slew limited drivers, minimizing interference both conducted and radiated.

The ADM483 can transmit at data rates up to 250 kbps.

A typical application for the ADM483E is illustrated in Figure 20. This shows a half-duplex link where data may be transferred at rates up to 250 kbps. A terminating resistor is shown at both ends of the link. This termination is not critical since the slew rate is controlled by the ADM483E and reflections are minimized.

The communications network may be extended to include multipoint connections as shown in Figure 30. Up to 32 transceivers may be connected to the bus.

Figure 20. Typical Half-Duplex Link Application

Tables II and III show the truth tables for transmitting and receiving.

Table II. Transmitting Truth Table

| Inputs |    |    | Outputs |      |

|--------|----|----|---------|------|

| RE     | DE | DI | В       | A    |

| Х      | 1  | 1  | 0       | 1    |

| Х      | 1  | 0  | 1       | 0    |

| 0      | 0  | X  | Hi-Z    | Hi-Z |

| 1      | 0  | X  | Hi-Z    | Hi-Z |

X = Don't Care.

Table III. Receiving Truth Table

| Inpu | ıts | Output                | 8    |

|------|-----|-----------------------|------|

| RE   | DE  | A-B                   | RO   |

| 0    | 0   | ≥ +0.2 V              | 1    |

| 0    | 0   | $\leq -0.2 \text{ V}$ | 0    |

| 0    | 0   | Inputs O/C            | 1    |

| 1    | 0   | X                     | Hi-Z |

X = Don't Care.

### **ESD/EFT TRANSIENT PROTECTION SCHEME**

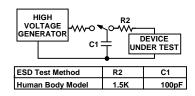

The ADM483E uses protective clamping structures on its inputs and outputs that clamp the voltage to a safe level and dissipates the energy present in ESD (Electrostatic) and EFT (Electrical Fast Transients) discharges.

The protection structure achieves ESD protection up to  $\pm 15$  kV according to the Human Body Model, and EFT protection up to  $\pm 2$  kV on all I-O lines.

### ESD TESTING

Two coupling methods are used for ESD testing, contact discharge and air-gap discharge. Contact discharge calls for a direct connection to the unit being tested. Air-gap discharge uses a higher test voltage but does not make direct contact with the unit under test. With air discharge, the discharge gun is moved toward the unit under test, developing an arc across the air gap, hence the term air-discharge. This method is influenced by humidity, temperature, barometric pressure, distance and rate of closure of the discharge gun. The contact-discharge method, while less realistic, is more repeatable and is gaining acceptance and preference over the air-gap method.

Although very little energy is contained within an ESD pulse, the extremely fast rise time, coupled with high voltages, can cause failures in unprotected semiconductors. Catastrophic destruction can occur immediately as a result of arcing or heating. Even if catastrophic failure does not occur immediately, the device may suffer from parametric degradation, which may result in degraded performance. The cumulative effects of continuous exposure can eventually lead to complete failure.

Figure 21. ESD Generator

I-O lines are particularly vulnerable to ESD damage. Simply touching or plugging in an I-O cable can result in a static discharge that can damage or completely destroy the interface product connected to the I-O port.

It is, therefore, extremely important to have high levels of ESD protection on the I-O lines.

It is possible that the ESD discharge could induce latchup in the device under test. It is therefore important that ESD testing on the I-O pins be carried out while device power is applied. This type of testing is more representative of a real world I-O discharge where the equipment is operating normally when the discharge occurs.

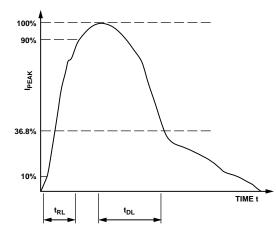

Figure 22. Human Body Model ESD Current Waveform

Table IV. ADM483E ESD Test Results

| ESD Test Method                                    | I-O Pins        | Other Pins |

|----------------------------------------------------|-----------------|------------|

| Human Body Model: Air<br>Human Body Model: Contact | ±15 kV<br>±8 kV | ±3.5 V     |

FAST TRANSIENT BURST IMMUNITY (IEC1000-4-4)

IEC1000-4-4 (previously 801-4) covers electrical fast-transient/ burst (EFT) immunity. Electrical fast transients occur as a result of arcing contacts in switches and relays. The tests simulate the interference generated when, for example, a power relay disconnects an inductive load. A spark is generated due to the well known back EMF effect. In fact, the spark consists of a burst of sparks as the relay contacts separate. The voltage appearing on the line, therefore, consists of a burst of extremely fast transient impulses. A similar effect occurs when switching on fluorescent lights.

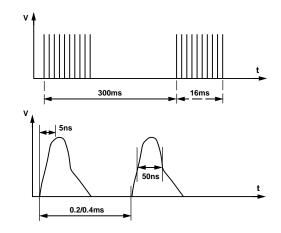

The fast transient burst test, defined in IEC1000-4-4, simulates this arcing and its waveform is illustrated in Figure 23. It consists of a burst of 2.5 kHz to 5 kHz transients repeating at 300 ms intervals. It is specified for both power and data lines.

Four severity levels are defined in terms of an open-circuit voltage as a function of installation environment. The installation environments are defined as

- 1. Well-protected

- 2. Protected

- 3. Typical Industrial

- 4. Severe Industrial

*Figure 23. IEC1000-4-4 Fast Transient Waveform* Table V shows the peak voltages for each of the environments.

| Table V. |                               |                               |  |  |  |

|----------|-------------------------------|-------------------------------|--|--|--|

| Level    | V <sub>PEAK</sub> (kV)<br>PSU | V <sub>PEAK</sub> (kV)<br>I-O |  |  |  |

| 1        | 0.5                           | 0.25                          |  |  |  |

| 2        | 1                             | 0.5                           |  |  |  |

| 3        | 2                             | 1                             |  |  |  |

| 4        | 4                             | 2                             |  |  |  |

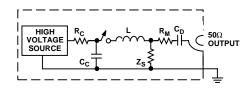

A simplified circuit diagram of the actual EFT generator is illustrated in Figure 24.

These transients are coupled onto the signal lines using an EFT coupling clamp. The clamp is 1 m long and completely surrounds the cable, providing maximum coupling capacitance (50 pF to 200 pF typ) between the clamp and the cable. High energy transients are capacitively coupled onto the signal lines. Fast rise times (5 ns) as specified by the standard result in very effective coupling. This test is very severe since high voltages are coupled onto the signal lines. The repetitive transients can often cause problems, where single pulses do not. Destructive latchup may be induced due to the high energy content of the transients. Note that this stress is applied while the interface products are powered up and are transmitting data. The EFT test applies hundreds of pulses with higher energy than ESD. Worst case transient current on an I-O line can be as high as 40 A.

Figure 24. EFT Generator

Test results are classified according to the following

- 1. Normal performance within specification limits.

- 2. Temporary degradation or loss of performance that is self-recoverable.

- 3. Temporary degradation or loss of function or performance that requires operator intervention or system reset.

- 4. Degradation or loss of function that is not recoverable due to damage.

The ADM483E has been tested under worst case conditions using unshielded cables, and meets Classification 2 at severity Level 4. Data transmission during the transient condition is corrupted, but it may be resumed immediately following the EFT event without user intervention.

### **RADIATED IMMUNITY (IEC1000-4-3)**

IEC1000-4-3 (previously IEC801-3) describes the measurement method and defines the levels of immunity to radiated electromagnetic fields. It was originally intended to simulate the electromagnetic fields generated by portable radio transceivers or any other device that generates continuous wave radiated electromagnetic energy. Its scope has since been broadened to include spurious EM energy, which can be radiated from fluorescent lights, thyristor drives, inductive loads, etc.

Testing for immunity involves irradiating the device with an EM field. There are various methods of achieving this including use of anechoic chamber, stripline cell, TEM cell and GTEM cell. These consist essentially of two parallel plates with an electric field developed between them. The device under test is placed between the plates and exposed to the electric field. There are three severity levels having field strengths ranging from 1 V to 10 V/m. Results are classified in a similar fashion to those for IEC1000-4-2.

- 1. Normal Operation.

- 2. Temporary Degradation or loss of function that is self-recoverable when the interfering signal is removed.

- 3. Temporary degradation or loss of function that requires operator intervention or system reset when the interfering signal is removed.

- 4. Degradation or loss of function that is not recoverable due to damage.

The ADM483E comfortably meets Classification 1 at the most stringent (Level 3) requirement. In fact, field strengths up to 30 V/m showed no performance degradation and error-free data transmission continued even during irradiation.

| Level<br>V/m | Field Strength |

|--------------|----------------|

| 1            | 1              |

| 2            | 3              |

| 3            | 10             |

### Table VI.

### **EMI EMISSIONS**

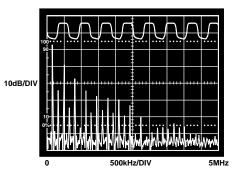

The ADM483E contains internal slew rate limiting in order to minimize the level of electromagnetic interference generated. Figure 25 shows an FFT plot when transmitting a 150 kHz data stream.

Figure 25. Driver Output Waveform and FFT Plot Transmitting @ 150 kHz

As may be seen, the slew limiting attenuates the high frequency components. EMI is therefore reduced, as are reflections due to improperly terminated cables.

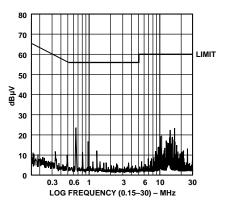

EN55022, CISPR22 defines the permitted limits of radiated and conducted interference from Information Technology Equipment (ITE).

The objective is to control the level of emissions, both conducted and radiated.

For ease of measurement and analysis, conducted emissions are assumed to predominate below 30 MHz, while radiated emissions predominate above this frequency.

### CONDUCTED EMISSIONS

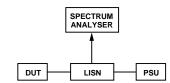

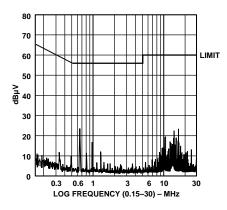

This is a measure of noise that is conducted onto the mains power supply. The noise is measured using a LISN (Linc Impedance Stabilizing Network) and a spectrum analyzer. The test setup is illustrated in Figure 26. The spectrum analyzer is set to scan the spectrum from 0 MHz to 30 MHz. Figure 27 shows that the level of conducted emissions from the ADM483E are well below the allowable limits.

Figure 26. Conducted Emissions Test Setup

Figure 27. Conducted Emissions

### **RADIATED EMISSIONS**

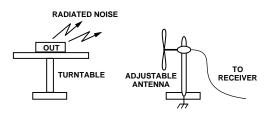

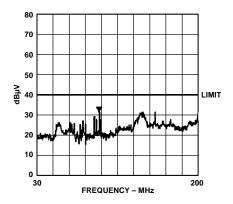

Radiated emissions are measured at frequencies in excess of 30 MHz.

A typical test setup for monitoring radiated emissions is illustrated in Figure 28.

Figure 28. Radiated Emissions Test Setup

Figure 29 shows that the level of radiated emissions is also well below the allowable limit.

Figure 29. Radiated Emissions

### APPLICATIONS INFORMATION

### **Differential Data Transmission**

Differential data transmission is used to reliably transmit data at high rates over long distances and through noisy environments. Differential transmission nullifies the effects of ground shifts and noise signals that appear as common-mode voltages on the line. There are two main standards approved by the Electronics Industries Association (EIA) that specify the electrical characteristics of transceivers used in differential data transmission.

The RS-422 standard specifies data rates up to 10 MBaud and line lengths up to 4000 ft. A single driver can drive a transmission line with up to 10 receivers.

In order to cater for true multipoint communications, the RS-485 standard was defined. This standard meets or exceeds all the requirements of RS-422, but also allows for up to 32 drivers and 32 receivers to be connected to a single bus. An extended common-mode range of -7 V to +12 V is defined. The most significant difference between RS-422 and RS-485 is the fact that the drivers may be disabled, thereby allowing more than one (32 in fact) to be connected to a single line. Only one driver should be enabled at a time, but the RS-485 standard contains additional specifications to guarantee device safety in the event of line contention.

### Cable and Data Rate

The transmission line of choice for RS-485 communications is a twisted pair. Twisted pair cable tends to cancel common-mode noise and also causes cancellation of the magnetic fields generated by the current flowing through each wire, thereby reducing the effective inductance of the pair.

A typical application showing a multipoint transmission network is illustrated in Figure 30. An RS-485 transmission line can have as many as 32 transceivers on the bus. Only one driver can transmit at a particular time, but multiple receivers may be enabled simultaneously.

Figure 30. Typical RS-485 Network

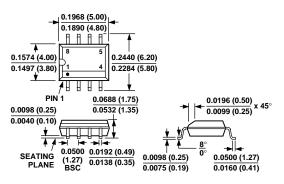

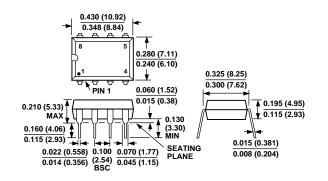

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

### 8-Lead SOIC (SO-8)

#### 8-Pin Plastic DIP (N-8)

C2934-12-1/97