# M66271FP

# **Operation Panel Controller**

REJ03F0267-0200 Rev.2.00 Mar 18, 2008

## **Description**

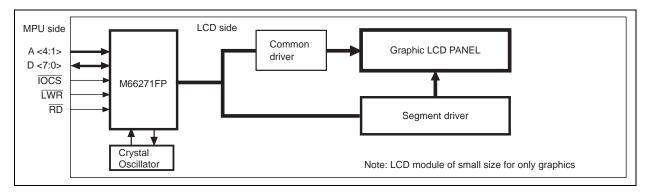

The M66271FP is a graphic display-only controller for displaying a high duty dot matrix type LCD which is used widely for PPC, FAX and multi-function telephones.

It is capable of controlling a monochrome STN LCD system of up to  $320 \times 240$  dots.

The IC has a built-in 9600-byte VRAM as a display data memory.

All of the VRAM addresses are externally opened. Address mapping in the MPU memory space allows direct addressing of all display data from the MPU, thus providing efficient display data processing such as drawing.

The built-in arbiter circuit (cycle steal system) which gives priority to display access allows timing-free access from MPU to VRAM, preventing display screen distortion.

The IC provides interface with a 8-bit/16-bit MPU with a READY (WAIT) pin.

And this IC has a function for LCD module built-in system by lessening connect pins between MPU.

### **Features**

- Displayable LCD

- Monochrome STN dot matrix type LCD of up to 76800 dots (equivalent to 320 × 240 dots)

- Maximum display duty: 1/240 (set to 240 line)

- : 1/255 (Max)

- Display memory

- Built-in 9600-byte (76800-bit) VRAM (equivalent to one screen of 320 × 240 dots LCD)

- All addresses of built-in VRAM are externally opened.

- Interface with MPU

- Capability of switching 8-bit type MPU/16-bit type MPU

- With WAIT output pin (Accessing register from MPU without WAIT output. Accessing VRAM from MPU with WAIT output.)

- Capability of controlling BHE or LWR/HWR at the interface with a 16-bit MPU.

- Interface with LCD

- LCD display data are 4-bit parallel output

- 4 kinds of control signals: CP, LP, FLM and M

- Display functions

- Graphic display only (characters drawn graphically)

- Binary display only (without tone display function)

- Vertical scrolling is allowed within memory range (small size LCD only)

- Additional function for LCD module built-in system

- 15 kinds of interface with MPU: A <4:1>, D <7:0>,  $\overline{IOCS}$ ,  $\overline{LWR}$ ,  $\overline{RD}$

- Accessing VRAM from MPU through I/O register

- Capability of interfacing with 8-bit type MPU only

- 5 V single power supply

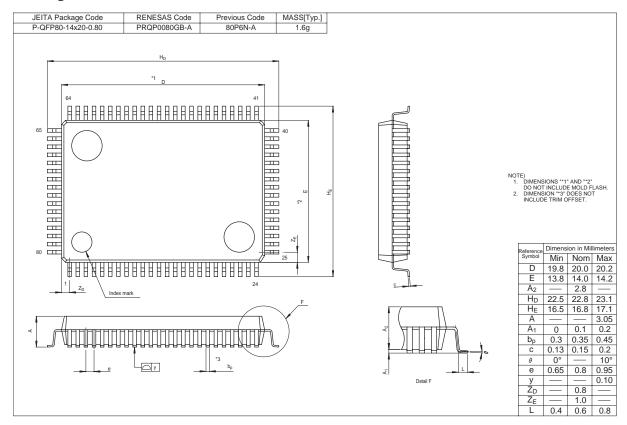

- 80-pin QFP

### **Application**

- PPC/FAX operation panel, display/operation panel of other OA equipment

- Multi-function/public telephones

- PDA/electronic notebook/information terminal

- Other applications using LCD of 76800 dots or less

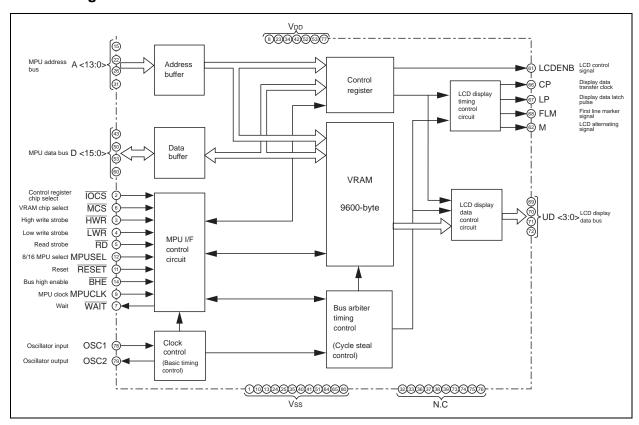

# **Block Diagram 1**

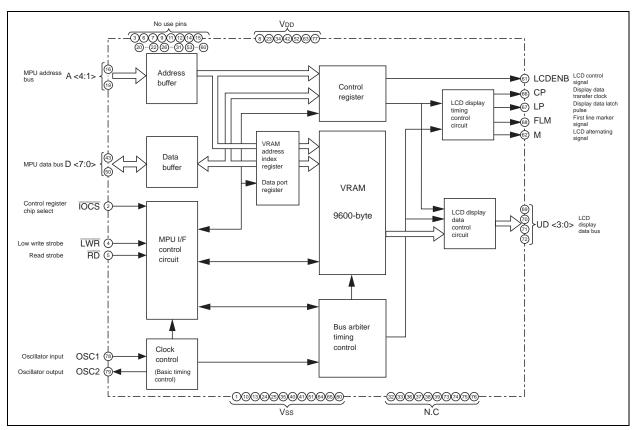

# Block Diagram 2 (In case of LCD module built-In system)

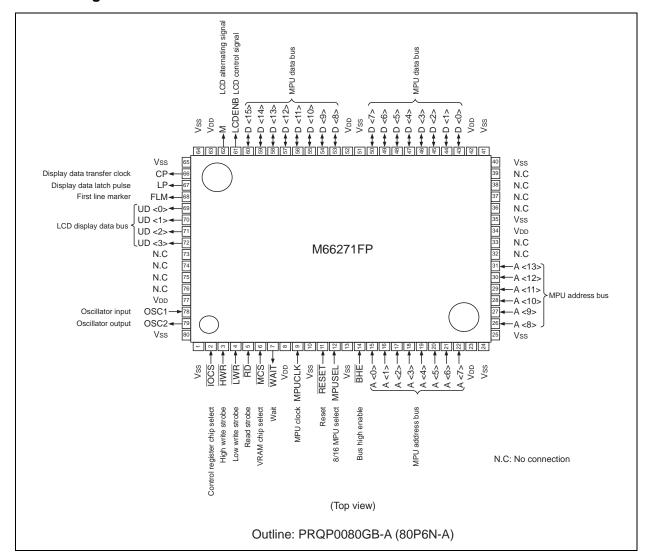

# **Pin Arrangement**

# **Pin Description**

| Item       | Pin Name        | Input/<br>Output | Function                                                                                                                                                      | Number<br>of Pins |

|------------|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| MPU        | D <15:0>        | Input/           | MPU data bus                                                                                                                                                  | 16                |

| interface  |                 | Output           | Connect to MPU data bus.  Selecting 8-bit MPU by MPUSEL input, D <15:8> connect to V <sub>DD</sub> or V <sub>SS</sub>                                         |                   |

|            | A <13:0>        | Input            | MPU address bus                                                                                                                                               | 14                |

|            | 7. 1.0.07       |                  | Connect to MPU address bus. When selecting 8-bit MPU, use A <13:0>. And                                                                                       |                   |

|            |                 |                  | selecting16-bit MPU, use A <13:1> for the address bus with combining A <0> and                                                                                |                   |

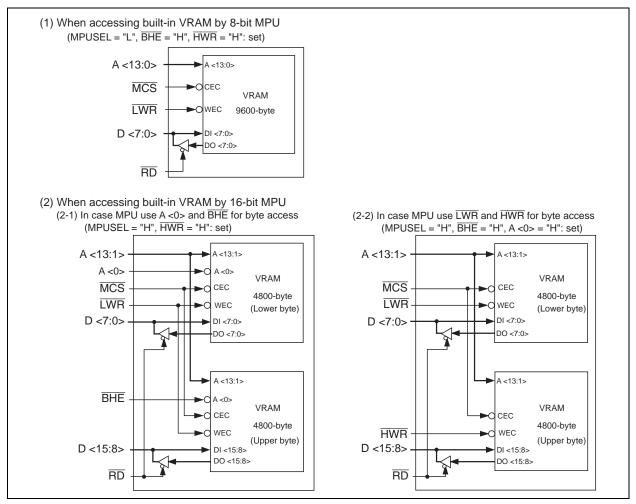

|            |                 |                  | BHE by the method of access to internal VRAM (Refer to figure 1). Use A <4:0> for                                                                             |                   |

|            |                 | Input            | selecting address of control register.  Chip select input of control register                                                                                 | 1                 |

|            | IOCS            | IIIput           | When this pin is "L", select the internal control register. Assign to I/O space of MPU.                                                                       | '                 |

|            | MCS             | Input            | Chip select input of VRAM                                                                                                                                     | 1                 |

|            |                 |                  | When this pin is "L", select the internal VRAM. Assign to memory space of MPU.                                                                                |                   |

|            | HWR             | Input            | High-write strobe input When this pin is "L", data write to the internal VRAM. HWR is valid only in using 16-                                                 | 1                 |

|            |                 |                  | bit MPU controlled byte access by LWR and HWR. (Refer to figure 1)                                                                                            |                   |

|            | ĪWR             | Input            | Low-write strobe input                                                                                                                                        | 1                 |

|            | LVVIII          | ·                | When this pin is "L", data write to the internal control register or VRAM. (Refer to                                                                          |                   |

|            |                 |                  | figure 1)                                                                                                                                                     |                   |

|            | RD              | Input            | Read strobe input When this pin is "L", data read from the internal control register or VRAM. (Refer to                                                       | 1                 |

|            |                 |                  | figure 1)                                                                                                                                                     |                   |

|            | MPUSEL          | Input            | 8/16-bit MPU select input                                                                                                                                     | 1                 |

|            |                 |                  | According to MPU, set "V <sub>SS</sub> " for 8-bit MPU and set "V <sub>DD</sub> " for 16-bit MPU                                                              |                   |

|            | RESET           | Input            | Reset input                                                                                                                                                   | 1                 |

|            |                 |                  | Use reset signal of MPU. When this pin is "L", initialize all internal control register and counter.                                                          |                   |

|            | MPUCLK          | Input            | MPU clock                                                                                                                                                     | 1                 |

|            |                 |                  | Input of MPU clock.                                                                                                                                           |                   |

|            | BHE             | Input            | Bus-high-enable input                                                                                                                                         | 1                 |

|            |                 |                  | This pin is valid when using 16-bit MPU controlled byte access by A <0> and BHE                                                                               |                   |

|            |                 |                  | (Refer to figure 1). Connect to "V <sub>DD</sub> " when using 8-bit MPU.<br>Set to "L" when using the additional function for the LCD module built-in system. |                   |

|            | WAIT            | Output           | WAIT output for MPU                                                                                                                                           | 1                 |

|            | WAII            |                  | This signal makes WAIT for MPU.                                                                                                                               | ·                 |

|            |                 |                  | Change WAIT "L" at timing of falling edge of overlapping with MCS and (RD or LWR                                                                              |                   |

|            |                 |                  | or HWR).  And return to "H" at synchronizing with the rising edge of MPUCLK after internal                                                                    |                   |

|            |                 |                  | processing.                                                                                                                                                   |                   |

|            |                 |                  | (Output WAIT only when requested access from MPU to VRAM during cycle steal                                                                                   |                   |

|            |                 | _                | access.)                                                                                                                                                      |                   |

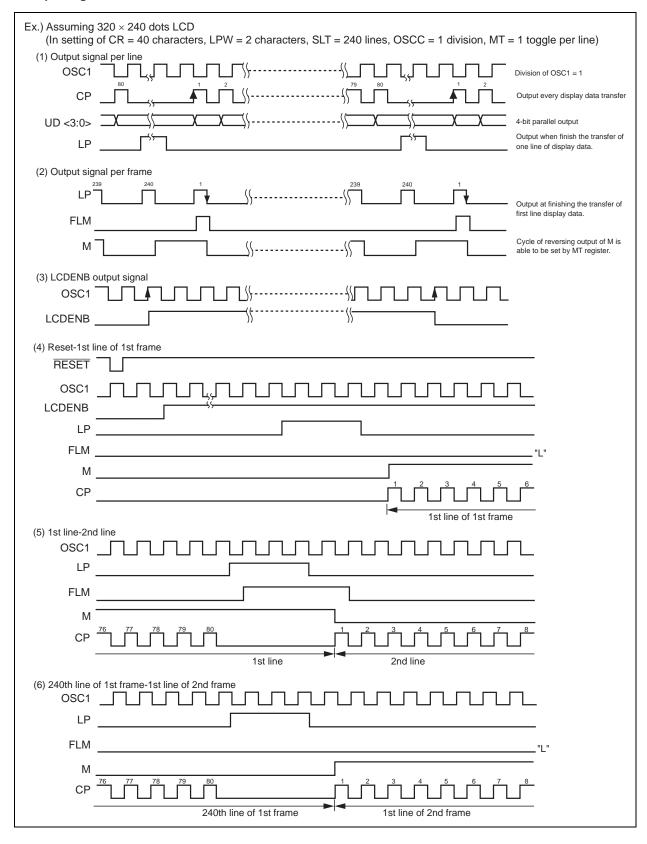

| LCD        | UD <3:0>        | Output           | Display data bus for LCD                                                                                                                                      | 4                 |

| interface  |                 |                  | Transfer the LCD display data with 4-bit parallel signal.  Mutually output upper/lower data every CP output.                                                  |                   |

|            | CP              | Output           | Display data transfer clock                                                                                                                                   | 1                 |

|            |                 |                  | Shift clock for the transfer of display data to LCD.                                                                                                          |                   |

|            |                 |                  | Take the display data of UD <3:0> to LCD at falling edge of CP.                                                                                               |                   |

|            | LP              | Output           | Display data latch pulse  This clock use both as the latch pulse of display data for LCD and the transfer of                                                  | 1                 |

|            |                 |                  | scanning signal.                                                                                                                                              |                   |

|            |                 |                  | LP output when finish the transfer of display data of a line.                                                                                                 |                   |

|            |                 |                  | Latch of display data and the transfer of scanning signal at falling edge of LP.                                                                              |                   |

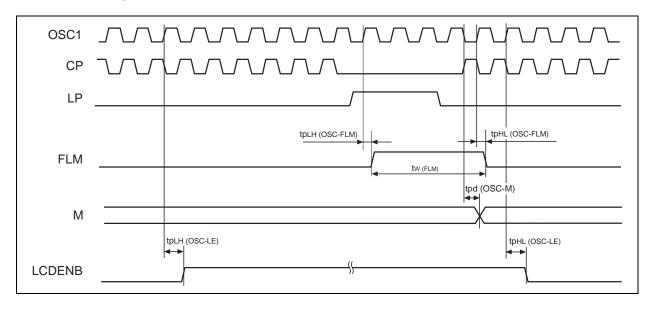

|            | FLM             | Output           | First line marker signal                                                                                                                                      | 1                 |

|            |                 |                  | Output the start pulse of scanning line.  This signal is "H" active, the IC for driving scanning line catch FLM at falling edge of                            |                   |

|            |                 |                  | LP.                                                                                                                                                           |                   |

|            | М               | Output           | LCD alternating signal output                                                                                                                                 | 1                 |

|            | LODENIS         | 0.4              | Signal for driving LCD by alternating current.                                                                                                                |                   |

|            | LCDENB          | Output           | LCD (ON/OFF) control signal output Output data which is set at bit "0" of mode register (R1) in control register. This                                        | 1                 |

|            |                 |                  | signal can use for controlling the LCD power supply, because LCDENB set to "L" by                                                                             |                   |

|            | <u> </u>        |                  | RESET.                                                                                                                                                        |                   |

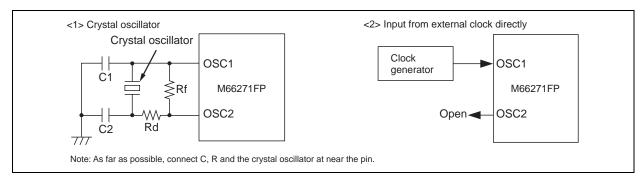

| Oscillator | OSC1            | Input            | Input pin for oscillator Generate an internal clock.                                                                                                          | 1                 |

| 0.1        | OSC2            | Output           | Output pin for oscillator For crystal oscillator or external clock signal.                                                                                    | 1                 |

| Others     | V <sub>DD</sub> | _                | Power supply (source + 5 V) Ground                                                                                                                            | 7<br>12           |

|            | V <sub>SS</sub> | Η=               | No connection                                                                                                                                                 | 10                |

|            | 14.0            |                  | THO CONTROLOGY                                                                                                                                                | 10                |

# **Absolute Maximum Ratings**

$(Ta = 0 \text{ to } +70^{\circ}\text{C unless otherwise noted})$

| Item                | Symbol         | Ratings                       | Unit |

|---------------------|----------------|-------------------------------|------|

| Supply voltage      | $V_{DD}$       | -0.3 to +6.5                  | V    |

| Input voltage       | V <sub>I</sub> | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage      | Vo             | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output current      | Io             | 10                            | mA   |

| Power dissipation   | Pd             | 600                           | mW   |

| Storage temperature | Tstg           | -55 to +150                   | °C   |

# **Recommended Operating Conditions**

$(Ta = 0 \text{ to } +70^{\circ}\text{C unless otherwise noted})$

| Item                  | Symbol          | Min | Тур | Max      | Unit |

|-----------------------|-----------------|-----|-----|----------|------|

| Supply voltage        | V <sub>DD</sub> | 4.5 | 5.0 | 5.5      | V    |

| Supply voltage        | V <sub>SS</sub> | _   | 0   | _        | V    |

| Input voltage         | Vı              | 0   | _   | $V_{DD}$ | V    |

| Output voltage        | Vo              | 0   | _   | $V_{DD}$ | V    |

| Operating temperature | Topr            | 0   | +25 | +70      | °C   |

# **Electrical Characteristics**

$(V_{DD} = 5 \text{ V} \pm 10\%, \text{ Ta} = 0 \text{ to} +70^{\circ}\text{C} \text{ unless otherwise noted})$

| Item                                | 1                                     | Symbol              | Min  | Тур | Max | Unit | Test Conditions                                                                                                                 |

|-------------------------------------|---------------------------------------|---------------------|------|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------|

| High-level input voltage            | All inputs except for OSC1, RESET and | V <sub>IH</sub>     | 2.2  | _   | _   | V    | V <sub>DD</sub> = 5.5 V                                                                                                         |

| Low-level input voltage             | MPUSEL                                | VIL                 | _    | _   | 0.8 | V    | V <sub>DD</sub> = 4.5 V                                                                                                         |

| High-level input voltage            | OSC1                                  | $V_{IH}$            | 3.5  | _   | _   | V    | $V_{DD} = 5.5 \text{ V}$                                                                                                        |

| Low-level input voltage             |                                       | V <sub>IL</sub>     | _    | _   | 1.0 | V    | $V_{DD} = 4.5 \text{ V}$                                                                                                        |

| Positive-going threshold voltage    | MPUSEL, RESET                         | V <sub>T</sub> +    | 2.3  |     | 3.7 | V    | V <sub>DD</sub> = 5.0 V                                                                                                         |

| Negative-going threshold voltage    |                                       | V <sub>T</sub> –    | 1.25 | _   | 2.3 | V    | V <sub>DD</sub> = 5.0 V                                                                                                         |

| High-level output voltage           | All outputs except for OSC2 and       | V <sub>OH</sub>     | 4.1  | _   | _   | V    | $V_{DD}$ $I_{OH} = -4 \text{ mA}$ $= 4.5 \text{ V}$                                                                             |

| Low-level output voltage            | outputs of D <15:0>                   | V <sub>OL</sub>     | _    | _   | 0.4 | V    | I <sub>OL</sub> = 4 mA                                                                                                          |

| High-level output voltage           | OSC2                                  | V <sub>OH</sub>     | 4.1  | _   | _   | V    | $V_{DD}$ $I_{OH} = -50 \mu A$                                                                                                   |

| Low-level output voltage            |                                       | V <sub>OL</sub>     | _    | _   | 0.4 | V    | = $4.5 \text{ V}$ $I_{OL} = 50 \mu A$                                                                                           |

| High-level input current            |                                       | I <sub>IH</sub>     | _    |     | 10  | Α    | $V_{DD} = 5.5 \text{ V}, V_{I} = V_{DD}$                                                                                        |

| Low-level input current             |                                       | I <sub>IL</sub>     | _    | _   | -10 | Α    | $V_{DD} = 5.5 \text{ V}, V_{I} = V_{SS}$                                                                                        |

| Off-state high-level output current | D <15:0>                              | l <sub>ozh</sub>    | _    | _   | 10  | Α    | $V_{DD} = 5.5 \text{ V}, V_{O} = V_{DD}$                                                                                        |

| Off-state low-level output current  |                                       | I <sub>OZL</sub>    | _    | _   | -10 | Α    | $V_{DD} = 5.5 \text{ V}, V_O = V_{SS}$                                                                                          |

| Operating supply current (Average)  |                                       | I <sub>DD (A)</sub> | _    | _   | 40  | mA   | $V_{DD} = 5.5 \text{ V},$ $V_{I} = V_{DD} \text{ or } V_{SS}$ $fosc = 10 \text{ MHz},$ $Output = open$                          |

| Stand-by supply current             |                                       | I <sub>DD</sub> (S) | _    | 1   | 500 | А    | $V_{DD} = 5.5 \text{ V},$ $\overline{\text{IOCS}}, \overline{\text{MCS}} = V_{DD}$ Other's $V_{I} = V_{DD}$ or $V_{SS}$ (valid) |

# **Switching Characteristics**

$(V_{DD} = 5 \text{ V} \pm 10\%, \text{ Ta} = 0 \text{ to} +70^{\circ}\text{C}, C_{L} = 50 \text{ pF})$

| Item                                      | Symbol                      | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------------------|-----|-----|-----|------|

| IOCS data access time                     | t <sub>a (IOCS-D)</sub>     | _   | _   | 70  | ns   |

| MCS data access time                      | t <sub>a (MCS-D)</sub>      |     |     |     |      |

| RD data access time                       | t <sub>a (RD-D)</sub>       |     |     |     |      |

| Output disable time after IOCS            | t <sub>dis (IOCS-D)</sub>   | _   | _   | 20  | ns   |

| Output disable time after MCS             | t <sub>dis (MCS-D)</sub>    |     |     |     |      |

| Output disable time after RD              | t <sub>dis (RD-D)</sub>     |     |     |     |      |

| WAIT output propagation time after MCS    | t <sub>pHL (MCS-WAIT)</sub> | _   | _   | 40  | ns   |

| WAIT output propagation time after WR     | t <sub>pHL (WR-WAIT)</sub>  |     |     |     |      |

| WAIT output propagation time after RD     | t <sub>pHL</sub> (RD-WAIT)  |     |     |     |      |

| WAIT output propagation time after MPUCLK | t <sub>pLH</sub> (CLK-WAIT) | _   | _   | 20  | ns   |

| CP output propagation time after OSC      | t <sub>pd (OSC-CP)</sub>    | _   | _   | 40  | ns   |

| LP output propagation time after OSC      | t <sub>pLH</sub> (OSC-LP)   | _   | _   | 40  | ns   |

|                                           | t <sub>pHL</sub> (OSC-LP)   |     |     |     |      |

| UD access time                            | t <sub>a (UD)</sub>         | _   | _   | 40  | ns   |

| FLM output propagation time after OSC     | t <sub>pLH</sub> (OSC-FLM)  | _   | _   | 40  | ns   |

|                                           | t <sub>pHL (OSC-FLM)</sub>  |     |     |     |      |

| M output propagation time after OSC       | t <sub>pd (OSC-M)</sub>     | _   | _   | 40  | ns   |

| LCDENB output propagation time after OSC  | t <sub>pLH</sub> (OSC-LE)   | _   | _   | 40  | ns   |

|                                           | t <sub>pHL</sub> (OSC-LE)   |     |     |     |      |

| Data definite time before canceling WAIT  | t <sub>pd (D-WAIT)</sub>    | 0   |     |     | ns   |

# **Timing Requirements**

$(V_{DD} = 5 \text{ V} \pm 10\%, \text{ Ta} = 0 \text{ to } +70^{\circ}\text{C})$

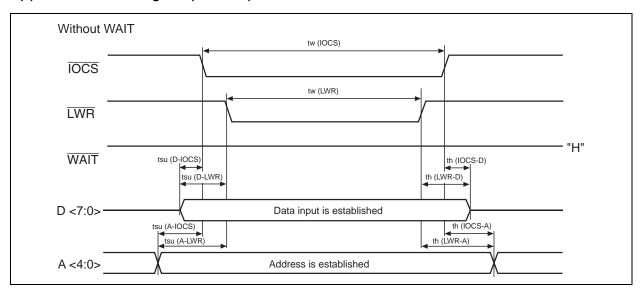

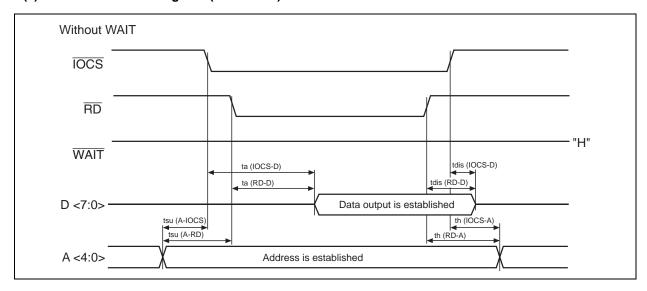

# (1) Accessing to Control Register

| ltem                                            | Symbol                   | Min | Тур | Max | Unit |

|-------------------------------------------------|--------------------------|-----|-----|-----|------|

| IOCS pulse width                                | tw (IOCS)                | 70  | _   | _   | ns   |

| LWR pulse width                                 | t <sub>W (LWR)</sub>     |     |     |     |      |

| Data set up time before falling edge of IOCS    | t <sub>su (D-IOCS)</sub> | 0   | _   | _   | ns   |

| Data set up time before falling edge of LWR     | t <sub>su (D-LWR)</sub>  |     |     |     |      |

| Data hold time after rising edge of IOCS        | t <sub>h (IOCS-D)</sub>  | 15  | _   | _   | ns   |

| Date hold time after rising edge of LWR         | t <sub>h (LWR-D)</sub>   |     |     |     |      |

| Address set up time before falling edge of IOCS | t <sub>su (A-IOCS)</sub> | 15  | _   | _   | ns   |

| Address set up time before falling edge of LWR  | t <sub>su (A-LWR)</sub>  |     |     |     |      |

| Address set up time before falling edge of RD   | t <sub>su (A-RD)</sub>   |     |     |     |      |

| Address hold time after rising edge of IOCS     | t <sub>h (IOCS-A)</sub>  | 15  | _   | _   | ns   |

| Address hold time after rising edge of LWR      | t <sub>h (LWR-A)</sub>   |     |     |     |      |

| Address hold time after rising edge of RD       | t <sub>h (RD-A)</sub>    |     |     |     |      |

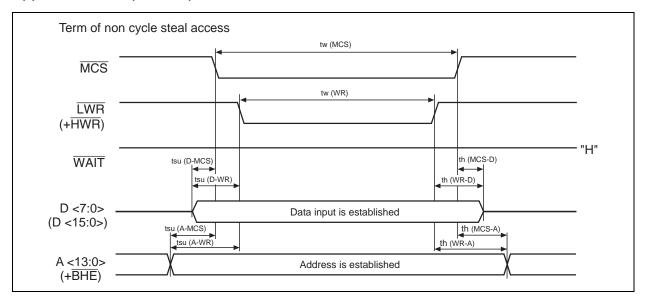

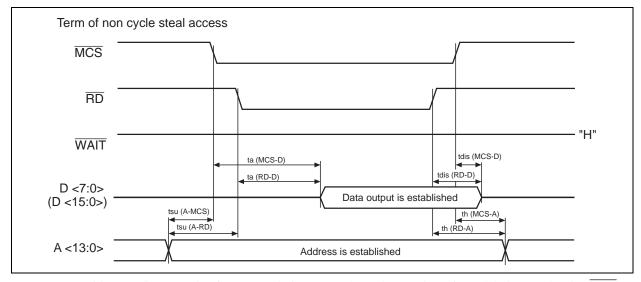

# (2) Accessing to VRAM

| Item                                           | Symbol                  | Min | Тур | Max | Unit |

|------------------------------------------------|-------------------------|-----|-----|-----|------|

| MCS pulse width                                | t <sub>W (MCS)</sub>    | 70  | _   | _   | ns   |

| WR pulse width                                 | t <sub>W (WR)</sub>     |     |     |     |      |

| Data set up time before falling edge of MCS    | t <sub>su (D-MCS)</sub> | 0   | _   | _   | ns   |

| Data set up time before falling edge of WR     | t <sub>su (D-WR)</sub>  |     |     |     |      |

| Data hold time after rising edge of MCS        | t <sub>h (MCS-D)</sub>  | 15  | _   | _   | ns   |

| Data hold time after rising edge of WR         | t <sub>h (WR-D)</sub>   |     |     |     |      |

| Address set up time before falling edge of MCS | t <sub>su (A-MCS)</sub> | 15  | _   | _   | ns   |

| Address set up time before falling edge of WR  | t <sub>su (A-WR)</sub>  |     |     |     |      |

| Address set up time before falling edge of RD  | t <sub>su (A-RD)</sub>  |     |     |     |      |

| Address hold time after rising edge of MCS     | t <sub>h (MCS-A)</sub>  | 15  | _   | _   | ns   |

| Address hold time after rising edge of WR      | t <sub>h (WR-A)</sub>   |     |     |     |      |

| Address hold time after rising edge of RD      | t <sub>h (RD-A)</sub>   |     |     |     |      |

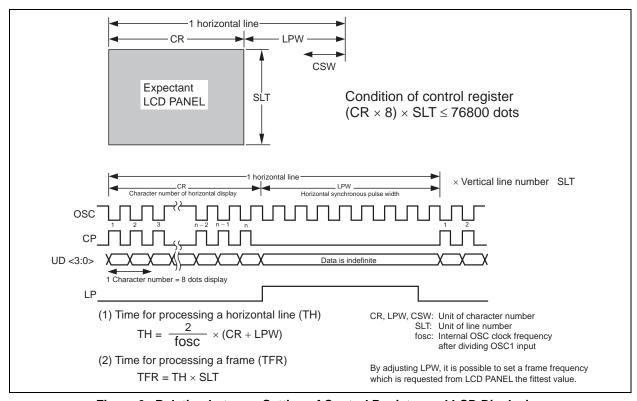

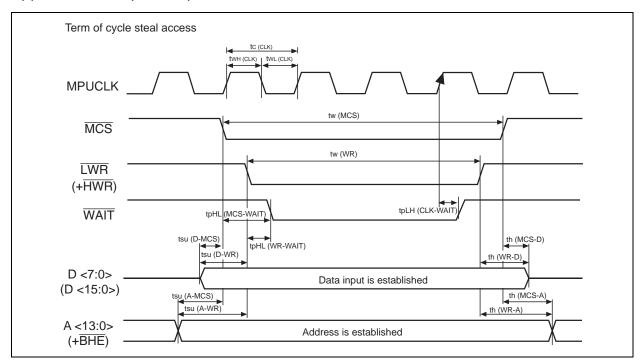

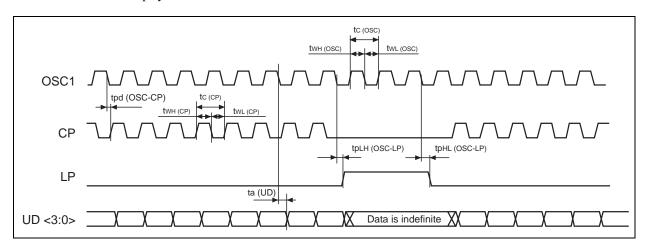

## (3) Clock and Accessing to LCD Display

| Item                   | Symbol                | Min | Тур                                               | Max | Unit |

|------------------------|-----------------------|-----|---------------------------------------------------|-----|------|

| MPUCLK cycle time      | t <sub>C (CLK)</sub>  | 50  | _                                                 |     | ns   |

| MPUCLK "H" pulse width | t <sub>WH (CLK)</sub> | _   | t <sub>C (CLK)</sub>                              | _   | ns   |

| MPUCLK "L" pulse width | t <sub>WL (CLK)</sub> |     | 2                                                 |     |      |

| OSC cycle time         | t <sub>C (OSC)</sub>  | 50* | _                                                 | I   | ns   |

| OSC "H" pulse width    | t <sub>WH</sub> (OSC) | _   | t <sub>c (osc)</sub>                              | _   | ns   |

| OSC "L" pulse width    | t <sub>WL (OSC)</sub> |     | 2                                                 |     |      |

| CP cycle time          | t <sub>C (CP)</sub>   |     | t <sub>C (OSC)</sub> (1/n)                        | l   | ns   |

| CP "H" pulse width     | t <sub>WH (CP)</sub>  | _   | t <sub>C (OSC)</sub>                              | _   | ns   |

| CP "L" pulse width     | t <sub>WL (CP)</sub>  |     | 2 • (1/n)                                         |     |      |

| FLM pulse width        | t <sub>W (FLM)</sub>  | _   | $\frac{2 \bullet t_{C (OSC)} \bullet LPW}{(1/n)}$ |     | ns   |

Note: Clock frequency of OSC1 input is less than fmax = 20 MHz.

Limit of OSC clock for the internal operation is fmax = 10 MHz.

When OSC1 is more than 10 MHz from external input, set OSC clock up to 10 MHz by using division of OSCC register.

Division is set with rising edge of OSC1 input.

1/n = Division of OSC1

LPW = Setting value of LPW register

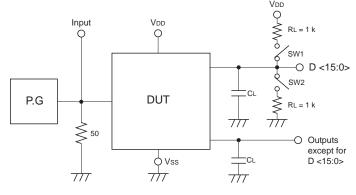

## **Test Circuit**

| Item                  | SW1    | SW2    |

|-----------------------|--------|--------|

| t <sub>dis (LZ)</sub> | Closed | Open   |

| t <sub>dis (HZ)</sub> | Open   | Closed |

| t <sub>a (ZL)</sub>   | Closed | Open   |

| t <sub>a (ZH)</sub>   | Open   | Closed |

(1) Input pulse level: 0 to 3 V

Input pulse rise/fall time: tr, tf = 3 ns

Input decision voltage: 1.5 V

Output decision voltage: V<sub>DD</sub>/2

(However,  $t_{\text{dis}\,(LZ)}$  is 10% of output amplitude and  $t_{\text{dis}}$   $_{(HZ)}$  is 90% of that for decision.)

(2) Load capacity C<sub>L</sub> include float capacity of connection and input capacity of probe.

### Outline

M66271FP is graphic display only controller for displaying a dot matrix type LCD. This IC has a built-in display data memory (VRAM) which is equivalent to  $320 \times 240$  dots LCD.

### Control register

When access the control register from MPU side, use  $\overline{IOCS}$ ,  $\overline{LWR}$ ,  $\overline{RD}$ , A <4:0> and D <7:0>. Refer to table 1, when set control type inputs.

Control registers are R1 to R8 for the normal mode function and R9 to R11 for the exclusive register for the LCD module built-in system.

### VRAM

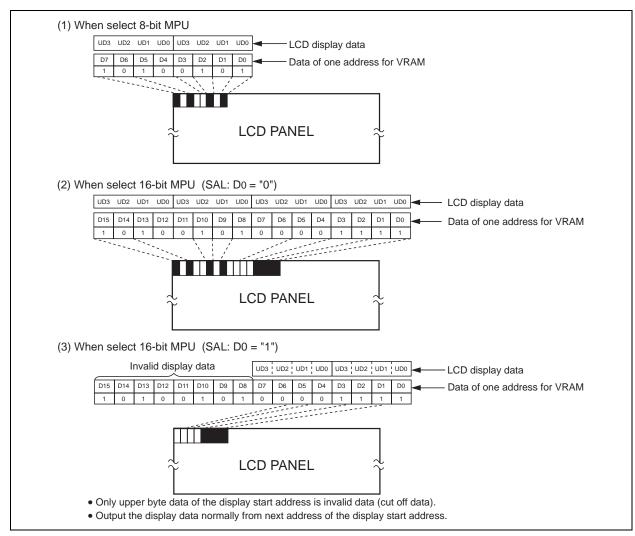

When access VRAM from MPU side, use  $\overline{MCS}$ ,  $\overline{HWR}$ ,  $\overline{LWR}$ ,  $\overline{RD}$ ,  $\overline{BHE}$ , A <13:0> and D <15:0>. And enable to correspond to both 8-bit and 16-bit MPU by using MPUSEL input. Refer to figure 1 and table 2 to 6 for a form of VRAM and input setting for 8/16-bit MPU.

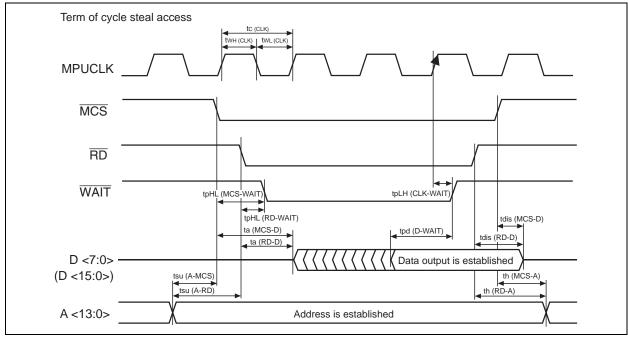

### · Cycle steal system

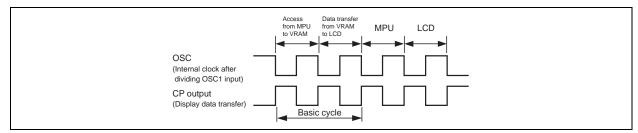

Cycle steal is interact method of transferring display data for LCD from VRAM and accessing VRAM from MPU on the basic cycle of OSC.

Basic timing is two clocks of OSC, and assign first clock to the access from MPU to VRAM and second clock to the transfer of display data from VRAM to LCD.

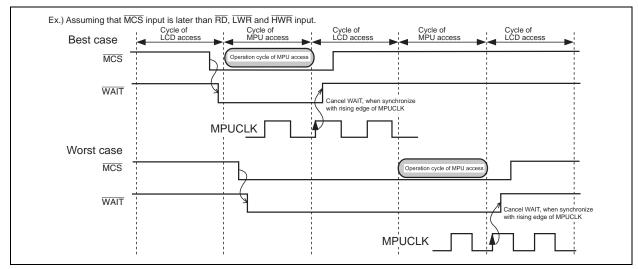

In accessing VRAM from MPU, output  $\overline{WAIT}$ . Change  $\overline{WAIT}$  to "L" at the timing of the falling edge of overlapping with  $\overline{MCS}$  and  $(\overline{RD}$  or  $\overline{LWR}/\overline{HWR})$ . And return to "H" at synchronizing with rising edge of MPUCLK after internal processing.

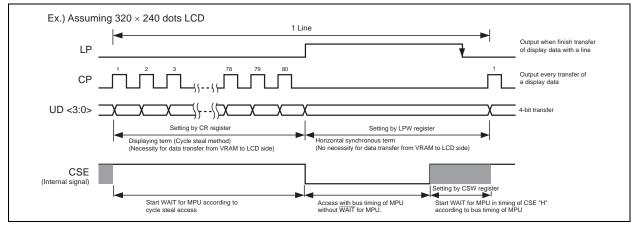

Cycle steal system can transfer data with more efficient. This function access with the cycle steal method as taking  $\overline{WAIT}$  for MPU during the display term with necessity for the display data transfer from built-in VRAM to LCD. On other side, don't output  $\overline{WAIT}$  for keeping throughput of MPU during horizontal synchronous term with no necessity for the display data transfer from VRAM to LCD side.

Refer to the following description of cycle steal.

### Output to LCD side

width by LPW register.

LCD display data UD <3:0> output synchronized with the rising edge of CP output per 4 bits.

LP output synchronized with the falling edge of OSC when finish the transfer of display data for a line. Enable to adjust the fittest value of the frame frequency requested by the LCD PANEL side with adjusting pulse

FLM output, when finish the transfer of display data of 1st line.

M output is the LCD alternating signal which is signal for driving LCD by alternating current.

M-cycle enable to set variably by M-cycle variable register in line unit, and enable to utilize for preventing LCD from being inferior.

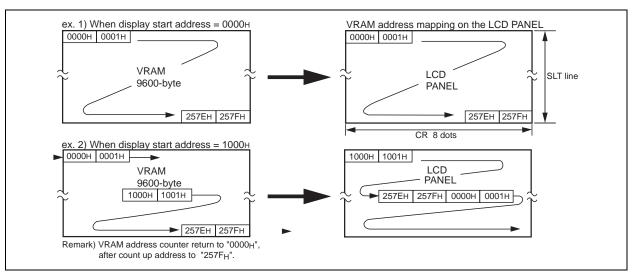

## Difference in VRAM between 8-bit and 16-bit MPU

Figure 1 Difference in VRAM between 8-bit and 16-bit MPU

# **Combination of Control Input Pins for MPU Interface**

Table 1 to 6 show conditions of input setting when access the control register and VRAM from MPU.

(1) Access control register (Use address = A < 4:0>, Data = D < 7:0>)

### Table 1

| IOCS | LWR | RD | Operation                  |

|------|-----|----|----------------------------|

| L    | L   | Н  | Write to control register  |

| L    | Н   | L  | Read from control register |

| Н    | Х   | Χ  | Invalid                    |

## (2) Writing to VRAM

(2-1) When use 8-bit MPU (MPUSEL = "L",  $\overline{BHE} = \overline{HWR} = "H"$ : set)

## Table 2

| MPU |     |     |       |     |     | Odd     | Even    | Valid Data Bus |

|-----|-----|-----|-------|-----|-----|---------|---------|----------------|

| SEL | MCS | BHE | A <0> | HWR | LWR | Address | Address | Width of MPU   |

| L   | L   | Н   | L     | Н   | L   | Invalid | Write   | 8-bit          |

|     |     |     | Н     |     |     | Write   | Invalid |                |

|     |     |     | Х     |     | Н   | Invalid | Invalid |                |

|     | Н   |     | Х     |     | Х   |         |         |                |

(2-2) When use 16-bit MPU (In MPU controls byte access with A <0> and  $\overline{BHE}$ , MPUSEL =  $\overline{HWR}$  = "H": set)

## Table 3

| MPU<br>SEL | MCS | BHE | A <0> | HWR | LWR | Upper<br>Byte | Lower<br>Byte | Valid Data Bus<br>Width of MPU |

|------------|-----|-----|-------|-----|-----|---------------|---------------|--------------------------------|

| Н          | L   | L   | L     | Н   | L   | Write         | Write         | 16-bit                         |

|            |     |     |       |     | Н   | Invalid       | Invalid       |                                |

|            |     |     | Н     |     | L   | Write         | Invalid       | Upper 8-bit                    |

|            |     |     |       |     | Н   | Invalid       | Invalid       |                                |

|            |     | Н   | L     |     | L   | Invalid       | Write         | Lower 8-bit                    |

|            |     |     |       |     | Н   | Invalid       | Invalid       |                                |

|            |     |     | Н     |     | L   | Invalid       | Write         | Lower 8-bit                    |

|            |     |     |       |     | Н   | Invalid       | Invalid       |                                |

|            | Н   | Х   | Х     |     | Х   |               |               |                                |

Even if

A <0> = "H",

enable to write

(2-3) When use 16-bit MPU

(In MPU controls byte access with  $\overline{LWR}$  and  $\overline{HWR}$ , MPUSEL =  $\overline{BHE}$  = A <0> = "H": set)

## Table 4

| MPU |     |     |       |     |     | Upper   | Lower   | Valid Data Bus |

|-----|-----|-----|-------|-----|-----|---------|---------|----------------|

| SEL | MCS | BHE | A <0> | HWR | LWR | Byte    | Byte    | Width of MPU   |

| Н   | L   | Η   | Н     | L   | L   | Write   | Write   | 16-bit         |

|     |     |     |       |     | Η   | Write   | Invalid | Upper 8-bit    |

|     |     |     |       | Н   | L   | Invalid | Write   | Lower 8-bit    |

|     |     |     |       |     | Н   | Invalid | Invalid |                |

|     | Н   |     |       | X   | Χ   |         |         |                |

(3) Reading from VRAM

(3-1) When use 8-bit MPU (MPUSEL = "L",  $\overline{BHE}$  = "H": set)

## Table 5

| MPU<br>SEL | MCS | BHE | A <0> | RD | Odd<br>Address | Even<br>Address | Valid Data Bus<br>Width of MPU |

|------------|-----|-----|-------|----|----------------|-----------------|--------------------------------|

| L          | L   | Н   | L     | L  | Invalid        | Read            | 8-bit                          |

|            |     |     | Н     |    | Read           | Invalid         |                                |

|            |     |     | Х     | Н  | Invalid        | Invalid         |                                |

|            | Н   |     |       | X  |                |                 |                                |

(3-2) When use 16-bit MPU (MPUSEL = "H": set)

## Table 6

| MPU<br>SEL | MCS | BHE | A <0> | RD | Upper<br>Byte | Lower<br>Byte | Valid Data Bus<br>Width of MPU |

|------------|-----|-----|-------|----|---------------|---------------|--------------------------------|

| Н          | L   | Х   | Х     | L  | Read          | Read          | 16-bit                         |

|            |     |     |       | Н  | Invalid       | Invalid       |                                |

|            | Н   |     |       | Х  |               |               |                                |

Note: Avoid setting combination except above, as cause of error action.

X = "L" or "H"

# **Description of Cycle Steal**

# **Basic Timing**

Basic timing of M66271FP is two clocks of OSC (internal clock after dividing OSC1 input).

Assign first clock to accessing from MPU to VRAM and second clock to transferring of display data from VRAM to LCD.

Figure 2 Basic Timing

## Operation Cycle of MPU Access (During WAIT Output)

Writing or reading operation for VRAM during cycle steal needs 1 cycle in best case or 3 cycles in worst case, according to the condition of the internal cycle steal at staring access requested from MPU.

Figure 3 Operation Cycle of MPU Access

## **Function of Cycle Steal Control**

M66271FP has a function for processing data of a line with more efficient. This function access with the cycle steal method as taking  $\overline{WAIT}$  for MPU during the display term with necessity for the display data transfer from built-in VRAM to LCD.

On other side, don't output  $\overline{WAIT}$  for keeping throughput of MPU during the horizontal synchronous term with no necessity for the display data transfer from VRAM to LCD side.

But certainly set a term of accessing with the cycle steal method by CSW register, for controlling an error action near the end of horizontal synchronous term.

Figure 4 Function of Cycle Steal Control

## **Handling of Oscillator Pin**

Figure 5 Oscillator Pin

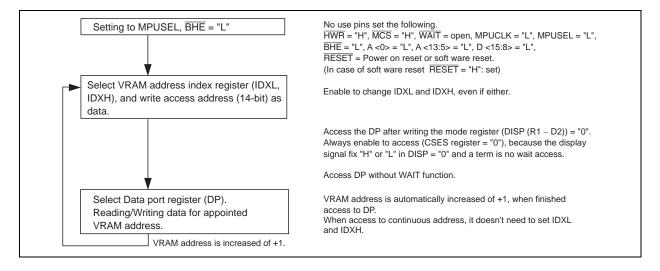

### Additional Function for LCD Module Built-in System

As all of the VRAM address in M66271FP are externally opened for addressing VRAM from MPU directly.

When consider the LCD module built-in system, connect pins are increased.

But M66271FP has an additional function for the LCD module built-in system by lessening connect pins.

Outline of the additional function for the LCD module built-in system.

- Interface pins with MPU

15 kinds of interface with MPU: A <4:1>, D <7:0>, IOCS, LWR, RD

- Method of accessing the internal VRAM

Access the internal VRAM through the VRAM address index register (IDXL, IDXH) and the data port register (DP)

which are used for I/O register.

The following show the process of accessing VRAM.

### **Application**

# **Control Register**

M66271FP has 9 kinds of control register.

To set mode from MPU to control register, use <del>IOCS</del>, <del>LWR</del>, <del>RD</del>, A <4:0> and D <7:0>.

(1) Kind of control register

## **Control Register Table**

| Kind | d of Register                                            |    | Α  | ddre | ss |    |             |       |             | Da     | ata   |       |     |           |                                                                                      |                      |

|------|----------------------------------------------------------|----|----|------|----|----|-------------|-------|-------------|--------|-------|-------|-----|-----------|--------------------------------------------------------------------------------------|----------------------|

| No.  | Name                                                     | A4 | А3 | A2   | A1 | A0 | D7          | D6    | D5          | D4     | D3    | D2    | D1  | D0        | Functions of Register                                                                | R/W                  |

| R1   | Mode<br>register                                         | 0  | 0  | 0    | 0  | 0  | CSES        | RESET | <del></del> | oscc   |       | DISP  | REV | LCDE      | D6 to D0 set the basic mode. D7 is the status register of cycle steal state.         | R/W<br>D7 = Only "R" |

| R2   | Horizontal<br>display<br>character<br>number<br>register | 0  | 0  | 0    | 1  | 0  |             |       | <b>-</b>    |        | CF    | ₹     |     |           | Set the number of horizontal display characters per line.                            | W                    |

| R3   | Horizontal<br>synchronous<br>pulse width<br>register     | 0  | 0  | 1    | 0  | 0  | <b>-</b>    |       |             | LP\    | w ——  |       |     | <b></b> → | Set the pulse width of LP per line.                                                  | W                    |

| R4   | Cycle steal<br>enable width<br>register                  | 0  | 0  | 1    | 1  | 0  | <b>-</b>    |       |             | — c    | sw —  |       |     |           | Set the term of cycle steal enable access during horizontal synchronous term.        | W                    |

| R5   | Vertical line<br>number<br>register                      | 0  | 1  | 0    | 0  | 0  | <b></b>     |       |             | S      | SLT — |       |     | <b></b> → | Set the number of display line of vertical direction.                                | W                    |

| R6   | Display start<br>address<br>register                     | 0  | 1  | 0    | 1  | 0  | <b></b>     |       |             | 8      | SAL — |       | _   |           | Set the display start address of VRAM.  Set lower 8-bit to SAL and                   | R/W                  |

| R7   | rogiotoi                                                 | 0  | 1  | 1    | 0  | 0  |             |       | <b>.</b>    |        |       | SAH - |     | <b></b> → | upper 6-bit to SAH.  Max = 257F <sub>H</sub>                                         |                      |

| R8   | M cycle<br>variable<br>register                          | 0  | 1  | 1    | 1  | 0  | <b>—</b>    |       |             | — М    | т —   |       |     |           | Set the cycle of LCD alternating signal from M.                                      | W                    |

| R9   | Data port register                                       | 1  | 0  | 0    | 0  | 0  | <del></del> |       |             | — D    | Р —   |       |     | <b>─</b>  | Data port register for accessing VRAM through the register.                          | R/W                  |

| R10  | VRAM<br>address<br>index<br>register                     | 1  | 0  | 0    | 1  | 0  | <del></del> |       |             | —— ID: | XL —  |       |     | <b></b> → | Set the address for accessing VRAM. Set lower 8-bit to IDXL and upper 6-bit to IDXH. | R/W                  |

| R11  | 129000                                                   | 1  | 0  | 1    | 0  | 0  |             |       | <u> </u>    |        | — IDX | (H —  |     |           | Max = 257F <sub>H</sub> And automatically increase in continuous address.            |                      |

Note: Data port register (DP) and VRAM address index register (IDXL, IDXH) are exclusive register, when using this IC for the LCD module built-in system.

When RESET, each register is initialize the setting which is assumed LCD size of  $320 \times 240$  dots.

Then, even if each register has not setting, output the signal to LCD side, it is possible to be alternation of LCD.

# (2) Description of register (2-1) Mode register [R1]

| Address | R/W                  |                   |                                         |                                          |                                                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reset |

|---------|----------------------|-------------------|-----------------------------------------|------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 00000   | R/W<br>D7 = Only "R" | D7 0 1            | _                                       | o wait a                                 | CSES<br>ccess<br>al access                                                   | <ul> <li>Status register for identifying active or inactive in cycle steal function.</li> <li>Set "1" during active with cycle steal function.</li> <li>CSES is for only reading, not for writing.</li> </ul>                                                                                                                                                                                                                                                                         | 0     |

|         |                      | <b>D6</b> 0 1     | -                                       | eset OF                                  |                                                                              | <ul> <li>Software reset.</li> <li>Surely return to reset off after reset on.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               | 0     |

|         |                      | D5<br>0<br>0<br>0 | 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | D3 0 1 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 | Division of OSC1  1  1/2 Division  1/4 Division  1/8 Division  1/16 Division | <ul> <li>Set the division of OSC clock for internal operation from OSC1 input pin.</li> <li>When reset, OSCC = 000, OSC1 clock doesn't divide.</li> <li>Don't set except left table.</li> </ul>                                                                                                                                                                                                                                                                                       | 000   |

|         |                      | D22<br>0<br>1     |                                         | Display                                  |                                                                              | <ul> <li>Control the displaying ON/OFF of LCD.</li> <li>When reset, DISP = 0, set display OFF.</li> <li>REV (D1) set "1", and when DISP = "0" display data<br/>UD &lt;3:0&gt; output "1" in reversal mode.</li> </ul>                                                                                                                                                                                                                                                                 | 0     |

|         |                      | 0<br>1            | ١                                       |                                          | REV<br>display<br>al display                                                 | <ul> <li>Control normal/reversal of LCD display.</li> <li>When reset, REV = 0, set normal display.</li> <li>In using LCD of permeation method, REV = "1" has effect.</li> </ul>                                                                                                                                                                                                                                                                                                       | 0     |

|         |                      | 0<br>1            | L                                       |                                          | LCDE  B = "0" output  B = "1" output                                         | <ul> <li>Set the output data from LCDENB output pin.</li> <li>When reset, LCDE = 0, LCDENB output "0" (Vss potential).</li> <li>This function is prepared for controlling the voltage of LCD.</li> <li>When the power supply is ON after finish each register setting, LCDE = "1", supply voltage of LCD.</li> <li>Conversely for setting power supply OFF, first LCDE = "0", the voltage of LCD is OFF. Therefore enable to prevent LCD from being unusual voltage as DC.</li> </ul> | 0     |

## (2-2) Horizontal display characters number register [R2]

| Address | R/W |     | Function                       |    |    |    |              |    |    |                           |                      |  |  |  |  |  |

|---------|-----|-----|--------------------------------|----|----|----|--------------|----|----|---------------------------|----------------------|--|--|--|--|--|

| 00010   | W   |     |                                |    |    |    |              |    |    |                           |                      |  |  |  |  |  |

|         |     |     |                                |    | С  | R  |              |    |    |                           |                      |  |  |  |  |  |

|         |     | D7  | D6                             | D5 | D4 | D3 | D2           | D1 | D0 | Character Number          | Display Dot Number   |  |  |  |  |  |

|         |     |     | /                              | 0  | 0  | 0  | 0            | 0  | 0  | _                         | _                    |  |  |  |  |  |

|         |     |     | /                              | 0  | 0  | 0  | 0            | 0  | 1  | 1                         | 8                    |  |  |  |  |  |

|         |     |     | /                              | 0  | 0  | 0  | 0            | 1  | 0  | 2                         | 16                   |  |  |  |  |  |

|         |     |     | /                              |    |    | ,  | $\downarrow$ |    |    | <b>\</b>                  | <b>↓</b>             |  |  |  |  |  |

|         |     |     | /                              | 1  | 1  | 1  | 1            | 1  | 1  | 63                        | 504                  |  |  |  |  |  |

|         |     | cha | e numbe<br>aracters<br>en rese | )  |    |    |              | ·  |    | an set to the extent of N | lax = 504 dots (= 63 |  |  |  |  |  |

Note: Definition of the number of display characters.

The number of display characters means data which is corresponding with 1 byte of VRAM. In case of binary, 1 bit of VRAM corresponds to 1 dot of display, then 1 character means 8 dots of display.

# (2-3) Horizontal synchronous pulse width register [R3]

| Address | R/W |                       |                                             |                                |                              |                          |                                |         | Fun    | ction                   |                                                                                                | Reset           |

|---------|-----|-----------------------|---------------------------------------------|--------------------------------|------------------------------|--------------------------|--------------------------------|---------|--------|-------------------------|------------------------------------------------------------------------------------------------|-----------------|

| 00100   | W   |                       |                                             |                                |                              |                          |                                |         |        |                         |                                                                                                | 01 <sub>H</sub> |

|         |     |                       |                                             |                                | LF                           | w                        |                                |         |        |                         |                                                                                                |                 |

|         |     | D7                    | D6                                          | D5                             | D4                           | D3                       | D2                             | D1      | D0     | Character Number        |                                                                                                |                 |

|         |     | 0                     | 0                                           | 0                              | 0                            | 0                        | 0                              | 0       | 0      | _                       |                                                                                                |                 |

|         |     | 0                     | 0                                           | 0                              | 0                            | 0                        | 0                              | 0       | 1      | 1                       |                                                                                                |                 |

|         |     | 0                     | 0                                           | 0                              | 0                            | 0                        | 0                              | 1       | 0      | 2                       |                                                                                                |                 |

|         |     |                       |                                             |                                | ,                            | $\downarrow$             |                                |         |        | <b>\</b>                |                                                                                                |                 |

|         |     | 1                     | 1                                           | 1                              | 1                            | 1                        | 1                              | 1       | 1      | 255                     |                                                                                                |                 |

|         |     | Ho<br>dis<br>Ad<br>Ar | orizonta<br>splayin<br>djusting<br>nd the a | al sync<br>g data.<br>g this p | hronou<br>ulse wi<br>LP outp | is pulse<br>idth is pout | e outpu<br>possibl<br>se is (L | e to se | LP out | put pin, and use for ch | er line in character unit.  anging serial/parallel of  alue.  ration of timing with CP output. |                 |

# (2-4) Cycle steal enable width register [R4]

| Address | R/W |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |    |    |              |    |    | Fund | ction            |   | Reset           |  |

|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|--------------|----|----|------|------------------|---|-----------------|--|

| 00110   | W   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |    |    |              |    |    |      |                  | 1 | 00 <sub>H</sub> |  |

|         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |    | CS | SW           |    |    |      |                  |   |                 |  |

|         |     | D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D6 | D5 | D4 | D3           | D2 | D1 | D0   | Character Number |   |                 |  |

|         |     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0  | 0  | 0  | 0            | 0  | 0  | 0    |                  |   |                 |  |

|         |     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0  | 0  | 0  | 0            | 0  | 0  | 1    | 1                |   |                 |  |

|         |     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0  | 0  | 0  | 0            | 0  | 1  | 0    | 2                |   |                 |  |

|         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |    | ,  | $\downarrow$ |    |    |      | <b>\</b>         |   |                 |  |

|         |     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  | 1  | 1  | 1            | 1  | 1  | 1    | 255              |   |                 |  |

|         |     | <ul> <li>During the horizontal synchronous term, set term of access by cycle steal method in character number unit.         Setting value of CSW sets below LPW value.     </li> <li>When reset, CSW = "00<sub>H</sub>"</li> <li>Note: Be careful with first and second byte of display data UD &lt;3:0&gt; output indefinite data when setting value of CSW is still reset (00<sub>H</sub>).         Surely CSW set over 01<sub>H</sub>.         (When select 8-bit MPU, 1 byte is indefinite.         When 16-bit and SAL: D &lt;0&gt; = 0, 2 byte are indefinite.     </li> </ul> |    |    |    |              |    |    |      |                  |   |                 |  |

# (2-5) Vertical line number register [R5]

| R/W |      | Function                     |                                             |                                                                      |                        |                                            |                                         |                                              |                                                   |     |                 |  |  |  |  |

|-----|------|------------------------------|---------------------------------------------|----------------------------------------------------------------------|------------------------|--------------------------------------------|-----------------------------------------|----------------------------------------------|---------------------------------------------------|-----|-----------------|--|--|--|--|

| W   |      |                              |                                             |                                                                      |                        |                                            |                                         |                                              |                                                   |     | F0 <sub>H</sub> |  |  |  |  |

|     |      |                              |                                             | SL                                                                   | .T                     |                                            |                                         |                                              |                                                   |     |                 |  |  |  |  |

|     | D7   | D6                           | D5                                          | D4                                                                   | D3                     | D2                                         | D1                                      | D0                                           | Vertical Line Number                              |     |                 |  |  |  |  |

|     | 0    | 0                            | 0                                           | 0                                                                    | 0                      | 0                                          | 0                                       | 0                                            | _                                                 |     |                 |  |  |  |  |

|     | 0    | 0                            | 0                                           | 0                                                                    | 0                      | 0                                          | 0                                       | 1                                            | 1                                                 |     |                 |  |  |  |  |

|     | 0    | 0                            | 0                                           | 0                                                                    | 0                      | 0                                          | 1                                       | 0                                            | 2                                                 |     |                 |  |  |  |  |

|     |      |                              |                                             | $\downarrow$                                                         | ,                      |                                            |                                         |                                              | <b>↓</b>                                          |     |                 |  |  |  |  |

|     | 1    | 1                            | 1                                           | 1                                                                    | 1                      | 1                                          | 1                                       | 1                                            | 255                                               |     |                 |  |  |  |  |

|     | • Se | tting of                     | SLT is                                      | sure                                                                 | to adju                | ist to th                                  | ne nun                                  |                                              |                                                   |     |                 |  |  |  |  |

|     |      | W D7 0 0 0 0 1 1 • SL' • Set | W D7 D6 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | D7 D6 D5  0 0 0  0 0 0  1 1 1  • SLT combine the • Setting of SLT is | W    D7   D6   D5   D4 | SLT   SLT     D7   D6   D5   D4   D3     0 | SLT   SLT   D7   D6   D5   D4   D3   D2 | SLT   SLT   D7   D6   D5   D4   D3   D2   D1 | SLT   SLT   D7   D6   D5   D4   D3   D2   D1   D0 | SLT | SLT             |  |  |  |  |

# (2-6) Display start address register [R6, R7]

| Address      | R/W |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |      |       |              |    |    | Fu | nctio | n  |    |              |    |    |    |                   | Reset             |

|--------------|-----|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------|----|----|----|-------|----|----|--------------|----|----|----|-------------------|-------------------|

| 01010        | R/W |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |      |       |              |    |    |    |       |    |    |              |    |    |    |                   | 0000 <sub>H</sub> |

| SAL          |     |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |      | SAH   |              |    |    |    |       |    | s  | AL           |    |    |    | Display Start     |                   |

|              |     | D7                                                  | D6                                                                                                                                                                                                                                                                                                                                                                                                     | O5 [ | D4 D3 | D2           | D1 | D0 | D7 | D6    | D5 | D4 | D3           | D2 | D1 | D0 | Address           |                   |

|              |     |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        | 0    | 0 0   | 0            | 0  | 0  | 0  | 0     | 0  | 0  | 0            | 0  | 0  | 0  | 0000н             |                   |

|              |     |                                                     | /[                                                                                                                                                                                                                                                                                                                                                                                                     | 0    | 0 0   | 0            | 0  | 0  | 0  | 0     | 0  | 0  | 0            | 0  | 0  | 1  | 0001 <sub>H</sub> |                   |

|              |     | /                                                   | / [                                                                                                                                                                                                                                                                                                                                                                                                    | 0    | 0 0   | 0            | 0  | 0  | 0  | 0     | 0  | 0  | 0            | 0  | 1  | 0  | 0002 <sub>H</sub> |                   |

|              |     |                                                     | / [                                                                                                                                                                                                                                                                                                                                                                                                    |      |       | $\downarrow$ |    |    |    |       |    |    | $\downarrow$ |    |    |    | <b>↓</b>          |                   |

|              |     | 1 <i>V V</i>                                        |                                                                                                                                                                                                                                                                                                                                                                                                        | 1    | 0 0   | 1            | 0  | 1  | 0  | 1     | 1  | 1  | 1            | 1  | 1  | 1  | 257F <sub>H</sub> |                   |

| 01100<br>SAH |     | <ul><li>Wh</li><li>Dissipation</li><li>Wh</li></ul> | <ul> <li>D6 and D7 output "0" when read SAH.</li> <li>It is possible to set display start address to the extent of 257F<sub>H</sub> (= 9600 address).</li> <li>Don't set over 2580<sub>H</sub>.</li> <li>When reset, SAL and SAH = "0000<sub>H</sub>"</li> <li>Display start address is established by the writing data to SAH register. Even if only change SAL, surely set SAH after SAL.</li> </ul> |      |       |              |    |    |    |       |    |    |              |    |    |    |                   |                   |

# (2-7) M cycle variable register [R8]

| Address | R/W                                                                                                                        |             |                                                                                          |       |         |        |        |        |          | Function                             | Reset           |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------|-------|---------|--------|--------|--------|----------|--------------------------------------|-----------------|--|--|--|--|

| 01110   | W                                                                                                                          |             |                                                                                          |       |         |        |        |        |          |                                      | 00 <sub>H</sub> |  |  |  |  |

|         |                                                                                                                            |             |                                                                                          |       | N       | IT     |        |        |          |                                      |                 |  |  |  |  |

|         |                                                                                                                            | D7          | D6                                                                                       | D5    | D4      | D3     | D2     | D1     | D0       | Cycle of M                           |                 |  |  |  |  |

|         |                                                                                                                            | 0           | 0                                                                                        | 0     | 0       | 0      | 0      | 0      | 0        | Toggle change at every 1 frame.      |                 |  |  |  |  |