# MITSUBISHI < DIGITAL ASSP>

# M66230P/FP

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

#### DESCRIPTION

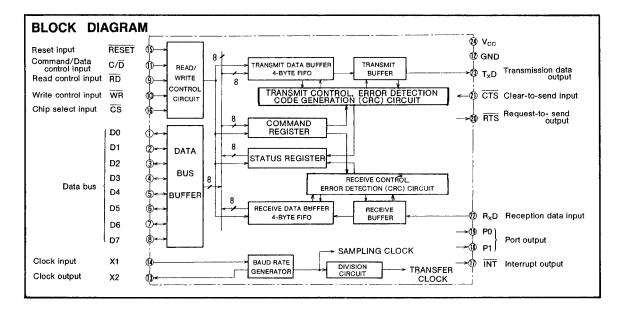

The M66230P/FP is an integrated circuit for asynchronous serial data communications. It is used in combination with an 8-bit micro-processor and is produced using the silicon-gate CMOS technology.

#### **FEATURES**

- Baud rate generator 500kbps (max)

- 4-byte FIFO data buffer for transmission and reception

- Error detection : CRC-CCITT, parity, overrun, and framing

- Wakeup function

- Transmisson / reception data format (number of bits) Start bit 1

- Data bit 8 Wakeup bit 1 or nil Parity bit 1 or nil Stop bit 1 or 2

- Access time ta (RD-D) : 100ns (max)

- High output current I<sub>OH</sub>=-24mA, I<sub>OL</sub>=24mA T<sub>x</sub>D, RTS, P0, P1 pins

- Schmitt triggered input RxD,CTS,RESET pins

### **APPLICATION**

Data communication control

### FUNCTION

The M66230P/FP is a UART (Universal Asynchronous Receiver/Transmitter) and is used in the peripheral circuit of a MPU. The M66230 receives parallel data, converts into serial format, and then transmits the serial data via the  $T_xD$  pin. The device also receives data via the  $R_xD$  pin from ex-

ternal circuits and converts it into parallel format, and sends the parallel data via the data bus.

### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

#### **OPERATION**

The M66230 is interfaced to a system bus and provides all functions needed for data communication.

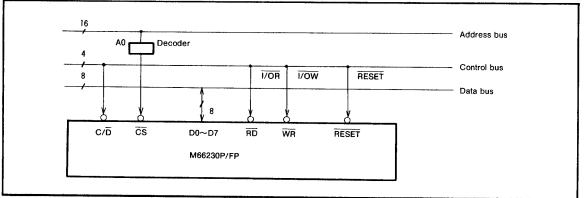

Fig. 1 Interface between the M66230 and MPU system bus.

When using the M66230, it is necessary to program the initial setting, baud rate, character length, CRC, parity, in accordance with the communication system. Once programmed, the communcation system functions are executed continuously.

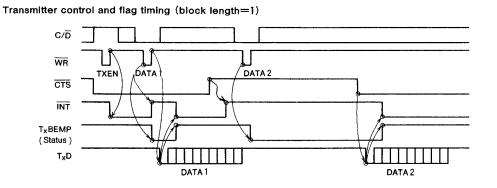

When initial setting of M66230 is completed, data communication becomes possible. When the transmitter is transmit-enabled (TXEN) by a command instruction and  $\overline{\text{CTS}}$  is low-level, data transfer starts up. If these conditions are not satisfied, data transmission is not executed. Reception is possible when the receiver is receive -enabled (RXEN) by a command instruction.

The MPU is able to read data when the interrupt output,  $\overline{INT}$ , goes low by packet end (PE) or buffer full (BF).

While receiving data, the M66230 checks for errors and provides status information. It checks for four types of errors : CRC, parity, overrun and framing errors. When an error occurs, M66230 continues operation. The error status is maintained until the error reset, (ER) is modified by a command instruction.

The access method of the M66230 is shown Table 1.

| C/D | RD | WR | CS | M66230 operation                      | MPU operation       |

|-----|----|----|----|---------------------------------------|---------------------|

| L   | L  | н  | L  | Data bus←Receiving data buffer (FIFO) | Read receive data   |

| L   | н  | Ľ  | L  | Data bus→Transmit data buffer (FIFO)  | Write transmit data |

| н   | L  | н  | L  | Data bus←Status register              | Read the status     |

| н   | н  | L  | L  | Data bus→Command register             | Write the command   |

| ×   | н  | н  | L  | Data bus : high impedance             |                     |

| ×   | ×  | ×  | н  | Data bus : high impedance             |                     |

TABLE 1 Access method of the M66230.

Note : X="L" or "H"

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

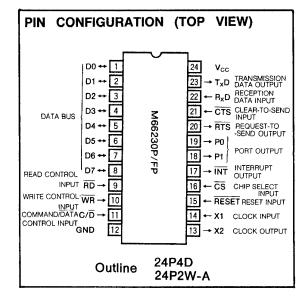

### **PIN DESCRIPTIONS**

| Pin           | Name                           | 1/0          | Function                                                                                                                                                                                                                                                         |

|---------------|--------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1            | Clock input                    | Input        | A crystal is externally connected to these pins for generating an internal clock. An external clock signal can                                                                                                                                                   |

| X2            | Clock output                   | output       | be input to X1 instead of a crystal. Then X2 output opened.                                                                                                                                                                                                      |

| RESET         | Reset input                    | Input        | This reset is a master reset, therefore commands should be loaded after the reset.                                                                                                                                                                               |

| <del>cs</del> | Chip select<br>input           | Input        | A low level signal on the chip select input enables the M66230. The device can not be accessed when the signal is high-level.                                                                                                                                    |

| C/D           | Command/<br>Data control input | Input        | This signal distinguishes whether the information on the M66230 data bus is data, command or status in-<br>formation. When the signal is high-level, the data bus has command or status information. When the signal<br>is low-level, the data bus has data.     |

| RD            | Read control input             | Input        | The receiving data or status information is output to the data bus from the M66230 by a low-level signal.                                                                                                                                                        |

| WR            | Write control input            | Input        | The data or command output from the MPU is written to the M66230 by a low-level signal.                                                                                                                                                                          |

| D0~D7         | Data bus                       | Input/output | This is an 8-bit bi-directional bus buffer. Command, status information, and transfer data are transferred to/from the MPU via this data bus buffer.                                                                                                             |

| INT           | Interrupt output               | Output       | This is used as an interrupt request to MPU. The interrupt request is generated when the receive FIFO is full, the transmit FIFO is empty, or the block reception is complete. D2 bit of command 6 controls the switching of low-level and high-level interrupt. |

| RxD           | Reception data input           | Input        | The serial data is sent to this pin.                                                                                                                                                                                                                             |

| TxD           | Transmission data output       | Output       | The serial data is transmitted from this pin.                                                                                                                                                                                                                    |

| P0            | Port output                    | Output       | This is an ordinary port pin. This pin is controlled by the D0 bit of command 6.                                                                                                                                                                                 |

| P1            | Port output                    | Output       | This pin has the same function as that of P0 pin and provides information of packet transmission's comple-<br>tion. The switching of this function is controlled by command 6, D1 bit.                                                                           |

| CTS           | Clear-to-send<br>input         | Input        | When the TXEN bit (D0) of command 4 is set to 1 and the $\overline{\text{CTS}}$ input is low-level, serial data is sent from the TxD pin. This is used as the clear-to-send signal.                                                                              |

| RTS           | Request-to-send<br>output      | Output       | This is used as the request-to-send signal. This pin is controlled by the D3 bit of command 4.                                                                                                                                                                   |

#### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

# DISCRIPTION OF FUNCTION Baud rate generator

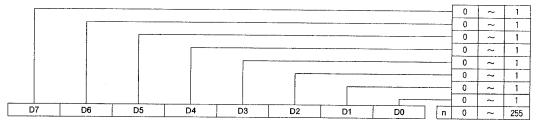

The 8-bit programmable divider (baud rate generator) generates the baud rate for transmit or receive. The division rate is (n+1) with a range of  $n=0\sim 255$ . The baud rate is calculated by the following formula :

#### baud rate=

$f(X1)/(prescaler division rate (2 or 32) \cdot baud rate generator division rate (n+1) \cdot 16).$

The prescaler division rate is set by the D0 bit of command 1. The baud rate generator division rate is set by command 2. Example as follows :

$9600bps = (9.8304MHz)/(2 \cdot (31+1) \cdot 16)$

where prescaler division rate is 2 and baud rate division rate is 31.

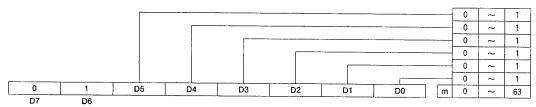

#### Block length counter

The M66230 can handle multiple-bytes of data as one block (packet).

Therefore, CRC of bytes is possible. The block length counter is a 6-bit programmable counter. The block length is (m+1) bytes with the allowed values of  $m=0\sim63$ .

#### Transmit data buffer (FIFO)

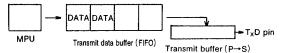

The transmit data buffer (FIFO) consists of 4-bytes. The transmit data buffer (FIFO) functions according to the block length.

#### Block length=1~3

When the transmit data buffer (FIFO) becomes empty (buffer empty) and  $\overline{INT}$  is set to low-active, the interrupt output  $\overline{INT}$  is set to a low-level. The MPU verifies the buffer is empty when the D2 bit of the status 1 information is read. The MPU should write the block length data to the transmit data buffer (FIFO) at this moment.

When a block of data is written to the transmit data buffer  $(FIFO),\overline{CTS}$  is low-level and TXEN is high-level, the data in the transmit data buffer (FIFO) is sent to the transmit buffer. If  $\overline{CTS}$  is high-level while data is transmitted, all data is transmitted (including the data in the transmit data buffer (FIFO)). When the buffer becomes empty, the data in the transmit data buffer (FIFO) is not be sent to the transmit buffer until MPU writes a new block of data to the transmit data buffer (FIFO). The MPU can not write new data to the transmit data buffer (FIFO) until the buffer becomes empty.

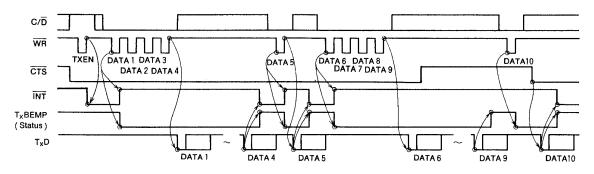

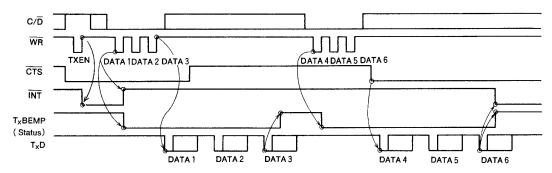

Example : Block length=2

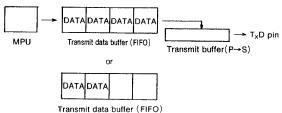

Block length=4 or more

When the transmit data buffer (FIFO) becomes empty and  $\overline{INT}$  is set low-active, the interrupt output  $\overline{INT}$  becomes low. The MPU verifies the buffer is empty by reading the D2 bit of the status 1 information.

When this happens, the MPU should write the 4-bytes of data to the transmit data buffer (FIFO). The data in the transmit data buffer (FIFO) is sent to the transmit buffer, when  $\overline{\text{CTS}}$  is low-level and TXEN is high-level. When the number of bytes from the MPU becomes less than 4 at the last stage of the block transmission, the same operation should be made as the block length=1~3.

When the buffer becomes empty, the data in the transmit data buffer (FIFO) is not be sent to the transmit buffer until MPU writes data of the fixed block length to the transmit data buffer (FIFO). The MPU cannot write data to the transmit data buffer (FIFO) until the buffer becomes empty.

Example : Block length=6

### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

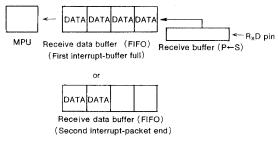

#### Receive data buffer (FIFO)

The receive data buffer (FIFO) consists of 4-bytes. The receive data buffer (FIFO) functions according to the block length.

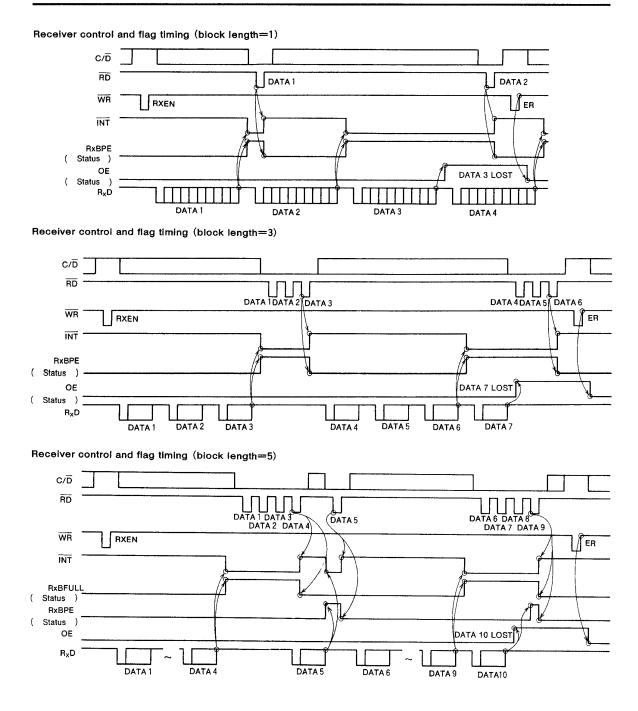

#### Block length=1~3

When the data of the block length is received and  $\overline{INT}$  is set to low-level, the interrupt output  $\overline{INT}$  becomes lowlevel. The MPU acknowledges the packet end by setting the D0 bit of the status 1 information.

In this case, the MPU should read all data from the receive data buffer (FIFO).

At the packet end, the data from the receive buffer cannot be transmitted to the receive data buffer (FIFO) until the MPU reads all data in the receive data buffer (FIFO). The MPU cannot read data in the receive data buffer until the packet end.

Example : Block length=2

Block length=4 or more

When 4-byte data enters the receive data buffer (FIFO) (buffer full) and  $\overline{INT}$  is set to low-active, the interrupt output  $\overline{INT}$  becomes low-level. The MPU acknowledges the buffer full status by setting the D1 bit of the status 1 information.

In this case, the MPU should read all data in the receive data buffer (FIFO).

When the last data enters the receive data buffer (FIFO), the packet end becomes the same operation as for  $1 \sim 3$  byte block length. If the block length is a multiple of four, the D0 and D1 bits of the status 1 information are set when the last data enters the receive data buffer (FIFO). At packet end or buffer full, the new data cannot be transferred from the receive buffer to the receive data buffer (FIFO). The MPU cannot read data in the receive data buffer (FIFO) until packet end or buffer full occurs.

# SUPPLEMENTARY DESCRIPTION

FIFO

The major purpose is not to interrupt the MPU by each character. The MPU is interrupted when :

Transmit data buffer (FIFO) empty

Receive data buffer (FIFO) full or packet end

The MPU interruption interval is as follows :

Approximately  $90\mu s$  (min) until the FIFO becomes full at

500kbps. Approximately 36.7ms (min) until the FIFO becomes full at 1.2kbps.

Read/write operation by the MPU should be made for all data in FIFO at once.

### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

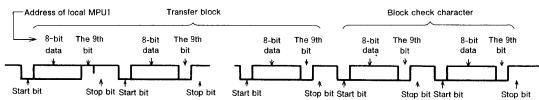

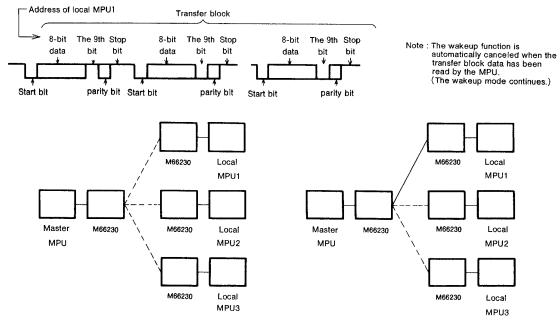

#### Wakeup

The wakeup mode of the M66230 can be set by setting the D2 bit of command 4 to "1". In wakeup mode, a 9th bit is automatically added (the wakeup bit).

Only the 9th bit of the first byte is "1", and the remainer blocks 9th bits are set to "0".

The wakeup is used when one master MPU and multiple local MPU are connected by serial I/O.

Examples of wakeup are shown below.

Initial setting

The initial setting should be made by the input of each command.

2 Wakeup mode

The wakeup mode of the M66230 is activated by setting D2 bit of the command 4 to "1". Command 5 can be input as the second byte of command 4 by setting D2 bit of the command 4 to "1" and each address is input. In the wakeup mode, the 9th bit is automatically added. Others remain the same.

③ Wakeup and data transfer (between master MPU and local MPU1)

Data is transmitted from the master MPU to each local MPU.

The first byte should hold the address of the local MPU. (in this case local MPU1.)

Each local M66230 checks the data (address) against command 5 (each address) when the first byte (address) is received. the M66230 which matches the address starts to accept the following data (wakeup). the M66230 which does not match the address, only accepts data, where the 9th bit is "1".

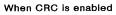

#### When parity is enabled

## A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

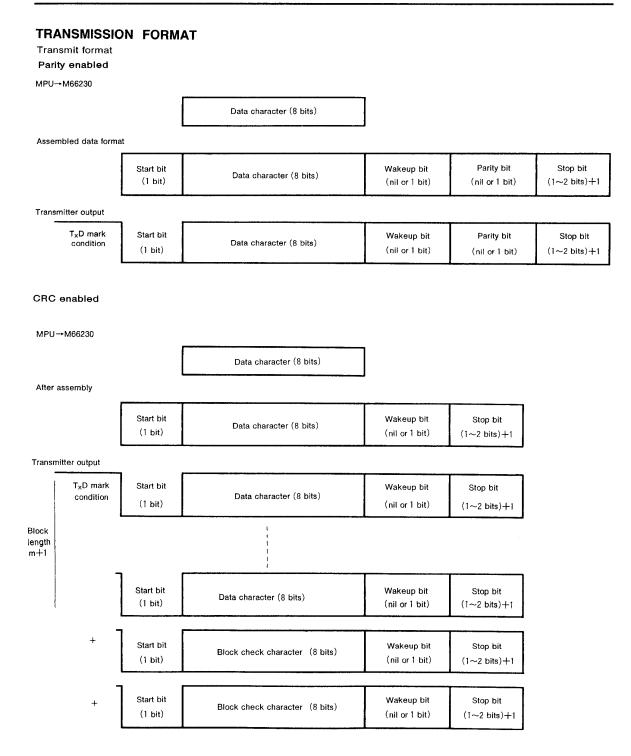

### • Error detection

#### Parity error

When a parity error occurs, D5 bit of status 1 information is set. The data is send to the receive data buffer (FIFO).

#### Framing error

When a framing error occurs, D3 bit of the status 1 information is set. The data is sent to the receive data buffer (FIFO).

#### Overrun error

When data is received before all data in the receive data buffer (FIFO) has been read by MPU, D4 bit of the status 1 information is set as an overrun error.

In this case, the new data in the receive buffer are lost.

#### CRC error

When an error occurs after receiving block check character, D6 bit of the status 1 information is set.

The above error information is maintained until D4 bit of command 4 is set.

#### SUPPLEMENTARY DESCRIPTION

Comparison between parity check and CRC Parity check

Parity check needs only one additional bit and is highly efficient. The formula is straightforward, and includes even parity and odd parity checks. In both cases, one bit is added.

CRC

The CRC polynominal expression is CRC-CCITT  $X^{16} + X^{12} + X^5 + 1.$

CRC deals with data characters in transmitted or received blocks. (Start, stop and wakeup bits are excluded.)

When the CRC is enabled, the transmit and receive data consists of block length  $(1 \sim 64 \text{ bytes}) + 2 \text{ bytes}$  (block check characters). The following table shows the comparision between parity check and CRC.

| Parity check | Burst error is not detected.<br>(50% of which can be de-<br>tected.)               |

|--------------|------------------------------------------------------------------------------------|

| CRC          | Burst error can be detected<br>(Burst error detection rate is<br>more than 99.9%.) |

#### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

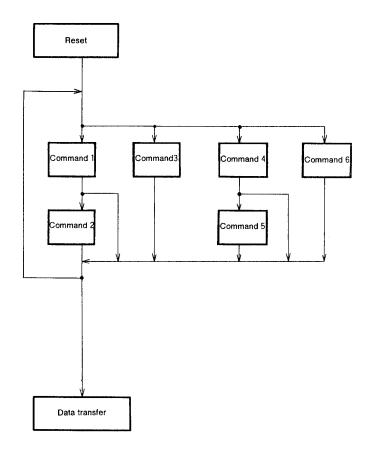

#### PROGRAMMING

The command must be loaded first to the M66230 by the MPU before data communication. M66230 has 6 command registers.

Data transfer is possible when commands have been loaded to these command registers after reset.

The flowchart of the initial setting is shown in the following diagram.

Flowchart of the M66230 initial setting.

### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

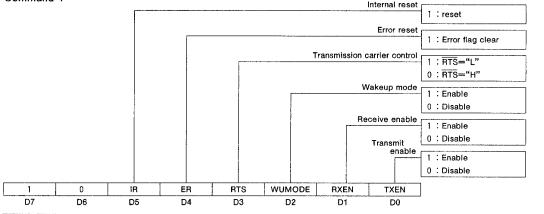

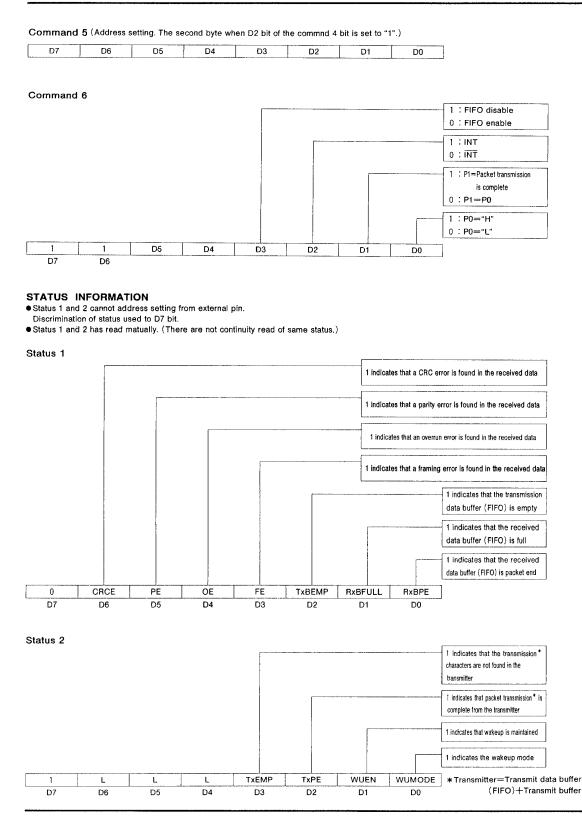

#### **COMMAND-INSTRUCTION FORMAT**

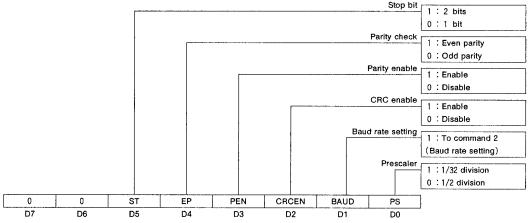

The commands are decoded by D7 and D6. Command1

Note 1 : Priority is given to parity enable, if parity enable and CRC enable are both "1" (D3, D2=1). Attention : TxD output wave is Stop bit (D5) setup value +1 (always)

Command 2 (Baud rate setting. The second byte when D1 bit of the command 1 is set to "1")

Command 3 (Block length setting)

Command 4

### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

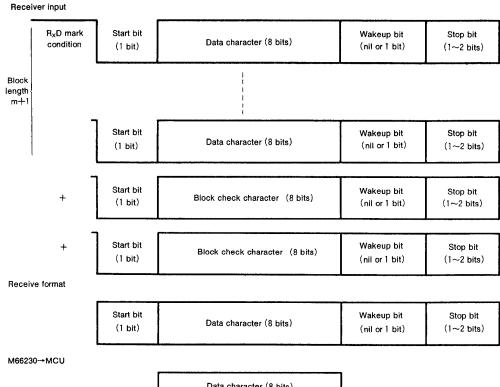

### TRANSMISSION FORMAT

**Receive format**

Parity enabled

Receiver input

| R <sub>x</sub> D mark | Start bit | Data character(8 bits) | Wakeup bit     | Parity bit     | Stop bit   |

|-----------------------|-----------|------------------------|----------------|----------------|------------|

| condition             | (1 bit)   |                        | (nil or 1 bit) | (nil or 1 bit) | (1-2 bits) |

| Receive format        |           |                        |                |                |            |

| Start bit | Data character (8 bits) | Wakeup bit     | Parity bit     | Stop bit   |

|-----------|-------------------------|----------------|----------------|------------|

| (1 bit)   |                         | (nil or 1 bit) | (nil or 1 bit) | (1~2 bits) |

M66230→MCU

| Data character (8 bits) |  |

|-------------------------|--|

|-------------------------|--|

#### **CRC** enabled

Data character (8 bits)

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

### **ABSOLUTE MAXIMUM RATINGS** ( $T_a = -40 \sim +85$ °C, unless otherwise noted)

| Symbol | Parameter           | Conditions                           | Ratings                   | Unit |

|--------|---------------------|--------------------------------------|---------------------------|------|

| Vcc    | Supply voltage      |                                      | -0.5~+7.0                 | v    |

| Vi     | Input voltage       | Value using the GND pin as reference | -0.5~Vcc+0.5              | v    |

| Vo     | Output voltage      |                                      | -0.5~V <sub>cc</sub> +0.5 | v    |

| Pd     | Power dissipation   | Actually mounted                     | 500                       | mW   |

| Tstg   | Storage temperature |                                      | -65~+150                  | °C   |

#### RECOMMENDED OPERATING CONDITIONS (Ta=-40~+85°C)

| Sumbal | Parameter             |     | Limits |     | Unit |

|--------|-----------------------|-----|--------|-----|------|

| Symbol | Parameter             | Min | Тур    | Max | Unit |

| Vcc    | Supply voltage        | 4.5 | 5.0    | 5.5 | V    |

| GND    | Ground                |     | 0      |     | V    |

| Topr   | Operating temperature | -40 |        | +85 | Ĵ    |

#### **ELECTRICAL CHARACTERISTICS** ( $\tau_a = -40 \sim +85$ °C, $v_{cc} = 5V \pm 10\%$ , GND=0V, unless otherwise noted)

| Symbol           | Parameter                           | Test conditions                 |                      | Limits |                      |      |

|------------------|-------------------------------------|---------------------------------|----------------------|--------|----------------------|------|

| Symbol           | Parameter                           |                                 | Min                  | Тур    | Max                  | Unit |

| VIH              | High-level input voltage            |                                 | 2.0                  |        |                      | v    |

| VIL              | Low-level input voltage             | RD, WR, C/D, CS, D0~D/          |                      |        | 0.8                  | v    |

| VIH              | High-level input voltage            | V4                              | V <sub>cc</sub> ×0.8 |        |                      | v    |

| VIL              | Low-level input voltage             | X1                              |                      |        | V <sub>cc</sub> ×0.2 | v    |

| $V_{\tau+}$      | Positive threshold voltage          |                                 |                      |        | 2.4                  | v    |

| V <sub>7</sub>   | Negative threshold voltage          | R <sub>x</sub> D, CTS, RESET    | 0.6                  |        |                      | v    |

| V <sub>H</sub>   | Hysteresis width                    |                                 | 0.2                  |        |                      | v    |

|                  | I <sub>OH</sub> ==−8mA              | I <sub>OH</sub> =-8mA INT,D0~D7 |                      |        |                      | v    |

| V <sub>он</sub>  | High-level output voltage           | IOH=-24mA TxD, RTS, PO, P1      | V <sub>cc</sub> -0.8 |        |                      | v    |

| ~~~~~            |                                     | I <sub>OL</sub> =8mA INT,D0~D7  |                      |        | 0.55                 | v    |

| Vol              | Low-level output voltage            | IoL=24mA TxD, RTS, PO, P1       |                      |        | 0.55                 | v    |

| l <sub>iH</sub>  | High-level input current            | VI=VCC                          |                      |        | 1.0                  | μA   |

| կլ               | Low-level input current             | VI=GND                          |                      |        | -1.0                 | μA   |

| l <sub>ozн</sub> | Off-state high-level output current | V <sub>o</sub> =V <sub>cc</sub> |                      |        | 5.0                  | μA   |

| lozi             | Off-state low-level output current  | V <sub>o</sub> =GND             |                      |        | -5.0                 | μA   |

| loc              | Static supply current               | VI=VCC, GND                     |                      |        | 40                   | mA   |

| C,               | Input capacitance                   |                                 |                      |        | 10                   | pF   |

| CI/O             | I/O capacitance                     |                                 |                      |        | 20                   | pF   |

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

| Symbol               | Dava                          |                                      | Test seedilises |      | Limits |     |      |

|----------------------|-------------------------------|--------------------------------------|-----------------|------|--------|-----|------|

| Symbol               | Parameter                     |                                      | Test conditions | Min  | Тур    | Max | Unit |

| t <sub>c1(x1)</sub>  | Clock frequency               |                                      |                 | 62.5 |        |     | ns   |

| t <sub>WH1(X1)</sub> | Clock high-level pulse width  | (Except Wakeup, CRC mode)            |                 | 30   |        |     | ns   |

| t <sub>WL1(X1)</sub> | Clock low-level pulse width   |                                      |                 | 30   |        |     | ns   |

| t <sub>C2(X1)</sub>  | Clock frequency               |                                      |                 | 80   |        |     | ns   |

| t <sub>WH2(X1)</sub> | Clock high-level pulse width  | (Wakeup, CRC mode)                   |                 | 38   |        |     | ns   |

| twL2(X1)             | Clock low-level pulse width   |                                      |                 | 38   |        |     | ns   |

| t <sub>r(x1)</sub>   | Clock rise time               |                                      |                 |      |        | 20  | ns   |

| t <sub>f(x1)</sub>   | Clock fail time               |                                      |                 |      |        | 20  | ns   |

| tsu(A-R)             | Address setup time before re  | ad $(\overline{CS}, C/\overline{D})$ |                 | 0    |        |     | ns   |

| th(R-A)              | Address hold time after read  | $(\overline{CS}, C/\overline{D})$    |                 | 0    |        |     | ns   |

| t <sub>W(R)</sub>    | Read pulse width              |                                      |                 | 100  |        |     | ns   |

| tsu(A-W)             | Address setup time before w   | rite (CS, C/D)                       |                 | 0    |        |     | ns   |

| th(w-A)              | Address hold time after write | $(\overline{CS}, C/\overline{D})$    |                 | 0    |        |     | ns   |

| t <sub>w</sub> (₩)   | Write pulse width             |                                      |                 | 100  |        |     | ns   |

| tsu(DQ-W)            | Data setup time before write  |                                      |                 | 50   |        |     | ns   |

| th(w-09)             | Data hold time after write    |                                      |                 | 5    |        |     | ns   |

| trec(RESET)          | Recoverry time between writ   | e                                    |                 | 100  |        |     | ns   |

| tw(RESET)            | Reset pulse width             |                                      |                 | 100  |        |     | ns   |

#### TIMING REQUIREMENTS ( $T_a = -40 \sim +85^{\circ}C$ , $V_{cc} = 5V \pm 10\%$ , $V_{ss} = 0V$ , unless otherwise noted)

#### SWITCHING CHARACTERISTICS ( $T_a = -40 \sim +85$ °C, $V_{cc} = 5V \pm 10\%$ , $V_{ss} = 0V$ , unless otherwise noted)

| 0                        | Bassantas                                                   | <b>-</b>        |     | Limits |     | 11.04 |

|--------------------------|-------------------------------------------------------------|-----------------|-----|--------|-----|-------|

| Symbol                   | Parameter                                                   | Test conditions | Min | Тур    | Max | Unit  |

| tpzh(A-DQ)               | Data output enable time after read                          |                 |     | 43     | 100 | ns    |

| tPZL(A-DQ)               | Data output enable time after read                          |                 |     | 52     | 100 | ns    |

| tPHZ(A-DQ)               | Data output disable time after read                         |                 |     | 33     | 85  | ns    |

| tPLZ(A-DQ)               | Data output disable time after read                         |                 |     | 32     | 85  | ns    |

| tPLH(R-INT)              | INT output propagation time after read data                 |                 |     | 62     | 170 | ns    |

| tPHL(R-INT)              | INT output propagation time after read data                 |                 |     | 63     | 170 | ns    |

| t <sub>PLH</sub> (W-INT) | INT output propagation time after write data                |                 |     | 54     | 150 | ns    |

| tPHL(W-INT)              | INT output propagation time after write data                |                 |     | 54     | 150 | ns    |

| t <sub>PLH</sub> (w-int) | INT output propagation time after write command (command 4) |                 |     | 33     | 100 | ns    |

| tPHL(W-INT)              | INT output propagation time after write command (command 4) |                 |     | 35     | 100 | ns    |

| tPLH(W-INT)              | INT output propagation time after write command (command 6) |                 |     | 28     | 100 | ns    |

| tPHL(W-INT)              | INT output propagation time after write command (command 6) |                 |     | 30     | 100 | ns    |

| tPLH(W-PO)               | P0 output propagation time after write command              |                 |     | 25     | 70  | ns    |

| tPHL(W-PO)               | P0 output propagation time after write command              |                 |     | 28     | 70  | ns    |

| t <sub>PLH</sub> (W-P1)  | P1 output propagation time after write command              |                 |     | 26     | 70  | ns    |

| t <sub>PHL</sub> (W-P1)  | P1 output propagation time after write command              |                 |     | 28     | 70  | ns    |

| tPLH(W-RTS)              | RTS output propagation time after write command             |                 |     | 25     | 70  | ns    |

| tPHL(W-RTS)              | RTS output propagation time after write command             |                 |     | 27     | 70  | ns    |

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

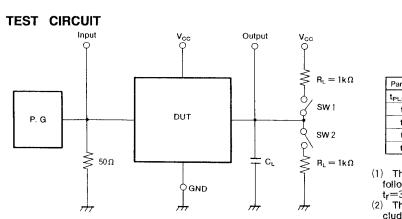

|                                     | the second s |        |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|

| Parameter                           | SW1                                                                                                            | SW2    |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Open                                                                                                           | Ореп   |

| t <sub>PLZ</sub>                    | Closed                                                                                                         | Open   |

| t <sub>PHZ</sub>                    | Open                                                                                                           | Closed |

| t <sub>PZL</sub>                    | Closed                                                                                                         | Open   |

| t <sub>PZH</sub>                    | Open                                                                                                           | Closed |

The pulse generator (PG) has the following characteristics (10%~90%) tr=3ns, tr=3ns

The capacitance C<sub>L</sub> = 150pF in-cludes stray wiring capacitance and the probe input capacitance.

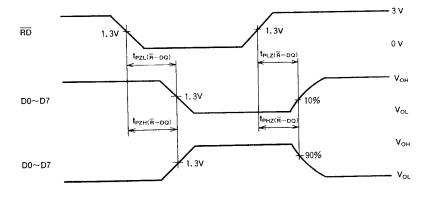

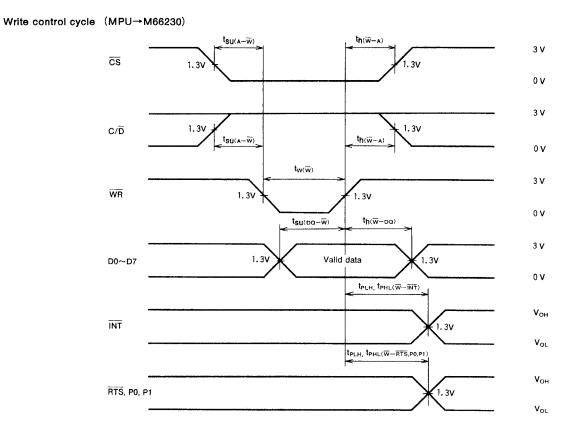

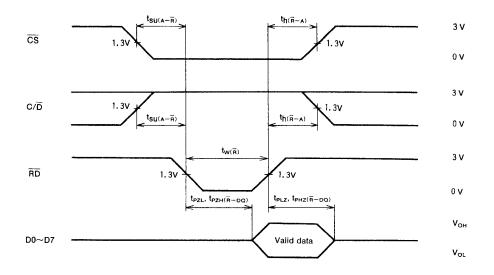

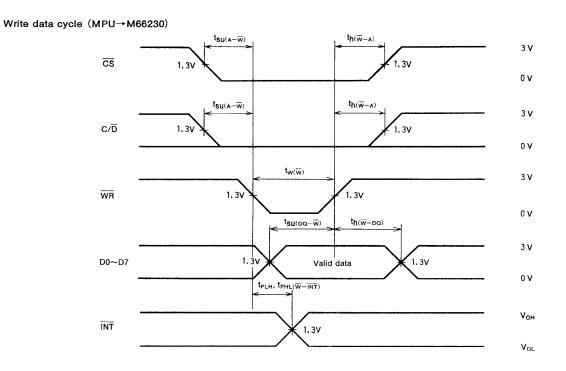

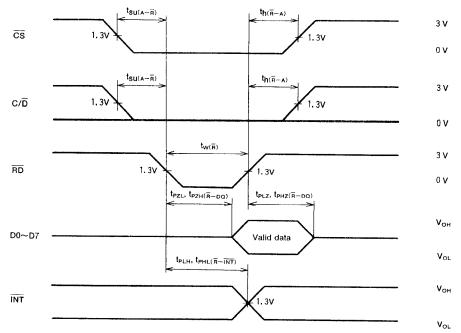

### TIMING DIAGRAM

Input/output waveform at read data and read status

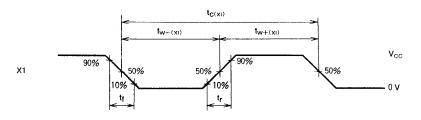

**Clock Timing**

MITSUBISHI (DIGITAL ASSP)

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

Read control cycle (M66230→MPU)

### A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

Read data cycle (M66230→MPU)

# A<sup>2</sup>RT(ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

Transmitter control and flag timing (block length=3)

Transmitter control and flag timing (block length =5)