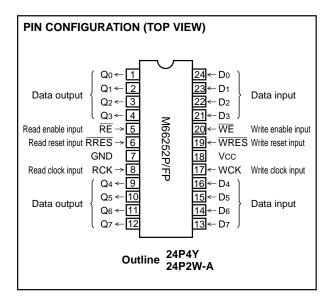

1152 x 8-BIT LINE MEMORY (FIFO)

#### **DESCRIPTION**

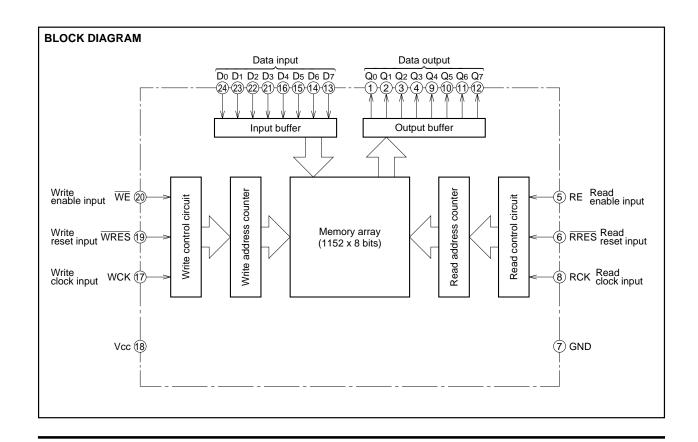

The M66252P/FP is a high-speed line memory with a FIFO (First In First Out) structure of 1152-word  $\times$  8-bit configuration which uses high-performance silicon gate CMOS process technology.

It has separate clock, enable and reset signals for write and read and is most suitable as a buffer memory between devices with different data processing throughput.

#### **FEATURES**

| Memory construction                           |                 |

|-----------------------------------------------|-----------------|

| 1152words x 8bits                             |                 |

| High-speed cycle                              | 50ns (min.)     |

| High-speed access                             | 40ns (max.)     |

| Output hold                                   | 5ns (min.)      |

| · Fully independent, asynchronous write       | and read opera- |

| tions                                         |                 |

| <ul> <li>Variable-length delay bit</li> </ul> |                 |

| • Output                                      | 3-state         |

#### **APPLICATION**

Digital photocopiers, high-speed facsimiles, laser beam printers.

# M66252P/FP

### 1152 x 8-BIT LINE MEMORY (FIFO)

#### **FUNCTION**

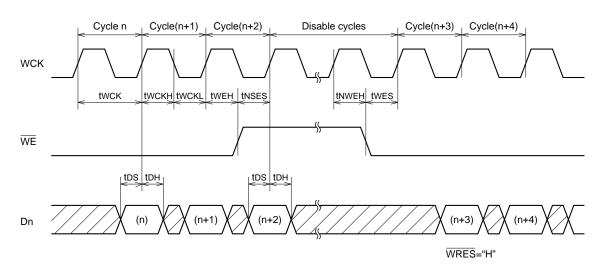

When the status of write enable input  $\overline{WE}$  is "L," data on Do thru D7 are written on the memory synchronously with write clock input WCK rise edges. At this time, write address counter executes counting.

The following write-related operations are also performed synchronously with WCK rise edges.

When  $\overline{\text{WE}}$  is "H," writing on memory is inhibited, and write address counter stops counting.

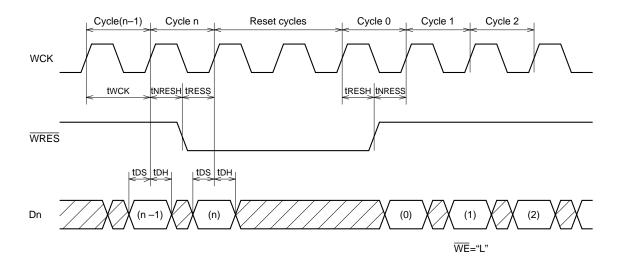

When write reset input  $\overline{\text{WRES}}$  is "L," write address counter is initialized.

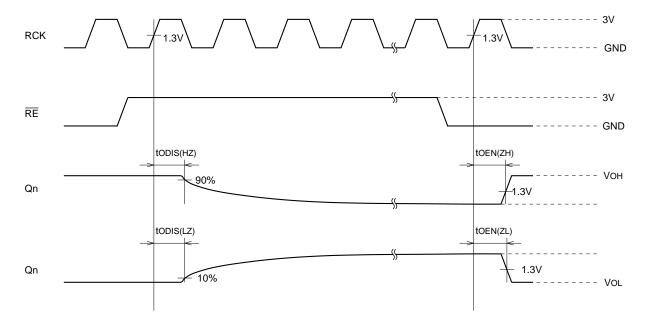

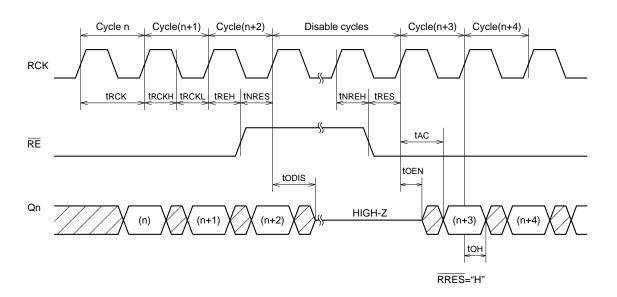

When read enable input  $\overline{RE}$  is "L," data on memory are output to Q0 thru Q7 synchronously with read clock input RCK rise edges. At this time, read address counter executes counting.

The following read-related operations are also performed synchronously with RCK rise edges.

When  $\overline{RE}$  is "H," reading from memory is inhibited, and read address counter stops counting. The status of Qo thru Q7 becomes high-impedance.

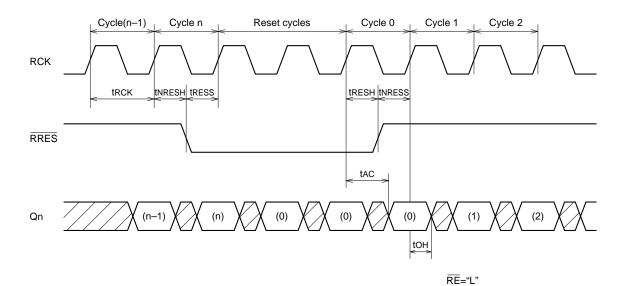

When read reset input RRES is "L," read address counter is initialized.

#### ABSOLUTE MAXIMUM RATINGS (Ta = -20 ~ 70°C unless otherwise noted)

| Symbol | Parameter           | Conditions         | Ratings             | Unit |

|--------|---------------------|--------------------|---------------------|------|

| Vcc    | Supply voltage      |                    | −0.5 ~ <b>+</b> 7.0 | V    |

| VI     | Input voltage       | Reference pin: GND | -0.5 ~ Vcc + 0.5    | V    |

| Vo     | Output voltage      |                    | -0.5 ~ Vcc + 0.5    | V    |

| Pd     | Power dissipation   | Ta = 25°C          | 550 (Note 1)        | mW   |

| Tstg   | Storage temperature |                    | −65 ~ 150           | °C   |

Note 1: Ta  $\geq$  62°C are derated at -8.8mW/°C (24P4Y) Ta  $\geq$  51°C are derated at -7.5mW/°C (24P2W)

#### RECOMMENDED OPERATIONAL CONDITIONS

| Cymbol           | Dorometer           |      | l lmit |      |      |  |

|------------------|---------------------|------|--------|------|------|--|

| Symbol Parameter |                     | Min. | Тур.   | Max. | Unit |  |

| Vcc              | Supply voltage      | 4.5  | 5      | 5.5  | V    |  |

| GND              | Supply voltage      |      | 0      |      | V    |  |

| Topr             | Ambient temperature | -20  |        | 70   | °C   |  |

### **ELECTRICAL CHARACTERISTICS** (Ta = $-20 \sim 70$ °C, Vcc = $5V\pm10\%$ , GND = 0V)

| Cumah al | Daramatar                                | Test conditions -                                  |                                          | Limits    |      |      | 1.124 |

|----------|------------------------------------------|----------------------------------------------------|------------------------------------------|-----------|------|------|-------|

| Symbol   | Parameter                                |                                                    |                                          | Min.      | Тур. | Max. | Unit  |

| VIH      | "H" input voltage                        |                                                    |                                          | 2.0       |      |      | V     |

| VIL      | "L" input voltage                        |                                                    |                                          |           |      | 0.8  | V     |

| Voн      | "H" output voltage                       | IOH = -4m                                          | ıΑ                                       | Vcc - 0.8 |      |      | V     |

| Vol      | "L" output voltage                       | IOL = 4mA                                          | ı                                        |           |      | 0.55 | V     |

| Іін      | "H" input current                        | VI = VCC                                           | WE, WRES, WCK, RE,<br>RRES, RCK<br>D0~D7 |           |      | 1.0  | μА    |

| lıL      | "L" input current                        | Vı = GND                                           | WE, WRES, WCK, RE, RRES, RCK D0~D7       |           |      | -1.0 | μА    |

| lozh     | "H" output current under "off" condition | Vo = Vcc                                           |                                          |           |      | 5.0  | μΑ    |

| lozL     | "L" output current under "off" condition | Vo = GND                                           |                                          |           |      | -5.0 | μΑ    |

| Icc      | Average supply current during operation  | VI = VIH, VIL, Outputs are open twck, tRck = 100ns |                                          |           |      | 100  | mA    |

| Сі       | Input capacitance                        | f = 1MHz                                           |                                          |           |      | 10   | pF    |

| Со       | Output capacitance under "off" condition | f = 1MHz                                           |                                          |           |      | 15   | pF    |

1152 x 8-BIT LINE MEMORY (FIFO)

### SWITCHING CHARACTERISTICS (Ta = -20 ~ 70°C, Vcc = 5V±10%, GND = 0V)

| Symbol | Parameter           | Limits |      |      | Unit |

|--------|---------------------|--------|------|------|------|

|        |                     | Min.   | Тур. | Max. | Unit |

| tAC    | Access time         |        |      | 40   | ns   |

| tон    | Output hold time    | 5      |      |      | ns   |

| toen   | Output enable time  | 5      |      | 40   | ns   |

| todis  | Output disable time | 5      |      | 40   | ns   |

## TIMING CHARACTERISTICS ( $Ta = -20 \sim 70^{\circ}C$ , $Vcc = 5V\pm10\%$ , GND = 0V)

| Cumbal | Devenuetes                                               |      | Limits |      |      |

|--------|----------------------------------------------------------|------|--------|------|------|

| Symbol | Parameter                                                | Min. | Тур.   | Max. | Unit |

| twcĸ   | Write clock (WCK) cycle time                             | 50   |        |      | ns   |

| twckh  | Write clock (WCK) "H" pulse width                        | 25   |        |      | ns   |

| twckl  | Write clock (WCK) "L" pulse width                        | 25   |        |      | ns   |

| trck   | Read clock (RCK) cycle time                              | 50   |        |      | ns   |

| trckh  | Read clock (RCK) "H" pulse width                         | 25   |        |      | ns   |

| trckl  | Read clock (RCK) "L" pulse width                         | 25   |        |      | ns   |

| tDS    | Input data setup time (in response to WCK)               | 15   |        |      | ns   |

| tDH    | Input data hold time (in response to WCK)                | 5    |        |      | ns   |

| tress  | Reset setup time (in response to WCK and RCK)            | 15   |        |      | ns   |

| tresh  | Reset hold time (in response to WCK and RCK)             | 5    |        |      | ns   |

| tNRESS | Reset non-select setup time (in response to WCK and RCK) | 15   |        |      | ns   |

| tNRESH | Reset non-select hold time (in response to WCK and RCK)  | 5    |        |      | ns   |

| twes   | WE setup time (in response to WCK)                       | 15   |        |      | ns   |

| tWEH   | WE hold time (in response to WCK)                        | 5    |        |      | ns   |

| tnwes  | WE non-select setup time (in response to WCK)            | 15   |        |      | ns   |

| tnweh  | WE non-select hold time (in response to WCK)             | 5    |        |      | ns   |

| tres   | RE setup time (in response to RCK)                       | 15   |        |      | ns   |

| treh   | RE hold time (in response to RCK)                        | 5    |        |      | ns   |

| tnres  | RE non-select setup time (in response to RCK)            | 15   |        |      | ns   |

| tnreh  | RE non-select hold time (in response to RCK)             | 5    |        |      | ns   |

| tr, tf | Input pulse rise time and fall time                      |      |        | 35   | ns   |

| tH     | Data hold time (Note 1)                                  |      |        | 20   | ms   |

Note 1. The following conditions should be met for each line access:

| WE "H" level period ≤ 20ms - 1152 · twck - WRES "L" level period RE "H" level period ≥ 20ms - 1152 · trck - RRES "L" level period 2. Perform reset operation after turning on power supply.

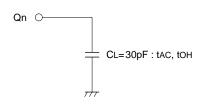

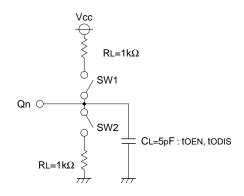

### **TEST CIRCUIT**

Input pulse level:  $0 \sim 3V$  Input pulse rise time and fall time: 3ns Measurement reference level, input: 1.3V

Measurement reference level, output: 1.3V (Note: todis (LZ) is tested at 10% output amplitude, and todis (HZ) is tested at 90% output amplitude.)

Load capacitance CL includes floating capacitance and probe input capacitance.

| Parameter | SW1    | SW2    |

|-----------|--------|--------|

| todis(LZ) | Closed | Open   |

| tODIS(HZ) | Open   | Closed |

| tOEN(ZL)  | Closed | Open   |

| tOEN(ZH)  | Open   | Closed |

## TEST CONDITIONS FOR OUTPUT DISABLE TIME tODIS AND OUTPUT ENABLE TIME TOEN

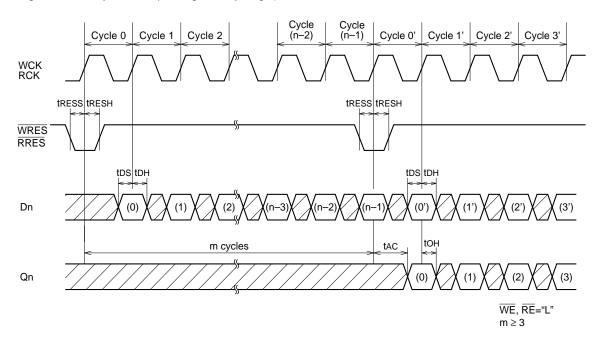

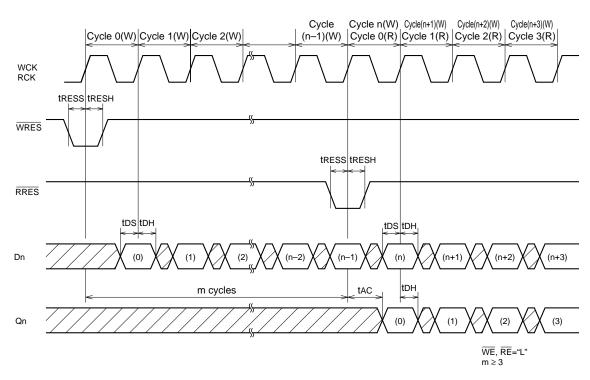

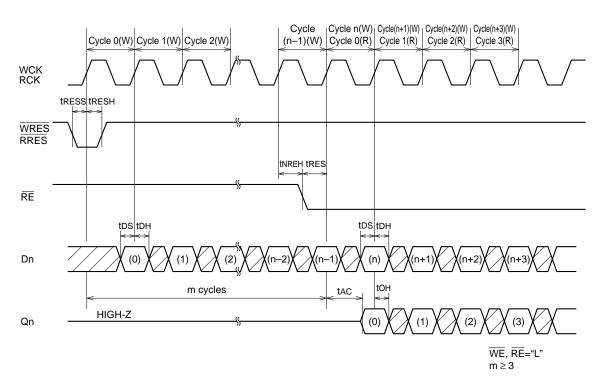

### **TIMING CHARTS**

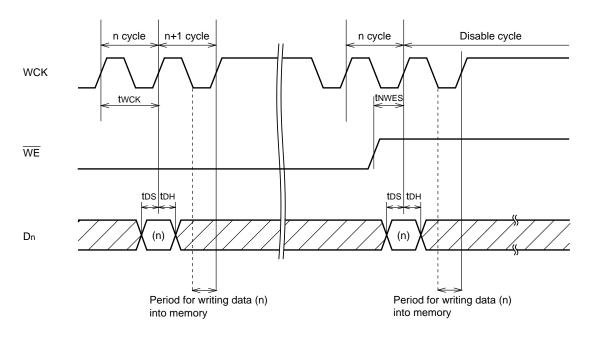

• Write Cycles

### • Write Reset Cycles

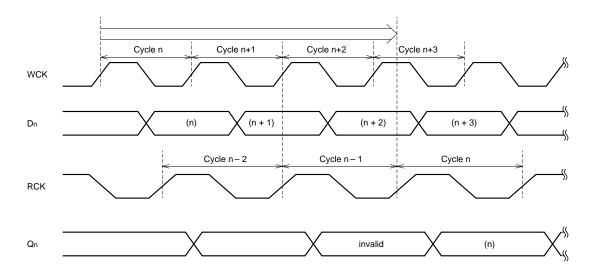

• Matters that needs attention when WCK stops

WRES = "H"

Input data of n cycle is read at the rising edge after WCK of n cycle and writing operation starts in the WCK low-level period of n+1 cycle. The writing operation is complete at the falling edge after n+1 cycle.

To stop reading write data at n cycle, enter WCK before the rising edge after n+1 cycle.

When the cycle next to n cycle is a disable cycle, WCK for a cycle requires to be entered after the disable cycle as well.

## • Read Cycles

### • Read Reset Cycles

MITSUBISHI ELECTRIC

## **VARIABLE-LENGTH DELAY BITS**

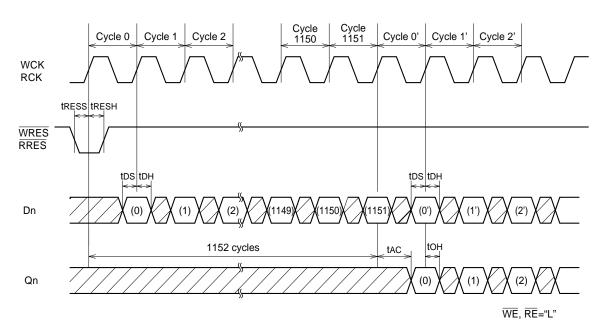

• 1-line (1152-bit) delay

A write input data is written into memory at the second rise edge of WCK in the cycle, and a read output data is output from memory at the first rise edge of RCK in the cycle, so that 1-line delay can be made easily.

n-bit delay 1

(Making a reset at a cycle corresponding to delay length)

n-bit delay 2 (Sliding WRES and RRES at a cycle corresponding to delay length)

n-bit delay 3

(Disabling RE at a cycle corresponding to delay length)

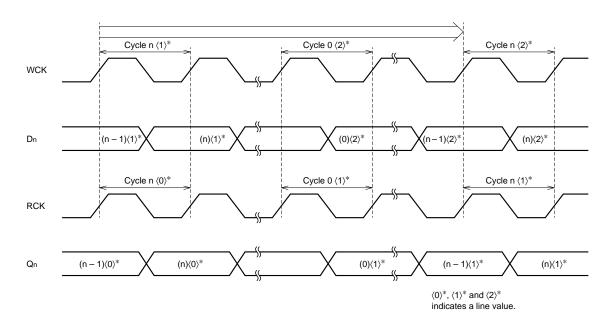

• Shortest read of data "n" written in cycle n

Cycle n-1 on read side should be started after end of cycle n+1 on write side

When the start of cycle n-1 on read side is earlier than the end of cycle n+1 on write side, output Qn of cycle n becomes invalid. In the figure shown below, the read of cycle n-1 is invalid.

Longest read of data "n" written in cycle n: 1-line delay

Cycle n <1>\* on read side should be started when cycle n <2>\* on write is started

Output Qn of n cycle <1>\* can be read until the start of reading side n cycle <1>\* and the start of writing side n cycle <2>\* overlap each other.

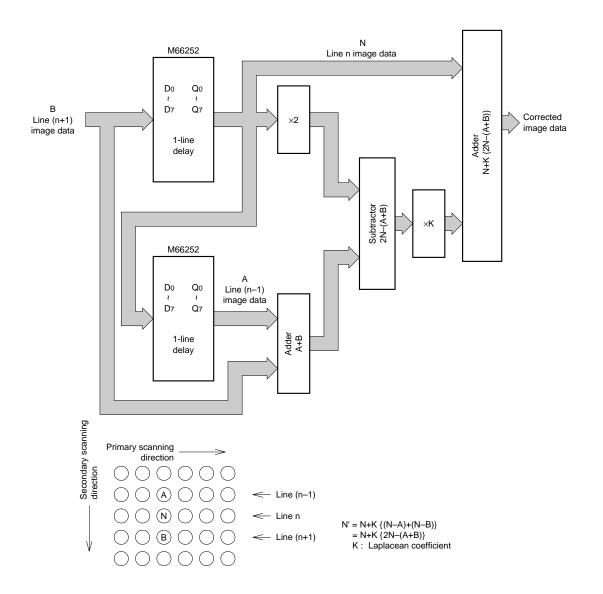

## **APPLICATION EXAMPLE**

Laplacian Filter Circuit for Correction of Resolution in the Secondary Scanning Direction.